столбца (кроме и ) соединены с входом первого операнда второй вычислительной ячейки N+1-го столбца матрицы соответственно, выходы суммы первой и второй вычислительных ячеек первого столбца матрицы соединены соответственно с входаЬли вт-орого операнда к + 1-й и К+2-Й вычислительных ячеек второго столбца матрицы, выходы суммы К вычислительных ячеек (К:: , к+1) N-ro столбца (, n/2-l и n/2+l, п-1) соединены соответственно с входами второго операнда К+2-х вычислительных ячеек ,к) N+1-г столбца матрицы, выходы первого коммутатора соединены соответственно с входами второго операнда К-х вычислительных ячеек ( п/2+1-го столбца матрицы, выходы второго коммутатора соединены соответственно с входами первого операнда К-х вычислительных ячеек (-3, к+1) П/2+1-ГО столбца матрицы, выходы п младших -разрядов седьмого коммутатора соединены соответственно с входами второго операнда первой и второй вычислительных ячеек столбцов с n/2+l по п матрицы, выходы Н/2+1 старших разрядов седьмого коммутатора соединены соответственно с первой группой входов первого коммутатора, входы первого операнда устройства соединены соответственно с первой группой входов четвертого коммутатра, входами группы элементов НЕ, первой группой входов второго коммтатора, входами первого операндов первых вычислительных ячеек столбцов с n/2+l по п матрицы, входы второго операнда устройства соединены соответственно с входами младших разрядов сумматора остатка, первой группой входов седьмого коммутатора, первой группой входов пятого коммутатора, вторая группа входов которого соединена с входами логического нуля устройства, вторая группа входов седьмого коммутатора соединена соответственно с выходами регистра остатка, выход знакового зазряда которого соедине с управляющим входом сумматора-вычитателя частного, выходы сумматора остатка соединены соответственно с входами регистра остатка, входы третьего операнда устройства соединены соответственно с вторыми входами элементов ИЛИ каждого столца с n/2+l по Т1 матрицы, с первыкм группами входов шестого коммутатора, вторые группы входов которого соединены соответственно с выходами группы элементов НЕ, выходы шестого коммутатора соединены соответственно с входами элементов

ИЛИ каждого столбца с 1 по п/2, выходы пятого коммутатора соединены соответственно с входами второго операнда второй и первой вычислительных ячеек каждого столбца с 1 по п/2 матрицы, выходы четвертого коммутатора соединены соответственно с входами первого операнда первой вычислительной ячейки каждого столбца с 1 по п/2 матрицы выход коммутатора операнда К-х вычислительных ячеек (, к+1) п/2 столбца соединены соответственно с второй группой входов второго коммутатора, выходы суммы К-х вычислительных ячеек к+1) п/2 столбца соединены соответственно с второй группой входов первого коммутатора, выходы суммы последних вычислительных ячеек N-ro столца , п/2) и К-х вычислительных ячеек (, к+1)п/2 столбца матрицы соединены соответственнр с первой группой входов сумматора остатка, а выходы суммы к-х вычислихельных ячеек (, к+1) п столбца соединены соответственно с второй группой входов сумматора остатка, начиная с п/2-го разряда, выходы суммы и переноса последних вычислительных ячеек каждого столбца с п/2-го по rt матрицы соединены соответственно с первой и второй группами входов сумматора, выходы которого соединены соответственно с первой группой входов третьего коммутатора, вторая группа входов которого соединена соответственно с выходами: переноса последних вычислительных ячеек каждого столбца с 11/2+1 по п матрицы, выходы третьего ком1у1утатора соединены соответственно с входами переноса коммутаторов переноса каждого столбца с n/2+l по fi матрицы, первой групп входов сумматора-вычитателя частного, вxoдa и регистра частного, второй группой входов четвертого коммутатора, выходы регистра частного соединены с второй группой входов сумматора-вычитателя частного соответственно, третий выход коммутатора переноса n/2+l столбца соединен с первым входом блока задания режимов, выход которого соединен с входами третьего и первого операндов последней вычислительной ячейки п/2-го столбца матрицы, управляющий вход деления устройств соединен с управляющими входами всех коммутаторов и вторым входом блока задания режимов, третий вход которого соединен с управляющими входом извлечения корня устройства

2. Устройство по п;1, отличающееся тем, что вычислительная ячейка содержит элемент И,

, коммутатор, причем первый вход элемента И соединен с входом первого операнда и выходом первого операнда вычислительной ячейки, второй вход элемента И соединен с входом третьего операнда вычислительной ячейки, выход элемента И соединён с первым входом сумматора, второй вход которого соединен с входом второго сятеранда вычислительной ячейки, первым входом коммутатора, второй вход которого соединен с выходом сумматора, вход переноса в младший разряд и въЕюд переноса которого соединены соответственно с входом переноса и выходом переноса вычислительной ячейки, первый и второй управляющие входы вычислительной ячейки соединёй соответственно с первым и вторым управляющими входами коммутатора и первыми выходами вычислительной ячейки выход коммутатора соединен с выходом суммы вычислительной ячейки.

3, Устройство поп, 1, отличающееся тем, что коммутатор переноса содержит первый и второй элементы ИЛИ, первый и второй элементы НЕ, причем управляющий

вход коммутатора переноса соединен с первым входом первого элемента ИЛИ и входом первого элемента НЕ, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с вторым входом первого элемента ИЛИ соединен с первым выходом кок1мутатора переноса и входом второго элемента НЕ, выход которого является вторым выходом коммутатора переноса, выход первого элемента ИЛИ является третьим выходом коммутатора переноса.

4. Устройство по П..1, о т ли чающееся тем, что блок задания режимов содержит элемент ИЛИ , элемент НЕ, элемент И, причем первцй вход блока задания режимов соединен с первым входом элемента И, второй вход которого соединен с элемента НЕ, вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с вторым входом, а второй вход с третьим входом блока задания режимов , выходом блока задания режимов является выход элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Устройство для возведения в квадрат и умножения | 1979 |

|

SU857975A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1108440A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1124284A1 |

1. УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРАТ, ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ, УМНОЖЕНИЯ И ДЕЛЕНИЯ,содержащее матрицу вычислительных ячеек, причем каждый столбец матрицы содержит к+п-1 ячеек (где к - номер столбца, , п, п - разрядность операндов) и коммутатор переноса, первый и второй выходы которого соединены соответственно с первым и вторым управляющими входами последних вычислительных ячеек каждого столбца матрицы, первый и второй управляющие выходы К-+1-й вычислительной ячейки (-К-- номер ячейки) каждого столбца матрицы соединены соответственно с первым и вторым управляющими входами вычислительной ячейки матрицы этого же столбца, выход переноса к-и вычислительной ячейки каждого столбца соединен с входом переноса lc+1-й вычислительной ячейки этого же столбца, отличающееся тем, что, с целью сокращения аппаратуры, оно содержит блок задания режимов, первый, второй, третий, четвертый, пятый, шестой, седьмой коммутаторы, сумматор остатков, регистр остатка, сумматор-вычитатель частного, регистр частного, сумматор, группу элементов НЕ, причем каждый столбец матрицы, кроме первого, содержит к+2 вычислительных ячеек, элемент ИЛИ, коммутатор операнда, первый столбец матрицы содержит две вычислительные ячейки, элемент ИЛИ и коммутатор операнда, выходы переноса последних вычислительных ячеек столбцов с первого по п/2 матрицы соединены, с входами переноса соответствующих коммутаторов переноса, третий выход коммутатора переноса N столбца . (N с 3 по п/2 и с п/2+2 до п) соединены соответственно с входами первого и третьего оп рандов последних вычислительных ячеек N-1-го столбца, входы третьего операнда К-х вычислительных ячеек (,к+1) каждого столбца матрицы соединены соответственно с выхода(Л ми элементов ИЛИ этого же столбца, вход извлечения корня устройства соединен с первым входом элемента ИЛИ, управляющим входом коммутатора операнда, входом переноса первой и входом первого и третьего операндов вторых вычислительных ячеек, управляющим входом коммута СЛ тора переноса столбцов с 1 по п/2 матрицы, вход ИзвлечеН1 е кэадратсо ного корня или деление устройства соСЛ единен с первым входом элемента ИЛИ, управлякщими входами коммутаторов -4j операндов, входами переноса первой и входами первого и третьего операндов вторых вычислительных ячеек, управляющим входом коммутаторов переноса столбцов с п/2+1-го по п и входами первого и третьего операндов последней вычислительной ячейки п-го столбца матрицы, второй управлякнций выход и выход пер- вого операнда первой вычислительной ячейки N-ro столбца (,n) соединены соответственно с первым и вторым входами коммутаторов операнда того же столбца матрицы, выходы коммутаторов операнда N-ro

Изобретение относится к вычислительной технике и может быть исползовано в универсальных или специа- лизированных цифровых вычислительных машинах и устройствах.

Известно устройство для возведения в квадрат и умножения, выполненное в виде матрицы вычислительных ячеек С1 J.

В этом устройстве не предусматривается выполнение операций извлечения квадратного корня и деления.

Известно также устройство для извлечения квадратного корня и возведения в квадрат, включающее треугольного типа матрицу из г строк с tn, вычислительными ячейками ( Шц 2 при к 1, h , к+2 при к 2,...п, где п- разрядность исходных операндов при возведении в квадрат и умножении) и первым логическим блоком в каждой к-й строке матрицы, причем каждая .i-я вычислительная ячейка к-й строки матрицы (i 2,.. .т,-1) соединена с (1-1)-й и (1+1)-й вычислительными ячейками этой же строки матрицы (при к 1,...,п), с (1+2)-й и кроме

вычислительных ячеек двух младших (.1 1,2) и старшего ,(i m) разрядов строк матрицы, с (1+1)-й вычислительными ячейками (К.+1 )-й, кроме

кг:п/2, строки матрицы. Матрица имеет п входов первой, 2п входов второй и п входов третьей групп выхо дов переноса и п выходов Сумма старших разрядов строк матрицы,

0 (п+1) выходов Сумма п-и строки матрицы, (и/2)-я строка матрицы имеет (n/2+l) выходов Сумма и iS/2 выходов Операнд , ()-я строка матрицы имеет (n/2+l) вход.дов четвертой и (п/2) входов пятой групп. Выполнение операции деления с использованием известного устройства возможно в случае, если делимое не превышаетп разрядов, а делитель - (п/2) разрядов. Для обеспечения возможности деления 2празрядных чисел на п- разрядные, кол1 чество вычислительных ячеек в известном устройстве увеличивают

на ( ). 1фоме того, при этом увеличивается время выполнения операций извлечения квадратного корня, возведения в квадрат и умножения за счет увеличения времени распространения переносов в строках матрицы 23.

Цель изобретения - сокращение аппаратурных затрат.

Шставленная цель достигается тем, что устройство для возведения в квадрат, извлечения квадратного корня,- умножения и деления, содержащее матрицу вычислительных ячеек, причем каждый столбец матрицы содержит K+h-l вычислительных ячеек (где К- номер столбца, К 1, п , п разрядность операндов) и коммутатор переноса, первый и второй выходы которого соединены соответственно с первым и вторым управляющими входами последних вычислительных ячеек каждого столбца матрицы, первый и второй управляющие выходы К + 1-Й вычислительной ячейки (К- номер ячейки) каждого столбца матрицы соединены соответственно с первым и вторым управляющими входами К-й вычислительной ячейки матрицы этого же столбца, выход переноса К-й вычислительной ячейки каждого столбца соединен с входом.переноса К+1-Й вычислительной ячейки этого же-столбца, содержит блок задания :режимов, первый, второй, третий, четвертый, пятый, шестой, седьмой коммутаторы, сумматор остатков, регистр остатка, сумматор-вычитатель частного, регистр частного, сумматор, группу элементов НЕ, причем каждый столбец матрицы, кроме первого; содержит К+2 вычислительных ячеек, элемент ИЛИ, коммутатор операнда, первый столбец матрицы содержит две вычислительные ячейки, элемент ИЛИ и коммутатор операнда, выходы переноса последних вычислительных ячеек столбцов с первого по п/2 матрицы соединены с входами переноса соответствующих коммутаторов переноса, третий выход коммутатора переноса N столбца (Nc3no п/2ис п/2+2 по h) соединены соответственно с входами первого и третьего операндов последних вычислительных ячеек Ч-1-го столбца, входы третьего операнда К.-х вычислительных ячеек (, к+1) каждого столбца матрицы соединены соответственно с выходам элементов ИЛИ этого же столбца, вход извлечения корня устройства соединен с первым входом элемента ИЛИ, управляющим входом коммутатор операнда, входом переноса первой и входом первого и третьего операндов вторых вычислительных ячеек управляющим входом коммутатора переноса столбцов с Г по п/2 матрицы, вход Извлечение квадратного корня или деление устройства соединен с первым входом элемента ИЛ управлякщигии входами коммутаторов

операндов, входами переноса первой и входами первого и третьего операндов вычислительных ячеек, управляющим входом коммутаторов переноса столбцов с п/2+1-го по г и входами первого и третьего операндов последней вычислительной ячейки п-го столбца матрицы, второй управляющий выход и выход первого операнда первой вычислительной ячейки 1-го столбца (,п ) соединены соответственно с первым и .вторым вхо.дами коммутаторов операнда того же столбца матрицы, выходы коммутаторов операндда N-ro столбца (кроме Ь) . N n) соединены с входом первого операнда торой вычислительной ячейки N+1-го столбца матрицы соответственно, выходы суммы первой и второй вычислительных ячеек первого столбца матрицы соединены соответственно с входами второго операнда К +1-й и К+2-Й вычислительных ячеек второго столбца матрицы, выходы суммы К вычислительных ячеек (, -R + l) N-ro столбца (, n/2-l и n/2+l, n-1) соединены соответственно с входами второго операнда k+2-x вычислительных ячеек (, X) N+1-го столбца, выходы первого операнда к-х вычислительных ячеек

(КгЗ, K.+1)N -го столбца (М 2, h/2-l и n/2-l, п -1) соединены соответственно с входа1«ш первого операнда К+1-х вычислительных ячеек N+1-го столбца матрицы, выходы первого коммутатора соединены соответственно с входами второго операнда к-х вычислительных ячеек (, ) п/2+1-го столбца матрицы, выходы второго коммутатора соединены соответственно с входами первого операнда К-х ВЕЛЧИСЛИтельныхячеек (, ) п/2+1-го столбца матрицы, выходы п младших разрядов седьмого коммутатора соединены соответственно с входами второго операнда первой и второй вычислительных ячеек столбцов с n/2+l по п матрицы, выходы n/2+l старших разрядов седьмого коммутатора соединены соответственно с первой группой входов первого коммутатора, входы первого операнда устройства соединены соответственно с первой группой входов четвертого коммутатора, входами группы элементов НЕ, первой группой входов второго коммутатора, входами первого операндов первых вичислительных ячеек столбцов с n/2+l по п матрицы, входы второго операнда устройства соединены соответственно с входами младших разрядов сумматора остатка, первой группой входов седьмого коммутатора, первой группой входов пятого коммутатора, вторая группа входов которого соединена с входами логического нуля устройства, вторая

группа входов седьмого коммутатора соединена соответственно с выходами регистра остатка, выход знакового разряда которого соединен с управляющим входом сумматора-вычитателя частного, выходы сумматора остатка соединены соответственно с входами регистра остатка, входы третьего операнда устройства соединены соответственно с вторыми входами элементов ИЛИ каждого столбца с rt/2+l по п матрицы, с первыми группами входов шестого коммутатора, вторые группы входов которого соединены соответственно с выходами группы элементов НЕ, выходы шестого коммутатора соединены соответственно с входами элементов. ИЛИ каждого столбца с 1 по п/2, выходы пятого коммутатора соединены соответственно с входами второго операнда второй и первой вычислительных ячеек каждого столбца с 1 по п/2 матрицы, выходы четвертого коммутатора соединены соответственно с входами первого операнда первой вычислительной ячейки каждого столбца с 1 по п/2 матрицы, выход коммутатора операнда и выходы первого операнда к-х вычислительных ячеек (,1«+1) п/2 столбца соединены соответственно с второй группой входов второго коммутатора, выходы суммы К-X вычислительных ячеек (К.-1, ) п/2 столбца соединены соответственно с второй группой входов первого коммутатора, выходы суммы последних вычислительных ячеек N-ro столбца (, Г1/2) и К-х вычислительных ячеек (, Ж+1) п/2 столбца матрицы соединены соответственно с первой группой входов сумматора остатка, а. выходы суммы К-х -вычислительных йчеек (, In+1 ) п столбца соединены соответственно с второй группой входов сумматора остатка, начиная с П/2-ГО разряда, выходы суммы и переноса последних вычислительных ячеек каждого столбца с п/2-го по п матрицы соединены соответственно с первой и второй.группами входов сумматора, выходы которого соединены соответственно с первой группой входов третьего коммутатора, вторая группа входов которого соединена соответственно с выходами переноса последних вычислительных ячеек каждого столбца см/2+1 по п матрицы, выходы третьего коммутатора соединены соответственно с входами переноса коммутаторов переноса каждого столбца с п/2+1 по п матрицы, первой группой входов сумматора-вычитателя частного, входами ретастра частного, второйгруппой входов четвертого комиутатора, выходы регистр частного соединены с второй группой входов сумматора-вычитателя частного соответственно, третий выход коммутатора переноса n/2+l столбца соединен с первым входом блока задания режимов, выход которого соединен с входами третьего и первого операндов последней вычисли-, тельной ячейки п/2-го столбца матрицы, управляющий вход деления устройства соединен с управляющими входа0 ми всех коммутаторов, и вторым- входом блока задания режимов, третий вход которого соединен с управляющим входом извлечения корня устройства. Вычислительная ячейка содержит

5 элемент И, сумматор, коммутатор, причем первый вход элемента И соединен с входом первого операнда и выходом первого операнда вычислительной ячейки, второй вход

0 элемента И соединен с входом третьего операнда вычислительной ячейки, .выход элемента И соединен с первым входом сумматора, второй вход которого соединен с входом второго опе5 ранда вычислительной ячейки, первым входом коммутатора, второй вход которого соединен с выходом сумматора, вход переноса в младший разряд и выход переноса которого сое0 динены соответственно с входом переноса и выходом переноса вычисли|тельной ячейки, первый и второй управляющие входы вычислительной ячейки, первый и второй управляющие

5 входы вычислительной ячейки соединены соответственно с первым вторым управляющими входами коммутатора и первыми выходами вычислительной ячейки, всзход коммутатора соединен

с выходом суммы вычислительной ячейки.

Коммутатор переноса содержит первый и второй элементы ИЛИ, первый и второй элементы НЕ, причем управляющий вход коммутатора переноса со- . единен с первым входом первого элемента ИЛИ и входом первого элемента НЕ, выход которого соединен ,с первым входом второго элемента ИЛИ, второй вход которого соединен с вторым вхо0 дом первого элемента ИЛИ и входом -переноса коммутатора переноса, выход второго элемента ИЛИ соединен с первым выходом коммутатора переноса и входом второго элемента НЕ,

5 выход которого является вторым ВЕЛХОдом коммутатора переноса, выход первого элемента ИЛИ является третьим выходом коммутатора переноса.

Блок задания режимов содержит эле0 мент ИЛИ, элемент НЕ, элемент И, причем первый вход блока задания режимов соединен с первым входом элемента И, второй вход которого соеди иен с выходом элемента .НЕ, вход 5 которого соединен с выходом элемента ИЛИ, первый вход которого соедилен с вторым входом, а второй вход с третьим входом блока задания режимов, выходом блока задания режимов является выход элемента И.

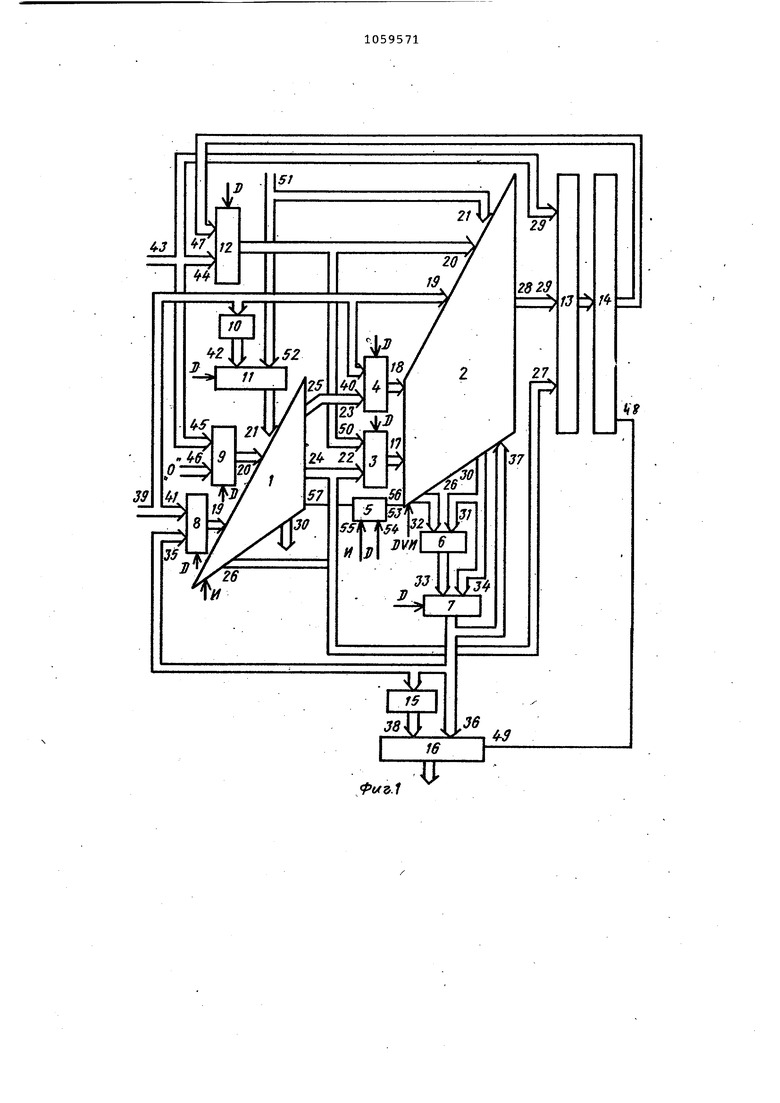

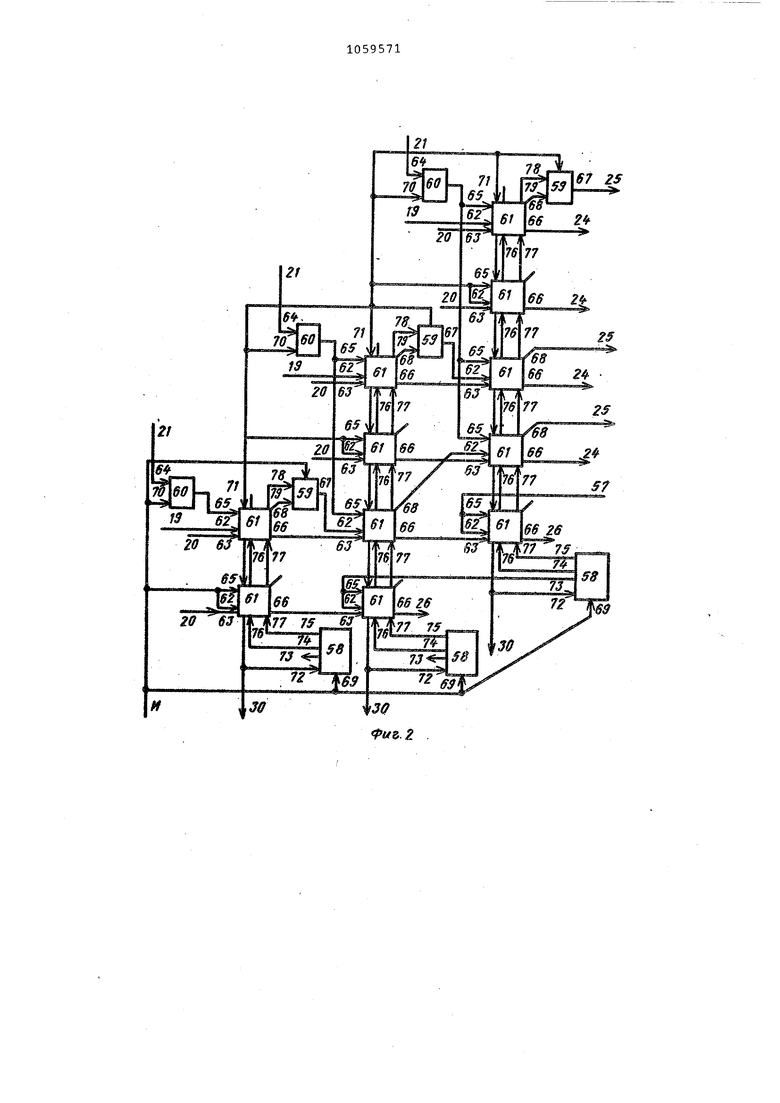

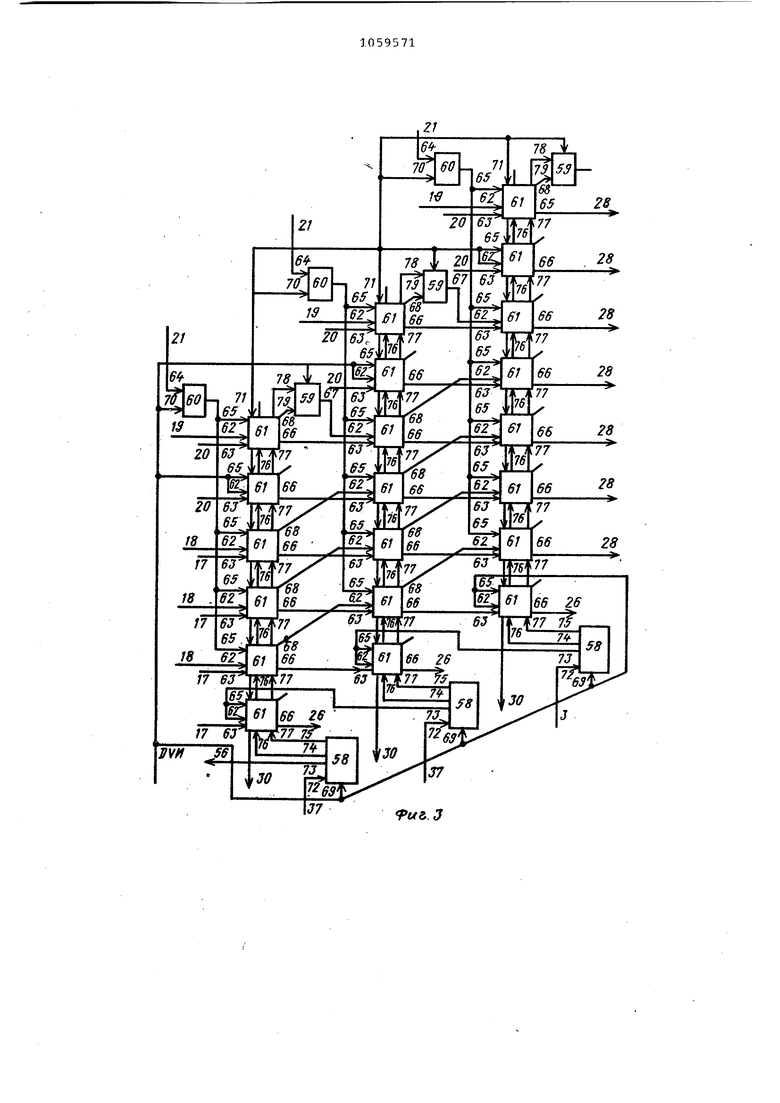

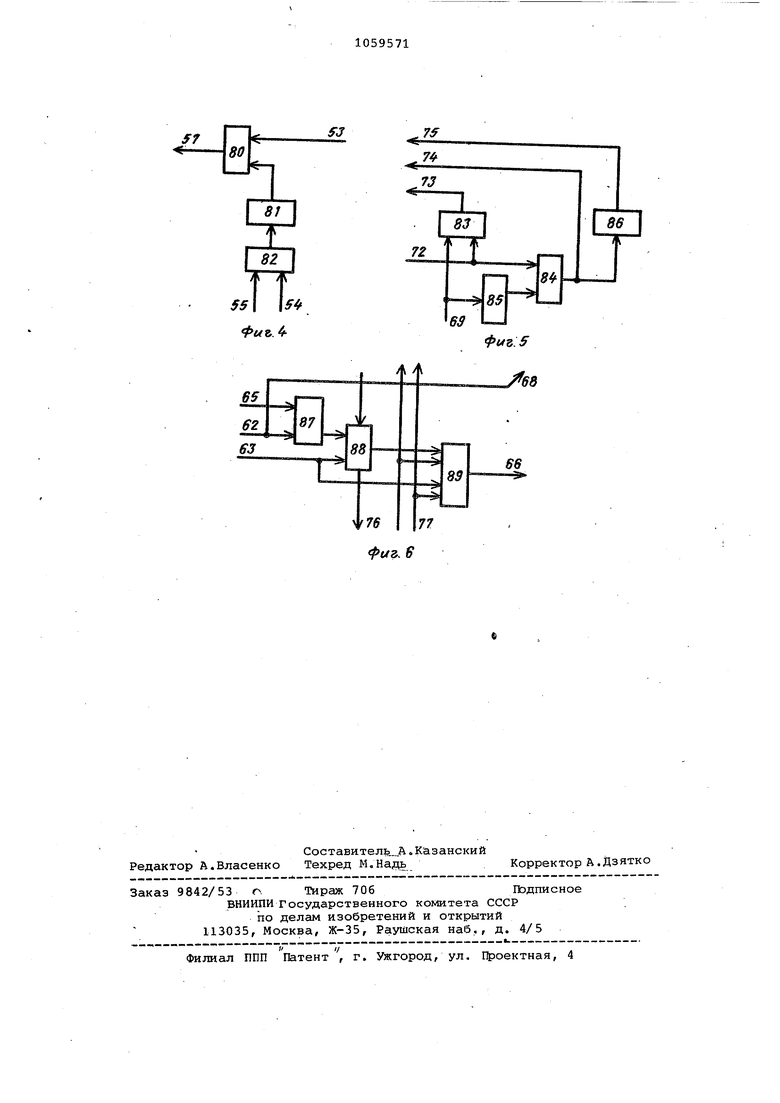

На фиг, 1 приведена схема устройства для возведения в квадрат, извлечения квадратного корня, умножения и деления; на фиг. 2 .- схема первой части матрицы вычислительных ячеек; на фиг. 3 - Схема второй части матрицы вьмислительных ячеек; на фиг. 4 - схема блока задания режимов; на фиг. 5 схема коммутатора . переноса; на фиг. 6 - схема вычислительной ячейки .

Устройство содержит первую 1 и вторую 2 части матрицы вычислительных ячеек, (n/2+l)-разрядный первый коммутатор 3, (п/2)-разрядный второй коммутатор 4, блок задания режимов, сумматор б, третий п/2-разрядный коммутатор 7, п/2-разрядный четвертый коммутатор 8, празрядный пятый коммутатор 9, группу п/2 элементов НЕ 10, п/2- разрядный коммутатор 11, п/2- разрядны шестой коммутатор 12, ( )-разрядный сумматор 13 остатков, (Зп/2+ +2)-разрядный регистр 14 остатка, п/2-разрядный регистр 15 частного, п-разрядный сумматор 16 частного, входы второго операнда 17, первого операнда 18 и 19, вход второго операнда 20, третьего операнда 21 матрицы, вторую группу 22 входов коммутатора 3, первую группу 23 входов 1 оммутатора 4, выходы суммы 24 и опранд 25, выход суммы 26, первую группу 27 входов сумматора 13 остатка, выходы 28 суммы матрицы, вторую группу входов 29 сумматора 13 остатка, выходы 30 переноса матрицы первую 31 и вторую 32 группу входов сумматоров, первую 33 и вторую 34 группу входов третьего коммутатора 7, вторую 35 группу входов коммутатора 4, первую 36 группу входов сумматора-вычитателя 16 частного, входы 37 переноса матрицы, вторую 38 группу входов сумматора-вычитателя частного, вход 39 первого оператора устройства, вторую 40 группу входов коммутатора 2, первую 41 группу входов коммутатора 4, вторую 42 группу входов коммутатора 11 вход 43 второго оператора, вторую 44 группу входов коммутатора 7, первую 45 и вторую 46 группы входов коммутатора 6, первую 47 группу входов коммутатора 7, выход 48 знакового разряда регистра остатка, управлякхций вход 49 сумматора-вычитателя частного, первую 50 группу входов коммутатора 3, вход 51 третьего операнда устройства, первую 52 группу входов коммутатора 11, первый вход 53 блока 5 задания режимов, второй вход 54 и третий вход 55 блока згщания режимов, выход 56 :переноса второй части 2 матрицы, вход 57 переноса первой части 1 матРИДЫ.

Матрица (фиг. 2 и 3 ) содержит коммутаторы 58 переноса, коммутаторы 59 операнда, элементы ИЛИ 60,

0 вычислительные ячейки 61, входы 62 первого операнда, входы 63 второго операнда, первые входы 64 элементов ИЛИ, входы65 третьего операнда, выходы 66 суммы вычислительных яче5 ек, выход 67 коммутатора операнда 59, выходы 68 первого операнда вычислительных ячеек, управляющие входы 69 коммутаторов переноса, вторые входы 70 элементов ИЛИ, входы

0 71 переноса вычислительных ячеек 61, входы 72 переноса коммутаторов 58 переноса, третий 73, второй 74, первый 75, выходы коммутаторов 58 переноса,, первый 76 и второй 77 управ5 ляющие входы вычислительных ячеек 61, первый 78 .и второй 79 входы коммутатора операнда 59.

Блок 5 задания режимов (фиг. 4) содержит элемент И 80, элемент НЕ 81, элемент ИЛИ 82.

Коммутатор 58 переноса (фиг. 5) содержит элементы ИЛИ 83 и 84, элементы НЕ 85 и 86.

Вычислительная ячейка 61 содержит элемент И 87, сумматор 88, коммутатор) 89.

Введенные в устройство коммутаторы обеспечивают подключение к входам матрицы информационных шин,

соответствующих заданному типу операции. Блок задания режимов обеспечивает при выполнении операций возведения в квадрат и умножения передачу сигнала переноса из второй

части матрицы в первую. Сумматор при выполнении операции деления исключает пропадание старших раз- рядов остатков и связанное с этим искажение результата. Сумматор остатков предназначен для вычитания суммы неучтенных при определении старших (младших)разрядов частного частей де штеля из остатка, получаемого после определения значения П/2-ГО .(п-го) разряда частного. Сумматор остатков преобразовывает также полученный полный остаток (в первом такте деления с учетом младших разрядов делимого) в прямой код. Код младших (п/2) разрядов частного может быть положительньш или отрицательным. В последнем случае cyi iaTop частного осуществляет вычитание кода младших (п/2) разрядов частного из кода старших

(п/2) разрядов частного.

Устройство работает следующим образом.

фи вьтолнении операции возведения в квадрат по входу 43 второго исходного операнда через пятый 9 и седьмой 12 коммутаторы на входы 20 матрицы вычислительных ячеек поступает 2п-разрядный код

00.,.00 при выполнении операции вида или код числа В при выполнении операции вида .

По входу 39 первого и по входу 51 второго исходных операндов код возводимого в квадрат числа А поступает соответственно на входы 19 (старшие п/2 разрядов - через четверть коммутатор 8) и на входы 21 (старшие п/2. разрядов - через шестой коммутатор 11) матрицы вычислительных ячеек. В вычислительных ячейках 61.матрицы элементами И 87 вырабатываются поразрядные логические произведения возводимого в квадрат числа. Поразрядные логические произведения суммируются сумматорами 88 вычислительных ячеек 61. Переносы из вычислительной, ячейки 61 старшего разряда каждого N-ro столбца матрицы (М7П/2) через сумматор б, коммутатор 7 и коммутаторы 58 переноса поступают для суммирования на входы вычислительной ячейки 61 старшего разряда (N-1 )-го столбца матрицы. Перенос из старшего разряда (п/2+1.)-го столбца матрицы проходит, кроме того/ через блок5 задания режимов. Переносы/из вычислительной ячейки б1 старшего разря-. да N-ro (, п/2-1,...3) столбца матрицы поступают для суммирования на входы вычислительной ячейки 61 старшего разряда (N-l)-ro столбца матрицы через соответствующие коммутаторы 58 переноса. Ifepвый 3 и второй 4.коммутаторы пропускают соответственно получении в первой части 1 матрицы код суммы с частных произведений и код старших разрядов возводимого в квадрат числа во вторую часть 2 матрицы Результат операции возведения в квадрат снимается с выходов Сумма 28 .п -го столбца матрицы и с выходов Сумма 26 старших разрядов столбца матрицы (кроме первого). Наличие сигналов на выходах 30 переноса вычислительных ячеек 61 старших разрядов первого и второго столбцов матрицы при выполнении операции вида +В говорит о перполнении.

. Операция умножения выполняется за два такта. В первом такте по входу 39 поступает м-разрядный код .-первого сомножителя А 1, а по входу 51 -п -разрядный код второго .сомножителя А 2. Полученный код на

выходах Сумма 28 и 26 запоминает. ся. Во втором такте по входу 39 поступает код второго сомножителя А 2, а по входу 51 - код первого сомножителя А 1. Снимаемый после окончания переходных процессов с выходов 28 и 26 матрицы код суммируется с полученным в первом такте. Результат суммирования - удвоенное произведение двух чисел ( Y 2АцУ О Agb Если пи входу 43 второго исходного операнда на входы 20 матрицы поступает код В 1, а во втоipOM такте - код В 2, то результат (Операции будет соответствовать ко5 ду Ц-2-А 1-А 2Ч-В 2.

Ши выполнении операции извлече- , ния квадратного корня по входу 43 второго исходного операнда подается код подкоренного выражения, кото0 рый через пятый 9 и седьмой 12 коммутаторы проходит на входы 20 второй группы соответственно первой 1 и второй 2 частей матрицы. По входу 39 первого исходного операнда 5 и по входу 51 второго исходного операнда на входы матрицы вычислительных ячеек поступают соответственно коды 0...0 и 1...1 .В каждом N-M столбце матрицы, начиная с пер0 вого,.из остатка от (N-1 )-го вычитания вычитается код а а ... сдвинутый на два разряда ff каждом последующем столбце матрицы относительно предыдущего. Сигналы с выхода 5 30 переноса из старшего разряда N-ro столбца матрицы, соответств ующий искомому значению а, поступает на вход соответствующего, разряда регистра результата, а также через д коммутатор 58 переноса (во второй части 2 матрицы также через сумматор 6 и третий коммутатор 7) на входы 76 и 77 вычислительных ячеек 61 N-го столбца матрицы для управа ления выдачей остатка в (N+1 ) стол- бец матрицы и на вход 79 коммутатора операнда 59 N-го столбца матрицы для формирования кодов .. .а.... aj.,01 (N+l,...,n-l). Сигнал операции извлечения квадратного 0 корня, поступаквдий по шине Извлечение в первую часть 1 матрицы и по шине Извлечение или деление во вторую 2 часть матрицы, управляет работой коммутаторов 58 переноса, 5 коммутаторов 59 операнда и используе.тся при формировании дополнительного кода числа ... Пэсле окончания выполнения операции с выходов 28 л -го столбца матрицы 0 снимается,код остатка.

фи выполнении операции деления код делимого поступает по входу 43 второго исходного операнда, инверсный код делителя - по входу 39 5 первого исходного операнда, по входу 51 третьего исходного операнда поступает код 1...1 , а по шинам логического нуля на входы 46 пятого коммутатора 9 поступает код .0...0

Операция деления выполняется в два такта. В первом такте операции деления код старших (Зп/2+1) раз- . рядов- делимого проходит через седьмой коммутатор 12 на входы 17(через коммутатор 3) и на входы 20 второй части 2 матрицы. Код делителя поступает на входы 18 (через второй коммутатор 4 ) и на входы 19 второй части 2 матрицы. В каждом N-M столбце (N n/2+l,...п) второй части 2 матрицы осуществляется вычитание в дополнительном коде делителя, имеющей вид ООа|,. . .a. Oa|j. из кода остатка, поступающего с выходов 66 (N-l)-ro столбца матрицы, дополненного в двух младших разрядах соответствующими двумя разрядами кода делимого. Формирующиеся в сумматор 6 переносы проходят через третий коммутатор 7, поступают на входы регистра старших разрядов частного 15, по входам 37 матрицы - в соответствующие коммутаторы 58 переноса и на входы четвертого коммутатора 8. Код на выходах переноса сумматора 6 соответствует старшим п/2 разрядам частного с точностью до младшего из них (при условии, что делитель нормализован, в противном случае точность может быть ниже ). Коммутаторы 58 переноса в зависимости от полученного кода разряда частного управляют выдачей остатка из -го в (м+1)-й столбец матрицы. Четвертый коммутатор 8 пропускает код старших разрядов частного на вхо.ды 19 первой части 1 матрицы. На входы 21 первой части 1 матрицы через группу элементов НЕ 10 и шеетой коммутатор11 проходит прямой код соответствующих младших разрядов делителя. В первой части 1 матрицы осуществляется суммирование кодов вида Oa.j. .. .ад (N h/2+l,..., и) и л/2 кодов вида Оа.,цОО...О , причем суммирование каждого иэ этих кодов осуществляется вычислительными ячейками, расп ложенными по диагонали в разных столбцах первой части 1 матрицы. Сумма указанных кодов соответствует сумме частей делителя,не участвовав.ших в вычитании, во второй части 2

матрицы ( с учетом полученных значений соответствующих разрядов частного ). Процесс суммирования в первой части 1 матрицы заканчивается к моменту завершения переходных процессов во второй части 2 матрицы. Устройство позволяет выполнять операции , V-Ai-Al,

, v e +2AiA2 + e2,У:Vc и угс/«.

и . Операция деления реализуется в предлагаемом устройстве без увеличения количества вычислительных ячеек в матрице и без снижения быстродействия при выполнении других операздий. .Суммирование .в операциях видау А --В и + 2Al производится без аппаратурных и временных затрат. В предлагаемом устройстве операции над числами с разрядностью в два раза меньше основной выполняются с большим, быстродействием, кроме того, в этом случае возможно одновременное выполнение двух операций различных видов (в первой и второй частях матрицы). Устройство содержит (,п-2)/2 вычислительных ячеек, семь коммутаторов с общей разрядностью 5п+2, три сумматора с общей разрядностью 3h+2 и два ре гистра с общей разрядностью 2п+2.

В устройстве-прототипе матрица содежит (3n2-h)/2 вычислительных ячеек и 2п+1 разрядный сумматор. Затраты на одну вычислительную ячейку превышают в два раза затраты на один разряд коммутаторам сумматора.

Сравним затраты оборудования, выраженные в количестве разрядов п сумматоров и коммутаторов и количестве гт вычислительных ячеек, прототипа и предлагаемого устройства.

,4n.,

Р...2.3П.2.2П.2 ,

.где Р.- затраты оборудования в прототипе ; Рх- затраты оборудования предла Й

гаемого устройства.

p..4n2M4n-4 0 Из решения уравнения следует, что предлагаемое устройство обладает меньшими аппаратурными затратами прИП,4, где п - разрядность операндов.

5J

f

75

7

цз

д: И

551 |5«

(puz.€

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Высокоскоростные арифметические устройства | |||

| ТИИЭР, т | |||

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Матрица для вьлполнения арифметических операций | |||

| Экспресс-информа ция | |||

| Вычислительная техника, 1980, № 5, с | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-12-07—Публикация

1981-01-26—Подача