выходы р-го управляющего узла подключены соответственно к пятому входу р-й ячейки дополнительно столбца, пятому входу р-й ячейки р-й строки, второму и первому входам р-й ячейки -го столбца матрицы, первые входы управляющих узлов являются входом второго операнда устройства, четвертые входы ячеек дополнительного столбца, вторые и третьи входы управляющих узлов являются соответственно иходами умножения, деления и извле ения квадратного корня устройства, третий вход первой ячейки дополнительного столбца третьи входы ячеек Ьервой строки и N-ro столбца матрицы являются входом третьего операнда устройства, четвертый вход м-го управляющего узла подключен к первому выходу (м-1)-и ячейки дополнительного столбца матрицы, первый выход частного и корня устройства подключен к четвертому входу второго управлякицего узла, пятый вход и пятый выход м-го управлякндего узла подключены соответственно к четвертому выходу (м-1)ячейки (м-1)-й строки матрицы и четвертому входу (м-1)-й ячейки м-й строки матрицы, пятый вход первой ячейки м-й строки матрицы поключен к пятому выходу м-й ячейки дополнительного столбца матрицы, пятый вход (к+2)-и ячейки к-й строки матрицы (к 1,2,...,N-2) подключен к четвертому выходу к-го управляющего узла, второй вход 1/-Й ячейки дополнительноТо столбца матри1ц 1 подключен к сиг,налу нулевого уровня, четвертый вход первого управляющего узла подключен k сигналу единичного уровня, третий вход м-й ячейки дополнительного столца подключен к Третьему выходу первой ячейки п-й строки матрицы, кроме того, управляющий узел содержит четыре элемента ИЛИ и четыре элемент И, причем первый вход управляющего узла соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с первыми входами первого и второго элементов И, второго элемента ИЛИ и вторым входом управляющего узла, третий вход которого соединен с первым входом третьего элемента И, третьим входом первого элемента ИЛИ, перзым входом третьего элемента ИЛИ и вторым входом второго элемента ИЛИ, выход которого соединен с первьм входом чет.вертого элемента И, второй вход которого соединен с вторыми входами первого, второго и третьего элементов И и четвертым входом управляющего, узла, выходы которого и третьего элементов И соединены соответственно с вторым входом третьего элемета ИЛИ и первым входом четвертого элемента ИЛИ, второй вход которого соединен с пятым входом управляющего узла, первый, второй, третий, четвертый и пйтьй выходы которого соединены соответственно с выходами четвертого элемента И, третьего элемента ИЛИ, первого элемента РШИ, первого элемента И и четвертого элемента ИЛИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1108440A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Арифметическое устройство | 1981 |

|

SU1105909A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

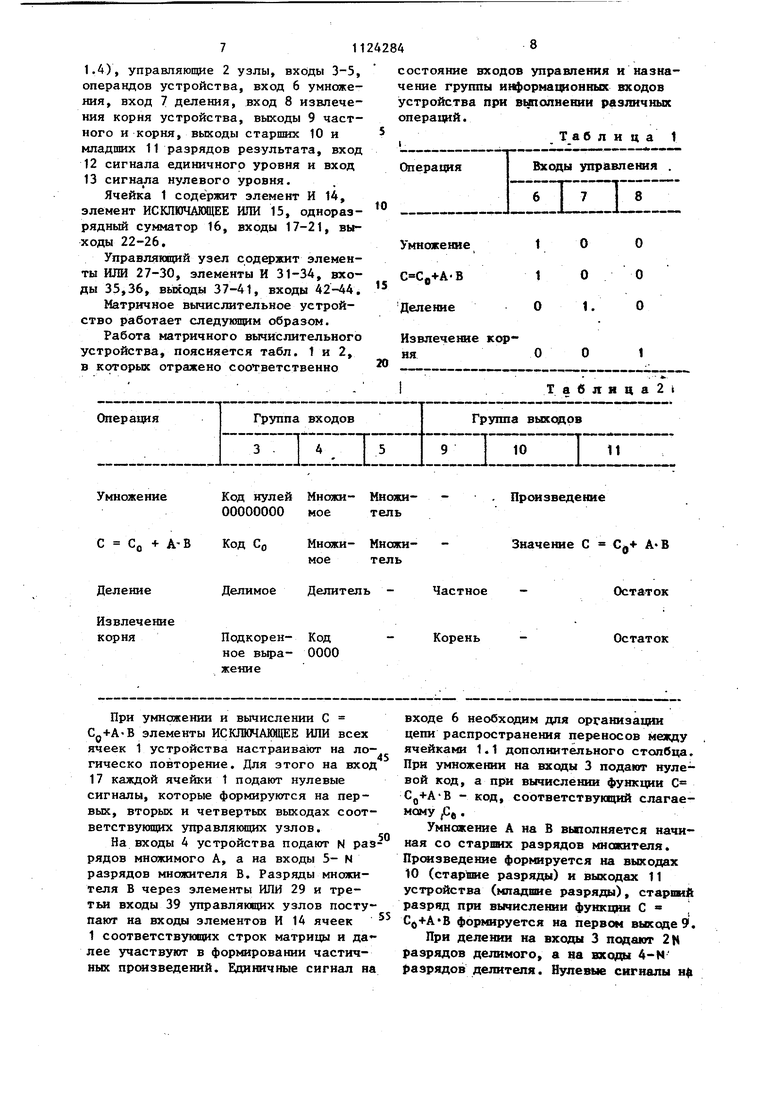

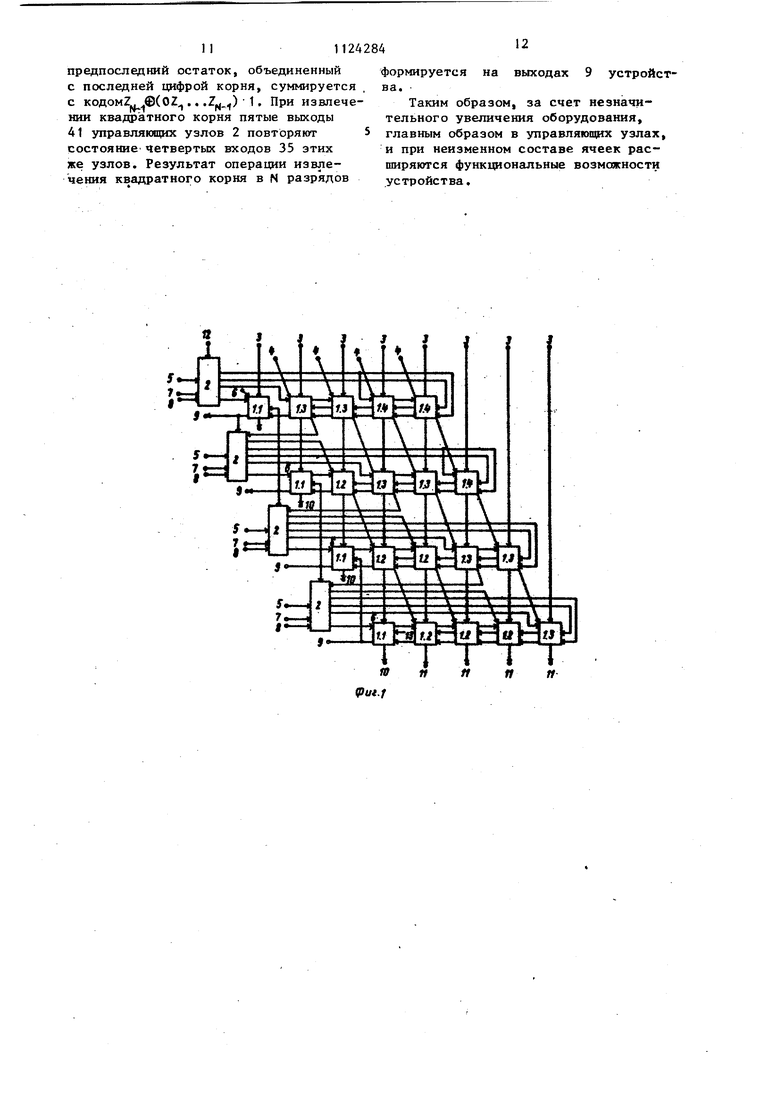

МАТРИЧНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее матрицу ячеек из N строк и N столбцов и дополнительный столбец из N ячеек, причем первый и второй входы п-й ячейки каждой строки матрицы (п 1,2, . .., N-1) подключены соответственно к первому и второму выходам (п+-1)-й ячейки этой же строки, третий вход каждой- ячейки матрицы, за исключением ячеек первой строки и N-ro столбца, подключен к третьему выходу ячейки предьщущей строки последующего столбца, четвертые входы ячеек первой строки матрицы подключены к входам операнда устройства, третьи выходы ячеек N-й строки матрицы являются выходами младших разрядов результа та устройства, четвертый вход каждой ячейки «-Й строки матрицы (м 2,3,...,N), ), за исключением (м-1)-й ячейки этой же строки, подключен к четвертому выходу ячейки предыдущей строки того же столбца,третьи выходь ячеек дополнительного стобца являются выходами старших разрядов результата, пятый вход т-й ячейки . Е-й строки матрицы (t U2,...N-3 т +3, Р +4,... N) подключен к пятому выходу (т-1)-й ячейки этой же строки, пятый выход -и ячейкиj-й с строки матрицы (j 3,4,...М; i 2,3,...j-1), подключен к пятому выходу

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях и быстродействующих ЭВМ для построения однотактных многофункциональных матричных устройств.

Известно матричное устройство для выполнения деления двоичных чисел в прямых кодах, содержащее матрицу ячеек, каждая из которых включает одноразрядный сумматор и элемент ИСКЛЮЧАКЩЕЕ ИЛИ l 3Недостаток данного устройства состоит в ограниченности функциональных

возможностей, так как устройство позволяет выполнять только деление.

Наиболее близким к изобретению по технической сущности является матричное вычислительное устройство, содержащее матрицу ячеек из N строк и N столбцов, дополнительную строку из Н ячеек, группу элементов ИЛИ и три группы элементов И, первый вход п-й ячейки каждой строки (п 2.,3,...,N) подключен к первому выходу (Г-1)-й ячейки этой же строки, второй и третий входы м-й ячейки каждой строки (м 1,2,...,М-1) соответственно подключены к второму и третьему выходу (м+1)-й ячейки этой же строки, вход каждой ячейки каждой erg ки, за исключением ячеек первой строки столбца, подключен к четвертому выходу ячейки предыдущей строки последующего столбца, третий вход каждой ячейки N-rb столбца подключен к первому выходу этой же ячейки, вторые входы ячеек первой строки соответственно подключены к входам первого операнда устройства, четвертые входы ячеек N-й строки являются выходами младших разрядов результата устройства, первый вход п-й ячейки дополнительной стро{ и под ключен к первому выходу (п-1)-й ячей ки этой же Строки, второй вход п-й ячейки дополнительной строки подключен к четвертому выходу (п-1)-й ячейкипервого столбца, третий вход м-й ячейки дополнительной строки подключен к третьему выходу (мн-1)-й ячейки этой же строки, четвертый вход м-й ячейки .дополнительной строки соединен с третьим выходом м-fi ячейки первого столбца, и с первым входом м-го элемента И первой группы, выход которого соединен с первым входом (м+1)-й ячейки первого столбца, третий и четвертый входы N-й ячейки дополнительной строки соединены соответственно с первым выходом этой же ячейки и третьим выходом N-й ячейки первого столбца, пятый вход м-й ячейки каждой строки подключен к пятому выходу (1)-й ячейки этой же строки, первые входы элементов И второй и третьей групп, элементов РШИ группы и вторыевходы элементов И первой группы подключены к первому управляющему входу устройства, вторые входы элементов ИЛИ группы подключены соответственно к вторым входам элементов И третьей группы и к входам старших разрядов второго операнда устройства, вторые входы элементов И второй группы подключены со ответственно к входам младших разрядов второго операнда устройства, четвертые выходы ячеек дополнительно строкиявляются выходами старших раз рядов результата устройства, первый .и второй входы первой ячейки дополни тельной строки подключены к входам нулевого сигнала, первый вход первой ячейки первой строки и пятый вход N-й ячейки дополнительной строки под ключены соответственно к первому и 1 44 торому управляющим входам устройста, четвертые входы ячеек первой троки и N -го столбца подключены сответственно к вькодам соответствуюих элементов И третьей и второй рупп, пятые входы ячеек N-го столба подключены к выходам соответстукяцих элементов ИЛИ группы. Каждая чейка известного устройства содержит дноразрядный сумматор, элемент СКЛЮЧАЩЕЕ ИЛИ и элемент И Zl, Недостатком данного устройства является ограниченность функциональных возможностей, так как при данном наборе ячеек и связей между ними выполняются только две арифметические операции - деление и умножение двоичных чисел в прямых кодах. Целью изобретения является расширение функциональных возможностей за счет реализации операций извлечения квадратного корня и . Поставленная цель достигается теМ, что матричное вычислительное устройство, содержащее матрицу ячеек из N строк и N столбцов, дополнительный столбец из N ячеек, причем первый и второй входы п-й ячейки каждой строки матрицы (п 1,2,.,.,N-1) соответственно подключены к первому и второму выходам (п+1)-й ячейки этой же строки, третий вход каждой ячейки матрицы, за исключениемячеек первой строки и М-го столбца, подключен к третьему выходу ячейки предыдущей строки последующего столбца, четвертые входы ячеек первой строки матрицы подключены к входам операнда устройства, третьи выходы ячеек М-й строки являются выходами младших разрядов результата устройства, четвертый вход каждой ячейки м-й строки матрицы (м 2,3,,.,,N), за исключением (м-1)-й ячейки этой же строки, подключен к четвертому выходу ячейки предьщущей строки того же столбца, третьи выходы ячеек Д9полнительного столбца являются выходами старших разрядов результата, пятый вход т-й ячейки 8-и строки матрицы (в 1,2, .. .,N-3 т +3, t+4,...,N) подключен к пятому выходу (т-1)-й ячейки этой же строки, пятый вход i -и ячейки -и строки мат рицы (3,4, ...,N, j 2,3,..., j-1), подключен к пятому выходу {|-1)-й ячейки этой же строки, пятый выход h-й ячейки п-й строки матрицы под ключей к пятому выходу ()-и ячейки этой же строки матрицы, причем каждая ячейка содержит одноразрядный сумматор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, пятый вход ячейки соеди |нен с пятым выходом ячейки и первым входом элемента ИСКЛЮЧАЮЩЕЕ. ИЛИ, второй вход которого соединен с выходом элемента И, выход элемента ИСКЛЮЧАЩЕЕ ИЛИ соединен с первым -ВХОДОМ сумматора, второй вход, выход суммы, вход переноса и выход переноса которого соединены соответственно с третьим входом, третьим выходом, первым входом и первым выхо(SOM ячейки, первый вход элемента И соединен с вторым входом и вторым вы ходом ячейки, второй вход элемента И соединен с четвертым входом и четвер тым выходом ячейки, содержит столбец из N управляющих .узлов, причем первый вход р-й ячейки дополнительно столбца матрицы подключен к первому выходу р-й ячейки первого столбца матрицы (р 1,2,...,М), второй вход п-й ячейки дополнительного столбца подключен к первому выходу (п+1 )-й ячейки этого же столбца и является выходом частного и корня устройства, первый, второй, третий и четвертый выходы р-го управляющего узла подклю чены соответственно к пятому входу р-й ячейки дополнительного столбца, пятому входу р-й ячейки р-й строки, . второму и первому входам р-й ячейки N-ro столбца матрицы, первые входы управлякшщх узлов являются входом второго операнда устройства, четвертые входы ячеек дополнительного стол ца, вторые и третьи входы управляющи узлов являются соответственно входами умножения, деления и извлечения квадрата корня устройства, третий вход первой ячейки дополнительного столбца, третьи входы ячеек первой строки и N-ro столбца матрицы являют ся входом третьего операнда устройст .Четвертый вход м-го управляклцего узл подключен к первому выходу (м-1)-ой ячейки дополнительного столбца матрицы, первый выход частного и корня устройства подключен к четвертому входу второго управляющего узла, пятьй вход и пятый выход м-го управляющего узла подклю(чены соответственно к четвертому выходу (п-1)-и . ячейки (м-1)-й строки матрицы и четвертому входу (м-1)-и ячейки м-й строки матрицы, пятый вход первой ячейки м-й строки матрицы подключен к пятому выходу м-й ячейки дополнительного столбца матрицы, пятый вход (к+2)-й ячейки к-й строки матрицы (,2,N-2) подключен к четвертому выходу к-го управляющего узла, третий вход м-й ячейки дополнительного столбца подключен к третьему выходу первой ячейки п-й строки матрицы, второй вход N-и ячейки дополнительного стодбца матрицы подключен к сигналу нулевого уровня, четвертый вход первого управляющего узла подключен к сигналу единичного уровня. кроме того,управлянщий узел содержит четыре элемента ИЛИ, четыре элемента И, причем первый вход управляющего узла соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с первыми входами первого и второго, элементов И, второго-элемента ИЛИ и вторым входом управлякяцего узла, третий вход которого соединен с первым входом третьего элемента И, третим входом первого элемент-а ИЛИ, первым входом третьего элемента ИЛИ и вторым входом вторд о элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с вторыми вxoдa м первого, второго и третьего элементов И и четвертым входом управляющего узла, выходы второго и третьего элементов И соединены соответственно с вторым входом третьего элемента ИЛИ и первым входом четвертого элемента ИЛИ, второй вход которого соединен с пятым входом управляющего узла, , второй, третий, четвертый и выходы которого соединены соответствеино с выходами четвертого элемента И, третьего элемента ИЛИ, первого элемента ИЛИ, первого элемента И и четвертого элемента ИЛИ. На фиг. 1 приведена структурная схема матричного вычислительного устройства (npHN-4)j на фиг. 2 - функциональная схема ячейки} на фиг. 3 функциональная схема управлякщего узла. Матричное вычислительное,устройство содержит ячейки 1 (ячейки дополнительного столбца отмечены позицией 1.1, а ячейки матрицы, предварительно разбитые на группы дпя вьятолнения операций извлечения квадратного корня, отмечены позициями 1.2, 1.3, и

12сигнала единичного уровня и вход

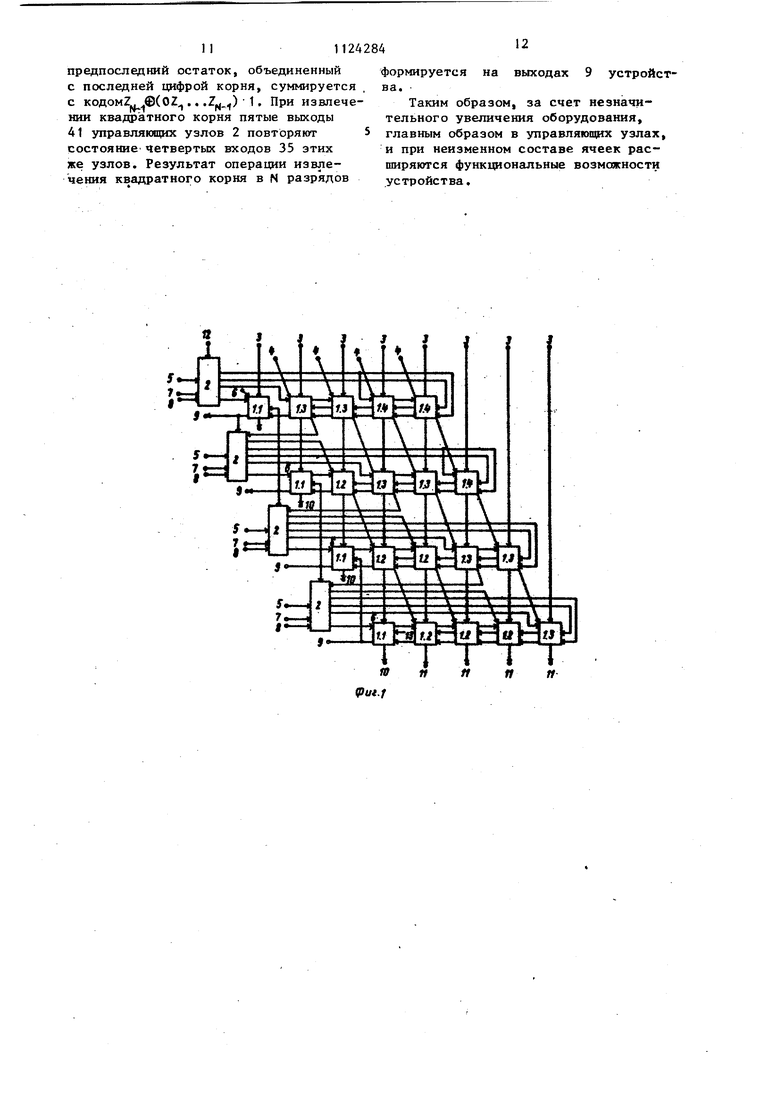

13сигнала нулевого уровня. Ячейка 1 содержит элемент И 14,

элемент ИСКЛЮЧАЩЕЕ ИЛИ 15, одноразрядный сумматор 16, входы 17-21, выходы 22-26.

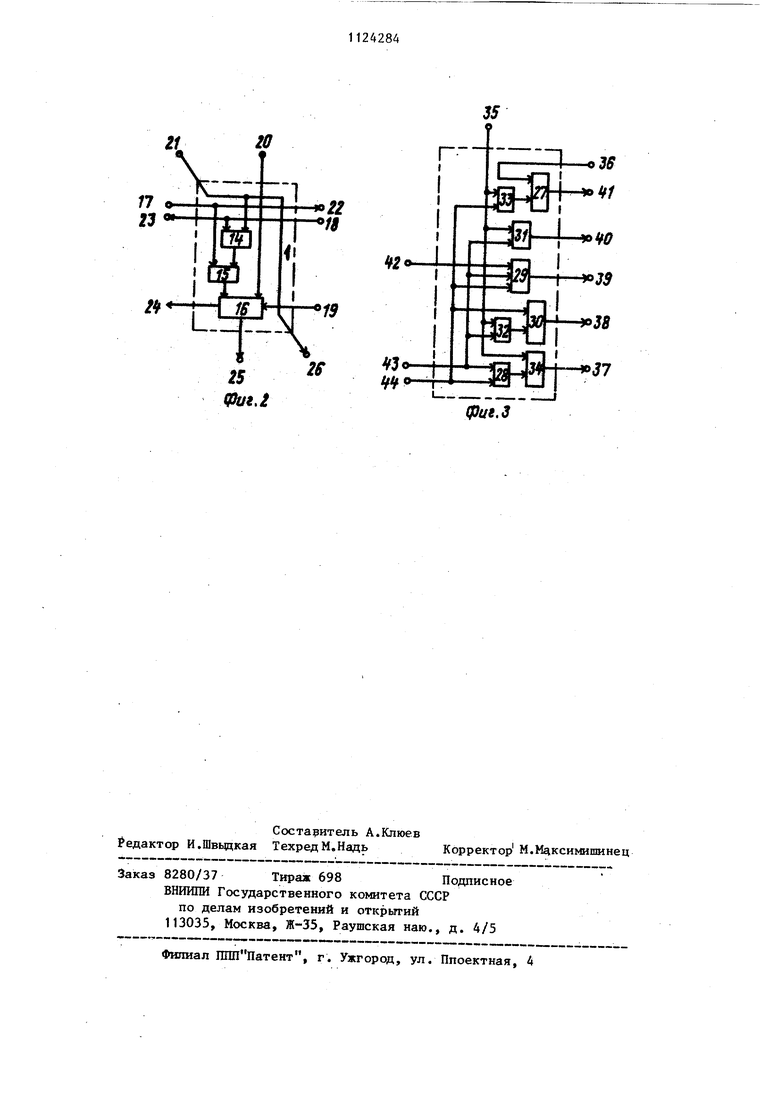

Управляющий узел содержит элементы ИЛИ 27-30, элементы И 31-34, входы 35,36, вькоды 37-41, входы 42-44.

Матричное вычислительное устройство работает следующим образом.

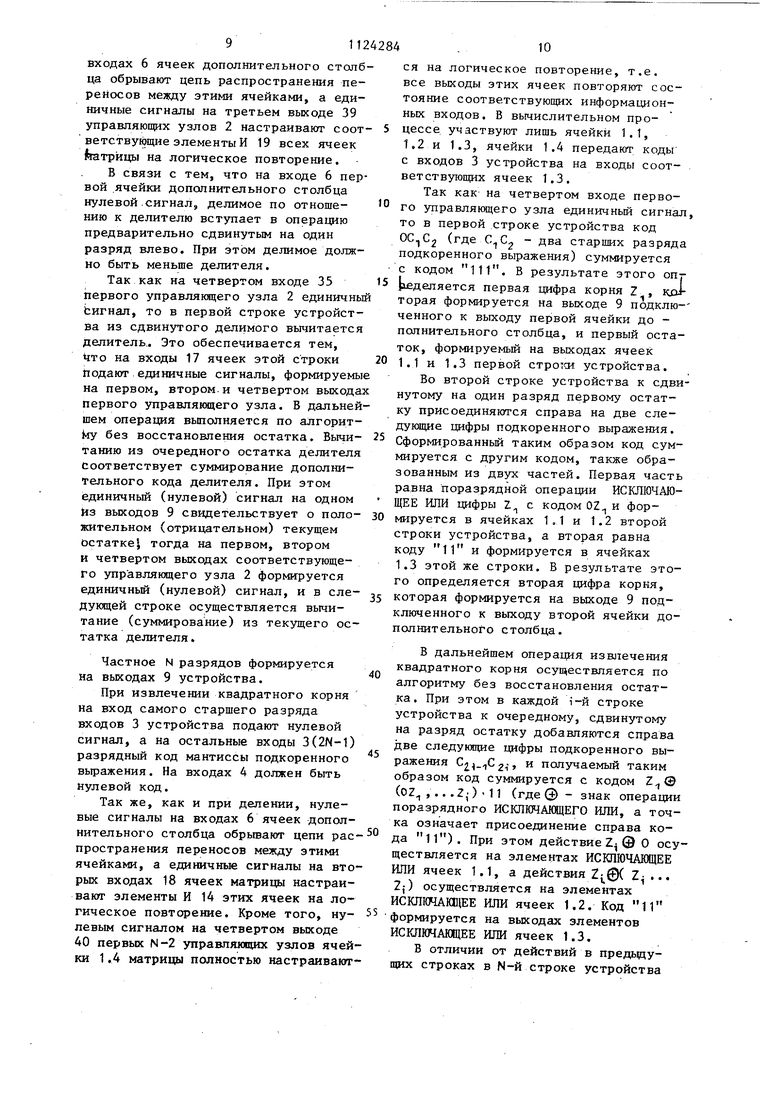

Работа матричного вычислительного устройства, поясняется табл. 1 и 2, в которых отражено соответственно

Код нулей Множи- МножиУмножение00000000 моетель

Мнсвки- МножиА-В

Код GO моетель

Делитель Делимое

е

Подкорен- Код ное выра- 0000 же«ие При умножении и вычислении С CJJ+A-В элементы ИСКЛЮЧАЮЩЕЕ ИЛИ вс ячеек 1 устройства настраивают на ло- гическо повторение. Для этого на вход 17 каждой ячейки 1 подают нулевые сигналы, которые формируются на первых, вторых и четвертых выходах соответствующих управляющих узлов. На входы 4 устройства подают N раз рядов множимого А, а на входы 5- N разрядов множителя В. Разряды множителя В через элементы ИЛИ 29 и третьи входы 39 управляющих узлов поступают на входы элементов И 14 ячеек 1 соответствующих строк матрицы и далее участвуют в формировании частичных прсясзведекий. Единичные сигнал на

состояние входов управления и назначение группы информафюнных входов устройства при выполнении различных операций.

Та блица 1 Входы управления .

Операщ1Я

ILTIilL 8

1 о о

Умножение

100 С Св-«-А-В

Извлечение корО

О ил

Т а в л и ц а 2 i

. Произведение

Значеиие С Сд А-В

Частное - Остаток

Корень - Остаток входе 6 необходим для организации цепи распространения переносов между ячейками 1.1 дополнительного столбца. При умножении на входы 3 подают нулевой код, а при вычислении функции С Cg-J-AB - код, соответствующий слагаемому jCj . Умнокение А на В выполняется начиная со старших разрядов ьшожителя. Прсжзведение формируется на выходах 10 (старшие разряда) и выходах 11 устройства (младшие разряды), старпий разряд при вычислении функции С формируется на первом выходе. При делении иа входы 3 подают 2Н разрядов делимого, а на входы 4-N разрядов делителя. Нулевые сигналы н|1 входах 6 ячеек дополнительного столб ца обрывают цепь распространения переносов между этими ячейками, а единичные сигналы на третьем выходе 39 управляющих узлов 2 настраивают соот ветствующие элементы И 19 всех ячеек Матрицы на логическое повторение. В связи с тем, что на входе 6 пер вой .ячейки дополнительного столбца нулевой.сигнал, делимое по отношению к делителю вступает в операцию предварительно сдвинутым на один разряд влево. При этом делимое должно быть меньше делителя. Так как на четвертом входе 35 первого управлякицего узла 2 единичны Ьигнал, то в первой строке устройства из сдвинутого делимого вычитается делитель.. Это обеспечивается тем, 4то на входы 17 ячеек этой строки подают.единичные сигналы, формируемы на первом, втором.и четвертом выхода первого управляющего узла. В дальней шем операция выполняется по алгоритйу без восстановления остатка. Вычитанию из очередного остатка делителя Соответствует суммирование дополнительного кода делителя. При этом единичный (нулевой) сигнал на одном из выходов 9 свидетельствует о положительном (отрицательном) текущем остаткеJ тогда на первом, втором и четвертом выходах соответствующего управляющего узла 2 фор1«труется единичньй (нулевой) сигнал, и в еледующей строке осуществляется вычитание (суммирование) из текущего остатка делителя. Частное N разрядов формируется на выходах 9 устройства. При извлечении квадратного корня на вход самого старшего разряда входов 3 устройства подают нулевой сигнал, а на остальные входы 3(2N-1) разрядный код мантиссы подкоренного выражения. На входах 4 должен быть нулевой код. Так же, как и при делении, нулевые сигналы на входах 6 ячеек дополнительного столбца обрьгоают цепи рас пространения переносов между этими ячейками, а единичные сигналы на вто рых входах 18 ячеек матрицы настраивают элементы И 14 этих ячеек на логическое повторение. Кроме того, нулевым сигналом на четвертом выходе 40 первых N-2 управляющих узлов ячейки 1.4 матрицы полностью настраиваютИСКПЮЧАЮЩЕЕ ИЛИ ячеек 1.3.

В отличии от действий в предьщущих строках в N-й строке устройства ся на логическое повторение, т.е. все выходы этих ячеек повторяют состояние соответствующих информационных входов. В вычислительном процессе участвуют лишь ячейки 1.1, 1.2 и 1.3, ячейки 1.4 передают коды с входов 3 устройства на входы соответствующих ячеек 1.3. Так как на четвертом входе первого управляющего узла единичньм сигнал, то в первой строке устройства код (где - два старших разряда подкоренного выражения) суммируется с кодом 111. В результате этого опг {ааделяется первая цифра корня 2 , ко торая формируется на выходе 9 подключенного к выходу первой ячейки до полнительного столбца, и первый остаток, формируемый на выходах ячеек 1.1 и 1.3 первой стротш устройства. Во второй строке устройства к сдвинутому на один разряд первому остатку присоединяются справа на две следукяцие цифры подкоренного выражения. Сформированньм таким образом код суммируется с другим кодом, также образованным из двух частей. Первая часть равна поразрядной операции ИСКПЮЧАЮЩЕЕ ИЛИ цифры Z с кодом OZ и формируется в ячейках 1.1 и 1.2 второй строки устройства, а вторая равна коду 11 и формируется в ячейках 1.3 этой же строки. В результате этого определяется вторая цифра корня, которая формируется на выходе 9 подключенного к выходу второй ячейки дополнительного столбца. В дальнейшем операция извлечения квадратного корня осуществляется по алгоритму без восстановления остатка. При этом в каждой i-й строке устройства к очередному, сдвинутому на разряд остатку добавляются справа две следующие цифры подкоренного выражения , и получаемый таким образом код суммируется с кодом (OZ , .. . 2, ) 11 (где 0 - знак операции поразрядного ИСКЛЮЧАЩЕГО ШШ, а точка означает присоединение справа кода ц). При этом действие Z @ О осуществляется на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ ячеек 1.1, а действия ( Z ... Zj) осуществляется на элементах ИСКЛШАЩЕЕ ИЛИ ячеек 1.2. Код 11 формируется на выходах элементов

предпоследний остаток, объединенный с последней цифрой корня, суммируется с кодом ©(OZ .. .Z.) 1. При извлечении квадратного корня пятые выходы 41 управляющих узлов 2 повторяют 5 состояние четвертых входов 35 этих же узлов. Результат операции извлечения квадратного корня в N разрядов

J

формируется на выходах 9 устройства.

Таким образом, за счет незначительного увеличения оборудования, главным образом в управляющих узлах, и при неизменном составе ячеек расширяются функциональные возможности устройства.

П ft

(Put. 3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Карцев М.А., Брик В.А., Вычислительные системы и синхронная арифметика | |||

| М., Радио и связь 1981, с | |||

| Ручная тележка для грузов, превращаемая в сани | 1920 |

|

SU238A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР | |||

| Матричное вычислительное устройство | 1982 |

|

SU1024910A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-15—Публикация

1983-07-29—Подача