N-го коммутатора соединен с выходом сумматора первой суммирующей ячейки N-й строки матрицы, второй вход элемента И с-й сумниругошей ячейки N-й строки матрицы соединен с вторым вхо дом с-го коммутатора, второй вход коммутатора соединен с выкодом переноса сумматора (N-1)-й корректирующей ячейки, управляющие входы коммутаторов соединены с первым входом задания режима устройства, выходы N коммутаторов и выходы сумматоров d суммирующих ячеек последней строки матрицы (, N+1) являются выходами разрядов результата устройства, выход переноса сумматоров первой суммирующей ячейки первой строки матрицы соединен с четвертым входом элемента 2И-ШТИ и вторым входом элемента И второй управляющей ячейки, выход переноса сумматора р-й кор ректирующей ячейки соединен с четвер тым входом элемента 2И-ИЛИ и первым входом элемента И t-й корректирующей ячейки (, N-2 , N), выход переноса сумматора с-й корректирующей ячейки соединен с первым входом элемен та И-ИЛИ (с-1)-и корректирующей ячейк выход элемента ИЛИ i-й управляющей ячейки соединен с первым входом элемента И первой суммирующей ячейки i-й строки матрицы, выход элемента fi 1-й управляющей ячейки соединен с вторым входом элемента И-ШМ с-й корректирующей ячейки, первый вход элемента И предыдущей суммирующей ячейки i-й строки матрицы соединен с первым входом элемента И последующей суммирующей ячейки i-й строки матрицы, выход переноса сумматора первой суммирующей ячейки q-й строки матрицы соединен с входом переноса сумматора х-й корректирующей ячейки (, N5 , N-1), второй вход элемента И-ИЛИ х-й корректирующей ячей10 ки соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой суммирующей ячейки q-й строки матрицы, выход элемента 2И-ИЛИ q-й управляющей ячейки соединен с вторым входом элемента И (q-1)-й суммирующей ячейки q-й строки матрицы, второй вход сумматора всех суммирующих ячеек каждой строки матрицы, кроме двух последних суммирующих ячеек каждой строки, подключен к выходу сумматора суммирующей ячейки предьщущей строки последующего столбца матрицы, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой суммирующей ячейки первой строки матрицы соединен с первым входом задания режима устройства, вторые входы элементов И двух последних суммирующих ячеек строк матрицы соединены с шиной логического нуля устройства, трет.и входы элементов И-ИЛИ (Ы-1)-й корректирующих ячеек соединены с В.ТОРЫМ входом задания режима устройства, второй вход элемента И (р-1)-й суммирующей ячейки р-й строки матрицы, кроме двух последних суммирующих ячеек этой же строки матрицы, подключен к второму входу элемента (р-1)-й суммирующяй, ячейки (р+1)-й строки матрицы, первые входы элементов ИСКЛЮЧА ОЩЕЕ ИЛИ предпоследних суммирующих ячеек М строк матрицы (, N) соединены с первым входом задания режима устройства, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ последних суммирующих ячеек строк матрицы соединены с шиной логического нуля устройства, третий вход элемента 2И-Ш1И f-й управляющей ячейки соединен с (f-l)-M входом старщего разряда операнда (, N), второй вход элемента ИЛИ i-й управляющей ячейки соединен с i-M входом старщего разряда операнда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1984 |

|

SU1171787A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1124284A1 |

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1608653A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1520512A1 |

МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРАТ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ, содержащее столбец из N управляющих ячеек, матрицу из N строк и N+1 столбцов суммируюгцих ячеек (N - разрядность входного числа) , причем первая строка матрицы содержит две суммирующие ячейки, а каждая последующая строка на одну ячейку больше, чем предыдущая, каждая суммирующая ячейка содержит сумматор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом сумматора, каждая управляющая ячейка содержит элемент 2И-ИЛИ, причем первые входы элементов И последних суммирующих ячеек всех строк матрицы соединены с входами переноса сумматоров этих суммирующих ячеек, вторые входы сумматоров п-й и (п+1)-й суммирующих ячеек п-й строки матрицы ( , N) соединены с соответствующими входами младших разрядов операнда устройства, выход переноса сумматора последующей суммирующей ячейки i-й строки матрицы соединен с входом переноса сумматора предьщущей суммирун1шей ячейки i-й строки матрицы i - номер строки матрицы ,N,(i+1)- количество суммирующих ячеек в каждой строке матрицы , первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первых (м-1)-х суммирующих ячеек М-й строки матрицы соединены между собой (,N ...), первый вход задания режима устройства соединен с первым и вторым входом элемента 2И-ИЛИ Ь-й управляющие ячейки (,N), третий вход элемента 2И-ИЛИ 1-й управляющей ячейки соединен с входом

Изобретение относится к вычислитольноГ технике и может быть использопяии I специализированных вычислителях и лысокопромзткдиччльиых ЭВМ

для однотактного выполнения операций возведения в квадрат и извлечения квадратного корня целых и дробных ДВОИЧН)1Х

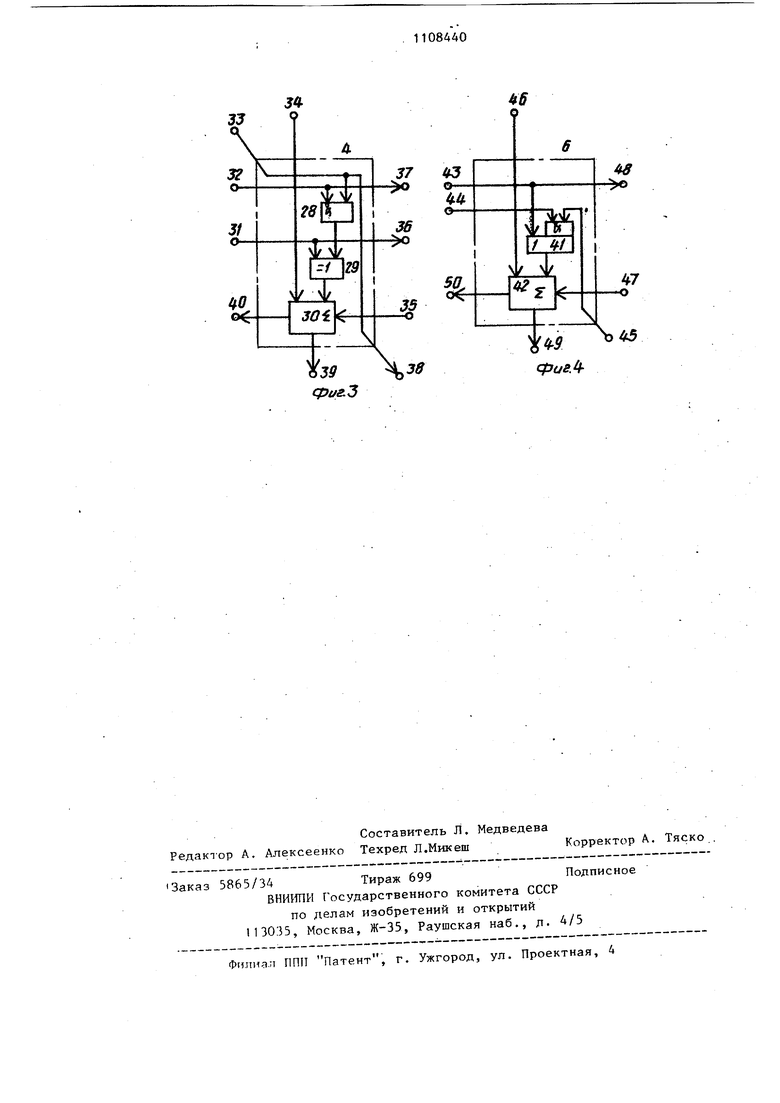

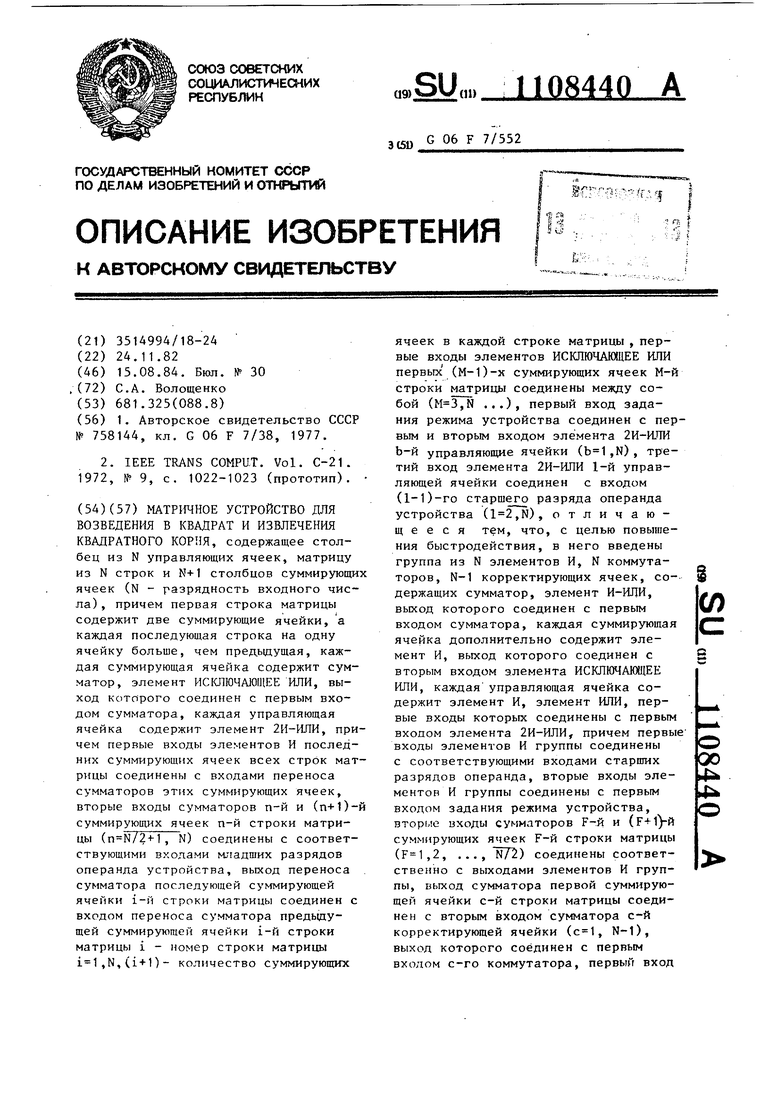

чисел,представленных в прям1.1к кодах. Известно матричное устройство для возведения в квадрат многоразрядных двоичных чисел, содержащее группу элементов И, блок комбинационных сумматоров и регистры для хранения кодов операнда и результатов, работа которого основана на решении формулы о квадрате числа, равного сумме квадратов составляющих его чисел плюс удвоенное произведение каждого числа на все остальные L11. Недостатком этого устройства явля ется отсутствие возможности выполнеНИН операции извлечения квадратного корня. Наиболее близким к изобретению по технической сущности является матрич ное устройство для возведения в квад рат и извлечения квадратного корня, содержащее столбец из N управляющих ячеек, матрицу из N строк и N+1 столбцов суммирующих ячеек, причем первая строка матрицы содержит две суммирующие ячейки, а каждая последу щая строка на одну ячейку больще,чем предыдущая, каждая суммирующая ячейка содержит сумматор и элемент ИСЮ OЧAЮЩEI: или, выход которого соединен с первым входом сумматора, каждая управляющая ячейка содержит элемент 2И-Ш1И, вторые входы сумматоров п-й и (п+1)-й суммирующих ячеек п-й строки матрицы п „ н-1 , N) соединены с соответствующими входами младших ра:фядов операнда устройства выход переноса сумматора последуюи ей суммирующей ячейки i-й строки матрицы соединен с входом переноса сумматора предьщущей суммирующей ячейки i-й строки матриць (i - номер строки матрицы 1 1, 2, ..., N; i. + l - количество суммирующих ячеек в каждой строке матрицы), первые входы элемен тов ИСКЛ10ЧЛЮ1ЦР:Е ИЛИ (М-1)-й суммирую щих ячеек М-й строки матрицы соединены .|ежду C()6oii (,N), первый вхо задания режима устройст1 а соединен с первым и вторым входом элемента 2И-ИЛИ Ь-й управляющей ячейки (,N), третий вход элсмента 2И-ИЛИ 1-й управляющей ячеГ|ки (,N) соединен с вхо дом (1-1)-ги старшего разряда операн.чй устройства 121. едостаток известного устройства зак.тючается и низком быстродействии, что яи.иетсм сглелствием и- быточного оборудования, возрастающего с уведгичением разрядности по закону суммы членов арифметической прогрессии. Цель изобретения - повышение быстродействия . Поставленная цель достигается тем, что в матричное устройство для возведения в .квадрат и извлечения квадратного корня, содержащее столбец из N управляющих ячеек, матрицу из N строк и N+1 столбцов суммирующих ячеек (N - разрядность входного числа), причем первая строка матрицы содержит две суммирующие ячейки, а каждая последующая строка на одну ячейку больше, чем предыдущая, каждая суммирующая ячейка содержит сумматор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом сумматора, каждая управляющая ячейка содержит элемент 2И-ИЛИ, первые входы элементов И последних суммирующих ячеек всех строк матрицы соединены с входами переноса сумматоров эт1тх сум-, мирующих ячеек, вторые входы сумматоров п-й и (п+1)-й сумь;ирующих ячеек п-й строки матрицы (n-N/2- 1 ,N) соединены с соответствующими входами младших разрядов операнда устройства, выход переноса сумматора последующей суммирующей ячейки i-й строки матрицы соединен с входом переноса сумматора предыдущей суммирующей ячейки i-й строки матрицы (i - номер строки матрицы, ,N, i+1 - количество суммирующих ячеек в каждой строке матрицы) , первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первых (М-1)-х суммирующих ячеек М-й строки матрицы соединены между собой (, N, .,.), первый вход задания режима устройства соединен с первым и вторым входом элемента 2И-ИЛИ Ь-й управляющей ячейки (,N), третий вход элемента 2И-ИЛИ 1-й управляющей я.чейки соединен с входом (l-l)-ro cтapщeJ разряда операнда устройства (,N), введены группа из N элементов И, N коммутаторов, N-1 корректирующих ячеек, содержащих сумматор и элемент И-ИЛИ, выход которого соединен с первым входом сумматора, каждая суммирующая ячейка дополнительно содержит элемент И, выход которого соединен с вторым входом элемента ИСКЛЮЧАЮ1ДЕЕ ИЛИ, каждая управляющая ячейка содержит элемент И и элемент КПИ, первые входы которых соединены с первым входом элемента 2И-)-ШИ, причем первые входы т.пементов и группы соединены с соответствующими входами старших разрядов опе ранда, вторые входы элементов И груп пы соединены с первым входом задания режима устройства, вторые входы сумматоров F-й и {Г+1)-й суммирующих ячеек F-й строки матрицы (,2,..,, N/2) соединены соответственно с выходами элементов И группы, выкод сум матора первой суммирующей ячейки с-й строки матрицы соединен с вторым вхйдом сумматора с-й корректирующей ячейки (, N-1), выход которого соединен с первым входом с-го коммутатора, первый вход N-ro коммутатора соединен с выходом сумматора первой суммирующей ячейки N-й строки матрицы, второй вход элемента И с-й сумми рующей ячейки N строки матрицы соеди нен с вторым входом с-го коммутатора второй вход N-ro коммутатора соединен с выходом переноса сумматора (Н-1)-й корректирующей ячейки, управ ляющие входы коммутаторов соединены с первым входом задания режима устройства, выходы N коммутаторов и выходы сумматоров d суммирую1цих ячеек последней строки матрицы (, N+1) являются выходами разрядов результа та устройства, выход переноса сумматора первой суьтирующей ячейки первой строки матрицы соединен с Йчетвер тым входом элемента 2И-ИЛИ и вторым входом элемента И второй управляющий ячейки, выход переноса сумматора р-й корректирующей ячейки соединен с четвертым входом элемента 2И-ИЛИ и первы входом элемента И t-и корректирующей ячейки ( N-2; ,N), выход переноса сумматора с-й корректирующей ячейки Соединен с первым входом элемента И-ИЛИ (с-1)-и. корректирующей ячейки, выход элемента ИПИ i-й управляющей ячейки соединен с первым входом элемента И первой суммирующей ячейки 1-Й I строки матрицы, выход элемента И 1-й управляющей ячейки соединен с вторым входом элемента И-ИЛИ с-й корректирующей ячейки, первый вход элемента И предыдущей суммируюи ей -ячейки i-й строки матрицы соединен с первым входом элемента fl последующей суммирующей ячейки i-й строки матрицы, выход переноса сумматора первой суммирующей ячейки q-й строки матрицы соединен с входом переноса сумматора х-й корректирующей ячейки (,N,, N-l), второй вход элемента И-ИЛИ х-й корректирующей ячейки соединен с первым входом элемента ИСКПЮЧАЮШЕЕ ИЛИ первой суммирующей ячейки q-й строки матрицы, выход элемента 2И-ИЛИ q-й управляющей ячейки соединен с вторым входом элемента И (q-1)-й суммирующей ячейки q-й строки матрицы, второй вход сумматора всех суммирующих ячеек каждой строки матрицы, кроме двух последних суммирующих ячеек каждой строки, подключен к выходу сумматора суммирующей ячейки предыдущей строки последующего столбца матрицы, первый вход элемента ИСКПЮЧАЮЩЕЕ ИЛИ первой суммирующей ячейки первой строки матрицы соединен с первым входом задания режима устройства, вторые входы элементов И двух последних суммирующих ячеек строк матрицы соединены с шиной логического нуля устройства, третьи входы элементов И-ИЛИ (Н-1)-й корректирующих ячеек соединены с вторым входом задания режима устройства, второй вход элемента И (р-1)-й суммирующей ячейки р-й строки матрицы, кроме двух последних суммирующих ячеек этой же строки матрицы, подключен к второму входу элемента (р-1)-й суммирующей ячейки (р-|-1)-й строки матрицы, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ предпоследних суммирующих ячеек М строк матрицы (, N) соединены с первым входом задания режима устройства, первые входы элементов ИСКЛЮЧАЮЩЕЕ последних суммирующих ячеек строк матрицы соединены с шиной логического нуля устройства, третий вход элемента 2И-ИЛИ f-й управляющей ячей.ки . соединен с (f-T)-M старщего разряда операнда (,N), второй вход элемента ИЛИ i-й управляющей ячейки соединен с i-м входом старшего разряда операнда. На фиг, 1 приведена структурная схема предложенного устройства для на фиг. 2 - функциональная схема управляющей ячейки; на фиг. 3 функциональная схема суммирующей ячейки; на фиг. 4 - функциональная схема корректирующей ячейки. Матричное устройство (фиг. 1) содержит столбец 1 из N управляющих ячеек 2, матрицу 3 суммирующих ячеек 4 (первая строка матрицы включает две ячейки 4, а каждая последующая строка включает на одну ячейку больше, чем предыдущая), столбец 5 из N-1 корректирующих ячеек 6, группа 7 из N элементов И 8, строку 9, комму таторы 10, входы 11 старших N разрядов операнда, входы 12 младших разрядов операнда, выходы 13 старших разрядов результата, выходы 14 млад ших N разрядов результата, первый 1 и второй 16 входы задания режима ра боты устройства, вход 17 шины логического нуля. Каждая управляющая ячейка 2 (фиг, 2) содержит элемент 2И-ИЛИ 18 элемент ИЛИ 19, элемент И 20, первый вход 21 элемента И 20 Первый вход элемента 2И-Ш1И 18 выполнен ин версным. Кроме этого, управляющая ячейка 2 имеет второй вход 22 элемента ИЛИ 19, третий вьгход 23 элемента 2И-ИЛИ 18, четвертый вход 24 элемента 2И-11ПИ 18, выход 25 элеме та И 20, выход 26 элемента ИЛИ 19, выход 27 элемента 2И-ИЛИ 18. Каждая суммирующая ячейка 4 содержит элемент И 28, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 29, сумматор 30, первый вход 31 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 29 первый вход 32 элемента И 28, второй вход 33 элемента И 28, вход 34 сумматора 30, вход 35 переноса сумматора 30, выход 36 суммирующей яче ки 4, соединенный с первым входом 31 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 29, выход 37 суммирующей ячейки 4, соеди ненньй с первым входом 32 элемента И 28, выход 38 суммирующей ячейки 4 соединенный с вторым входом 33 элемента И 28, выход 39 сумматора 30, выход 40 переноса сумматора 30. Каждая корректирующая ячейка 6 содержит элемент И-ИЛИ 41, сумматор 42, второй, третий и первый входы 43, 44 и 45 элемента И-ИЛИ 41 вход 46 сумматора 42, вход 47 переноса сумматора 42, выход 48 корректирующей ячейки 6, соединенный с вт рым входом элемента И-ИЛИ 41, вьгход 49 суммы, вьгход 50 переноса сумматора 42. Номера строк матрицы 3 суммирующих ячеек 4 возрастают сверху вниз а столбцов - слева направо. При нулевом сигнале на управляющих входах коммутаторов 10 (на первом входе 15 задания режима работы ycтpgйcтвa О), коммутаторы переда ют информацию со своих первых входов, а при единичном сигнале - с вторых входов. Для вьтолнения операции возведеия в квадрат на входах 15 и 16 задаия режима устройства должетбыть од 01, а при извлечении квадратого корня - 10. Матричное устройство работает ледующим образом. Возведение в квадрат в устройстве осуществляется по алгоритму, который для дробных чисел выражается нтерационной формулой fn-, 01)-2 . f-2 Р,Г„., +f И F 0, при ,N п-й разряд N-разрядного кода операнда; 7 - значение квадрата числа на п-м шаге итерации; Гц - результат вьтолнения операции возведения в квадрат. Код операнда в N разрядов подают на входы 11 устройства. Результат выполнения операции возведения в квадрат формируется на выходах 13 и 14 устройства. При этом на выходах 13 формируется N старших разрядов результата, а на выходах 14 - N младщих разрядов. На входах 12 должен быть нулевой код. Операция возведения в квадрат осуществляется в устройстве с использованием сумматоров 30 и элементов И 28 суммирующих ячеек 4. Лри этом все элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 29 нулевым сигналом на первом входе настраиваются на логическое повторение. Необходимые нулевые сигналы поступают на элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 29 с входом 15 и 17, а также с выхода элемента И 20 управляющих ячеек 2. Единичный сигнал на входах 16 организует цепь распространения переносов между сумматорами 42 корректирующих ячеек 6. Умножение на коэффициент 2 выполняется сдвигом и соответствующей коммутацией входов и выходов матрицы 3 строк суммирующих ячеек 4 устройства. Вычисление произведения (f f2 .. . fr(., 01) осуществляется на элементах И 28 суммирующих ячеек 4 п-й строки матрицы 3. Вычисление суммы в итерационной формуле алгоритма осуществляется с испольтованием сумматоров 30 суммирующих ячеек 4 п-й строки матрицы 3 и сумматора 9 42 (п-1)-й корректирующей ячейки 6 столбца 5. При этом нулевое значение обеспечивается нулевым кодо на входах 12 и нулевым сигналом на входе 15 задания режима, блокирующи элементы И 8.Передача же в п-ю строку матрицы 3 п-1 цифр операнда осуществляется через третьи нходы элемен тов 2И-ИЛИ 18 управляющих ячеек 2 столбца 1, выходы которых подключены к вторым входам элементов И 28 соответствующих суммирующих ячеек 4 матрицы. Передача же в п-ю строку ма рицы 3 цифры f операнда для последующего вычисления произведения ( fj ... 01) осуществляется через элемент ИЛИ 19 п-й управляющей ячейки 2. Формирование кода 01 во втором сомножителе произведения осуществляется связью входов перекоса сумматора последней суммирующей ячей ки 4 каждой строки матрицы 3 с первым входом элемента И 28 этой суммирующей ячейки 4. В силу того, что на управляющих входах коммутаторов 10 нулевой сигнал, на выходы 13 передается код N старших разрядов результата, формируемый на выходах сумматоров 42 коррек тирующих ячеек 6 и выходе сумматора 30 первой суммирующей ячейки 4 п-й строки матрицы 3. Младшие N разрядов результата, поступающие на выход 13 устройства, формируются на Bbixoдах сумматоров остальных {N-1)-x сум мирующих ячеек 4 N-й строки матрицы 3. Извлечение квадратного корня в устройстве осуществляется по известному алгоритму, извлечения корня без восстановления остатка, в которо п-я цифра корня Z( равна 1, если п-й остаток , шги Z равна О, если Qr| О. При этом Qy, вычисляется по выражению , .f,,, f, +Zvi-, +0,11-2 при ,N и Од 0, f 2п очередная п-я пара анализируемых разрядов 2К-разрядного подкоренного вьфажения; -п разрядный код, равный 7,„-, .2 Zj ... . . . Zt,, , т.е. опера ции поразрядного ИСКЛЮЧАЮЩЕГО ИЛИ t40 (п-1)-и цифры корня со всеми определенными до того цифрами, с цифрой О в знаковом разряде при Zo 0. Настройка на извлечение квадратного корня осу дествляется подачей на входы 15 и 16 кода 10. На входы 11 и 12 подают 2N разрядов подкоренного выражения. При этом на входы 11 подают N старших разрядов, а на входы 12-N младщих разрядов подкоренного числа. Результат операции в N разрядов-f(значение корня) формируется на выходах 13 устройства. На выходах 13 формируется N-разрядный остаток в дополнительном коде. Выполнение операции осуществляется с использованием сумматоров 30 и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 29 суммирующих ячеек 4. При этом все элементы И 28 суммирующих ячеек 4 единичным сигналом на первых входах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 29 настраиваются на логическое повторение. Необходимые для этого единичные сигналы поступают с выходов элементов HJIH 19 управляющих ячеек 2. Нулевой сигнал на входах 16 ликвидирует цепь распространения переносов между сумматорами 42 корректирующих ячеек 6 столбца 5. I Умножение,кода предыдущего остатка Q на 2 выполняется сдвигом и соответствующей коммутацией входов и выходов сумматоров 30 CTpoij суммирующих ячеек 4 устройства. Очередные пары анализируемых разрядов подкоренного выражения подаются на вторые входы сумматоров 30 двух последних суммирующих ячеек 4 п-й строки матрицы 3 с входов 12 или через элементы И 8 с входов 11 устройства. Вычисление слагаемого Z tPO.... ...Z/,1 осуществляется на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 29 суммирующих ячеек 4 п-й строки матрицы 3, за исключением двух последних суммирующих ячеек 4 той же строки матрицы 3. Вычисление сум-м двух ходов, первый из которых составлен из первого и второго слагаемых, а второй - из третьего и четвертого слагаемых выражения для вычисления остатка ()vi осуществляется с использовалием сумматороп 40 суммирующих ячеек 4 n-)f строки матрицы 3 и сумматора 42 (п-1)-й корректирующей ячейки 6 столбца 5. При этом нулевое значение Qg обеспечивается нулевыми сигналами на входах 17 суммирующих ячеек 4 первой строки матрицыЗ, а код П четвертого слагаемого - единичными сигналами на входа 15, подключенных к первым входам эле ментов ИСКПЮЧАЮЩЕЕ ИЛИ 29 предпослед них суммирующих ячеек 4 каждой строки матрицы 3 и связью первого входа элемента И 28 и входа переноса сумма тора 30 каждой из последних суммирую щих ячеек 4 матрицы 3. Цифры корня формируются на выходах переноса сумматоров 42 корректирующих ячеек 6 и выходе переноса сумматора 30 первой суммирующей ячейки 4 первой строки. Так как на входе 15 единичный сигнал передача в п-ю строку матрицы 3 п-1 выполненных цифр корня осуществляется через четвертые входы элементов 2 И-ИЛИ 18 управляющих ячеек 2 столбца 1. Передача же в п-ю строку матрицы 3 цифры ZM- для последующего вычисления Zk,,, (JO. . . .Zv,, осуществляется через элемент И 20 п-й управляющей ячейки 2. Так как на управляющих входах ком мутаторов 10 единичный сигнал, на выходы 13 передается код N разрядов корня, сформирован}1ый на выходах переноса сумматоров 42 корректирующих .11 ячеек 6 и на выходе переноса сумматора 30 первой суммируюп(ей ячейки 4 первой строки матрицы 3. Время извлечения квадратного«корня у прототипа равно t,,{2,5-N+0,5 NOtp+N(,,,, ,,д„ ) где tp - время распространения переноса в сумматоре; -K.wcti. i(tu время срабатывания коммутатора и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Время извлечения квадратного корня у матричного устройства равно t(0,5N4-0,(t,+t,,ctA.) + +t| +2tp . Бремя возведения в квадрат сохранилось прежним и равно 2Nt-p+2tj/. При сопоставлении t и t2 видно, что .t(.,, т.е. увеличивается быстродействие . Кроме того, ( окращается объем аппаратурных затрат, разница в числе суммирующих ячеек двух соседних строк матрицы у предложенного устройства равна единице, а прототипа - дпум, при этом элементов в суммирующей ячейке прототигта больше.

Фи8.2

Ъ39 ф1/&3

5

38 ФиеЛ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 758144, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| IEEE TRANS COMPUT | |||

| Vol | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| ПРЕДОХРАНИТЕЛЬ ОТ ВЗРЫВА ХРАНИЛИЩ ЛЕГКО ВОСПЛАМЕНЯЮЩИХСЯ ЖИДКОСТЕЙ | 1923 |

|

SU1022A1 |

Авторы

Даты

1984-08-15—Публикация

1982-11-24—Подача