(54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1978 |

|

SU773617A1 |

| Устройство для вычисления показательно-степенной функции | 1980 |

|

SU920717A1 |

| Устройство для вычисления логарифмов чисел | 1980 |

|

SU932491A1 |

| Устройство для вычисления корней квадратного уравнения | 1980 |

|

SU999060A1 |

| Устройство для извлечения корняТРЕТьЕй СТЕпЕНи | 1979 |

|

SU842803A1 |

| Матричный вычислитель | 1983 |

|

SU1137464A1 |

| Устройство для вычисления зависимости @ = @ + @ + @ | 1981 |

|

SU1019446A1 |

| Матричный вычислитель | 1982 |

|

SU1083185A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

1

Изобретение относится к вычислительной технике и может быть применено автономно в качестве спецпроцессора в комплексе с цифровой вычислительной машиной для оперативного вычисления корня квадратного в системах автоматического управления динамическими объектами.

Известно устройство для извлечения квадратного корня, содержащее сумматор,первую и вторую группу вентилей, схему И, генератор тактовых импульсов, счетчик 1 .

Однако в известном устройстве вычислительный процесс организован в виде временной последовательности шагов, что определяет его относительно невысокое быстродействие.

Наиболее близким к предлагаемому по технической сущности является устройство для извлечения квадратного корня, содержащее (п-.1) группу последовательно соединенных одноразрядных сумматоров, где п - разрядность выходного кода, группу сумматоров по модулю два, группу злемеитов ИЛИ, группу элементов НЕ, (п-2) дополнительных группы

ИЗ (п-i-1) (где i - номер группы) суммато ров по модулю два в каждой группе {2. .

Недостатками устройства являются относительно высокая сложность и низкое быстродействие, обусловленные использованием в каждой i-ой группе 2 (п-i) одноразрядных сумматоров и структурной организацией устройства.

Цель изобретения - упрощение устройства для извлечения квадратного корня и увеличение быстродействия.

10

Указанная цель достигается тем, что в устройство для извлечения квадратного корня, содержащее (п-1) группу последовательно соединенных одноразрядных сумматоров, где п разрядность выходного кода, группу сумматор

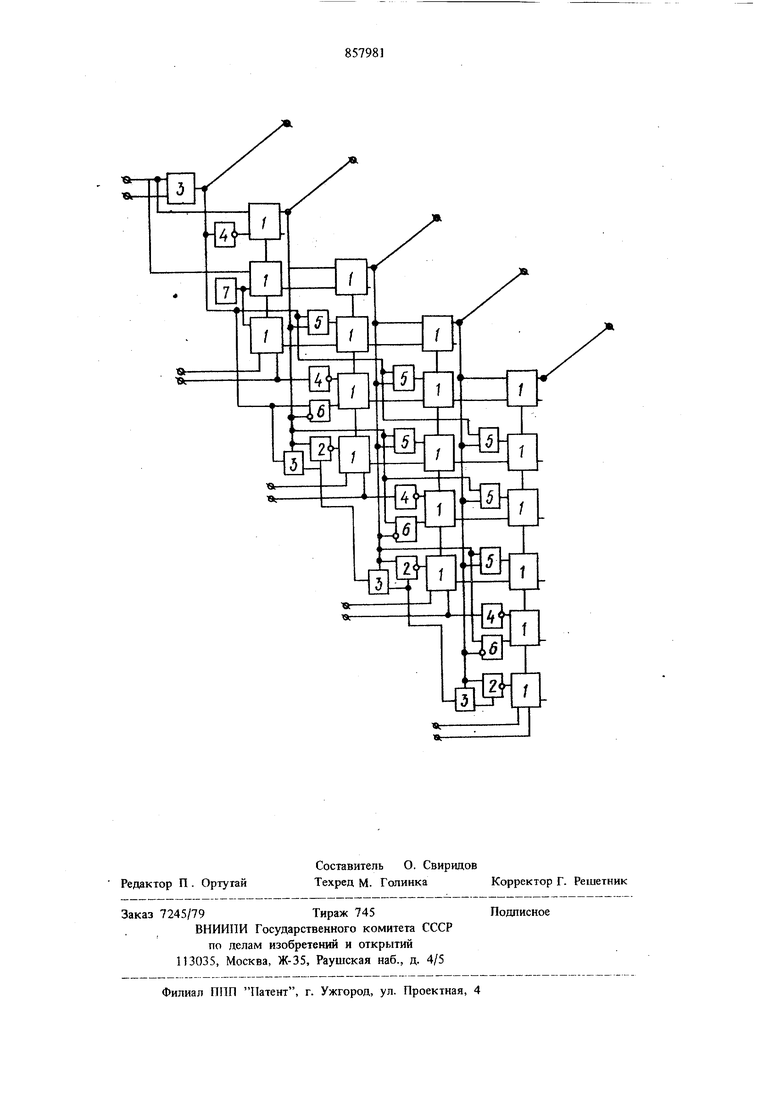

5 по модулю два, группу элементов ИЛИ, элементов НЕ, (п-2) дополнительных группы из (п-i-1), где i - номер группы сумматоров по модулю два в каждой группе, введены генератор единицы и группа из (п-2) элемен20тов И, каждая i-я группа (, Z... п-1) одноразрядных сумматоров содержит (п+2-i) одноразрядных сумматоров, группы элементов ИЛИ, элементов НЕ содержат (п-1) элементов, группа сумматоров по модулю два содержит (п-2) сумматоров по модулю два, причем выход каждого j-ro ... n-i + 1) одноразрядного сумматора (1+1)-ой группы соединен с первым входом (j-l)-ro одноразрядного сумматора, t-ой группы второй вход первого одноразрядного сумматора i-ой группы соединен с выходом переноса первого бдноразрядного сумматора (1+1)-ой группы первыми входами i-ых элементов И, ИЛИ, сумматоров по модулю два групп и сумматоров по модулю два i-ой дополнительной группы, выходы которых соединены с вторыми входами j-ых (,... п-1) одноразрядных сумматоров i-ой группы, вторые входы j-ых ,... n-i-1) сумматоров по мбдулю два i-ой дополнительной группы соединены с выходами переноса первых одноразрядных сумматоров ()-ых групп, выход i-ro элемента НЕ группы подключен к первому вхо;;у (п+1-i)-ro одноразрядного сумматора i-ой группы, второй вход которого соединен с выходом i-ro элемента И группы, подключенного вторым входом к выходу переноса первого одноразрядного сумматора (i-2)-о группы, первый вход (п-ь2-)-го одноразрядного сумматора i-ой группы подключен к выходу ,i-ro сумматора по модулю два группы, подключешюго вторым входом к выходу i- го элемента ИЛИ группы, второй вход которого соединен с выходом (i-(-l)-ro элемента ИЛИ группы, выход (п-1)-го элемента ИЛИ которой соединен с первы входом первого сумматора по модулю два каждой i-ой дополнительной группы, входом (п-1)-го элемента. НЕ группы и вторым входом (п-2)-то элемента ИЛИ группы, второй вход (п+2-i)-ro одноразрядного сумматора i-ой группы соединен с 21-ым разрядом входного кода устройства, {2i-1)-й разряд которого подключен к третьему входу одноразрядного сумматора и входу i-ro элемента НЕ группы, 2п и (2п-1)-й разряд входного кода устройства подключены к входам (п-1)-го элемента ИЛИ группы и к первым входам соответственно первого и второго одноразрядного сумматора (п-1)-и группы, вторые входы которых соединены соответственно с выходом (n-l)-ro элемента НЕ группы и генератора единиц, подключенного к перво му входу третьего одноразрядного сумматора (п-1)-и группы, выходы переносов первых одноразрядных сумматоров и выход (п-1) элемента ИЛИ группы являются выходами устройства. На чертеже представлена схема устройства для извлечения квадратного корня для случая, когда . Устройство содержит одноразрядные сумматорь I, сумматоры 2 по модулю два, элементы ИЛИ 3, элементы НЕ 4, дополнительные сумматоры 5 по модулю два, элементы И 6, генера1тор 7 единиц. Работа предлагаемого устройства для конкретного значения У,430664062 5 или в разрядной форме У-Го 1 1 О 1 1 1 О О ll происходит следующим образом. При подаче значения вектора У на вход устройства и после окончания переходного процесса в схеме на выходе четвертого элемента ИЛИ 3 группы образуются значения старшего разряда искомого вектора X, л 1. Далее на вход четвертой группы одноразрядных сумматоров 1 подаются вектор 01 1 Ij и соответственно вектор | О 1 1 Ц. Там реализуется сумма векторов. В результате на выходе четвертой группы одноразрядных сумматоров 1 образуется вектор 11 10 а на выходе переноса первого одноразрядного сумматора 1 - значение последующего разряда 0 вектора х Значение вектора fl О 1 1 1 | подается на вход третьей группы одноразрядных сумматоров I, на вторые входы которой с выходов третьей группы сумматорюв 5 по модулю два, третьего элемента НЕ 4 группы, третьего элемента И 6 группы и третьего сумматора 2 по модулю два группы подается значение вектора 011011 . В третьей группе одноразрядных сумматоров образуется вектор | О 0101 значение последующего разряда х 1 вектора X. Значение вектора |0 1 00 1 б поступает на вход второй группы одноразрядных сумматоров 1, на второй вход которой подается значение вектора )1 О 101 П. благодаря чему в третьей группе одноразрядных сумматоров 1 йбразуется значение вектора j 1 1 1 1 О 1} , а значение X-0. Далее значение вектора (l 1 1 О 1 ОП подается на вход первой группы одноразрядных сумматоров 1, на второй вход которой подается вектор ЩГО 1 1 О ij, благодаря чему в первой группе одноразрядных сумматрров 1 образуется значение младшего разряда. Х-1 искомого вектора л. Введение новых элементов - генератора единиц и (п-2) элемента И - и между элементами выгодно отличает предлагаемое устройство от известного, так как при новой структурной организации уменьшается количество необходимого электронного оборудования и увеличивается быстродействие устройства. Формула изобретения 1. Устройство для извлечения квадратного корня, содержащее (п-1) группу последовательно соедине1шых одноразрядных сумматоров, где п - разрядность выходного кода, группу сумма ор в по модулю два, группу элементов ИЛИ, группу элементов НЕ, (п-2) дополнительных группы из (п-1-1), где i - номер группы, сумматоров по модулю два в каждой гру-ппе. отличающееся тем, что, с целью упрощения устройства и увеличения быстродействия, в него введены генератор единицы и группа из (п-2) элементов И, каждая i-я груп па (, 2... п-1) одноразрядных сумматоров содержит (п+2Ч.) одноразрядных сумматоров, группы элементов ИЛИ, элементов НЕ содержат (п-1) элементов, группа сумматоров по модул два содержит (п-2) сумматоров по модулю дв причем выход каждого j-ro (... n-i+1) одно раэрядного сумматора (1-И)-ой группы соединен с первым входом (j-l)-ro одноразрядного сумматора i-ой группы, второй вход первого одноразрядного сумматора i-ой группы соединен с выходом переноса первого одноразрядного сумматора (i + 1)-ой группы, первыми входами i-ых элементов И, ИЛИ, сумматоров по модулю два групп и сумматоров по модулю два i. дополнительной группы, выходы которых соединены с вторыми входами j-ых (,.,.n-l) одноразрядных сумматоров i-ой группы, вторые входы j-ых (,... п-1--1) сумматоров по модулю два i-ой дополнительной группы соединены с выходами переноса первых одноразрядных сумматоров (п-i+l)-bix групп, выход i-ro элемента НЕ группы подключен к первому входу (n+l-1)-го одноразрядного сумматора i-ой группы, второй вход которого соединен с выходом i-ro элемента И группы, подключенного вторым входом к выходу переноса первого одноразрядного сумматора (1-2)-ой группы, первый вход (n+2-i)-ro одноразрядного сумматора i-ой группы подключен к выходу i-ro сумматора по модулю 1ша группы, подключенного вторым входом к выходу i-ro элемента ИЛИ группы, второй вход которого соединен с выходом (i+l)-ro элемента ИЛИ группы, выход (п-1)-го элемента ИЛИ которой соединен с первым входом первого сумматора по модулю два каждой i-ой дополнительной группы, входом (п-1)-го элемента НЕ группы и вторым входом (п-2)-го элемента ИЛИ группы, второй вход (п+2-i)-ro одноразрядного сумматора i-ой группы соединен с 2 i-ым разрядом входного кода устройства, (2i-I)й разряд которого подключен к третьему входу одноразрядного сумматора и входу i-ro элемента НЕ группы, 2п-й и (2п-1)-й разряд входного кода устройства подключены к входам (п-1)-го элемента ИЛИ грзшпы и к первым входам соответствен но первого и второго одноразрядного сумматора (п-1)-й группы, вторые входы которых соединены соответственно с выходом ()-ro элемента НЕ группы и генератора единиц, подключенного к первому входу третьего одноразрядного сумматора (п-1)-й группы, выходы переносов первых одноразрядных сумматоров и выход (п-1) элемента ИЛИ группы являются выходами устройства. Источники информацни, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 571807, кл. G 06 F 7/38, 1974. 2.Авторское свидетельство СССР по заявке № 2685734/18-24, 27.06.79 (прототип).

Авторы

Даты

1981-08-23—Публикация

1979-11-06—Подача