о со

со

О5

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения цифровых следящих систем кругового вра- щекУ1я.

Целью изобретения является повышение точности и быстродействия сие- темы.

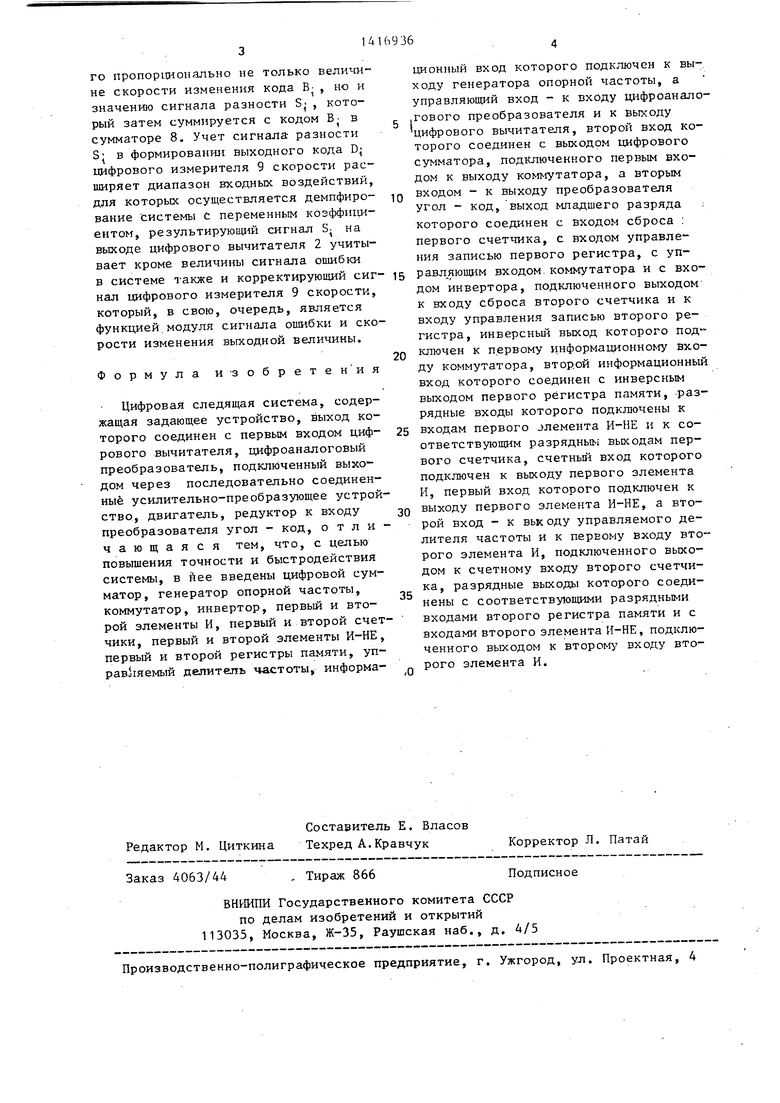

На чертеже изображена блок-схема системы.

Цифровая следящая система содержит: задающее устройство 1, цифровой вычитатель 2, цифроаналоговый преобразователь 3, усилительно-преобразу- ющее устройство 4, двигатель 5, редуктор 6р преобразователь 7 угол - код, цифровой сумматор 8, цифровой измеритель 9 скорости, генератор 10 опорной частоты, измерительные каналы 11, 12, коммутатор 13, инвертор 14, первый элемент И 15, первый счетчик 16, первый элемент И-НЕ 17, первый регистр 18 памяти, управляемый делитель 19, частоты, второй элемент И 20, второй счетчик 21, второй элемент И-НЕ 22, второй регистр 23 памяти.

Устройство работает следующим об- |разом.

Задающее устройство 1 вырабатывает управляющий сигнал А; в виде двоичного кода, который поступает на вход цифрового вычитателя 2, где из управляющего сигнала вычитается сиг-

нал

поступающий из преобразователя 7 угол - код, через сумматор 8 также в виде двоичного кода. Сигнал разности S;, полученный в цифровом вычитателе 2 по формуле

S; А;- В;,

поступает на вход цифроаь алогового преобразователя 3, где преобразуется в напряжение постоянного тока. Усилительно-преобразующее устройство 4 усиливает полученное напряжение до величины, необхо 1;имой для управления двигателем 5, который через редуктор 6 поворачивает преобразователь 7 угол - код на такой угол, при котором S; 0.

Кроме того, сигнал разности S, , поступая на управляющие входы управг ляемого делителя 19 частоты, изменяет его коэ нЬициент уашения, что приводит к регулированию (изменению) в функции сигнала ошибки частоты поступления импульсов на втором входе цифрового измерителя 9 скорости.

В режиме кругового слежения младший разряд двоичного кода обратной связи В; поступает в качестве управляющего на вход цифрового измерителя 9 скорости. При значениях младшего разряда сигнала В, соответствующего 1 в измерительном канале 11 осуществляется перевод счетчика 16 по входу сброса R в режим счета, регистра 18 памяти по входу управления записью в режим записи, а также подключение коммутатором 13 инверсных выходов регистра 23 памяти измерительного канала 12 к входам сумматора 8. Счетчик 16 измерительного канала 11 про- извоДит подсчет поступаюк их с выхода управляемого делителя 19 частоты прямоугольных импульсов за время присутствия управляющего сигнала 1. Число импульсов, накапливаемых в счетчике 16, определяется значением сигнала разности Sj (кода ошибки) и временем присутствия на входе цифрового измерителя 9 скорости сигнала 1 (скоростью изменения выходной величины) « Если при подсчете входных импульсов наступит полное заполнение счетчика срабатывает схема И-НК 17, выходной сигнал которой закрывает элемент И 15. Состояние же регистра 18 памяти соответствует текущему состоянию счетчика 16.

При значениях младшего разряда (сигнала В, соответствующего О, в измерительном канале 11 осуществляется перевод регистра 18 памяти по входу управления записью в режим памяти

сброс счетчика 16 по входу R в О и подключение коммутатором 13 инверсных выходов регистра 18 памяти измерительного канала 11 к входам сумматора 8.

Счетчик 21 измерительного канала 12 работает аналогично счетчику измерительного канала 11, подсчитывает входные импульсы только во время присутствия сигнала О в младшем разряде кода В;. Сигнал разрешения на работу счетчика 21 и запоминание его текущего состояния с помош зю регистра памяти 23 приходит с выхода инвертора 14. Работа измерительного канала 12 аналогична работе канала 11

Таким образом, на выходе коммутатора 13 всегда присутствует параллельный двоичный код Т), значение которого пропорционально не только величине скорости изменения кода В-, но и значению сигнала разности S , который затем суммируется с кодом В- в сумматоре 8. Учет сигнала разности Sj в формировании выходного кода DJ цифрового измерителя 9 скорости расширяет диапазон входных воздействий, для которых осуществляется демпфирование системы с переменным козффида- ентом, результирующий сигнал S на выходе цифрового вычитателя 2 учитывает кроме величины сигнала ошибки в системе также и корректирующий сиг нал цифрового измерителя 9 скорости, который, в свою, очередь, является функцией,модуля сигнала ошибки и скорости изменения вьпсодной величины.

Формула И зобретен ия

Цифровая следящая система, содержащая задающее устройство, выход которого соединен с первым входом цифрового вычитателя, цифроаналоговый преобразователь, подключенный выходом через последовательно соединенные усилительно-преобразующее устройство, двигатель, редуктор к входу преобра13ователя угол - код, отличающаяся тем, что, с целью повышения точности и быстродействия системы, в йее введены цифровой сумматор, генератор опорной частоты, коммутатор, инвертор, первый и второй элементы И, первый и второй счетчики, первый и второй элементы И-НЕ, первый и второй регистры памяти, уп- рав5шемый делитель частоты, информа5 I

10

15

20

25

30

35

-О

ционный вход которого подключен к выходу генератора опорной частоты, а управляющий вход - к входу дифроанало- гового преобразователя и к выходу цифрового вычитателя, второй вход которого соединен с выходом цифрового сумматора, подключенного первым входом к выходу коммутатора, а вторым входом - к выходу преобразователя угол - код, выход младшего разряда которого соединен с входом сброса : первого счетчика, с входом управления записью первого регистра, с уп- равл яюшим входом, коммутатора и с входом инвертора, подключенного выходом к входу сброса второго счетчика и к входу управления записью второго регистра, инверсный выход которого подключен к первому информационному входу коммутатора, второй информационный вход которого соединен с инверсным выходом первого регистра памяти, разрядные входы которого подключены к входам первого элемента И-НЕ и к со- oTBeTCTBymmjiM разрядным выходам первого счетчика, счетньи вход которого подключен к выходу первого элемента И, первый вход которого подключен к выходу первого элемента И-НЕ, а второй вход - к вьк оду управляемого делителя частоты и к первому входу второго элемента И, подключенного выходом к счетному входу второго счетчика, разрядные выходы которого соединены с соответствующими разрядными входами второго регистра памяти и с входами второго элемента И-НЕ, подключенного выходом к BTopoNfi входу второго элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВАЯ СЛЕДЯЩАЯ СИСТЕМА | 1991 |

|

RU2018899C1 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2105410C1 |

| ИМИТАТОР УГЛА ПОВОРОТА АНТЕННЫ РЛС | 1987 |

|

SU1841003A1 |

| Преобразователь угловых перемещений в код | 1985 |

|

SU1311024A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Установка для присоединения проволочных выводов | 1988 |

|

SU1549698A1 |

| Двухотсчетный следящий привод | 1989 |

|

SU1700535A1 |

| Цифровая следящая система | 1990 |

|

SU1833835A1 |

| Цифровая следящая система | 1990 |

|

SU1835533A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения цифровых следящих систем кругового вращения. Целью изобретения является повышение точности и быстродействия iсистемы. Система содержит задающее устройство 1, цифровой вычитатель 2, цифроаналоговый преобразователь 3, усилительно-преобразующе:: устройство 4, двигатель 5, редуктор 6, преобразователь 7 угол - код, цифровой сумматор 8, цифровой измеритель 9 скорости, генератор 10 опорной частоты, элементы И 15, 20, счетчики 16, 21, элементы И-НЕ 17, 22, регистры 18, .23 памяти, коммутатор 13, инвертор 14. В системе в дополнение к сигналу ошибки вырабатывается дополнительное регулирующее воздействие, являющееся функцией модуля сигнала ошибки и скорости изменения выходной величины. 1 кл. (О (Л

| Теория автоматического управления/Под ред | |||

| Нетунила | |||

| М.: Высшая школа, 1976, с | |||

| ПЕРЕДВИЖНАЯ ДИАГРАММА ДЛЯ СРАВНЕНИЯ ЦЕННОСТИ РАЗЛИЧНЫХ ПРОДУКТОВ ПО ИХ КАЛОРИЙНОСТИ | 1919 |

|

SU285A1 |

| Цифровая следящая система | 1983 |

|

SU1149216A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-08-15—Публикация

1986-12-01—Подача