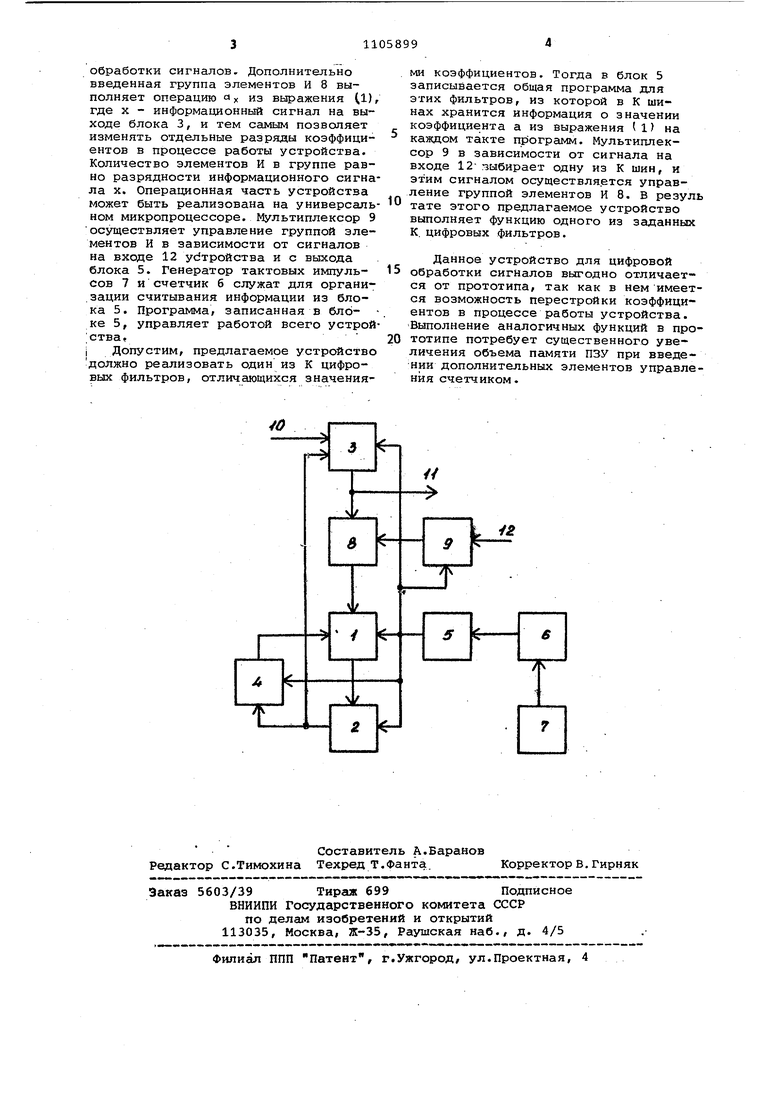

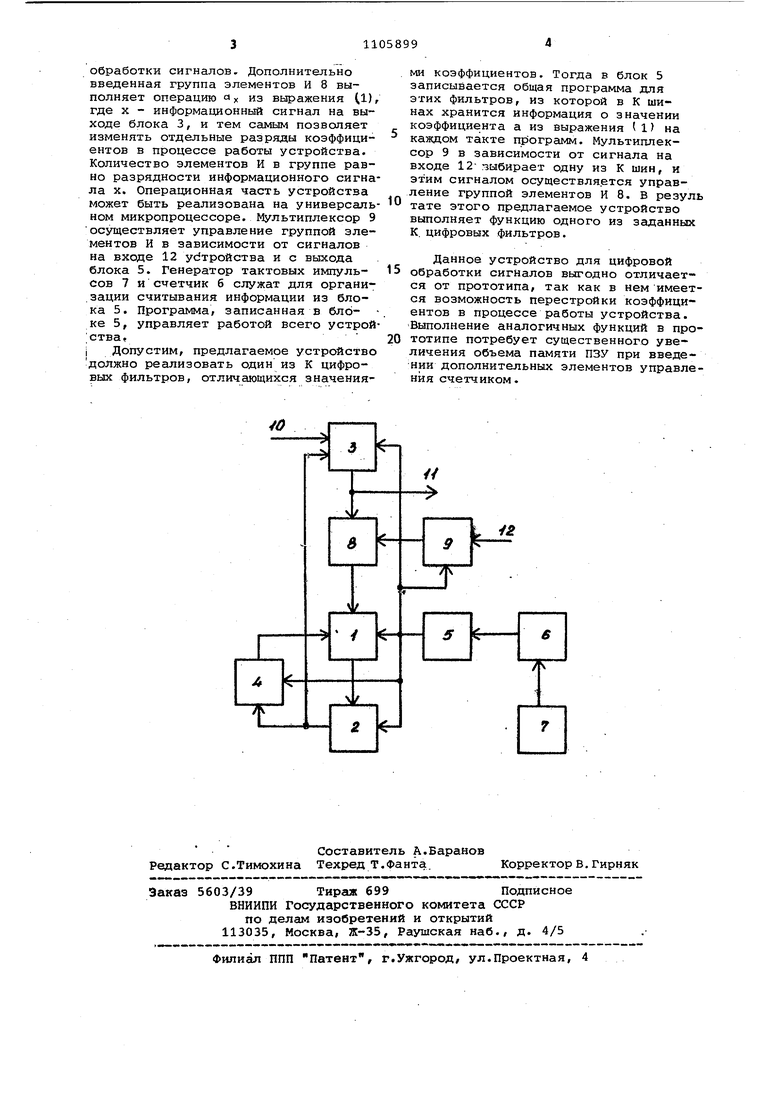

Изобретение относится к вычиели.тельной технике и может быть исполь зовано в системах обработки и передачи дискретной информации, радиои гидролокации, медицинской и другой аппаратуре, где используются ци ровая фильтрация и спектральный ана лиз. Известно устройство для цифровой обработки сигналов, содержащее арифметико-логическое устройство (АЛУ), оперативное и постоянное запоминающие устройства ОЗУ и ПЗУ), умножитеЛь параллельного типа и буферное устройство, входы АЛУ общей шиной соединены с выходами ОЗУ, буферного устройства и умножителя, а выходы ПЗУ соединены с управляющиг/ш входами ОЗУ, умножителя и АЛУ Cl Недостатком такого устройства являются большие аппаратные затраты связанные с использованием умножите ля параллельного типа, а также нево можность перестройки устройства в процессе работы. Наиболее близким по технической сущности к данному изобретению явля ется устройство для цифровой обрабо ки сигналов, содержащее сумматор-выч татель, сдвигатель, ОЗУ, регистры, ПЗУ, счетчик и генератор импульсов, причем один выход ОЗУ непосредственно связан с одним из входов сумматора-вычитателя, а второй выход ОЗУ связан со входом сумматора-вычитателя через сдвигатель, выход сумматора вычитателя через регистр подключен ко входу ОЗУ 2J. Сложность этого устройства невелика, так как операция умножения реа лизуется программным путем в виде сложений (вычитаний) и сдвигов. Одна ко указанное устройство может реализ вать только алгоритмы цифровой обработки с постоянными коэффициентами, так как программа жестко записана в ПЗУ и циклически повторяется по ме ре поступления входных сигналов. Это Hi позволяет использовать такое устройство для реализации цировых фильт ров с переменными коэффициентами или для реализации алгоритмов быстрого преобразования Фурье (БПФ) с разбие нием на одинаковые подпрограммы. Так например,, при реализации N-Точёчного алгоритма БПФ IN 2) на основе двухточечных преобразований используется N/2 различных типов преобразований, каждое из которых потребует отдельной пoдпpoгpaм lы. Целью изобретения является расши рение функциональ 5ых возможностей устройства за счет перестройки коэффициентов в процессе работы при реализации алгоритмов цифровой обработ ки сигналов. Поставленная цель достигается тем, что в устройство для цировой обработки сигналов, содержащее генератор тактовых импульсов, выход которого подключен к счетн.ому входу счетчика, информационный выход которого соединен с адресным входом блока постоянной памяти, выход которого подключен к управляющему входу блока памяти, управляющему входу сумматора-вычитателя, управляющему входу сдвигового регистра и тактовому входу регистра, информационный выход которого соединен с информационным входом блока памяти и информационным входом сдви.рового регистра, информационный выход которого подключен к первому информационному входу сумматора-вычитателя, информационный выход которого соединен с информационным входом регистра, а информационный вход и информационный выход блока памяти являются соответственно информационными входом и выходом устройства, введены группа элементов И и мультиплексор, информационный выход которого подключен к первым входам элементов И группы, вторые входы которых соответственно соединены с разр5щами информационного ввдхода блока памяти, выходы элементов И группы соответственно .соединены с разрядами второго информационного входа сумматора-вы-. читателя, выход блока постоянной памяти подключен к управляющему входу мультиплексора, информационный вход которого является входом задания режима работы устройства. На чертеже изображена структурная схема устройства для цифровой обработки сигналов. Устройство содержит сумматор-вычитатель 1, регистр 2, блок памяти 3, сдвиговый регистр 4, блок постоянной памяти 5, счетчик б, генератор тактовых импульсов 7, группу элементов И 8, мультиплексор 9, информационные вход 10 и выход 11, вход задания режима работы 12. Устройство работает следующим образ ом. в данном устройстве можно выделить две части: операционную и управляющую. В состав операционной части входят сумматор-вычитатель 1, регистр 2, блок 3, сдвиговый регистр 4, группа элементов И 8, а в состав управляющей - генератор тактовьах импульсов 7, счетчик 6, блок 5 и мультиплексор 9. Операционная часть предназначена для многократной реализации выражения:У У . t а . X ,И где - , 7 - информационные цифровые сигналы, а, feef0,1J. С помощъю этого выражения можно реализовать лкг&сйг алгориттл цифровой

обработки сигналов. Дополнительно введенная группа элементов И 8 выполняет операцию «х из выражения (1), где X - информационный сигнал на выходе блока 3, и тем самым позволяет изменять отдельные разряды коэффициентов в процессе работы устройства. Количество элементов И в группе равно разрядности информационного сигнала X. Операционная часть устройства может быть реализована на универсальном микропроцессоре. Мультиплексор 9

осуществляет управление группой элементов И в зависимости от сигналов на вхсэде 12 ус тройства и с выхода блока 5. Генератор тактовых импульсов 7 и счетчик б служат для органи.зации считывания информации из блока 5. Программа, записанная в блоке 5, управляет работой всего устрой;ства.

i Допустим, предлагаемое устройство

должно реализовать один из К цифровых фильтров, отличающихся значениями коэффициентов. Тогда в блок 5 записывается общая программа для этих фильтров, из которой в К шинах хранится информация о значении коэффициента а из выражения (1) на каждом такте программ. Мультиплексор 9 в зависимости от сигнала на входе 12-выбирает одну из К шин, и этим сигналом осуществляется управление группой элементов И В. В резул тате этого предлагаемое устройство выполняет функцию одного из заданных К. цифровых фильтров.

Данное устройство для цифровой обработки сигналов выгодно отличается от прототипа, так как в нем имеется возможность перестройки коэффициентов в процессе работы устройства. Выполнение аналогичных функций в прототипе потребует существенного увеичения объема памяти ПЗУ при введении дополнительных элементов управления счетчиком.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Процессор быстрых дискретных преобразований | 1989 |

|

SU1725227A1 |

| ПРОЦЕССОР С МАКСИМАЛЬНО ВОЗМОЖНОЙ ПРОИЗВОДИТЕЛЬНОСТЬЮ ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2005 |

|

RU2290687C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Фазометр | 1991 |

|

SU1817037A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для определения среднеквадратического значения переменного сигнала | 1989 |

|

SU1781686A1 |

УСТРОИСТЮ ДЛЯ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ, содержащее генератор тактовых импульсов, выход кото рого подключен к счетному входу счетчика, информационный выход которого соединен с адресным входом блока постоянной памяти, выход которого подключен к управляющему входу блока ,памяти, управляющему входу сумматора-вычитателя, управляющему входу сдвигового регистра и тактовому входу регистра, информационный выход которого соединен с информационным вЯодом блока памяти и информационным входом сдвигового регистра, информационный выход которого подключен к первому информационному входу сумматора-вьлчитателя, информационный выход которого соединен с информационным входом регистра, а информационный вход и информационный выход блока памяти являются соответственно информационнь 1И входом и выходом устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет перест ройки коэффициентов, в него введеi ны группа элементов И и мультиплексор, информационный выход которого (О подключен к первым входам элементов И группы, вторые входы которых соответственно соединены с разрядами информационного выхода блока памяти, выходы элементов И группы соответственно соединены с разрядами второго информационного входа сумматоравычитателя, выход блока постоянной памяти подключен к управляющему входу мультиплексора, информационный сд вход которого является входом задания режима работы устройства. 00 со ;о

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| D.M.Bell, L.E.Hand | |||

| А micro | |||

| siRnal Processing Module, IEEE Proceeding, | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| M, Townseiad, M | |||

| Hoff, P | |||

| Holm An WMOS microprocessor for analog signal processing, IEEE Traqs | |||

| on computer, vol.C-29, I 2, February,1980 (прототип). | |||

Авторы

Даты

1984-07-30—Публикация

1983-05-24—Подача