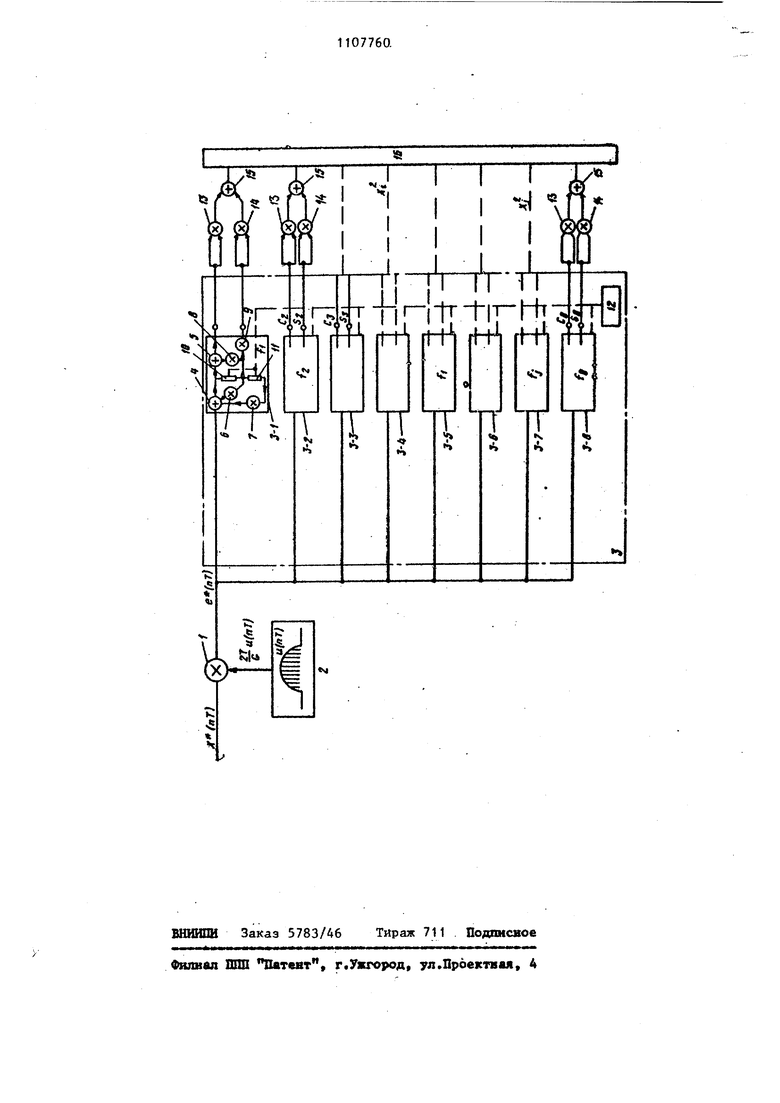

11 Изобретение относится к анализато рам, которые позволяют измерять спек ральную плотность энергии или амплитуду составляющих спектра дискретных сигналов, предстарзленных в виде числевой последовательности х (пТ), гд® Т период дискретизации, п - ранг дискрета. Известны устройства для измерения спектральной плотности энергии, кото рые содержат умножитель свертки, пер вый вход которого является входом устройства, 3 второй вход соединен с блоком памяти окна вевешивания, причем выход умножителя свертки соедине с ГцИфровым фильтром, квадратичный интегратор и преобразователь -фурье, логичесзсий решающий блок ,1}. Недостатками устройства являются схемная сложность и ограниченность анализа частотами, кратными I/NT, где N длительность сигнала. Целью изобретения является повы-шение быстродействия анализа при одн временном уменьшении схемных затрат. Поставленная цель достигается за счет того, что в устройстве цифрового анализа спектра сигнала, квантова ного по частоте и кодированного для распознавания нескольких особых частот, содержащем умножитель свертки, первьШ вход которого является входом устройства, а второй вход соединен с блоком памяти окна взвешивания, причем выход умножителя свертки соединен с цифровым фильтром, логический решающий блок, цифровой фильтр выполнен в виде цифровых идеальных резонаторов, число которых равно числу распознаваемых частот, причем каждый из цифровых резонаторов содержит пер вый сумматор, первый вход которого является входом резонатора, а выход соединен с входом двух последователь но включенных блоков задержки, причем выход первого блока задержки сое динен через блок умножения на (2cos 2nfрТ)5 .где fp- частота настройки рассматриваемого резонатора, п - шаг дискрета, Т - период дискретизации, с вторым входом первого сумматора, вькод второго блока задержки соединен через блок умножения на (-1) с третьим входом первого сумматора, выход первого сумматора также соединен с первым входом второго сумматора, выход которого составляет выход действительной части амплитуды сигнала, на частоту которого настроен 0 рассматриваемый резонатор, в.ыхол первого блока задержки также соединен с одной стороны с блоком умножения на (-COS 2п fpT}, выход которого соединен с вторым входом второго сумматора, и с другой стороны - с блоком умножения на (sinZnfpT), выход которого составляет выход мнимой части амплитуды сигнала, выход умножителя свертки подключен к входам всех идеальньрс резонаторов, а входы обоих блоков задержки каждого резонатора соединены со средством сброса в , причем выходы действительной части и мнимой частей амплитуды сигнала каждого резонатора подключены каждьй к двум входам умножителя, выходы которых соединены с входами третьего сумматора, при этом выходы всех третьих сумматоров соединены с логическим решающим блоком. Не чертеже представлена структурная схема цифрового анализа. Устройство содержит умножитель 1 свертки, подключенный к блоку 2 памяти окна взвешивания, выход умножителя 1 соединен С цифровым фильтром 3, которьй состоит из ряда идеальных резонаторов 3-1тЗ-8. Каждый идеальньй резонатор, например первый, состоит из первого 4 и второго 5 сумматоров, первого блока 6 умножения на (2cos 2nfрТ), блока 7 умножения на (-1),блока 8 умножения на (-cos 2п f Т), блока 9 умножения на (sin 2п fpT) и двух блоков 10 и 11 задержки, котогрые соединены со средством 12 сброса в О. В состав анализатора входят также умножители 13 и 14, третьи сумматоры 15 и логический решающий блок 16. Устройство работает следующим образом. Входной сигнал х (+) после дискретизации, квантования и кодирования принимает вид х(пТ) и поступает На умножитель 1 свертки, в котором этот сигнал умножается на ампли2Ттуды --- и(пТ) окна ограничения, записанные в блоке 2 памяти. Сигнал и(пТ) является нулевым вне интервала , где G - максимальная амплитуда преобразования величины U(nT). Сигналы е(пТ), выходящие из умножителя 1 свертки, обрабатываются цифровым фильтром 3, состоящим из восьми идеальных резонаторов 3-173-8 с двумя вьрсодами С и S. Эти резонаторы включены параллельно и казвдый настроен на одну из восьми частот рассматриваемого кода. Выходы С и S каждого резонатора соединены с умножителями 1-3 и 14. Выходы каждой пары умножителей подключены к сумматорам 15.

Выходы сумматоров 15 содержат искомые величины и X. после, проме жутка времениE NT, за которым следу ет появление первого показательного дискрета на входе умножителя 1. Выхо других сумматоров могут также содержать данные заметно более слабых уровней, чем X и X, Речь особенно Идет о различных помехах, связанных с гармониками nf- и nf: , сигналов кода. В самом деле, в дискретизированном спектре появляются частоты nfjimFe; nfjjmFe, которые могут быт равными другой частоте Кода или быть соседними. Однако вследствие компенсации системы уровень этих помех по отношению к X и Х не может быть большим уровня гармоник nf- и п f- в передаваемом сигнале, таком как определенный в спецификациях различных систем многочастотных кодов (Кг М.Ф.Сокотель, клавир).

Логический решающий блок 16 позволяет классифицировать уровни Х, X,,

..., сравнивать их и решать, принадлежат ли они к коду Б соответствии со с пе цифика ция ми.

Измерение X и X- получают после истечения времени . Обычные средства, подключенные в основном к блоку 8, должны быть предусмотрены, чтобы вернуть в начальное состояние блоки задержки резонаторов 3-143-8, когда . Те же средства должны обеспечить повторное открытие окна ограничения, которое йакрьгеается после прохождения N дискретов, следовательно после времени .f. Выбор момента времени возврата в начальное положение остается на усмотрении пользователя, так как в принципе X. и ХЯ не изменяются после времени NT.

По отношению к известным устройствам предлагаемый анализатор позволяет Сэкономить большое число фильтров и блок памяти со схемами управления за счет непосредственного подключения умножителя свертки окна взвешивания с входами резонаторов. Кроме того, скорость анализа в устройстве значительно вьше благодаря прим неНию в цифровом фильтре идеальных резонаторов со сбросом на ноль схем задержки.

/«S1 vS I

I I I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифровой пространственно-временной фильтрации телевизионного сигнала изображения | 1989 |

|

SU1646074A1 |

| Нерекурсивный цифровой фильтр-дециматор | 1986 |

|

SU1354394A1 |

| Цифровой фильтр | 1975 |

|

SU636616A1 |

| Цифровой резонатор | 1979 |

|

SU796853A1 |

| Устройство для преобразования виртуального адреса в реальный адрес | 1979 |

|

SU1162377A3 |

| Цифровой нерекурсивный фильтр | 1974 |

|

SU516043A1 |

| Нерекурсивный цифровой фильтр | 1983 |

|

SU1171994A1 |

| Цифровой формирователь сигнала с линейной частотной модуляцией | 1982 |

|

SU1099407A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1774464A1 |

УСТРОЙСТВО ЦИФРОВОГО АНАЛИЗА СПЕКТРА СИГНАЛА, КВАНТОВАННОГО ПО ЧАСТОТЕ И КОДИРОВАННОГО ДЛЯ РАСПОЗНАВАНИЯ НЕСКОЛЬКИХ ОСОБЫХ ЧАСТОТ, содержащее умножитель свертки, первый вход которого является свходом устройства, а второй вход соединен с блоком памяти окна взвешивания, причем выход умножителя свертки соединен с цифровым фильтром, логический решающий блок, отличающееся тем, что, с целью повышения быстродействия при одновременном уменьшении схемных затрат, цифровой-фильтр выполнен в виде цифровых идеальных резонаторов, число которых равно числу распознаваемых частот, причем каждый из цифровых резонаторов состоит из первого сумматора, первый вход которого является входом резонатора, а выход соединен с входом двух последовательно соединенных блоков задержки, причем выход первого блока задержки соединен через блок умножения на

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| I.Max | |||

| Methodes et techiques de traitement du signal et application aux mesures physiques | |||

| Изд | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1984-08-07—Публикация

1979-04-23—Подача