(Л

СО

о

О5

(,

Ьлок 4 вычитания импульсов, счетчик 5 импульсоп, первый регистр 6 памяти, nepubiii пычитающиГ) счетчик 7, формирователь 8 1мпульсов, триггер 10, пер- яый сумматор 11, второй регистр 12

памяти, второй вычитаюии-1й счетчик 13, первый и второй элементы 14 и 16 задержки, третий регистр 17 памяти, второй сумматор и входную и выходную шины 9 и 15. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1985 |

|

SU1305822A1 |

| Дискретный умножитель частоты | 1985 |

|

SU1337988A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Умножитель частоты | 1988 |

|

SU1562908A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU898600A1 |

| Умножитель частоты | 1987 |

|

SU1499341A1 |

| Цифровой умножитель частоты следования импульсов | 1980 |

|

SU1013952A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Умножитель частоты | 1984 |

|

SU1238070A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705657A1 |

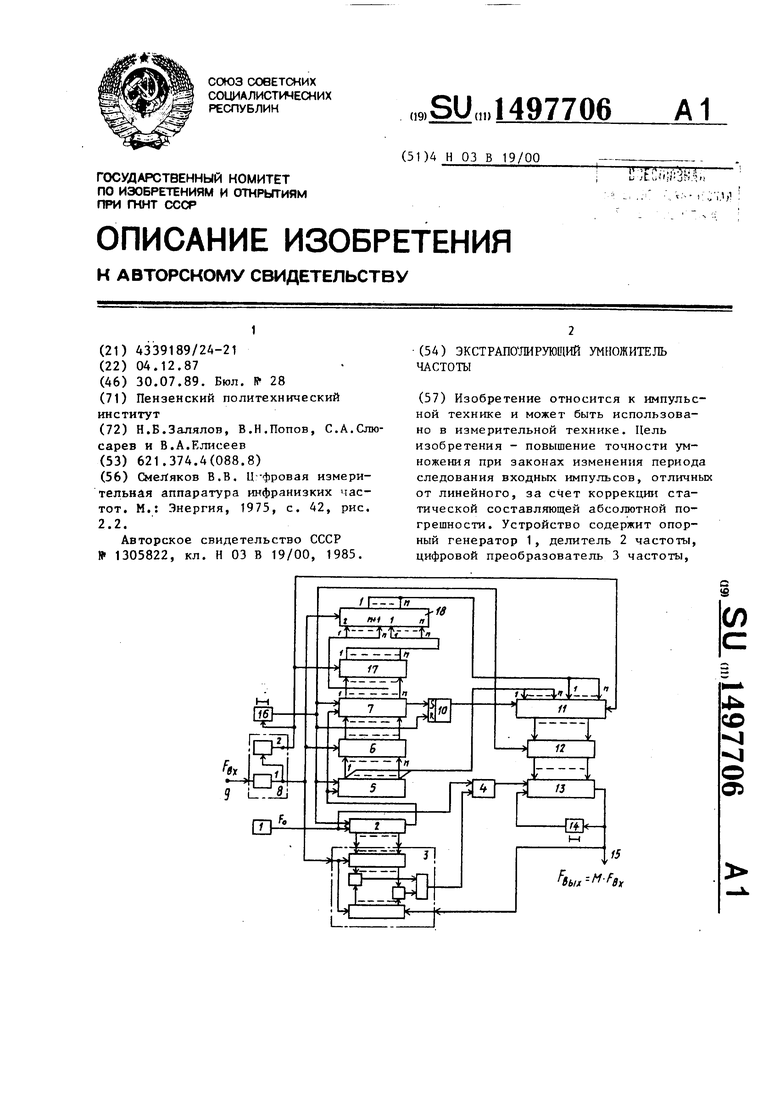

Изобретение относится к импульсной технике и может быть использовано в измерительной технике. Целью изобретения является повышение точности умножения при законах изменения периода следования входных импульсов, отличных от линейного, за счет коррекции статической составляющей абсолютной погрешности. Устройство содержит опорный генератор 1, делитель 2 частоты, цифровой преобразователь 3 частоты, блок 4 вычитания импульсов, счетчик 5 импульсов, первый регистр 6 памяти, первый вычитающий счетчик 7, формирователь 8 импульсов, триггер 10, первый сумматор 11, второй регистр 12 памяти, второй вычитающий счетчик 13, первый и второй элементы 14 и 16 задержки, третий регистр 17 памяти, второй сумматор и входную и выходную шины 9 и 15. 1 ил.

Изобретение относится к импульсной технике и может быть использовано в измерительной техн ике.

Цель изобретения - повышение точности умножения при законах измене- НИН периода следования входных импульсов, отличных от линейного за счет коррекции статической составляющей абсолютной погрешности.

На чертеже представлена структур- ная ;)лектрпческая схема устройства.

Устройство содержит опорный генератор 1, выход которого соединен с тактовым входом делителя 2 частоты, информационные выходы которого сое- динены с информадионными входами циф- IJOBoro преобразователя 3 частоты, выход которого соединен с первым входом блока 4 вычитания импульсов, второй вход которого соединен с выходом опор ного генератора 1, счетчик 5, первый регистр 6 памяти, информационные входы которого соединены с информационными выходами счетчика 5, первый вычитающий счетчик 7, 1шформацион11Ь1е входы которого соединены с информационными выходами первого регистра 6 памяти, счетный вход - со счетным входом счетчика 5 и выходом делителя 2 частот, формирователь 8 1-1мпульсов, вход к iTOporo соединен с входной ьта- ной 9 /стройства, а первый его выход- с упраляющим входом цифрового преоб- разова /еля 3 частоты, триггер 10, S-вход которого соединен с выходом первого вычитающего счетчика 7, первый сумматор 11, знаковый вход которого cof. с выходом триггера 10, первая группа ei o информационных входов соединена с информационными вы- ходами счетчика 5, второй регистр 12 памяти, информационные входы которого соединены с информационными выходами первого сумматора 11, второй вычитающий счетчик 13, информационные входы которого соединены с информационными выходами второго регистра 12 памяти, его счетный вход соединен с выходом блока 4 вычитания импульсов, первый элемент 14 задержки, вход которого соединен с выходом второго вычитающего счетчика 13, со счетным входом цифрового преобразователя 3 частоты и выходной шиной 15 устройства, а выход - с входом началь HOii установки второго вычитающего счетчика 13, в.торой элемент 16 задержки, вход которого соединен с вторым выходом формирователя 8 импульсов, третий регистр 17 памяти, информационные входы которого соединены с ин- формационнь1ми БЫХО ;ами первого вычитающего счетчика 7, второй сумматор 18, первая группа информационных входов которого соединена с информационными выходами первого в,rчитaющeгo счетчика 7, вторая группа информационных входоь - с ииформационныгш выходами третьего регистра 17 памяти, информационные его выходы соединены с второй группой информационных входов первого сумматора 11, управляющий Бход которого соединен с входом записи третьего регистра 17 памяти и вторым выходом формирователя 8 импульсов , первый выход которого соединен с управляющим входом второго сумматора 18, выход второго элемен- . та 16 задержки соединен с входом записи второго рех истра 12 памяти, с R-входами делителя 2 частоты, счетчика 5 и триггера 10 и с входом начальной установки первого вычитающего счетчика 7.

Принцип действия экстраполирующего умножителя частоты заключается в следующем .

Для экстраполяции периода умножени используется кроме конечной разности первого порядка 4Tj Т;,,-Т конечная разность второго порядка 4 Т ; JTj - /ST., где экстраполируемый период умножения определяется выражением

Tui + aTi4i +й,

которое после подстановки приводится к виду

т

Т,,,,.,,- Т;.

Из этого соотношения видно, что каждый четвертый период определяется по значениям трех ). Если использовать запись в виде кодов, чт соответствует цифровому принципу работы умножителя, то код, экстраполирующий текущее значение периода, определяется выражением

Nf.a N,v,±(2/1N,.,,,),

где знак плюс соответствует возраста20

ющему монотонному закону изменения периода входной частоты, а знак минус - убывающему.

Это соо- юшение справедливо только при монотонных законах изменения частоты, при которых совпадают знаки первой и второй конечных разностей. Поэтому в предлагаемом умножителе определяется знак только первой конечной разности.

Устройство работает следующим образом.

Входной сигнал в виде последовательности импульсов (т. - период следования импульсов) поступает на вход формирователя 8. По йронту входного сигнала на первом выходе формировате- 30 ля 8 вырабатывается короткий импульс, по окончании которого короткий импульс вырабатывается на его втором выходе.

С второго выхода формирователя 8 короткий импульс поступает на вход второго элемента 16 задержки, время задержки которого выбирается таким образом, чтобы на его выходе появился короткий импульс по окончании им- 40 пульса с второго выхода формирователя 8.

Таким образом, на выходах формирователя 8 и второго элемента 16 заПо импульсу с второго выхода формирователя 8 информация с разрядных выходов первого вычитающего счетчика 7 записывается в третий регистр 17 памяти, одновременно в первом сумматор 11 выполняется операция суммирования двоичных кодов с выходов счетчика 5 и второго сумматора 18, которая осуществляется с учетом знака содержимого первого вычитающего счетчика 7 , который фиксируется в триггере 10.

По импульсу с второго элемента 16 задержки информации с разрядных выходов первого сумматора 11 записывается 25 во второй регистр 12 памяти, производится начальная установка первого ш- читающего счетчика 7, а делитель 2, счетчик 5 и триггер 10 устанавливаются в ноль.

Периодическая последовательность импульсов с периодом следования Т, с выхода опорного генератора 1 поступает на вход делителя 2 частоты, коэффициент деления которого М соответ- 22 ствует коэффициенту умножения умножителя. С выхода делителя 2 импульсная последовательность с периодом Tj Т,

., М поступает на счетные входы счетчика 5 и первого вычитающего счетчика 7. К моменту окончания периода Т ,чг на разрядных вьЕходах счетчика 5 значение двоичного кода равно

+7

/TO-M,

а на разрядных

Nl42 Т ;

выходах первого вычитающего счетчика

держки последовательно формируются со-ДЗ формируется разность кодов (конечная разность первого порядка) двух периодов (i+2)-ro и (1+1 )-го N , IN,- -N + 11. Знак результата вычисления N f+ фиксируется тригге- 50 ром 10. Код предыдущей разности двух периодов (i+1)-ro и i-ro 4N к этому времени хранится в третьем регистре 17 памяти.

За счет соответствующего соединеответствующие три импульса управления. Интервалы между импульсами на каждом из этих выходов соответствуют периоду входного сигнала Т|.

По импульсу с первого выхода формирователя 8 производится запись информации в цифровой преобразователь 3 частоты (с разрядных выходов делителя 2) и запись информации в первый регистр 6

памяти (с разрядных выходов счетчика 5), 55 разрядов на первую группу входов одновременно во втором сумматоре 18 второго сумматора 18 подается код выполняется операция вычитания из удвоенного двоичного кода с выходов первого вычитающего счетчика 7 (ум2iJN,, , а на вторую группу - N;. По соответствующему управляющему импуль су второй сумматор 18 производит one

о 5

10

20

30,

40

497706

ножение кода на два производится за счет соединения разрядных выходов первого вычитающего счетчика 7 с nepBoii группой входов второго сумматора 18 со сдвигом на один разряд в сторону старших разрядов) двоичного ьода с разрядных выходов третьего регистра 17 памяти.

По импульсу с второго выхода формирователя 8 информация с разрядных выходов первого вычитающего счетчика 7 записывается в третий регистр 17 памяти, одновременно в первом сумматор 11 выполняется операция суммирования двоичных кодов с выходов счетчика 5 и второго сумматора 18, которая осуществляется с учетом знака содержимого первого вычитающего счетчика 7 , который фиксируется в триггере 10.

По импульсу с второго элемента 16 задержки информации с разрядных выходов первого сумматора 11 записывается 25 во второй регистр 12 памяти, производится начальная установка первого ш- читающего счетчика 7, а делитель 2, счетчик 5 и триггер 10 устанавливаются в ноль.

Периодическая последовательность импульсов с периодом следования Т, с выхода опорного генератора 1 поступает на вход делителя 2 частоты, коэффициент деления которого М соответ- 22 ствует коэффициенту умножения умножителя. С выхода делителя 2 импульсная последовательность с периодом Tj Т,

., М поступает на счетные входы счетчика 5 и первого вычитающего счетчика 7. К моменту окончания периода Т ,чг на разрядных вьЕходах счетчика 5 значение двоичного кода равно

+7

/TO-M,

а на разрядных

Nl42 Т ;

выходах первого вычитающего счетчика

разрядов на первую группу входов второго сумматора 18 подается код

2iJN,, , а на вторую группу - N;. По соответствующему управляющему импульсу второй сумматор 18 производит oneрацик1 вычитания, формируя на своих выходах код 24N ,- ,-, что соответствует изменению длительности периода входного сигнала, В случае монотонного плавного изменения периода, включая и линейное изменение, входного сигнала учет 2JN,-, - AN- поз- во.аяет экстраполировать текущее значение периода.

N;..3 ,V,(,.,- 4N.).

Например, при линейном изменении

периода входного сигнала /: N; const, 15 вьгходного сигнала, поступающего на

следовательно, текущее значение периода экстраполируется значением кода

N

I - 3

N,

,t4M..

{ + 2 ЧТО соответствует экстраполяции, производимой в известном устройстве.

Операция суммирования и получения кода N ., производится первым сумматором 11 с приходом соответствующего управляющего импульса. Знак операции суммирования соответствует воз- растающим или убывающим законам изменения периода входных сигналов и задается триггером 10,

Скорректированный код н ; запоминается во втором регистре 12 памяти И поступает на входы второго вычитающего счетчика 13, 1-1мпульс с выхода последнего, который формируется при каждом переходе счетчика 13 через ноль, через первый элемент 14 задерж- ки поступает на вход начальной установки второго вычитающего счетчика 13 и осуществляет запись двоичного кода с вг ходов второго регистра 12 памяти р.. второй вычитающий счетчик 13,40 деляемой остатком кода 4М в делителе

На сч: ный вход второго вычитающего счетчиг.а 13 поступают импульсы с периодом следования Tj, с опорного генератора 1 через блок 4 вычитания импульсов, который совместно с цифровым преобразователем 3 частоты используются для коррекции статической составляющей абсолютной погрешности умножения, обусловленной эффектом квантования и определяемой значением кода 4М в делителе 2 частоты. При период следования импульсов на выходе второго вычитающего счетчика 13 равен

Т Т ьы о

NW

3

При К ; NI.,

TBI,X т,е.

Гби. F.-M

Если в конце периода входного си1- нала на разрядных выходах делителя 2 установлен код числа О АН М, то в экстраполирующем умножителе производится коррекция статической составляющей абсолютной погрешности умножения таким же образом, как и в известном устройстве.

Например, если коэффициент умножения М 64 и ЛМ 8, то каждый восьмой период следования импульсов увеличивается на Тд путем преобразования последовательности импульсов

0

5

О вход цифрового преобразователя 3 частоты, в последовательность из восьми импульсов (на интервале Т.), которые с выхода цифрово1 о преобразователя 3 частоты поступают на второй вход блока 4 и вычитают из периодической последовательности И1-1пульсов опорного генератора 1 каждый восьмой импульс. Данная операция соответствует увеличению периода следования каждого восьмого импульса на выходе экстраполирующего умножителя частоты на интервал Тр, Эта процедура обеспеч шает равномерную за интервал Т; коррекцию периодов следования выходных импульсов, что (как показывает анализ) уменьщает погрешность, обусловленную смс щением импульсов, до величины, не превышающей (Т,,,

Таким образом, в предлагаемом устройстве осуществляется коррекция статической составляющей абсолютной погрешности, обусловленной квантованием периода входного сигнала и опре

2, а также исключается составляющая динамической погрешности не только в случае линейного изменения периода входного сигнала, но и при любых других гладких монотонных законах его изменения. При этом результирующий сдвиг импульсов реальной последовательности на выходе экстраполирующего умножителя относительно импульсов идеальной последовательности не превышает по абсолютной величине период опорного сигнала (,

Формула изобретения

Экстраполирующий умножитель час- TOTbi, содержащий опорный генератор, выход которого соединен с тактовым входом делителя частоты, информационные выходы которого соединены с информационными входами цлфрового -преобразователя частоты, выход которого соединен с первым входом блока вычи- тания импульсов, второй вход которого соединен с выходом опорного генератора, счетчик, первый регистр памяти, информационные входы которого соединены с информационными выходами счетчика, первый вычитающий счетчик, информационные входы которого соеди- ены с информационными выходами первого регистра памяти, а счетный вход со счетным входом счетчика и выходом делителя частоты, формирователь импульсов, вход которого соединен с входной шиной устройства, а первый ег выход - с управляющим входом цифрового преобразователя частоты, триггер, S-БХОД которого соединен с выходом первого вычитающего счетчика, первый сумматор, знаковый вход которого соединен с выходом триггера, первая группа информационных входов - с информа- ционными выходами счетчика, второй регистр памяти, информационные входы которого соединены : информационными выходами первого сумматора, второй вычитающий счетчик, информационные входы которого соединены с информаци- онньп4и выходами второго регистра памяти, счетный вход - с выходом блока вычитания импульсов, первый элемент задержки, вход которого соединен с

Составитель О.Бодряшова Редактор М.Петрова Техред Л.Олийнык Корректор М.Пожо

Заказ 4455/54

Тираж 884

ВНИИПИ Государственнрго комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

выходом второго вычитающего счетчнкл, со счетньм входом гхифрового преобразователя частоты и выходной шинси устройства, а выход с входом начальной установки второго вычитающего счетчика, отличающийся тем, что, с цель:о повышения точности умножения частоты, в него введены второй ллемент задержки, вход которого соединен с вторым выходом формирователя импульсов, третий регистр памяти, информационные входы которого соединены с информа1Ц1онными выходами к первого вычитающего счетчика, второй сумматор, первая группа информационных входов которого соединена с информационными выходами первого вычитающего счетчика, вторая группа информационных входов соединена с информационными выходами третьего регистра памяти, информационные выходы - с второй группой информационных входов первого сумматора, управляющий вход которого соединен с входом записи третьего регистра памяти и третьим выходом формирователя импульсов, первый выход которого соединен с управляющим входом второго сумматора, выход второго элемента задержки соединен с входом записи второго регистра памяти, с R-входами делителя частоты, счетчика и триггера и входом начальной установки первого вычитающего счетчика.

Подписное

| СмеЛяков В.В | |||

| Ц фровая измерительная аппаратура инфранизких частот | |||

| М.: Энергия, 1975, с | |||

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Умножитель частоты | 1985 |

|

SU1305822A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-07-30—Публикация

1987-12-04—Подача