Адрес

Ut

(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С БЫСТРОЙ ПЕРЕСТРОЙКОЙ ЧАСТОТЫ | 2012 |

|

RU2491710C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1999 |

|

RU2149503C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1999 |

|

RU2143173C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204196C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204197C2 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР | 2005 |

|

RU2286645C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР СИГНАЛОВ | 2004 |

|

RU2257669C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2012 |

|

RU2490789C1 |

| Цифровой синтезатор частот с высокой линейностью закона изменения частоты | 2016 |

|

RU2635278C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С КВАДРАТУРНЫМИ ВЫХОДАМИ | 2005 |

|

RU2294054C1 |

Изобретение относится к электронной технике, предназначено для синтеза сигналов с линейно-частотной модуляцией и может быть использовано в радиолокации, широкополосных системах связи и зондирования ионосферы. Устройство содержит: два блока постоянного запоминания (1,4), накопитель (2), умножитель кодов (3), счетчик (5) с предварительной установкой, преобразователь кодов (6), регистр памяти (7), цифроаналоговый преобразователь (8), фильтр (9) нижних частот, генератор (10) тактовых импульсов, блок задержки (11). Все перечисленные блоки соединены следующим образом: 1-2-3-6-7-8-9. 11-2, , 11-3,11-7.10-11. Цель изобретения-повышение быстродействия - достигается при помощи введения умножителем кодов 3, преобразователя кодов 6, регистра памяти 7, блока постоянного запоминания 4 и счетчика 5 с предварительной установкой. 3 ил.

8

Ч

ч

t

о

Изобретение относится к электронной технике, предназначено для синтеза сигналов с линейно-частотной модуляцией и может быть использовано в радиолокации, широкополосных системах связи и зондирования ионосферы.

Наиболее близким техническим решением к предлагаемому является цифровой синтезатор частот, содержащий блок установки частоты, накопитель, генератор тактовых импульсов, блок задержки, первый преобразователь кодов, блок вычисления угловой коррекции, блок постоянного запоминания, умножитель кодов, первый регистр памяти, распределитель кодов, второй преобразователь кодов, сумматор, второй регистр памяти, цифрооналоговый преобразователь и фильтр нижних частот.

Однако такой синтезатор но обеспечивает достаточно высокого быстродействия. Целью изобрегения является повышение быстродействия. Поставленная цель достигается тем, что в цифровой синтезатор частот, содержащий последовательно соединенные генератор тактовых импульсов и блок задержки, последовательно соединенные регистр памяти, цифроаналоговый преобразователь и фильтр нижних частот, первый блок постоянного запоминания, умножитель кодов, преобразователь кодов, накопитель, тактовый вход которого соединен с первым отводом блока задержки, второй отвод которого соединен с тактовым входом регистра памяти, дополнительно введены последовательно соединенные второй блок постоянного запоминания и счетчик с предварительной установкой, тг.к- товый вход которого соединен с первым отводом блока задержки, третий отвод которого соединен со входом сигнала записи множимого умножителя кодов, вход сигнала записи множителя которого соединен с четвертым отводом блока задержки, пятый вывод блока задержки соединен со входом сигнала записи результата умножения умножителя кодов, вход множимого которого соединен с выходом накопителя, информационный вход которого соединен с выходом первого блока постоянного запоминания, а выход счетчика с предварительной установкой соединен со входом множителя умножи- теля кодов, выход сигнала старшего разряда которого соединен со входом сигнала старшего разряда преобразователя ко- дов, кодовый вход сигнала младших разрядов которого соединен с кодовым выходом сигналов младших разрядов умножителя кодов, выход преобразователя кодов соединен с информационным входом регистра памяти.

В разработанном техническом решении осуществляется непосредственное вычисление фазы синтезируемого ЧМ сигнала. Это позволяет исключить операции вычисления синуса и косинуса сигнала и обеспечить положительный эффект - повышение быстродействия.

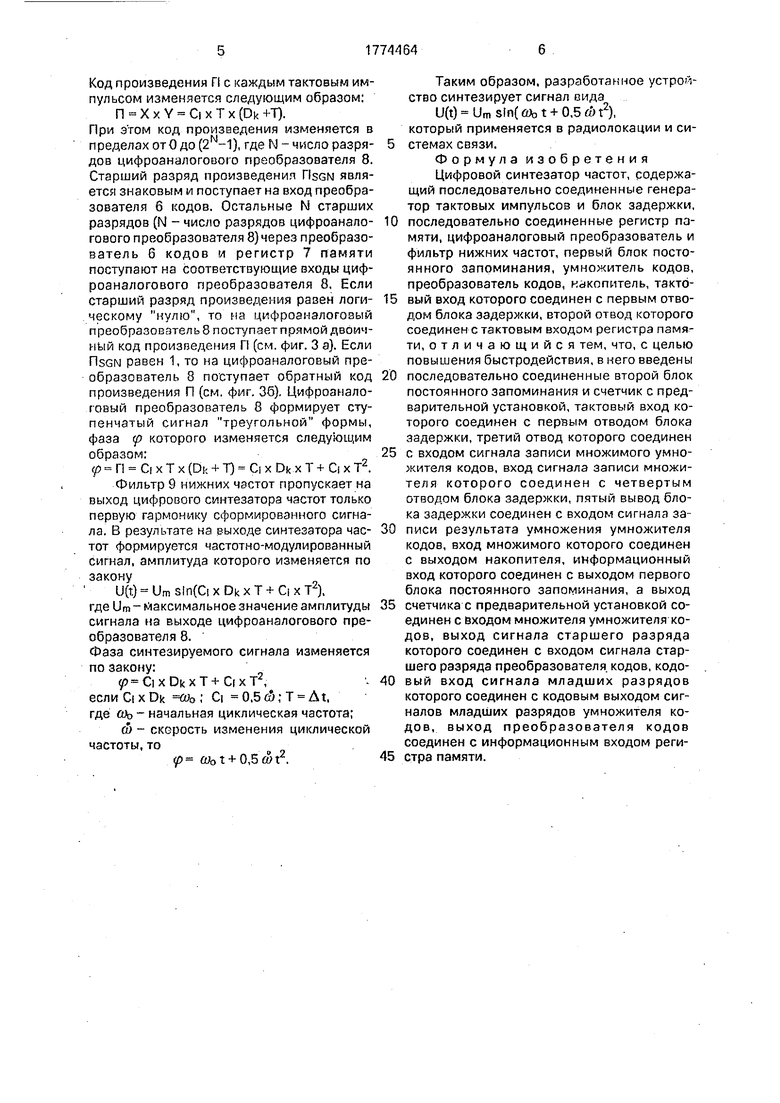

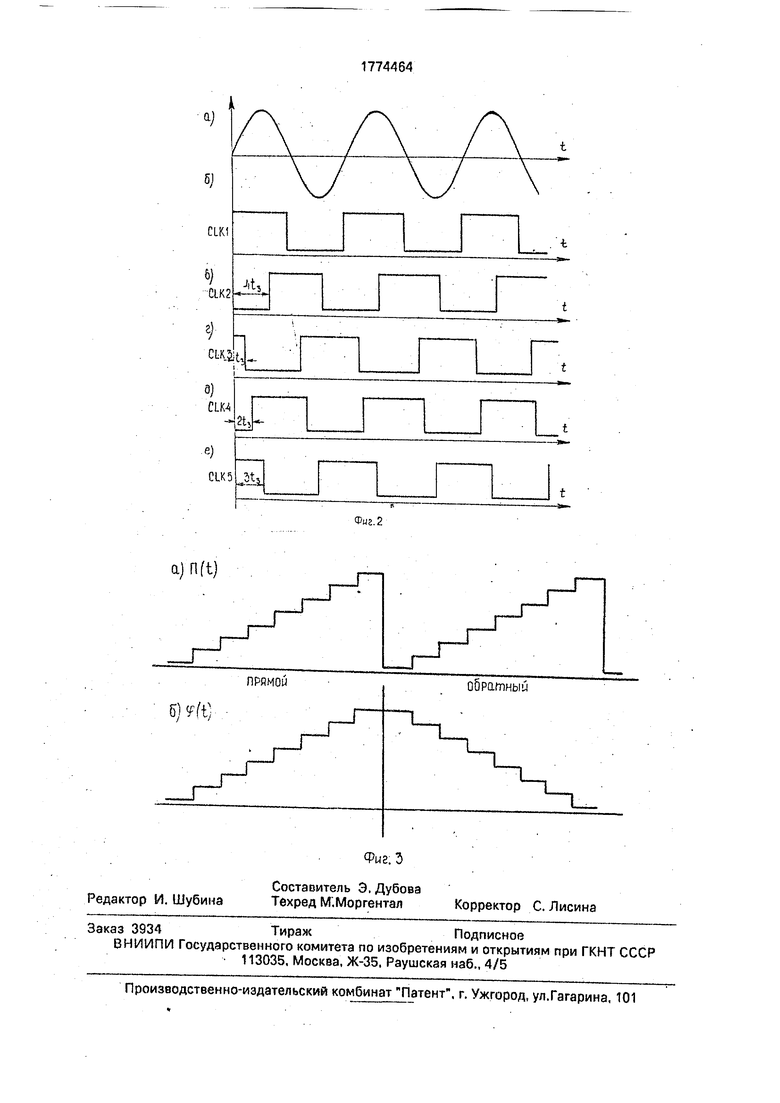

На фиг. 1 приведена структурная схема разработанного цифрового синтезатора ча0 стот; на фиг. 2а,б,в,г,д,е приведены, соответственно, эпюры на выходе генератора тактовых импульсов и на первом, втором, третьем, четвертом и пятом отводах блока задержки; на фиг. За приведена временная

5 диаграмма изменяющегося кода П на выходе умножителя кодов. На фиг. 36 приведена временная диаграмма изменяющегося кода фазы р на выходе регистра памяти.

Устройство по фиг, 1 содержит блок 1

0 постоянного запоминания, накопитель 2, умножигельЗ кодов, блок 4 постоянного запоминания, счетчик 5 с предварительной установкой, преобразователь 6 кодов, регистр 7 памяти, цифроаналоговый преобразова5 те ль 8, фильтр 9 нижних частот, генератор 10 тактовых импульсов и блок 11 задержки. Цифровой синтезатор частот работает следующим образом.

На адресные входы блоков 1,4 постоян0 ного запоминания поступают адреса выборки Ci, Dk, определяющие начальную частоту и скорость изменения частоты синтезируемого частотно-модулированного сигнала. Генератор 10 тактовых импульсов фор5 мирует синусоидальный сигнал опорной частоты f (см. фиг. 2 а). Блок 11 задержки осуществляет преобразование этого сигнала в тактовые импульсы типа меандр. За счет того, что последовательности тактовых

0 импульсов с выходов блока 11 задержки разнесены на время т.3эд, обеспечивается значительное снижение шумов переключе- ния накопителя 2, умножителя 3 кодов и счетчика 5 при неопределенных состояниях

5 на их выходах.

На выходе накопителя 2 результирующие значения чисел обновляются с частотой синхронизации f. Код числа X на выходах накопителя 2 изменяется следующим обра0 зом:

X Ci x Т.

где Т - номер тактового импульса (Т -0,1,2...).

Код числа Y на выходах счетчика 5 с

5 предварительной установкой изменяется следующим образом: Y Dk + T.

Умножитель 3 осуществляет перемножение кодов X - множимое MY- множитель.

Код произведения П с каждым тактовым импульсом изменяется следующим образом:

П X х Y Ci х Т х (Dk +T). При этом код произведения изменяется в пределах от0 до (2N-1), где N - число разрядов цифроаналоговою преобразователя 8. Старший разряд произведения PIsGN является знаковым и поступает на вход преобразователя б кодов. Остальные N старших разрядов (N - число разрядов цифроанало- гового преобразователя 8)через преобразователь б кодов и регистр 7 памяти поступают на соответствующие входы циф- роаналогового преобразователя 8, Если старший разряд произведения равен логическому нулю, то на цифроаналоговый преобразователь 8 поступает прямой двоичный код произведения П (см. фиг. 3 а). Если risGN равен 1, то на цифроачалоговый преобразователь 8 поступает обратный код произведения П (см. фиг. 36). Цифроаналоговый преобразователь 8 формирует ступенчатый сигнал треугольной формы, фаза (f которого изменяется следующим образом: р П Ci х Т х (Ok + Т) Ci х Dk х Т + Ci х Т2.

Фильтр 9 нижних частот пропускает на выход цифрового синтезатора частот только первую гармонику сформированного сигнала. В результате на выходе синтезатора частот формируется частотно-модулированный сигнал, амплитуда которого изменяется по закону

U(t) Um (Ci х Dk x Т + d х Т2), где Urn - максимальное значение амплитуды сигнала на выходе цифроаналогового преобразователя 8.

Фаза синтезируемого сигнала изменяется по закону:

# C xDkxT + CixT2, ecnnCixDk ftb; О 0,5c5,-T At, где ftb - начальная циклическая частота;

ct - скорость изменения циклической частоты, то

р Шо г + 0,5 СУ t2.

Таким образом, разработанное устройство синтезирует сигнал вида

U(t) UmSln(uA,t + 0,5c&t2), который применяется в радиолокации и си- 5 стемах связи.

Формула изобретения Цифровой синтезатор частот, содержащий последовательно соединенные генератор тактовых импульсоа и блок задержки, 10 последовательно соединенные регистр памяти, цифроаналоговый преобразователь и фильтр нижних частот, первый блок постоянного запоминания, умножитель кодов, преобразователь кодов, ксжопитель, такто5 вый вход которого соединен с первым отводом блока задержки, второй отвод которого соединен с тактовым входом регистра памяти, отличающийся тем, что, с целью повышения быстродействия, в него введены

0 последовательно соединенные второй блок постоянного запоминания и счетчик с предварительной установкой, тактовый вход которого соединен с первым отводом блока задержки, третий отвод которого соединен

5 с входом сигнала записи мнохшмого умножителя кодов, вход сигнала записи множителя которого соединен с четвертым отводом блока задержки, пятый вывод блока задержки соединен с входом сигнала за0 писи результата умножения умножителя кодов, вход множимого которого соединен с выходом накопителя, информационный вход которого соединен с выходом первого блока постоянного запоминания, а выход

5 счетчика с предварительной установкой соединен с входом множителя умножителя кодов, выход сигнала старшего разряда которого соединен с входом сигнала старшего разряда преобразователя кодов, кодо0 вый вход сигнала младших разрядов которого соединен с кодовым выходом сигналов младших разрядов умножителя кодов, выход преобразователя кодов соединен с информационным входом реги5 стра памяти.

6) CLK2

г;

CLI&t

.J tS.

14

e) CLK5

,%

прямой

обратный

| Цифровой синтезатор частот | 1978 |

|

SU813675A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-11-07—Публикация

1990-08-30—Подача