1

(21)4401437/24-24

(22)31.03.88

(46) 07.11.89. Бюл. Р 41

(71)Одесский политехнический институт

(72). Дрозд, Е.Л. Полин, A.M. Романкевич, В.Н. Валуйский и С.А. Не стеренко

(53)681.325(088.8).

(56)Авторское свидетельство СССР № 842804, кл, G 06 F 7/552, 1979.

Авторское свидетельство СССР № 1439583, кл. G 06 F 7/552, 1985,

(54)МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРАТ

(57)Изобретение относится к вычислительной технике и позволяет вычислять квадрат аргумента и осуществлять контроль вычислений по неразрешенным

кодам результата. Устройство содержит элементы И 1 ячеек матрицы, определяющие всевозможные конъюнкции значений различных разрядов аргумен- j-a, сумматоры 2 ячеек матрицы, вы- числяняще квадрат аргумента путем нахождения взвешенной суммы зна1| ений конъюнкций и разрядов аргумента. Устройство содержит также блок 3 свертки по модулю семь, определяющий остаток от деления кода результата на семь, блок 5 свертки по модулю два и элемент ИЛИ 4. Элемент НЕ 6 и элемент И 7 по сигналам с выходов блока 5 и элемента 4 идентифихщруют коды остатка 3, 5 и б, указываюпдае на неразрешенные коды результата и соответственно на неправильное функционирование устройства, t ил.

(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1509881A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1608653A1 |

| Устройство для сложения операндов с плавающей точкой с контролем | 1986 |

|

SU1310826A1 |

| Устройство для умножения | 1988 |

|

SU1603379A1 |

| Устройство для контроля умножения двоичных чисел по модулю три | 1988 |

|

SU1774337A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Множительно-делительное устройство | 1981 |

|

SU1267407A2 |

| Устройство для умножения | 1988 |

|

SU1501047A1 |

| Устройство для упорядочения единиц | 1990 |

|

SU1751746A1 |

Устройство относится к вычислительной технике и позволяет вычислять квадрат аргумента и осуществлять контроль вычислений по неразрешенным кодам результата. Устройство содержит элементы И 1 ячеек матрицы, определяющие всевозможные конъюнкции значений различных разрядов аргумента, сумматоры 2 ячеек матрицы, вычисляющие квадрат аргумента путем нахождения взвешенной суммы значений конъюнкций и разрядов аргумента. Устройство содержит также блок 3 свертки по модулю семь, определяющий остаток от деления кода результата на семь, блок свертки по модулю два 5, и элемент ИЛИ 4. ЭЛЕМЕНТ НЕ 6 И ЭЛЕМЕНТ И 7 ПО СИГНАЛАМ С ВЫХОДОВ БЛОКА 5 И ЭЛЕМЕНТА 4 ИДЕНТИФИЦИРУЮТ КОДЫ ОСТАТКА 3, 5 И 6, УКАЗЫВАЮЩИЕ НА НЕРАЗРЕШЕННЫЕ КОДЫ РЕЗУЛЬТАТА И СООТВЕТСТВЕННО НА НЕПРАВИЛЬНОЕ ФУНКЦИОНИРОВАНИЕ УСТРОЙСТВА. 1 ИЛ.

СП

|С

о

ел го

.3

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях.

Цель изобретения - повышение достоверности функционирования.

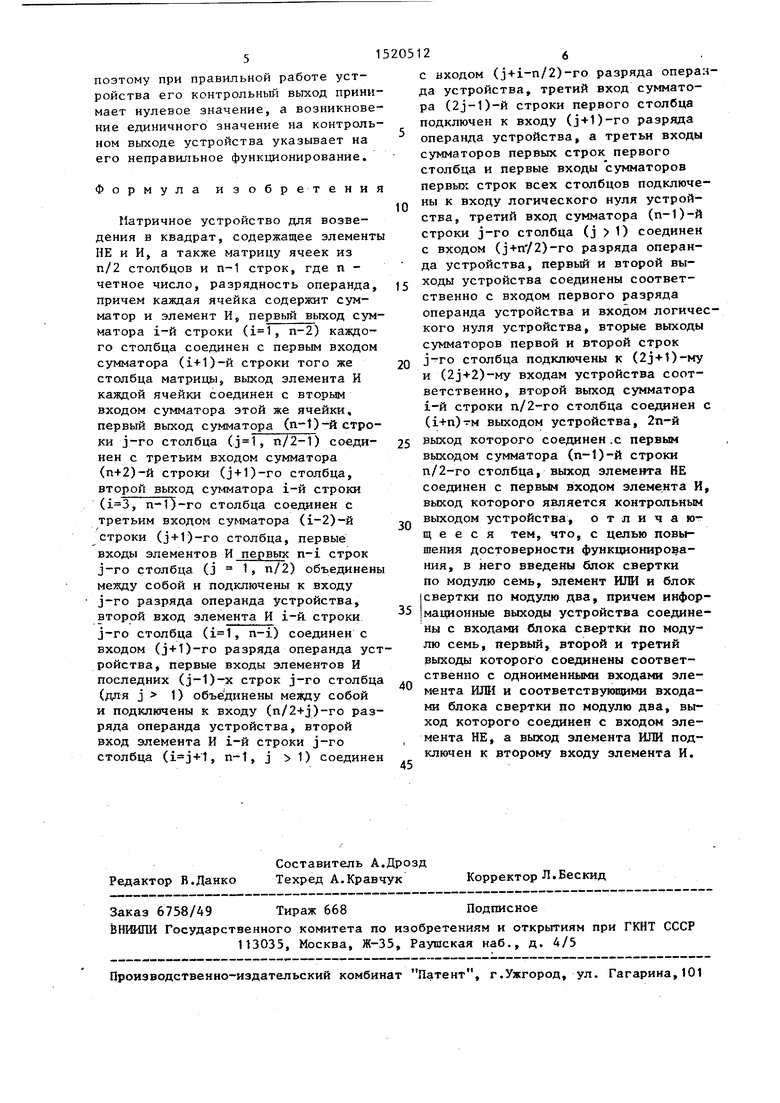

На чертеже представлена структурная схема устройства для .

Устройство содержит элементы И 1, сумматоры 2, блок 3 свертки по модулю семь, элементы ИЛИ 4, блок 5 срертки по модулю два, элемент НЕ б и элемент И 7,

; Устройство работает следующим образом.

Разряды операнда поступают на рходы устройства. При этом первый разряд операнда подается на первый выход устройства, второй выход ко- торого постоянно принимает значение логического нуля. Кроме того, первый разряд tp подается на первые входы элементов И 1 первого столбца, на вторые входы которых поступают соответственно последующие разряды операнда 2pj Зр, 4р, 5р и 6р. На выхода элементов И 1 первого столбца образуются конъюнкции 1р 2р., tp;3p, 1р-4р, 1р-5р и Тр-бр, которые Посту

пают на вторые входы соответствующих сумматоров 2 первого столбца, Через первые входы-и выходы этих маторов 2, как и сумматоров 2 последующих столбцов, распространяется сигнал переноса .(кроме первого входа первого сумматора 2j который, как и в последующих столбцах, занулен, а также кроме первого выхода последующего пятого сумматора 2, с выхода которого, как и во втором столбце, сигнал переноса поступает на третий вход четвертого сумматора 2 следующего столбца).

Третьи входы четных сумматоров первого столбца занулены, а на третьи входы первого, третьего и пятого суматоров 2 первого « столбца поступают разряды операнда, соответственно 2р , Эр и 4р .

При этом определяются третий и четвертый разряды результата, посту- пакмцие с вторых выходов первого и второго сумматоров 2 первого столбца на третий и четвертый вькоды устройства. Сигналы суммы с вторых вьпсо- дов третьего, четвертого и пятого сумматоров 2 первого столбца поступают, как и сигналы суммы с соответствующих сумматоров 2 второго столб0

05

5

0

0

5 0

5

0 е

124

ца, на третьи входы соответственно первого, второго и третьего сумматоров следующего столбца. Элементы I И 1 второго столбца вычисляют в соответствии с заведенными на их входы разрядами операнда конъюнкции 2р-3р, 2р 4р5 2р 5р 5 2р-6р и 4р 5р, которые поступают на вторые входы сумматоров 2 второго столбца. На третий вход пятого сумматора 2 второго столбца поступает разряд операнда 5р.

При этом определяются пятый и шестой разряды результата, поступающие с вторых выходов первого и второго с т маторов 2 второго столбца на пятый и шестой выходы устройства. Элементы И 1 третьего столбца определяют в соответствии с заведенными на их входы разрядами операнда конъюнкции Зр-4р, Зр-Зр, Зр-6р, 4р6р и Зр бр, которые поступают на вторые входы соответствующих сумма- Т.ОРОВ 2 третьего столбца. На третий вход пятого сумматора 2 третьего столбца поступает разряд операнда 6р. При этом определяются последующие разряды результата, поступающие с вторых выходов ci MMaTopa 2 третьего столбца и первого выхода пятого сумматора 2 третьего столбца соответственно на выходе устройства .с седьмого по двенадцатый.

-Кроме того, все разряды результа- та поступают соответственно на входы блока 3 свертки по модулю семь. При этом блок 3 определяет остаток от деления результата на семь. Код остатка поступает на входы элемента ИЛИ 4 5 а также на входы блока 5 , свертки по модулю два. Блок 5 принимает единичное значение при нечетном количестве единиц в коде остатка; Это значение инвертируется элементом НЕ 6 и устанавливает выход элемента И 7 в нулевое значение по первому входу. По второму входу элемент И 7 устанавливается в ноль при нулевом коде остатка, выявляемом элементом ИЛИ 4. Таким образом, все коды остатка имеющие четное количество единиц, отличное от нуля, установит выход элемента И 7, являющийся конт- рольнь1М выходом устройства в единичное значение.

Правильно вычисленный результат возведения операнда в квадрат не может иметь кода остатка с четным количеством единиц, .отличным от нуля.

поэтому при правильной работе устройства его контрольный выход принимает нулевое значение, а возникновение единичного значение на контрольном выходе устройства указывает на его неправильное функционирование.

Формула изобретения

Матричное устройство для возведения в квадрат, содержащее элементы НЕ и И, а также матрицу ячеек из п/2 столбцов и п-1 строк, где п - четное число, разрядность операнда, причем каждая ячейка содержит сумматор и элемент И, первый выход сумматора i-й строки ( , п-2) казвдо- го столбца соединен с первым входом сумматора (1+1)-й строки того же столбца матрицы, выход элемента И каждой ячейки соединен с вторым входом сумматора этой же ячейки, первый выход сумматора (n-t)-ft стро- ки j-ro столбца (, п/2-1) соединен с третьим входом сумматора (п+2)-й строки (j+1)-ro столбца, второй вьгход сумматора i-й строки (, п-1)-го столбца соединен с третьим входом сумматора (1-2)-й строки (j+1)-ro столбца, первые входы элементов И первых п-1 строк j-ro столбца (j 1, п/2) объединены между собой и подключены к входу j-ro разряда операнда устройства, второй вход элемента И 1-й строки j-ro столбца (, n-i) соединен с входом (j+1)-ro разряда операнда устройства, первые входы элементов И последних (j-l)-x строк j-ro столбца (для j 1) объединены между собой и подключены к входу (n/2+j)-ro разряда операнда устройства, второй вход элемента И 1-й строки j-ro столбца (, п-1, j 1) соединен

10

15

20

25

30

35

40

45

126

с входом (j+i-n/2)-ro разряда опера: - да устройства, третий вход сумматора (2j-1)-й строки первого столбца подключен к входу (j+1)-ro разряда операнда устройства, а третьи входы сумматоров первых строк первого столбца и первые входы сумматоров первых строк всех столбцов подключены к входу логического нуля устройства, третий вход сумматора (п-1)-и строки j-ro столбца (j 1) соединен с входом (j+nV2)-ro разряда операнда устройства, первый и второй выходы устройства соединены соответственно с входом первого разряда операнда устройства и входом логического нуля устройства, вторые выходы сумматоров первой и второй строк столбца подключены к (2j+1)-My и (2j+2)-My входам устройства соответственно, второй вьпсод сумматора 1-й строки П/2-ГО столбца соединен с (1+п)-гм выходом устройства, 2п-й эыход которого соединен .с первым выходом сумматора (п-1)-и строки Д/2-ГО столбца, выход элемента НЕ соединен с первым входом элемента И, выход которого является контрольным выходом устройства, отличающееся тем, что, с целью повышения достоверности функционирования, в него введены блок свертки по модулю семь, элемент ИЛИ и блок свертки по модулю два, причем информационные выходы устройства соединены с входами блока свертки по модулю семь, первый, второй и третий выходы которого соединены соответственно с одноименными входами элемента ИЛИ и соответствукнцими входами блока свертки по модулю два, выход которого соединен с входом элемента НЕ, а выход элемента ИЛИ подключен к второму входу элемента И.

Авторы

Даты

1989-11-07—Публикация

1988-03-31—Подача