Изобретение относится к области измерительной и вычислительной техники и может быть использовано для измерения функдаи взаимной корреля- каждого из суммы случайных процессов, подвергнутых разным масштабно-временным искажениям.

Цель изобретения - повышение быстродействия.

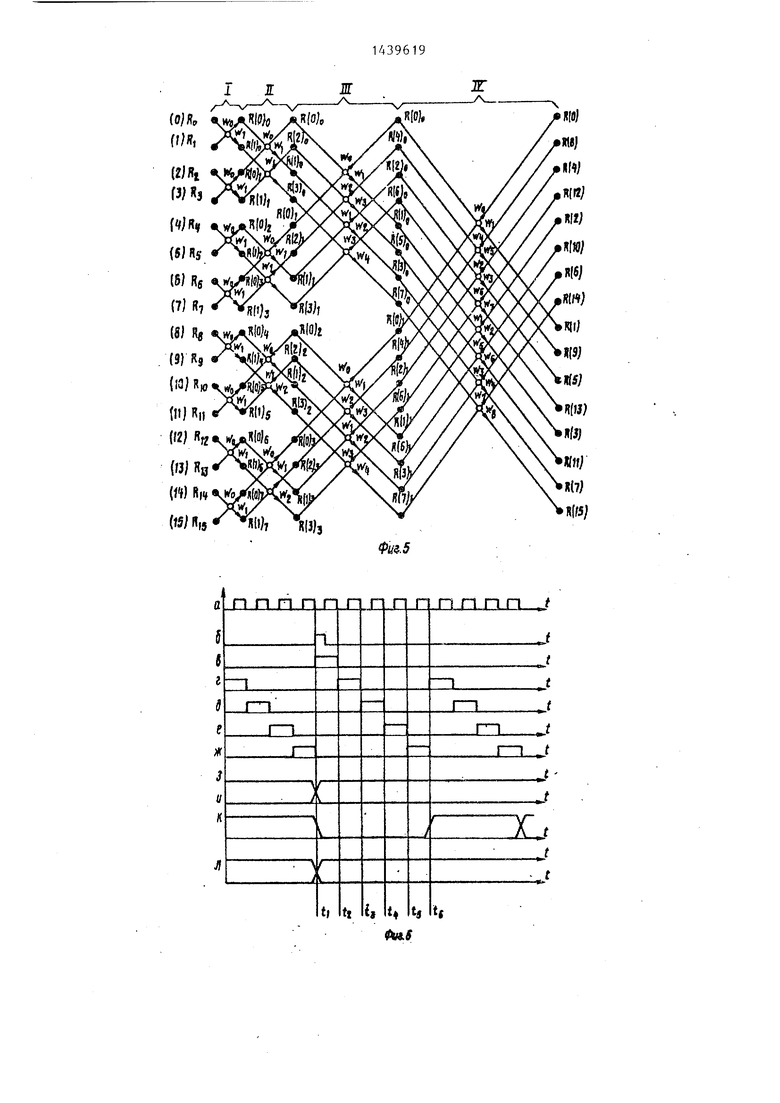

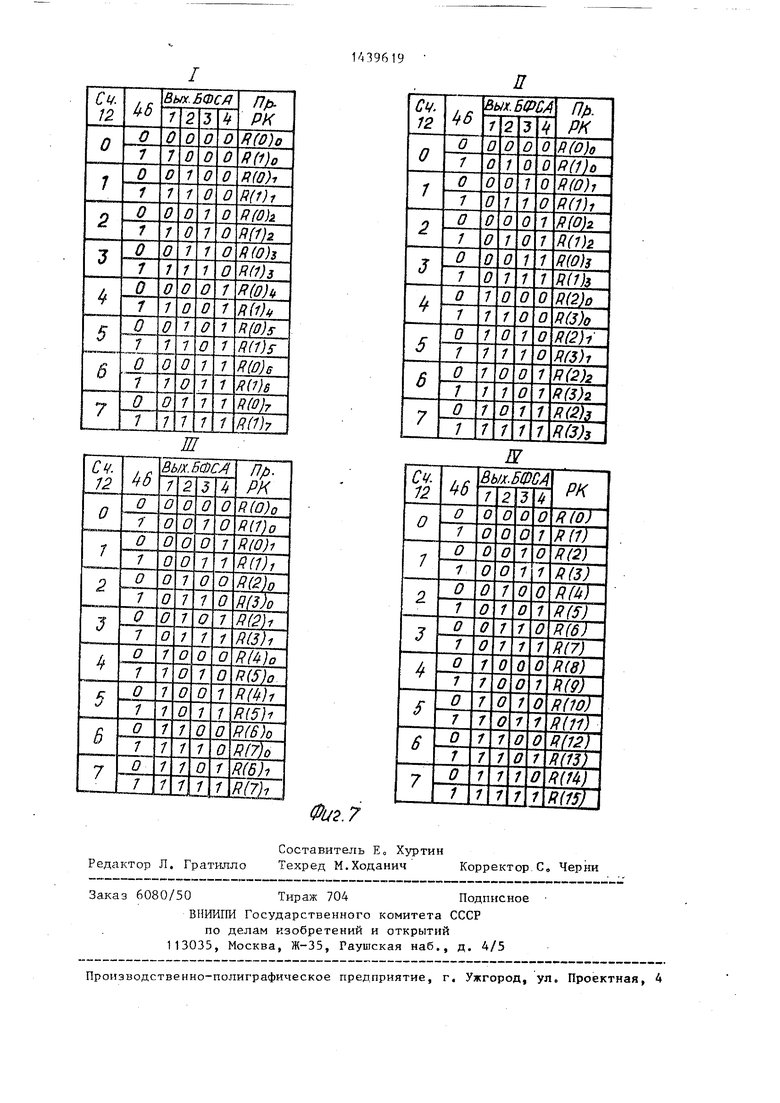

На фиг. 1 изображена структурная схема устройства для разделения кор- релограмм; на фиг. 2 - структурная схема блока формирования младших адресов; на фиг, 3 - структурная схема блока формирования старших адресов; на фиг, 4 - структзфная схема блока вычисления сумм частных коррелограмм на фиг о 5 - направленньй граф алгоритма вычисления отсчетов результи- рующих коррелограмм; на фиг 6 - временные диаграммы работы; на фиг„ 7 - таблицы состояний входов и выходов блока формирования старших адресов

Устройство дпя разделения корре- лограмм состоит из блока 1 синхро- низа1щи, блока 2 вычисления сумм частных коррелограмм, коррелятора 3, первой группы элементов И 4, второ- го 5 и четвертого 6 элементов И, rpyn пы элементов ШТИ 7, третьего элемента ИЛИ 8, блока 9 памяти, первого триггера 10, второго 11, третьего 12 и первого 13 счетчиков, блока 14 формирования младцшх адресов (БФМА), бл ка 15 формирования старших адресов (БФСА), второго триггера 16, второй группы элементов И 17, третьего 18, первого 19 и пятого 20 элементов И, четвертого 21, первого 22, пятого 23 и второго 24 элементов ИЛИ

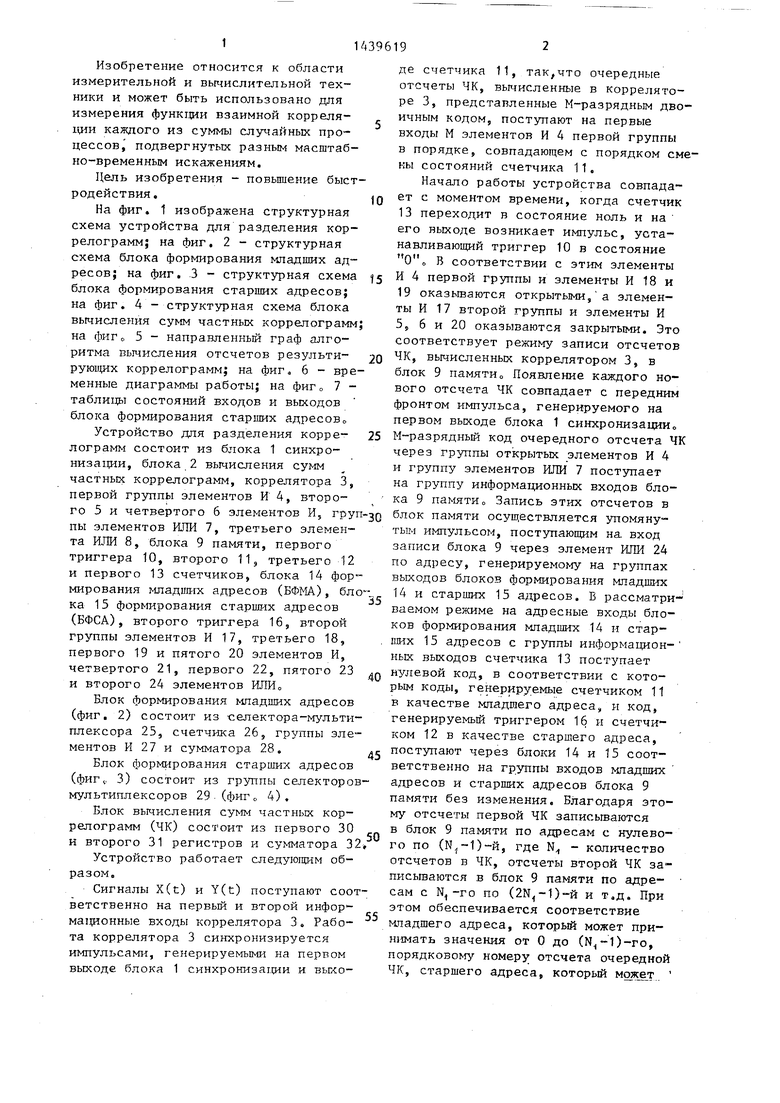

Блок формирования младших адресов (фиг. 2) состоит из селектора-мультиплексора 25, счетчика 26, группы элементов И 27 м сумматора 28.

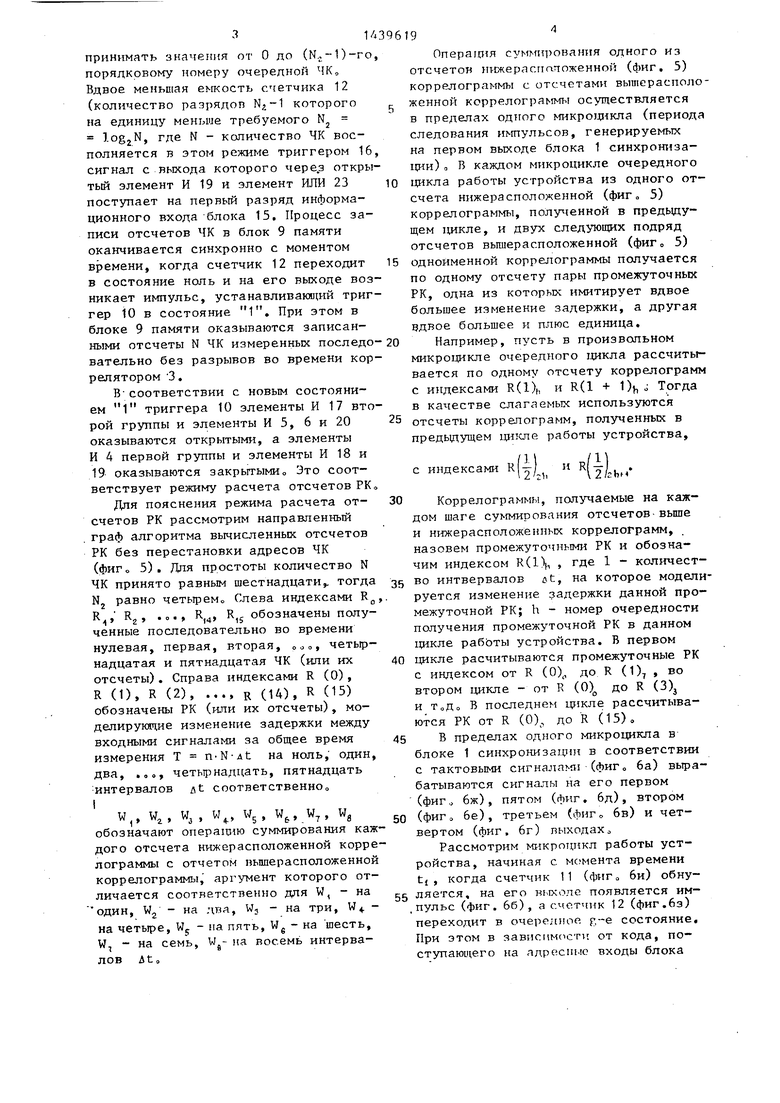

Блок формироБан 1я старших адресов (фигt 3) состоит из группы селекторо мультиплексоров 29 (фиг о 4).

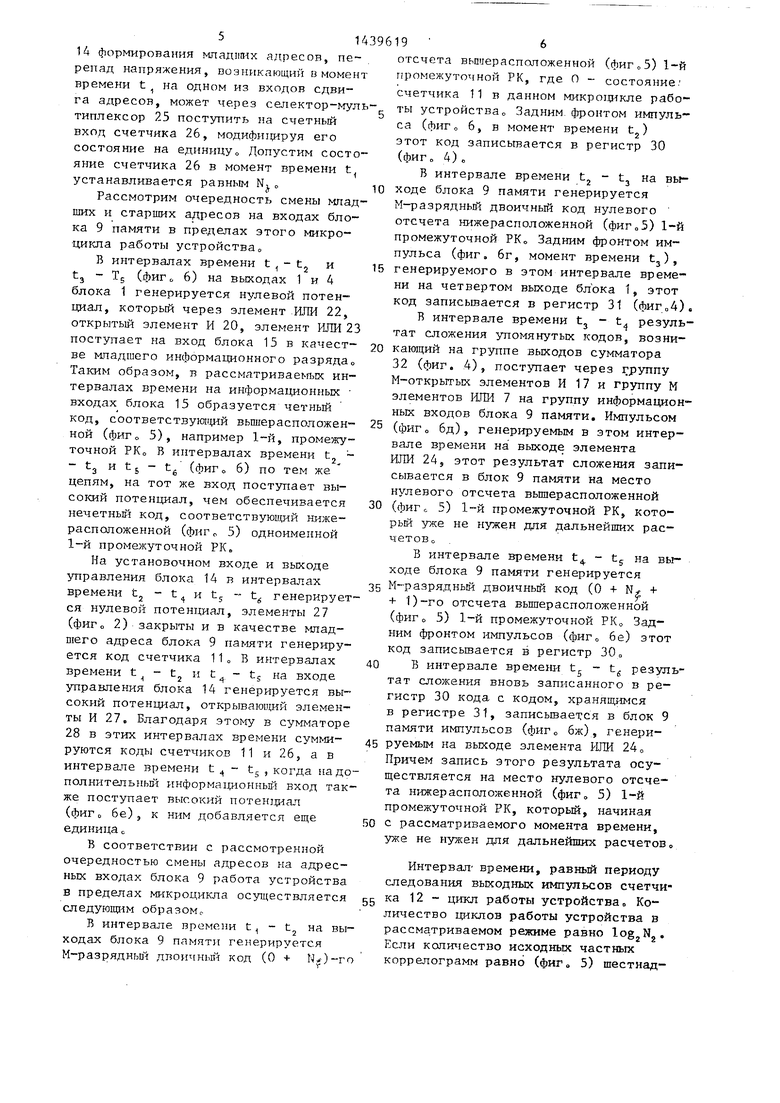

Блок вычисления сумм частных коррелограмм (ЧК) состоит из первого 30 и второго 31 регистров и сумматора 3

Устройство работает следующим образом.

Сигналы X(t) и Y(t) поступают сооветственно на первый и второй инфор- мапронные входы коррелятора 3. Работа коррелятора 3 си1-гхронизируется импульсам -, генерируемыми на первом выходе блока 1 синхронизатщи и вько

Q

j

0

5

де счетчика 11, так,что очередные отсчеты ЧК, вычисленные в корреляторе 3, представленные М-разрядным двоичным кодом, поступают на первые входы М элементов И 4 первой группы в порядке, совпадающем с порядком смены состояний счетчика 11.

Начало работы устройства совпада- ет с моментом времени, когда счетчик

13переходит в состояние ноль и на его выходе возникает импульс, устанавливающий триггер 10 в состояние В соответствии с этим элементы И 4 первой группы и элементы И 18 и 19 оказьшаются открытыми, а элементы И 17 второй группы и элементы И 5, 6 и 20 оказываются закрытыми. Это соответствует режиму записи отсчетов ЧК, вычисленных коррелятором 3, в блок 9 памяти Появление каждого нового отсчета ЧК совпадает с передним фронтом импульса, генерируемого на первом выходе блока 1 синхронизации М-разрядный код очередного отсчета ЧК через группы открытых элементов И 4

и группу элементов ИЛИ 7 поступает на группу информационных входов блока 9 памяти о Запись этих отсчетов в блок памяти осуш;ествляется упомяну- тым импульсом, поступаюпщм на вход записи блока 9 через элемент ИЛИ 24 по адресу, генерируемому на группах выходов блоков формирования младших

14и старших 15 адресов. В рассматри ваемом режиме на адресные входы блоков формирования младших 14 и старших 15 адресов с группы информацион- ных выходов счетчика 13 поступает нулевой код, в соответствии с которым коды, генерируемые счетчиком 11

в качестве мпядс его адреса, и код, генерируемый триггером 16 и счетчиком 12 в качестве старшего адреса, поступают через блоки 14 и 15 соответственно на группы входов младших адресов и старших адресов блока 9 памяти без изменения. Благодаря этому отсчеты первой ЧК записываются в блок 9 памяти по адресам с нулевого по (Nj-1)-M, где N - количество отсчетов в ЧК, отсчеты второй ЧК записываются в блок 9 памяти по адре- сам с по ()-й и т.д. При этом обеспечивается соответствие младшего адреса, который может принимать значения от О до ()-ro, порядковому номеру отсчета очередной ЧК, старшего адреса, которьй .

31/4

принимать значения от О до (N.,-1)-го, порядковому номеру очередной ЧК., Вдвое меньшая емкость счетчика 12 (количество раэрядоп которого на единицу меньше требуемого N , где N - количество ЧК восполняется в этом режиме триггером 16, сигнал с выхода которого через открытый элемент И 19 и элемент ИЛИ 23 поступает на первый разряд информационного входа блока 15. Процесс записи отсчетов ЧК в блок 9 памяти оканчивается синхронно с моментом времени, когда счетчик 12 переходит в состояние ноль и на его выходе возникает импульс, устанавливакяций триггер 10 в состояние 1. При этом в блоке 9 памяти оказываются записанными отсчеты N ЧК измеренных последовательно без разрывов во времени коррелятором 3,

В-соответствии с новым состоянием 1 триггера 10 элементы И 17 втоой группы и элементы И 5, 6 и 20 оказываются открытыми, а элементы 4 первой группы и элементы И 18 и 19 оказываются закрытыми Это соответствует режиму расчета отсчетов РК,

Для пояснения режима расчета отсчетов РК рассмотрим направленный граф алгоритма вычисленных отсчетов РК без перестановки адресов ЧК (фиг о 5). Для простоты количество N К принято равным шестнадцати. тогда Nj равно четыремо Слева индексами RQ,. R, Rg, .0., R,4 R,5 обозначены полученные последовательно во времени нулевая, первая, вторая, ооо, четырнадцатая и пятнадцатая ЧК (или их отсчеты). Справа индексами R (0), R (1), R (2), .... R (14), R (15) обозначены РК (или их отсчеты), моелирующие изменение задержки между входными сигналами за общее время измерения Т на ноль, один, ва, .,,, четырнадцать, пятнадцать интервалов t соответственно,

W,. W, W, , W, W, , W,, W,, Wg бозначают операшш суммирования кажого отсчета нижерасположенной корре- ограммы с отчетом пьшерасположенной оррелограммы, аргумент которого отичается соответственно для W, - на один, Wj - на .чвя, Wj - на три, W4. - на четыре, W - на пять, Wg - на шесть, W, - на семь, на восемь интервалов At,

19

Операция cyм fиpoвaния одного из отсчетов Н1гаераспагтоженно1 (фиг, 5) коррелограммы с отсчетами вышсрасполо- женной коррелограммы осуществляется в пределах одного микро)1кла (периода следования и myльcoв, генерируемых на первом выходе блока 1 синхронизации) о В каждом микроцикле очередного

цикла работы устройства из одного отсчета нижерасположенной (фиг 3) коррелограммы, поЛу 1енной в предыдущем 1у1кле, и двух следующих подряд отсчетов вышерасположенной (фиг о 5)

одноименной коррелограммы получается по одному отсчету пары промежуточных РК, одна из которых имитирует вдвое большее изменение задержки, а другая вдвое большее и плюс единица.

Например, пусть в произвольном

микродакле очередного тдикла рассчитывается по одному отсчету коррелограмм с индексами R(l)(, и R(l + 1)ьо Тогда в качестве слагаемых используются

отсчеты коррелограмм, полученных в предыдущем цшсле работы устройства.

с индексами К1тг) / гЬ

ilbMКоррелограмм,, получаемые на каждом шаге суммировсчния отсчетов- выше и нижерасположенных коррелограмм, назовем промежуточными РК и обозначим индексом R(l)b , где 1 - количество интвервалов лС, на которое моделируется изменение задержки данной промежуточной РК; h - номер очередности получения промежуточной РК в данном 1щкле работы устройства. Б первом

цикле расчитываются промежуточные РК с индексом от R (0), до R (1) , во втором цикле - от R (0) до R (3)j и ТоДо в последнем цикле рассчитываются РК от R (0), до R (15),

В пределах одного микроцикла в блоке 1 синхронизации в соответствии с тактовыми сигналами (фиг 6а) вырабатываются сигналы на его первом (фиг о 6ж), пятом (фиг. 6д), втором

(фиг о бе), третьем (фиг о 6в) и четвертом (фиг. 6г) выходах о

Рассмотрим №1кроцикл работы устройства, начиная с момента времени tj, когда счетчик 11 (фиг, 6и) обнуяется, на его выхоле появляется им- ульс (фиг. 6б), а счетчик 12 (фиг.бз) ереходит в очередное р,-е состояние. ри этом в зав11сим 1сти от кода, поступающего на лдреспмо входы блока

514396

1А формирования мпадпих адресов, пе репад напряжения, возникающий в момент времени t , на одном из входов сдвига адресов, может через селектор-мультиплексор 25 поступить на счетный вход счетчика 26, модифитщруя его состояние на единицу Допустим состояние счетчика 26 в момент времени t устанавливается равным Nj о-JQ

Рассмотрим очередность смены мпад- ших и старших адресов на входах блока 9 памяти в пределах этого микро- цикла работы устройства

В интервалах времени t - t

и

tj - TS (фиг о 6) на выходах 1 и 4 блока 1 генерируется нулевой потенциал, который через элемент ИЛИ 22, открытый элемент И 20, элемент ИЛИ 23 поступает на вход блока 15 в качает- ве младшего информационного разряда Таким образом, в рассматриваемых интервалах времени на информационных входах блока 15 образуется четный код, соответстБую1(щй вышерасположен- ной (фиго 5), например 1-й, промежуточной РКо В интервалах времени t - - tg и tj - tg (фиго 6) по тем же цепям, на тот же вход поступает высокий потенциал, чем обеспечивается нечетный код, соответствуюищй нижерасположенной (фиг с 5) одноименной 1-й промежуточной РК.

На установочном входе и выходе управления блока 14 в интервалах времени t - t и tj t генерируется нулевой потенциал, элементы 27 (фиг о 2) закрыты и в качестве младшего адреса блока 9 генерируется код счетчика 11 В интервалах времени t - t и t - t; на входе управления блока 14 генерируется высокий потенциал, открывающий элементы И 27е Благодаря этому в сумматоре 28 в этих интервалах времени сумми- руются коды счетчиков 11 и 26, а в интервале времени t - t, , когда на дополнительный информахщонньй вход также поступает высокий потентд ал (фиг о бе)5 к ним добавляется еще единица

В соответствии с рассмотренной очередностью смены адресов на адресных входах блока 9 работа устройства в пределах микроцикла осуществляется следующим образомо

В интервале времени t, - t на выходах блока 9 памяти генерируется М-разрядньп1; двоичньм код (О N)-r

5

0 5 0

,5 0 5 о

g

19 6

отсчета вьпиерасположенной (фиг о 5) 1-й ггромежуточной РК, где О - состояние, счетчика 11 в данном микротдткле работы устройства Задним, фронтом импульса (фиг 6, в момент времени t) этот код записьгаается в регистр 30 (фиг о 4)о

В интервале времени t - t на выходе блока 9 памяти генерируется М-разрядньп{ двоичный код нулевого отсчета нижерасположенной () 1-й промежуточной РК Задним фронтом импульса (фиг. 6г, момент времени t), генерируемого в этом интервале време ни на четвертом выходе блока 1, этот код записьшается в регистр 31 (фиг„4).

В интервале времени tj - t результат сложения упомянутых кодов, возникающий на группе выходов сумматора 32 (фиг. 4), поступает через группу М-открытых элементов И 17 и группу М элементов ИЛИ 7 на группу информационных входов блока 9 памяти. Импульсом (фиго 6д), генерируемым в этом интервале времени на выходе элемента ИЛИ 24, этот результат сложения записывается в блок 9 памяти на место нулевого отсчета вьпаерасположенной (фиг с 5) 1-й промежуточной РК, который уже не нужен для дальнейших расчетов

В интервале времени t - t на выходе блока 9 памяти генерируется М-разрядньй двоичный код (О N + + 1)-го отсчета вьштерасположенной (фиг 5) 1-й промежуточной РК Задним фронтом импульсов (фиго бе) этот код записьшается в регистр 30„

В интервале времени t - t результат сложения вновь записанного в регистр 30 кода с кодом, хранящимся в регистре 31, записьшается в блок 9 памяти импульсов (фиг бж), генерируемым на выходе элемента ИЛИ 24 Причем запись этого результата осуществляется на место нулевого отсчета нижерасположенной (фиг 5) 1-й промежуточной РК, который, начиная с рассматриваемого момента времени, уже не нужен для дальнейших расчетов

Интервал- времени, равный периоду следования выходных импульсов счетчи ка 12 - цикл работы устройства Количество циклов работы устройства в рассматриваемом режиме равно . Если количество исходных частных коррелограмм равно (фиг„ 5) шестнадцати, то количество циклов работы устройства равно четырем.

На Лиг о 7 изображены четыре табли- цы I-IV (в соответствии с количеством циклов) состояний выходов блока формирования старших адресов, В этих таблицах столбик Счо12 отражает со стояния счетчика 12; столбик 46 - состояние пятого элемента ИЛИ 23: столбики Вых.БФСА - состояния выходов блока формирования старших адресов; в столбце Пр.РК изображены промежуточные РК R(l),, .

В течение первого цикла (I) на адресные входы БФМД 14 и БФСА 15 из счетчика 13 поступает нулевой код, в соответствии с которым мультиплексоры 29 (фиг, 3) передают на выходы

Поэтому в первой половине второго цикла в счетчике 26 сохраняется нуле вое состояние, а во второй половине единичное состояние, В соответствии с перестановкой старших адресов, про изошедшей во втором цикле в БФСА, в первой половине второго цикла из блока 9 памяти в вычислительньй блок 2 вызываются отсчеты промежуточных РК с индексом ноль к (0) , а во второй половине - с индексом один R (1) о В первой половине второго цикла в БФМА происходит сдвиг адресов суммируемых отсчетов на ноль и один интервал jt, в результате чего получаются промежуточные РК с индексом ноль и единица соответственно R (0)j и к (1.) о Во второй полови

информацию, поступающую на их первые 20 не второго цикла в БФМА происходит

сдвиг адресов суммируемых отсчетов на один и два интервала at, в результа те чего получаются промежуточные РК с индексом два и три соответственно

адресные входы БФМА и БФСА из счетчи ка 13 поступает код, равньй двум, в соответствии с которым селекторывходы. Код БФСА (фиго 7, 1) в этом случае полностью совпадает с кодом, поступающим на информационные входы БФСАо Мультиплексор 25 БФМА в рассматриваемом цикле также передает на его 25 Тк (2)1 и к (3)1 выход или на счетный вход счетчикав течение третьего цикла (III) на

26 информацию, поступающую на его вход. Так как эта информация равна нулю, состояние счетчика 26 в рассматриваемом цикле не меняется и все вре- зо мультиплексоры 29 и селектор-мульти- мя равно нулюо В связи с этим в каж-плексор 25 передают на выход инфордом микроцикле первого цикла работы устройства отсчеты нижестоящей (фиг,5) коррелограммы складываются с отсчетами вьштестоящей коррелограммы либо без сдвига (получаются отсчеты промежуточных РК с индексом Р (0), либо со сдвигом на единицу (ползгчаются отсчеты промежуточных РК с индексом R (1))о

В течение второго цикла (II) на

мацию, поступающую на их третьи входы Код БФСА в этом случае (фиг„7, ИГ) представляет собой перестановку

25 разрядов кода, поступающего на его информационные входы в порядке: первый разряд - на место третьего, второй - на место четвертого и т.До, последний - на место первого, пред40 последний - на место второго. На третий вход селектора-мультиплексора 25

9619

Поэтому в первой половине второго цикла в счетчике 26 сохраняется нулевое состояние, а во второй половине - единичное состояние, В соответствии с перестановкой старших адресов, произошедшей во втором цикле в БФСА, в первой половине второго цикла из блока 9 памяти в вычислительньй блок 2 вызываются отсчеты промежуточных РК с индексом ноль к (0) , а во второй половине - с индексом один R (1) о В первой половине второго цикла в БФМА происходит сдвиг адресов суммируемых отсчетов на ноль и один интервал jt, в результате чего получаются промежуточные РК с индексом ноль и единица соответственно R (0)j и к (1.) о Во второй полови10

15

20 не второго цикла в БФМА происходит

сдвиг адресов суммируемых отсчетов на один и два интервала at, в результате чего получаются промежуточные РК с индексом два и три соответственно

Тк (2)1 и к (3)1 в течение третьего цикла (III) на

адресные входы БФМА и БФСА из счетчика 13 поступает код, равньй двум, в соответствии с которым селекторымультиплексоры 29 и селектор-мульти- плексор 25 передают на выход информацию, поступающую на их третьи входы Код БФСА в этом случае (фиг„7, ИГ) представляет собой перестановку

разрядов кода, поступающего на его информационные входы в порядке: первый разряд - на место третьего, второй - на место четвертого и т.До, последний - на место первого, предоследний - на место второго. На третий вход селектора-мультиплексора 25

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

| Устройство для определения взаимных корреляционных функций | 1981 |

|

SU1016791A1 |

| Разделитель коррелограмм | 1988 |

|

SU1506453A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Устройство для определения взаимной корреляционной функции | 1983 |

|

SU1108463A1 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Разделитель коррелограмм | 1988 |

|

SU1624478A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

Изобретение относится к измерительной и вычислительной технике и может быть использовано для измерения функции взаимной корреляции каждого из суммы случайных процессов, подвергнутых разным масштабно-временн ым исК ахенияМо Цель изобретения - повьше- ние быстродействия о Устройство содержит блок синхронизации 1, блок 2 вычисления сумм частных коррелограмм, коррелятор 3, .группы элементов И-.4, 17, группу элементов ИЛИ, элементы И 5, 6, 18-20, блок памяти 9, триггеры 10, 16, счетчики 11-13, блоки формирования младших 14 и старших 15 адресов, элементы ИЛИ 8, 21-24. Устройство позволяет вычислять результирующие коррелограммы По массиву, состоящему из частных коррелограмм, используя для хранения массивов отсчетов- частных и результирующих коррелограмм ,д один и тот же массив ячеек памяти S 2 ЗоП. ф-лы, 7 илз сл САЭ Х СО

адресные входы БФМА и БФСА из счетчи- поступает выход третьего от конца разка 13 поступает код, равньй единице,ряда счетчика 12, отрицательный пере- в соответствии с которым селекторы- пйд напряжения на котром происходит мультиплексоры 29 и селектор-мульти- g три раза, каждый раз через четверть

длительности третьего , В результате первую четверть третьего щжла счетчик 26 находится в состоянии ноль, вторую - один, третью - два, 50 четвертую - три о В соответствии с пеплексор 25 передают на выходы информацию, поступающую на их вторые входы „ Код на выходах БФСА в этом случае (фиг, 7, II) представляет собой перестановку разрядов кода, поступающего на информационные входы БФСА: первьй разряд - на место второго, второй - на место третьего и т,д,, последний - Hd место первогоо На вторестановкой старших адресов, произошедшей в третьем цикле в БФСА, в первой четверти третьего цикла из блока 9 памяти в вычислитепьпый блок 2 вырой вход селектора-мультиплексора 25 gg зьшаются отсчетм промежуточных РК с

поступает выход предпоследнего разряда счетчика 12, отрицательный перепад напряжения на котором происходит как раз посредине второго цикла.

индексом ноль IК (0) , во второй четверти - с индексом один R (1) , в третьей четверти - с индексом два R (2) , в четвертой четверти - с и

рестановкой старших адресов, произошедшей в третьем цикле в БФСА, в первой четверти третьего цикла из блока 9 памяти в вычислитепьпый блок 2 вызьшаются отсчетм промежуточных РК с

индексом ноль IК (0) , во второй четверти - с индексом один R (1) ,, в третьей четверти - с индексом два R (2) , в четвертой четверти - с индексом три R (3) о В первой четверт третьего тщкла в БФМА происходит сдвиг адресов сзгммируёмых отсчетов на ноль и один интервал д1, в результате чего получаются промежуточные РК с индексом ноль и единица соответственно R (0) и R (1) о Во второй четверти третьего цикла в БФМА происходит сдвиг адресов суммируемых отсчетов на один и два интервала At, в результате чего получаются промежуточные РК с индексом два и три соответственно к (2) и к (3) В третьей четверти третьего цикла в БФМА происходит сдвиг адресов суммируемых отсчетов промежуточных РК на два и три интервала At, в результате чего получаются промежуточные РК с И1щексом четьгое и пять соответственно R (4)J и к (5) , В четвертой четверти третьего цикла в . происходит сдвиг адресов суммируемых от- счетов промежуточных коррелограмм с индексом R (3) на три и четыре интервала dt, в результате чего получаются промежуточные РК с индексом шесть и семь соответственно R (6) и R (7) о

Последукщне циклы работы устройства протекают аналогичным образомо Каждая смена состояния счетчика 13 вызьшает новую перестановку старших адресов, формируемых БФСА по описанному принципу На вход счетчика 26 через селектор-мультиплексор 25 коммутируется следующий, более младший разряд счетчика 12о Количество моде- лируемых законов изменения задержки удваивается, пока в последнем цикле не будут вычислены все N РК, моде- лирукшщх N законов изменения задержiKHo

В предлагаемом устройстве алгоритм вычисления РК, представленньй графом (фиг о 5), не требует перестановки адресов ЧК перед началом вычисления о Однако, при этом требуется перестановка адресов РКо

Предлагаемое устройство позволяет реализовать алгоритм вычисления отсчетов РК с перестановкой адресов ЧК, gg ным входом i-peTbero счетчика выход

дпЯ Чего достаточно изменить порядок соединения выходов БФСА с входами старших адресов блока 9 памяти на инверсныйс

переполнения которого соединен с пер вым входом четвертого элемента И, установочньгм входом блока формирования младшюс адресов и установочньп 1

5

Формула изобретения

1 о Устройство для раздачения кор- реттограмм, содержащее, коррелятор, первьй и второй информационные входы которого являются соответственно первым и вторым информационными входами устройства, две группы элементов И, группу элементов ИЛИ, первый элемент И, три счетчика, блок памяти, первьй триггер и блок синхронизации, первый выход которого соединен с входом синхронлзатдии коррелятора, разрядные выходы которого соединены с первыми входами элементов И первой группы выходы элементов И второй группы соединены с первыми входами элементов ИЛР1 группы, выход переполнения первого счетчика подключен к входу сброса первого триггера, инверсный выход которого соединен с первым входом первого элемента И, отличающееся тем, что, с целью повьЕиения быстродействия, в него введены блок формирования младгшх адресов, блок формирования cTaputtcc адресов, второй триггер четыре элемента И, пять элементов

0 ИЛИ, и блок, содержащий два регистра и сумматор, причем выходы элементов И первой группы соединены с вторыми входат-ш элементов ШШ группы, выходы которых подключены к инфopмaщ oннo ri

г, входу блока памяти, первьй вькод

блока синхрош-гзации соединен с первыми входами первого и второго тов ИЛИ и счетным входом второго счет0

5

единен с входами сброса коррелятора и блока синхронизаг ки, первым входом второго элемента И и счетныг-г входом второго триггера, выход которого соединен с вторым входом первого эле мента И и первым входом третьего элемента И, второй вход которого соединен с инверсным выходом первого триггера и вторыми входами элементов И первой группы,,, а выход соединен с первым входом третьего элемента ИЛИу

выход которого соединен с (Nj loggN, N - число частных коррато- грамм) входом сдвига адреса блока формирования младших адресов и счетпереполнения которого соединен с первым входом четвертого элемента И, установочньгм входом блока формирования младшюс адресов и установочньп 1

11

входом пергзого триггера, прямой выход которого соединен с первыми входами элементов И второй группы, первым входом пятого элемента И, вторым входом второго элемента И, выход которого подключен к второму входу третьего элемента ИЛИ, прямой выход первого триггера подключен к второму входу четвертого элемента И, выход которого соединен со счетным входом первого счетчика, разрядные выходы которого подключены к группам адресных входов блоков формирования младших адресов и формирования старших адресов, ( информационный выход третьего счетчика соединен с Nj-M разрядом информационного входа блока формирования старших адресов, информа1дионные выходы с первого по (NJ - 2)-и третьего счетчика подключены к информационным входам с второго по ( блока формирования старших адресов и соответственно к входам сдвига адресов которого соединен с шиной нулевого потенциала, информационньй выход второго счетчика соединен с первым информационным входом блока формирования младших адресов, информационньй выход которого соединен с младшими разрядами адесного входа блока памяти, второй ыход блока синхронизации соединен информационным входом блока формиования младших адресов и первым вхоом четвертого элемента ИЛИ, второй вход которого подключен к третьему выходу блока синхронизации, а выход соединен с входом управления режимом блока формирования младших адресов и входом записи первого регистра блока вычисления сумм частных коррело- рамм, выход сумматора блока вычисления сумм частных коррелограмм соединен с втopы и входами элементов И второй группы, первьй и второй информационные входы сумматора соединены соответственно с выходами первого и второго регистров вычисления сумм частных коррелограмм блока, информа- ционньй выход блока памяти подршючен к информационным входам первого и второго регистров, блока вычисления сумм частных коррелограмм, четвертьй выход блока синхронизации соединен с входом записи второго регистра блока вычисления сумм частных коррелограмм и вторым входом первого элемента ИЛИ, выход которого подключен к

3961912

второму входу пятого элемента И, выход которого соединен с первым входом пятого элемента НИИ, второй вход которого подключен к выходу первого элемента И, выход пятого элемента ИЛИ соединен с первым разрядом информационного входа блока формирования старших адресов, выход которого со10 единен со старшими разрядами адресного входа блока памяти, пятый выход блока синхронизации подключен к второму входу второго элемента ИЛИ, выход которого подключен к входу за15 писи блока памяти.

2 о Устройство по п. 1, отличающееся тем, что блок формирования младших адресов содержит се-

20 лектор-мультиплексор, счетчик, группу элементов И и сумматор, причем адресные входы селектора-мультиплексора являются адресными входами блока, а информапз онньй вход селектора25 мультиплексора является входом сдвига адресов блока, выход селектора- мультиплексора подключен к счетному входу счетчика, вход сброса которого является установочным входом блока,

30 разрядные выходы счетчика подключены к первым входам элементов И групгы, вторые входы которых соединены и яр- ляются входом управления режимом блока, выходы элементов И группы под35 ключены к первой группе входов сумматора , вторая группа входов которого является первым информационным входом блока, вход переноса сумматора Является информащюнным входом блока,

40 а выход сум атора является выходом блока о

3 о Устройство по По 1, о т л и ч а- ю щ е а с я тем, что блок формирова-

кия cTapi JHX адресов содержит группу из Nj селекторов-мультиплексоров, адресные входы которых поразрядно соединены и являются адресными входами блока, информаи онные входы с первого

по q-й q-ro селектора-мультиплексора (q 1, N2) подключены соответственно с q-ro по первьй разрядам информационного входа блока, а входы с (q+1)-ro по q-ro селектора-муль-

типлексора (кроме ) соединены

с (N,j - q + 1)м разрядом информаи юН - ного входа блока, выходы селекторов- мультиплексоров яв.пяются выходом бло- као

Фиг. 2

Фиг.

фиг.З

. ff/ff

/

п

| Устройство для определения взаимной корреляционной функции | 1977 |

|

SU691866A1 |

| Коррелометр | 1979 |

|

SU783799A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-23—Публикация

1987-04-06—Подача