динен с инверсным выходом второго I RS-TpHrrepa, а выход - с входом сброса второго счетчика и 5 входом второгоD -триггера, выход пятого

элемента И соединен с вторым входом четвертого элемента И, выход шестого элемента И - со счетным входом второго счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| СПЕЦПРОЦЕССОР ДЛЯ ЗАДАЧИ ВЫПОЛНИМОСТИ БУЛЕВЫХ ФОРМУЛ | 2017 |

|

RU2644505C1 |

| Устройство для распаковки команд | 1984 |

|

SU1251075A1 |

| Устройство для сопряжения каналов ЭВМ с периферийными устройствами | 1990 |

|

SU1732348A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

| Устройство для формирования и передачи сообщения | 1990 |

|

SU1778767A1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ .ОБМЕНОМ ИНФОРМАЦИИ, содержащее приемопередатчик, состоящий из элементов И, регистра .признака, регистра байта данных, первогоD-триггера, двух R5-триггеров, элемента ИЛИ, мультиплексора, первого счетчика и регистра сдвига, причем первый и второй входы первого элемента И являются соответственно входами старшего разряда адреса и записи устройства, а выход соединен с первыми входами второго и третьего элементов И, вторые входы которых объединены и являются входом младшего разряда адреса устройства, вьиоды второго и третьего элементов И соединены с управляющими входами регистра признака и регистра байта данных, информационные входы которых образуют вход данных устройства, а выходы соединены с информационными входами мультиплексора, выход которого соединен с информационным входом регистра сдвига, вход сброса устройства - с первым входом элемен-г та ИЛИ,R -входом первого R5-триггера и сбросовым входом первого счет ика, счетный вход которого и сдвиговый вход регистра сдвига соединены с выходом четвертого элемента И, первый вход которого соединен с выходом первого PS-триггера, 5-вход которого соединен с выходом первого элемента И, выходы третьего элемента И и элемента ИЛИ соединены с установочными входами первого D-триггера, прямой и инверсный выходы которого соединены с управляющими входами мультиплексора и установочными входами второго Рбттриггера, С-вход которого и управляющий вход регистра сдвига соединены с первым 9 выходом счетчика, второй выход которого соединен с вторым входом элемента ИЛИ, прямой выход первого -триггера является выходом запроса передачи устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит пятый, шестой и седьмой элементы И, вторые D-триггер, элемент ИЛИ и счетО СО чик, причем тактовый вход устройства соединен с С-входом второго 3)-триг | гера, первым инверсным входом пятого fO СР элемента И и инверсным входом шестого элемента И, вьрсод второго счетчика соединен с вторым инверсным входом пятого элемента И и инверсным входом седьмого элемента И, прямой вход которого соединен с выходом регистра сдвига, а выход - с прямьм входом шестого элемента И,Г -входом второго D -триггера и является информационным выходом устройства, инверсный выход второго Г-триггера соединен с перовым входом второго эле,мента ИЛИ, второй вход которого сое

Изобретение относится к вычислительной технике, а более конкретно к вводным и выводным устройствам дл передачи данных, и может быть исползовано для первичной обработки данных, передаваемых по дискретным каналам передачи данных, в узлах обработки или узлах коммутации сообщений в АСУ или в сетях ЭВМ.

Известно устройство, предназначенное для предварительной обработки и обмена данными по дискретным каналам передачи Данных и между ЭВМ и используемое в узлах обработки данных или узлах коммутации сообщений в АСУ, Оно содержит блок управления, ПЗУ команд, арифметический блок, оперативный запоминающий блок блок регистров общего назначения, счетчик сдвигов, дешифратор нуля, регистр промежуточного результата, регистр результата, коммутатор и блок сумматоров по модулю два (1 .

Ввиду использования большого количества функциональных блоков различного назначения с большим числом связей ними данное устройство имеет большие габариты, низкую надежность и высокую стоимость.

Наиболее близким по сущности технического решения к изобретению является процесрор передачи данных, содержащий блок управления, включающий микропроцессор, а также тактовый генератор и узел управления доступом к шине, блок памяти программ буфер данных, генератор контрольной последовательности, вспомогательный блок управления, включающий таймер и задающий генератор скорости обмена данными, блок универсального синхро-асинхронного приемопередатчика, блок контроллера прерьгааний и блок программирзпощего сопряжения параллельным каналом 23,

Однако известный процессор передачи данных имеет низкое быстродействие вследствие того, что реализация функций управления передачей данных осуществляется только программным путем.

Цель изобретения - повьш1ение быстродействия устройства.

Указанная цель достигается тем, что устройство для управления обменом информации, содержащее прг емопередатчик, состоящий из элементов И, регистра признака, регистра байта данных, первого)-триггера, двух RS-триггеров, элемента ИЛИ, мульти5 плексора, первого счетчика и регистра сдвига, причем первый и второй входы первого элемента И являются соответственно входами старшего разряда адреса и записи устройства, а

0 выход соединен с первыми входами

второго и третьего элементов И, вторые входы которых объединены и являются входом младшего разряда адреса устройства, выходы второго и

5 третьего элементов И соединены с управляющими входами регистра признака и регистра байта- данных, информационные входы которых образуют вход данных устройства, а выходы соедине0 ны с информационными входами мультиплексора, выход которого соединен с информационным входом регистра сдвига, вход сброса устройства - с первым входом элемента ИЛИ,R -входом первого Р5-триггера и сбросовым входом первого счетчика, счетный вход которого и сдвиговый вход регистра сдвига соединены с выходом четвертого элемента И, первый вход которого соединен с выходом первого RS-триггера, 5-вход которого соединен с выходом первого элемента И, выходы третьего элемента И и элемента ИЛИ соединены с установочными входами

j первого D-триггера, прямой и инверсный выходы которого соединены с упра;вляющими входами мультиплексора

и установочными входами второго RS-триггера, С-вход которого и управляющий вход регистра сдвига соединены с первым выходом счегчика,

второй вь1ход которого соединен с

в-торым входом элемента ИЛИ, прямой выход первого D-триггера является выходом запроса передачи устройства, содержит пятый, шестой -и седьмой элементы И, вторыеD-триггер, элемент ИЛИ и счетчик, причем тактовый вход устройства соединен с С-входом второго D-триггера, первыминверсным входом пятого элемента И и инверсным входом шестого элемента.И, выход второго счетчика соединен с вторым инверсным входом пятого элемента И и инверсным входом седьмого элемента И, прямой вход которого соединен с выходом регистра сдвига, а выход - с прямым входом шестого элемента И,D-входом второго D-триггера и является информационным выходом устройства, инверсный выход второго Г-триггера соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с инверсным выходом второго RS-триггера, а выход - с входом сброса второго счетчика и 5-входом второгоD-триггера, выход пятого элемента И соединен с вторым входом четвертого элемента И вькод шестого элемента И - со счетным Входом второго счетчика.

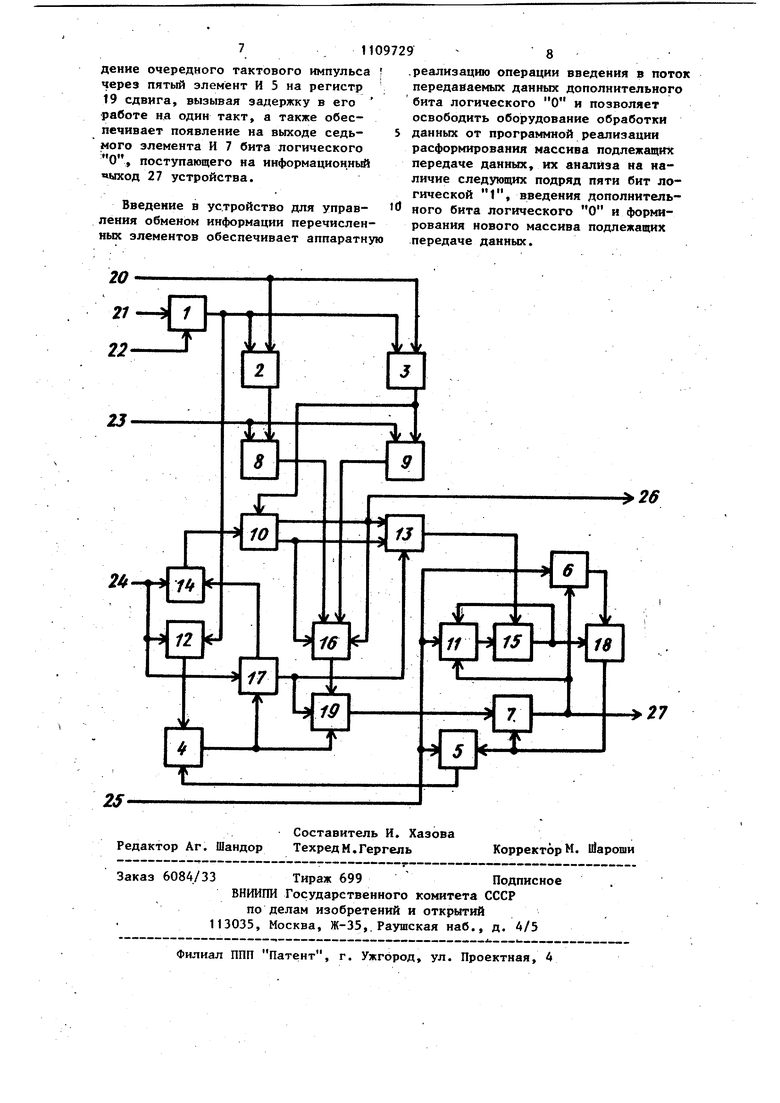

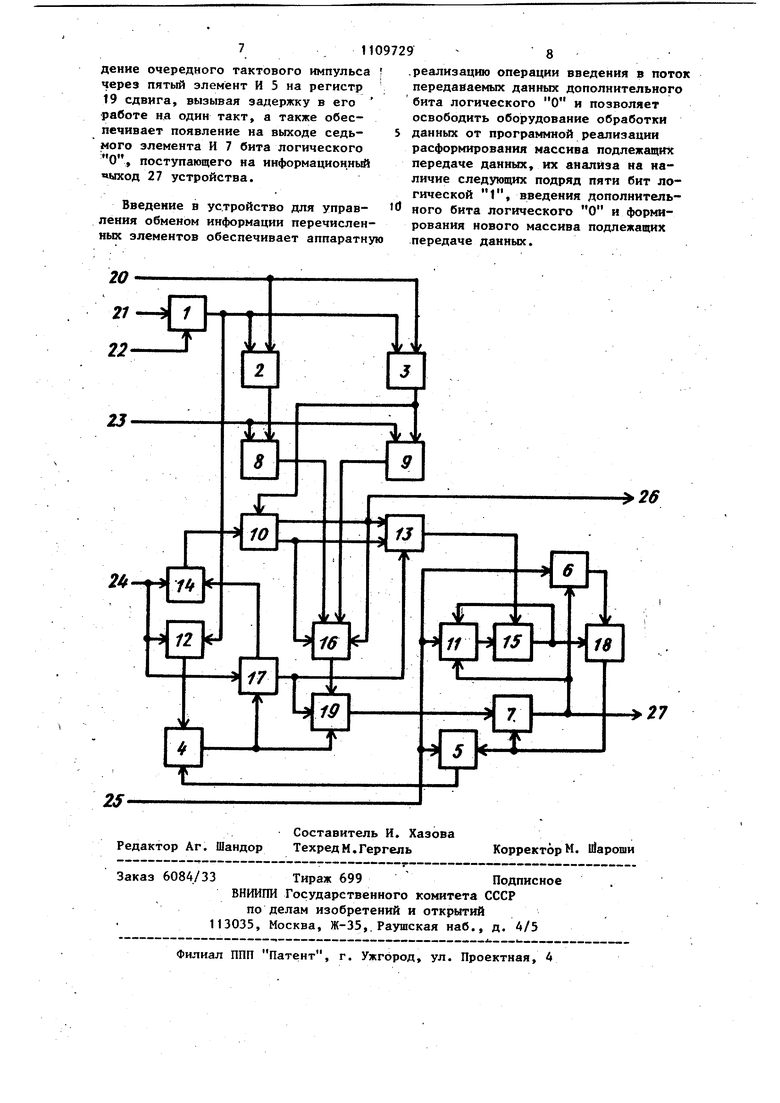

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит первый 1, второй 2, третий 3, четвертый 4, пятый 5, шестой 6 и седьмой 7 элементы И, регистр 8 признака, регистр 9 байта данных,первый 10 и второй 11 D-триггеры, первый R5-триггер 12, второй (тактируемый) RS-триггер 13, первый 14 и второй 15 элементы ИЛИ, мультиплексор 16, первый 17 и второй 18 (двоичные) счетчики, регистр 19 сдвига, вход 20 младшего разряда адреса, вход 21 старшего разряда адреса, вход 22 записи, входную шину 23 данных, вход 24 сброса, так товый вход 25, выход 26 запроса передачи и информационный выход 27 устройства.

Устройство работает следующим образом.

При инициализации работы устройства сигнал на выходе 24 сброса, поступающий на Р-вход первогоRS-тригера 12 и на сбросовый вход первого

счетчика 17, устанавливает их в исходное состояние. Одновременно положительный фронт этого сигнала, проходя через первый элемент ИМ 14 по его первому входу, поступает на С-вход первого 1)-триггера 10 и устанавливает его в исходное состояние

При загрузке в приемопередатчик признака, используемого для синхронизации передачи данных, на первый и второй вход|)1 первого элемента И 1 соответственно по входу 21 старшего разряда адреса и по входу 22 записи поступают сигналы, вызывающие появление положительного сигнала на его выходе. При этом сигнал на входе 20 младшего разряда адреса обеспечивает появление сигнала на выходе второго элемента И 2, что вызывает запись признака с входной шины 23 данных в регистр 8 признака. Состояние первого D-триггера 10 в этом случае обеспечивает посредством положительного сигнала на его инверсном выходе прохождение через мультиплексор 16 на информационный вход регистра 19 сдвига сигнала с выхода регистра 8 признака. Одновременно сигнал с выхода первого элемента И 1 устанавливает по 5-входу первый RS-триггер 12, что вызывает прохождение тактовых импульсов с выхода пятого элемента И 5 на второй вход четвертого элемента И 4.

Появление тактового импульса на выходе четвертого элемента И 4, связанном со счетным входом первого счетчика 17 и сдвиговым входом сдвигового регистра 19, вызывает изменение на 1 состояние счетчика 17 и появление сигнала на его первом выходе, связанном с управляющим входом регистра 19 сдвига и С-входом второгоRS-триггера 13. При этом обеспечивается параллельное занесение информации в регистр 19 сдвига с его информационного входа, а также тактирование второго RS-триггера 13, на выходе которого появляется сигнал, свидетельствующий о передаче на информационный выход 17 устройства признака, используемого для синхронизации передачи данных. Следующий тактовый импульс на тактовом входе 25 вызовет сдвиг на один разряд содержимого сдвигового регистра 19 и изменит состояние первого счетчика :17, второй выход которого связан с вторым входом первого элемента ИЛИ 14. Состояние счетчика 17 периодически повторяется через 8 тактевых импульсов на его счетном входе. Прямо ьыход первого Л-триггера to связан с выходом 26 запроса передачи устройства. Поэтому его установка по С-входу вызывает появление сигнала на выходе 26 запроса передачи, что приводит к загрузке в приемопередатчик очередного байта данных для передачи. При этом на выходе первого элемента И 1 вновь появится сигнал, вызьтающий совмест но с сигналом на входе 20 младшего разряда адреса запись байта данных с входной шины 23 данных в регистр 9 байта данных. Одновременно с этим по установочному входу ус танавливается первый Б-триггер 10, что снимает сигнал на выходе 26 запроса передачи устройства и обеспечивает прохожйение на выход мультиплексора 16 сигнала с выхода регист ра 9 байта данных. Завершелие передачи байта признака с выхода регистра 19 сдвига, вызываемое поступлением восьмого та тового импульса на его сдвиговый вход, одновременно приводит к появлению сигнала на первом выходе счет чика 17. При этом сигнал, присутств ющий на выходе мультиплексора 16, з носится в регистр 19 сдвига и однов ременно переключается второй Rs-три гер 13, снимая сигнал с его выхода свидетельствуя о передаче с выхода регистра 19 сдвига байта данных. Очередной тактовый импульс на выходе четвертого элемента Fi 4 вызывает сдвиг содержимого регистра 19 сдвига и изменение состояния первого счетчика 17. При этом сигнал на его втором выходе вызовет переключение первогоD-триггера 10 и появление сигнала на выходе 26 запроса передачи, после чего возможна загрузка в приемопередатчик очередного байта данных. I Если к моменту завершения переда чи с выхода регистра 19 сдвига последнего разряда передаваемого байт данных в регистр 9 байта данньпс не будет загружен новый байт данных, т через мультиплексор 16 в регистр 19 сдвига будет записан сигнал с выход регистра 8 признака, и работа устройства повторится. Появление сигнала на выходе второго RS-триггера 13, свидетельствующего о передаче с выхода регистра 19 сдвига байта признака и поступающего на второй вход второго элемента ИЛИ 15,- вызывает сброс второго счетчика 18 в исходное состояние. При этом обеспечивается прохождение тактовых импульсов с тактового входа 25 устройства через пятый элемент И 5 на второй вход четвертого элемента И 4, а также прохождение в последовательной форме байта признака с выхода сдвигового регистра 19 через седьмой элемент И 7 на информационный выход 27 устройства. В случае отсутствия сигнала на выходе второго КЗ-триггера 13, что свидетельствует о передаче с выхода сдвигового регистра 19 байта данных, который в последовательной форме поступает на прямой вход седьмого элемента И 7, второй счетчик 18 осуществляет подсчет бит данных, имеющих значение логической 1 и поСтзгаающих на информационный выход 27 устройства. Сигналы логической 1,поступая на прямой вход шестого элемента И 6 с информационного выхода 27 устройства, вызывают прохождение тактовых импульсов с тактового входа 25 устройства на выход шестого элемента И 6 и далее на счетный вход второго счетчика 18. Появление на информационном выходе 27 устройства бита логического О вызывает переключение второго В -триггера 11 с п1риходом тактового импульса на его С-вход и прохождение положительного сигнала через второй элемент ИЛИ 15 на сбросовый вход второго счетчика 18. При этом второй счетчик 18 переводится в исходное состояние. Одновременно по 5-входу устанавливается в исходное состояние второй D-триггер 11. Если результат подсчета меньше 5, байт данных в последовательной форме, поступает на прямой вход седьмого элемента И 7 и без изменения передается на информационный выход 27 устройства. При достижении вторым счетчиком 18 состояния, соответствующего прохождению на информационный выход 27 устройства пяти бит логической 1, сигнал с выхода второго счетчика 18 запрещает прохождение очередного тактового импульса через пятый элемент И 5 на регистр 19 сдвига, вызывая задержку в его работе на один такт, а также обеспечивает появление на выходе седьмого элемента И 7 бита логического О, поступающего на информацион.ный 27 устройства.

Введение в устройство для управления обменом информации перечисленных элементов обеспечивает аппаратную

.реализацию операции введения в пото передаваемых данных дополнительного бита логического О и позволяет освободить оборудование обработки данных от программной реализации расформирования массива подлежащих передаче данных, их анализа на наличие следующих подряд пяти бит логической 1, введения дополнительного бита логического О и формирования нового массива подлежащих передаче данных.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Процессор связи | 1976 |

|

SU682890A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство противодействия передаче информации управления несанкционированными устройствами | 2022 |

|

RU2813382C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-23—Публикация

1981-11-25—Подача