J

ел

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649506A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1476465A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммный модуль | 1986 |

|

SU1427366A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

Изобретение относится к автоматике и вычислительной технике. Оно может быть использовано в распределенных отказоустойчивых управляющих системах АСУТП, использующих программный принцип управления. Цель - повышение быстродействия и расширение области применения. Она достигается введением в модульное устройство программного Т-триггера 4 управления и контроля, мультиплексора 8 адресного кода управления, регистра-приемника 10 адресного кода управления, регистра 11 синхронизации, шестого, седьмого элемен

00

о

со

Ю

;о

СЛ

тов И регистра-передатчика адресного кода управления, регистра кода модулей адресатов адресного кода управления, счетчика ожидания передачи, IK-триггера, блока элементов И, блока элементов ИЛИ. Сущность изобретения заключается в том, что за счет введения новых элементов и их связей, которые позволяют обеспечить асинхронную выдачу модулем управляющих сигналов, обеспечить возможность ожидания и передачи управляюИзобретение относится к области автоматики и вычислительной техники. Оно может быть использовано в распределенных отказоустойчивых управляющих системах АСУ, ТП, использующих программный принцип управления, с большим числом контролируемых параметров, допускающих наращивание при расширении числа выполняемых функций.

Целью изобретения является повышение быстродействия и расширение области применения.

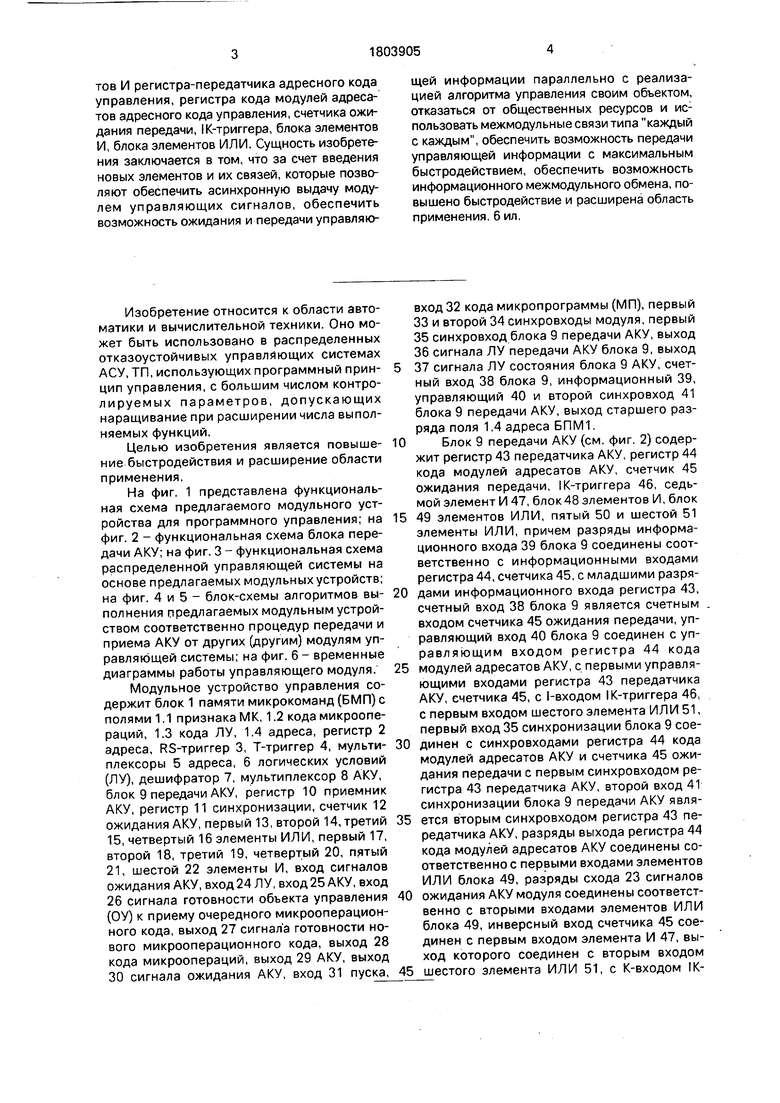

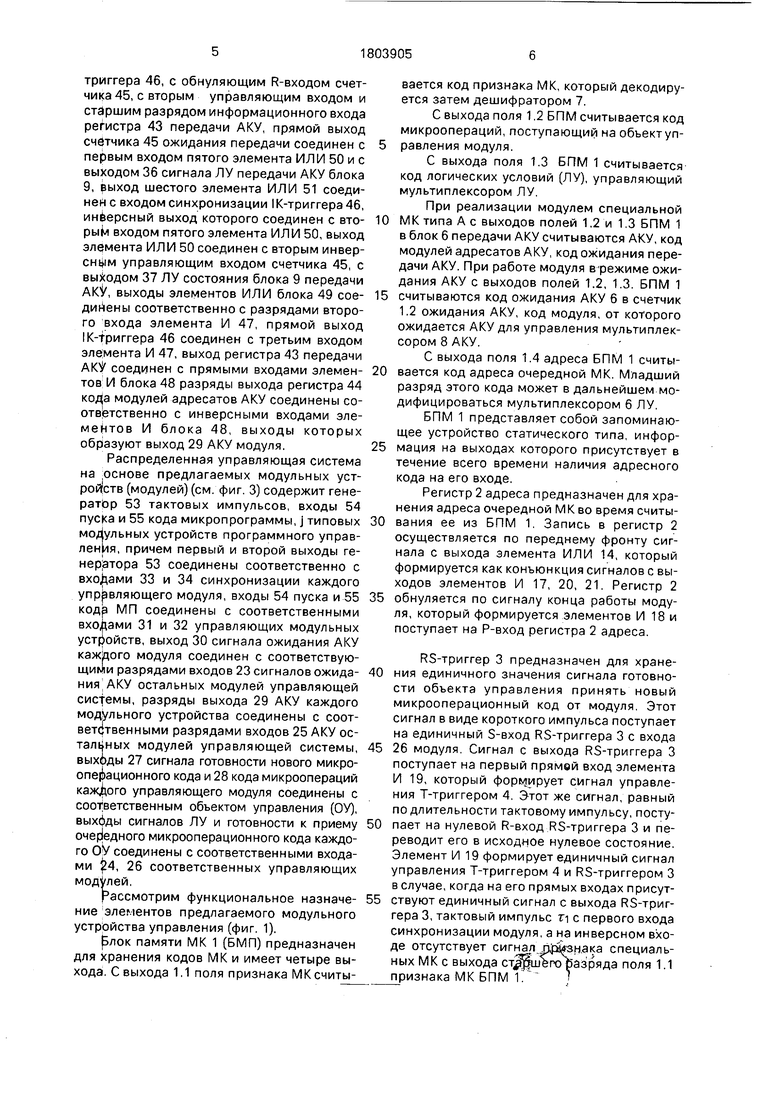

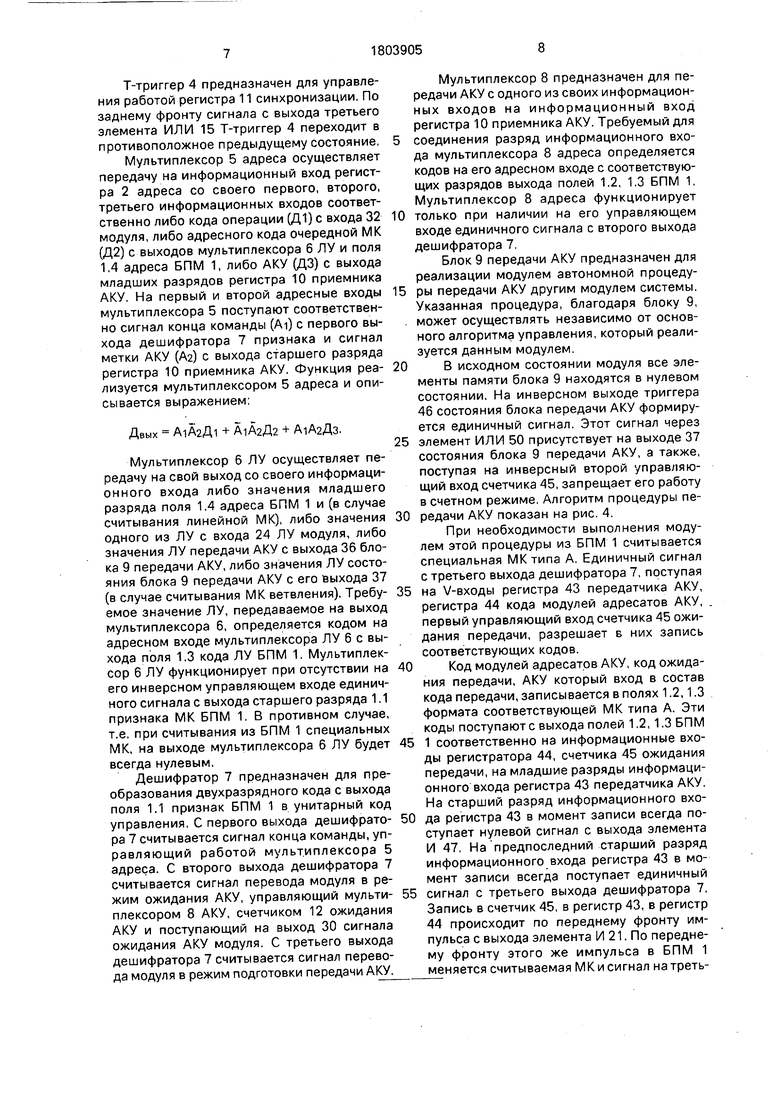

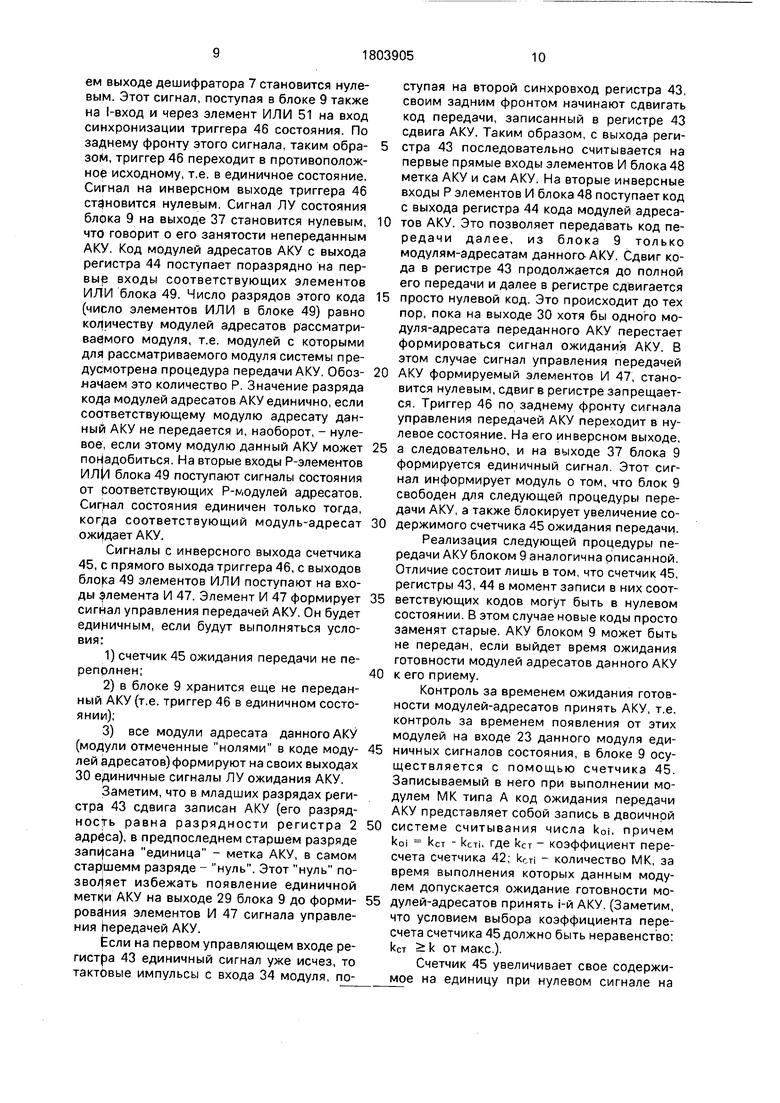

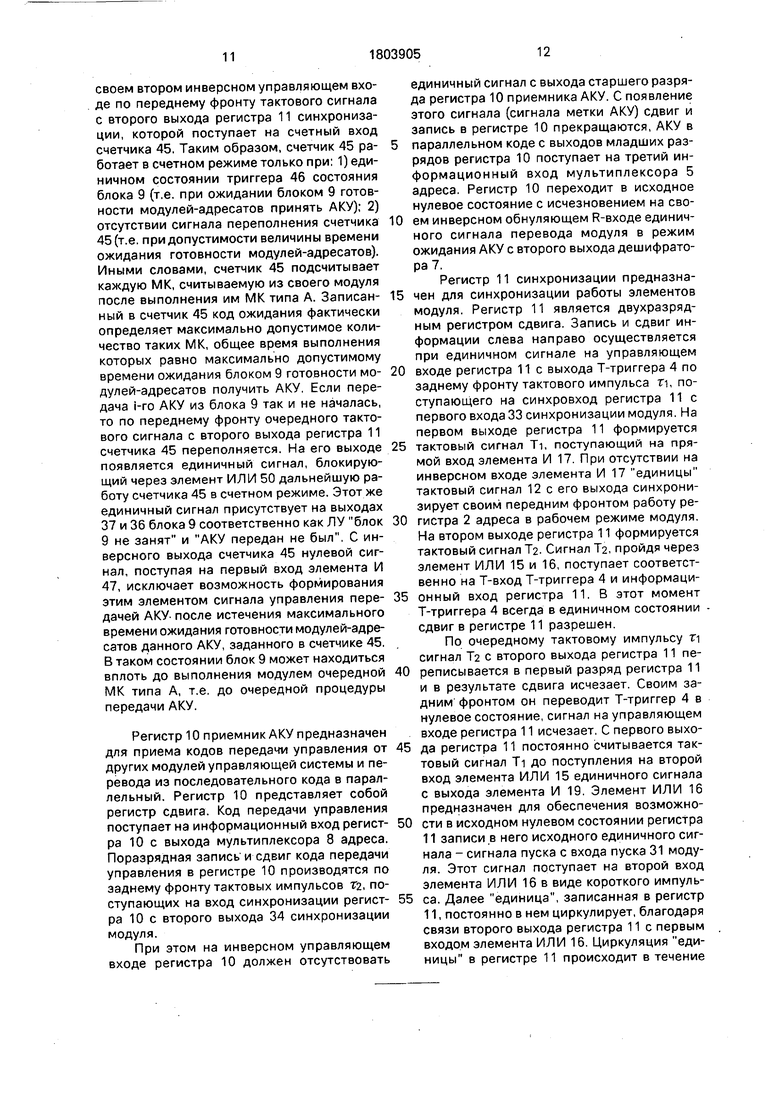

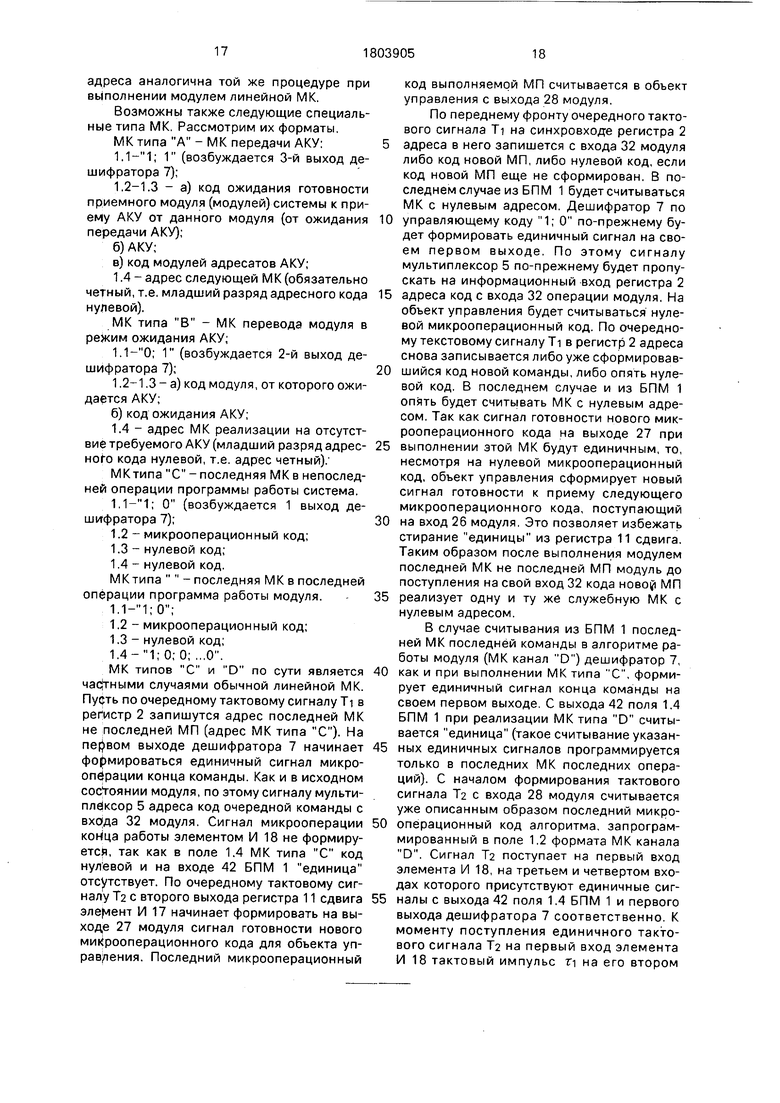

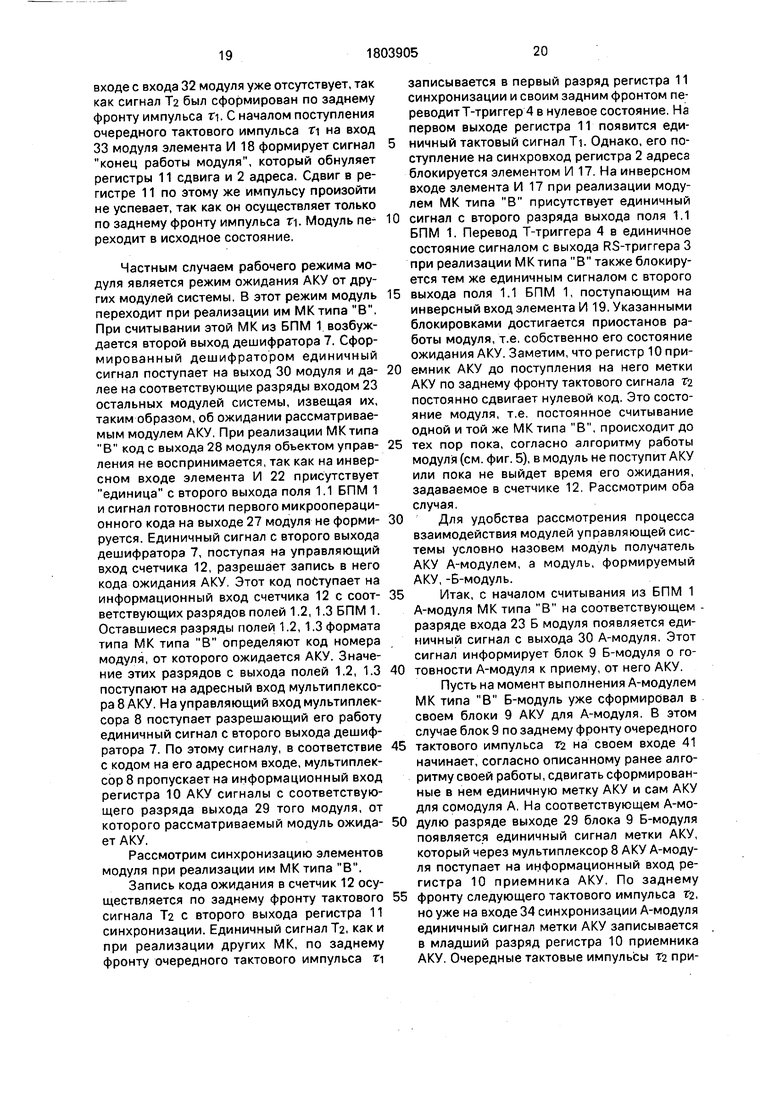

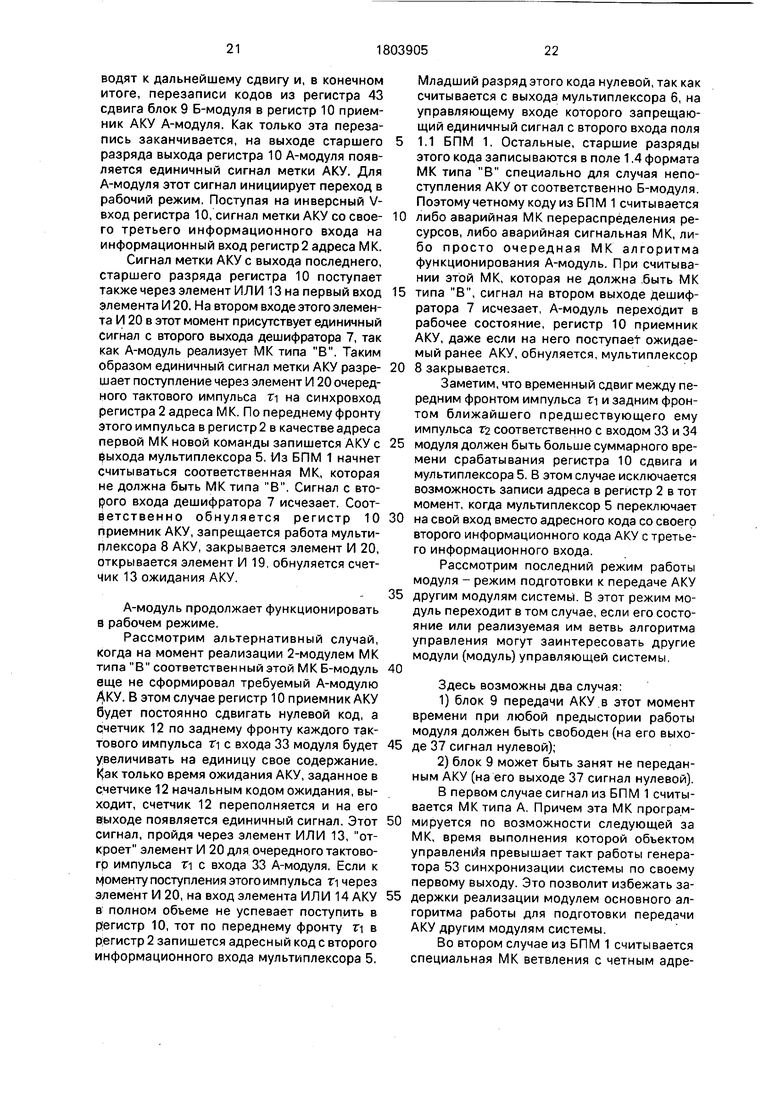

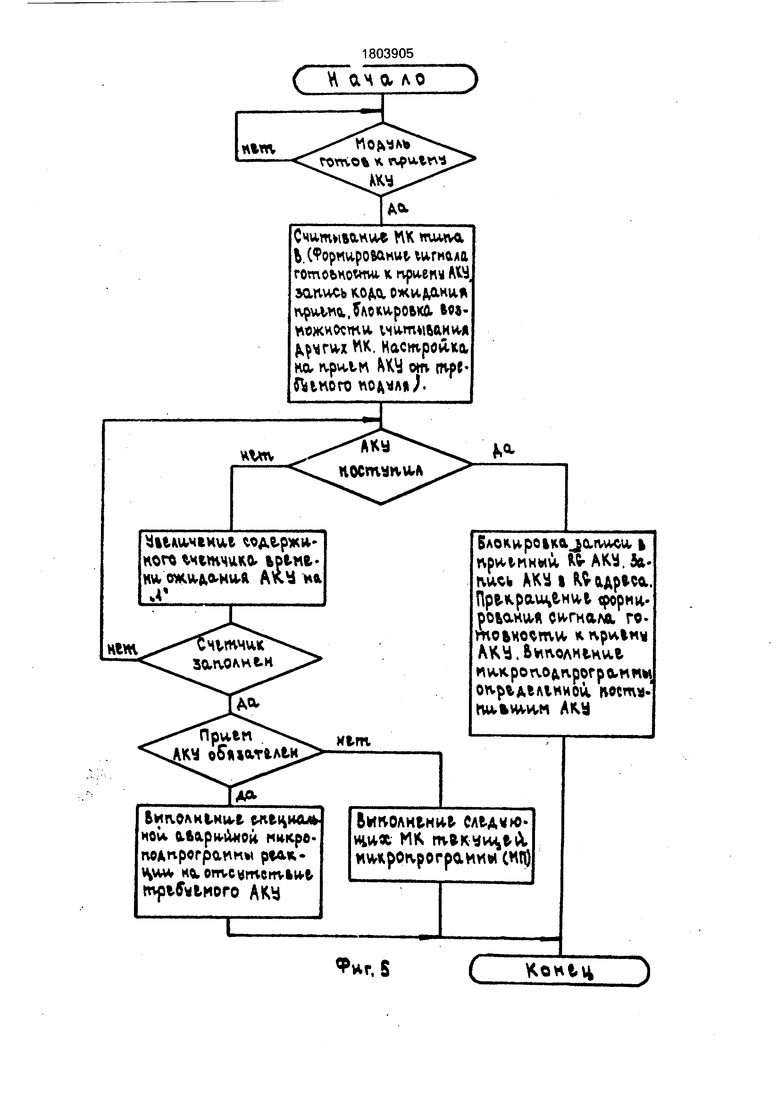

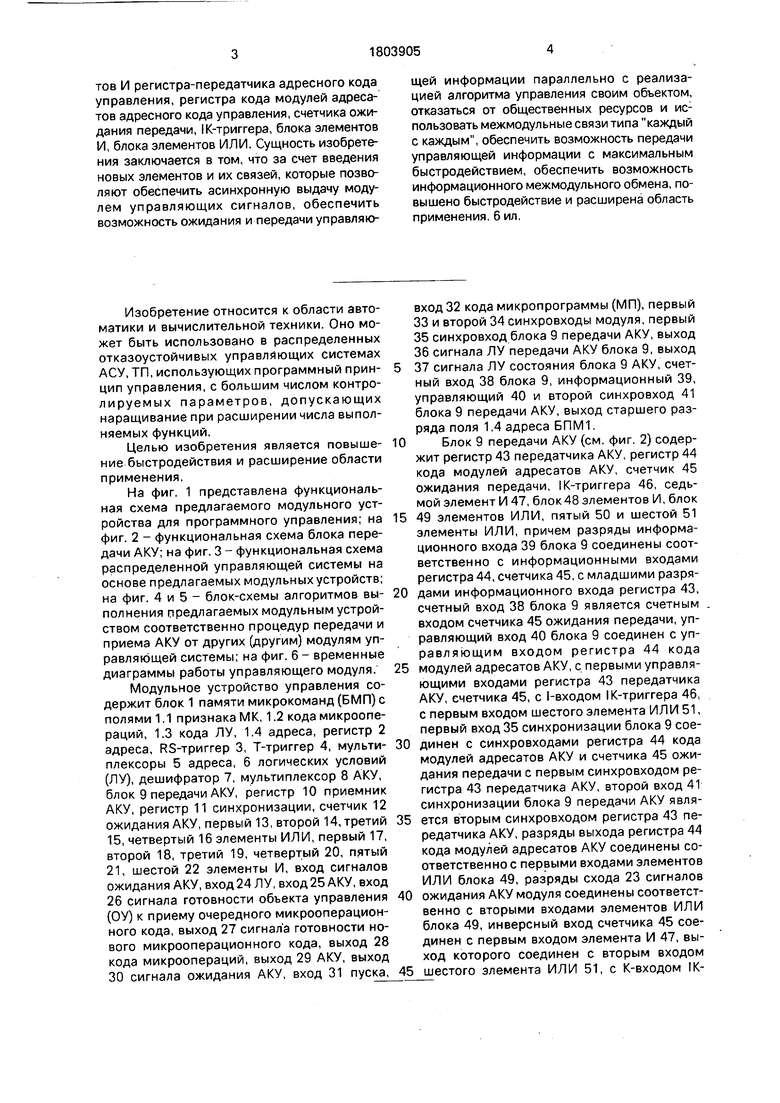

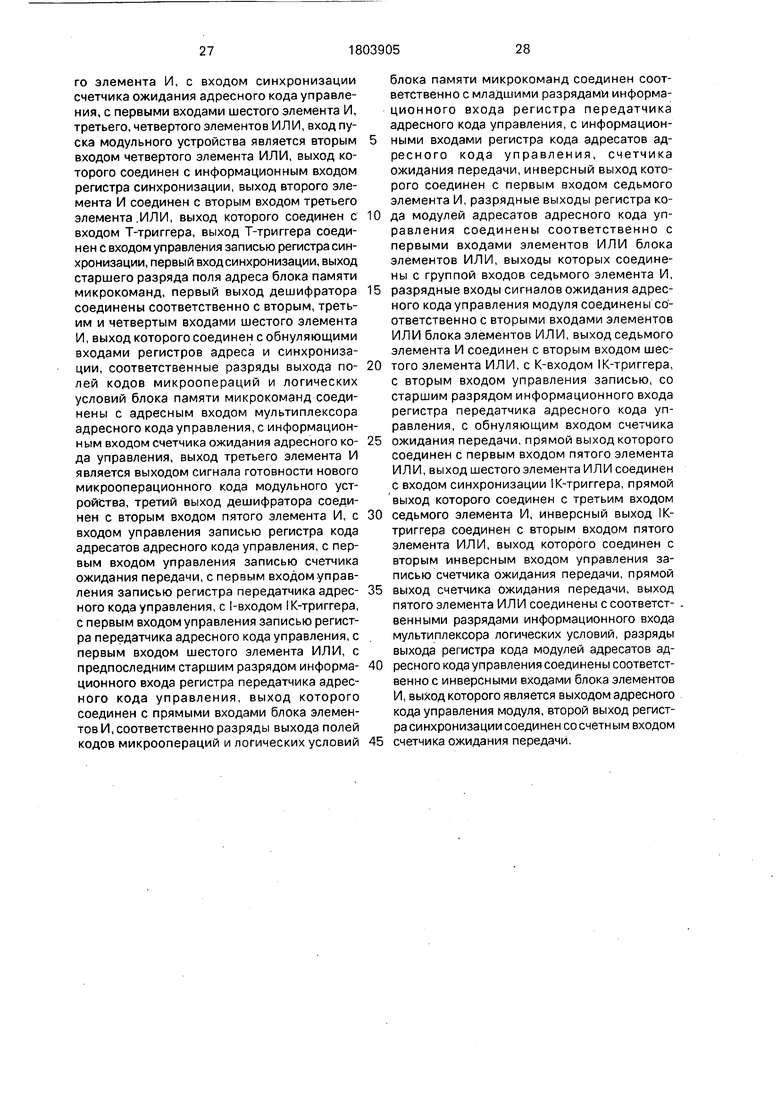

На фиг. 1 представлена функциональная схема предлагаемого модульного устройства для программного управления; на фиг. 2 - функциональная схема блока передачи АКУ; на фиг. 3 - функциональная схема распределенной управляющей системы на основе предлагаемых модульных устройств; на фиг. 4 и 5 - блок-схемы алгоритмов выполнения предлагаемых модульным устройством соответственно процедур передачи и приема АКУ от других (другим) модулям управляющей системы; на фиг. 6 - временные диаграммы работы управляющего модуля.

Модульное устройство управления содержит блок 1 памяти микрокоманд (БМП) с полями 1.1 признака МК, 1.2 кода микроопераций, 1.3 кода ЛУ, 1.4 адреса, регистр 2 адреса, RS-триггер З, Т-триггер 4, мультиплексоры 5 адреса, 6 логических условий (ЛУ), дешифратор 7, мультиплексор 8 АКУ, блок 9 передачи АКУ, регистр 10 приемник АКУ, регистр 11 синхронизации, счетчик 12 ожидания АКУ, первый 13, второй 14, третий 15, четвертый 16 элементы ИЛИ, первый 17, второй 18, третий 19, четвертый 20, пятый 21, шестой 22 элементы И, вход сигналов ожидания АКУ, вход 24 Л У, вход 25 АКУ, вход 26 сигнала готовности объекта управления (ОУ) к приему очередного микрооперационного кода, выход 27 сигнала готовности нового микрооперационного кода, выход 28 кода микроопераций, выход 29 АКУ, выход 30 сигнала ожидания АКУ, вход 31 пуска,

щей информации параллельно с реализацией алгоритма управления своим объектом, отказаться от общественных ресурсов и использовать межмодульные связи типа каждый с каждым, обеспечить возможность передачи управляющей информации с максимальным быстродействием, обеспечить возможность информационного межмодульного обмена, повышено быстродействие и расширена область применения, 6 ил.

вход 32 кода микропрограммы (МП), первый 33 и второй 34 синхровходы модуля, первый

35 синхровход блока 9 передачи АКУ, выход

36 сигнала ЛУ передачи АКУ блока 9, выход

37 сигнала ЛУ состояния блока 9 АКУ, счетный вход 38 блока 9, информационный 39, управляющий 40 и второй синхровход 41 блока 9 передачи АКУ, выход старшего разряда поля 1.4 адреса БПМ1.

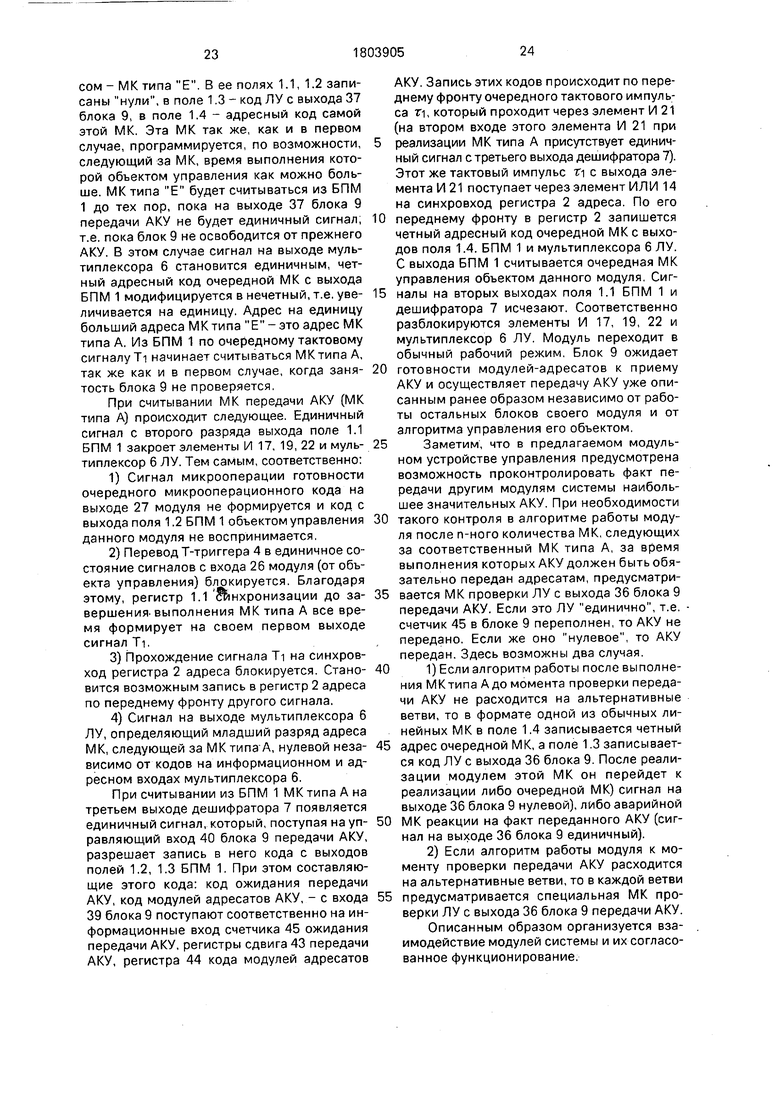

Блок 9 передачи АКУ (см. фиг. 2) содержит регистр 43 передатчика АКУ, регистр 44 кода модулей адресатов АКУ, счетчик 45 ожидания передачи, IK-триггера 46, седьмой элемент И 47, блок48 элементов И, блок

49 элементов ИЛИ, пятый 50 и шестой 51 элементы ИЛИ, причем разряды информационного входа 39 блока 9 соединены соответственно с информационными входами регистра 44, счетчика 45, с младшими разрядами информационного входа регистра 43, счетный вход 38 блока 9 является счетным входом счетчика 45 ожидания передачи, управляющий вход 40 блока 9 соединен с управляющим входом регистра 44 кода

модулей адресатов АКУ, с первыми управляющими входами регистра 43 передатчика АКУ, счетчика 45, с 1-входом IK-триггера 46, с первым входом шестого элемента ИЛИ 51, первый вход 35 синхронизации блока 9 соединен с синхровходами регистра 44 кода модулей адресатов АКУ и счетчика 45 ожидания передачи с первым синхровходом регистра 43 передатчика АКУ, второй вход 41 синхронизации блока 9 передачи АКУ является вторым синхровходом регистра 43 передатчика АКУ, разряды выхода регистра 44 кода модулей адресатов АКУ соединены соответственно с первыми входами элементов ИЛИ блока 49, разряды схода 23 сигналов

ожидания АКУ модуля соединены соответственно с вторыми входами элементов ИЛИ блока 49, инверсный вход счетчика 45 соединен с первым входом элемента И 47, выход которого соединен с вторым входом

шестого элемента ИЛИ 51, с К-входом IKтриггера 46, с обнуляющим R-входом счетчика 45, с вторым управляющим входом и старшим разрядом информационного входа регистра 43 передачи АКУ, прямой выход счетчика 45 ожидания передачи соединен с первым входом пятого элемента ИЛИ 50 и с выходом 36 сигнала ЛУ передачи АКУ блока 9, выход шестого элемента ИЛИ 51 соединен с входом синхронизации К-триггера46, инверсный выход которого соединен с вто- рым входом пятого элемента ИЛИ 50, выход элемента ИЛИ 50 соединен с вторым инверсным управляющим входом счетчика 45, с выходом 37 ЛУ состояния блока 9 передачи АКУ, выходы элементов ИЛИ блока 49 сое- динены соответственно с разрядами второго входа элемента И 47, прямой выход IK-триггера 46 соединен с третьим входом элемента И 47, выход регистра 43 передачи АКУ соединен с прямыми входами элемен- тов И блока 48 разряды выхода регистра 44 код;а модулей адресатов АКУ соединены со- отв|етственно с инверсными входами элементов И блока 48, выходы которых образуют выход 29 АКУ модуля.

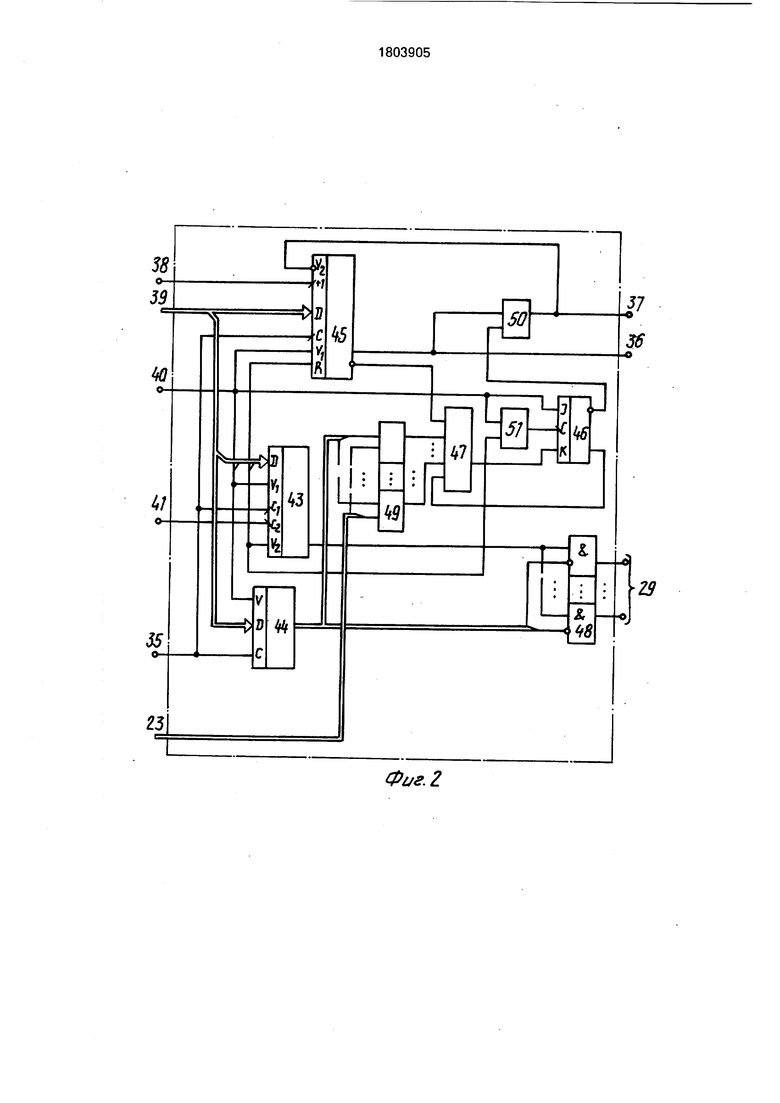

Распределенная управляющая система на основе предлагаемых модульных устройств (модулей) (см. фиг. 3) содержит генератор 53 тактовых импульсов, входы 54 пуска и 55 кода микропрограммы, j типовых модульных устройств программного управления, причем первый и второй выходы ге- нер;атора 53 соединены соответственно с входами 33 и 34 синхронизации каждого управляющего модуля, входы 54 пуска и 55 кодр МП соединены с соответственными входами 31 и 32 управляющих модульных устройств, выход 30 сигнала ожидания АКУ каждого модуля соединен с соответствующими разрядами входов 23 сигналов ожида- ния АКУ остальных модулей управляющей системы, разряды выхода 29 АКУ каждого модульного устройства соединены с соответственными разрядами входов 25 АКУ ос- талцных модулей управляющей системы, выходы 27 сигнала готовности нового микро- опе ационного кода и 28 кода микроопераций каждого управляющего модуля соединены с соответственным объектом управления (ОУ), выхфды сигналов ЛУ и готовности к приему очередного микрооперационного кода каждого ОУ соединены с соответственными входами $4, 26 соответственных управляющих моделей.

рассмотрим функциональное назначе- ние элементов предлагаемого модульного устройства управления (фиг. 1).

БЛОК памяти МК 1 (БМП) предназначен для хранения кодов МК и имеет четыре выхода. С выхода 1,1 поля признака МК считывается код признака МК, который декодируется затем дешифратором 7.

С выхода поля 1.2 БПМ считывается код микроопераций, поступающий на объект управления модуля.

С выхода поля 1.3 БПМ 1 считывается код логических условий (ЛУ), управляющий мультиплексором ЛУ.

При реализации модулем специальной МК типа А с выходов полей 1,2 и 1.3 БПМ 1 в блок 6 передачи АКУ считываются АКУ, код модулей адресатов АКУ, код ожидания передачи АКУ. При работе модуля врежиме ожидания АКУ с выходов полей 1.2, 1.3. БПМ 1 считываются код ожидания АКУ 6 в счетчик 1.2 ожидания АКУ, код модуля, от которого ожидается АКУ для управления мультиплексором 8 АКУ.

С выхода поля 1.4 адреса БПМ 1 считывается код адреса очередной МК. Младший разряд этого кода может в дальнейшем модифицироваться мультиплексором 6 ЛУ.

БПМ 1 представляет собой запоминающее устройство статического типа, информация на выходах которого присутствует в течение всего времени наличия адресного кода на его входе.

Регистр 2 адреса предназначен для хранения адреса очередной МК во время считывания ее из БПМ 1. Запись в регистр 2 осуществляется по переднему фронту сигнала с выхода элемента ИЛИ 14, который формируется как конъюнкция сигналов с выходов элементов И 17, 20, 21. Регистр 2 обнуляется по сигналу конца работы модуля, который формируется элементов И 18 и поступает на Р-вход регистра 2 адреса.

RS-триггер З предназначен для хранения единичного значения сигнала готовности объекта управления принять новый микрооперационный код от модуля. Этот сигнал в виде короткого импульса поступает на единичный S-вход RS-триггера З с входа 26 модуля. Сигнал с выхода RS-триггера З поступает на первый прямдй вход элемента И 19, который формирует сигнал управления Т-триггером 4. Этот же сигнал, равный по длительности тактовому импульсу, поступает на нулевой R-вход RS-триггера З и переводит его в исходное нулевое состояние. Элемент И 19 формирует единичный сигнал управления Т-триггером 4 и RS-триггером З в случае, когда на его прямых входах присутствуют единичный сигнал с выхода RS-триггера 3, тактовый импульс т- с первого входа синхронизации модуля, а на инверсном входе отсутствует сигнал лда43н.ака специальных МК с выхода {Заз р яда поля 1.1 признака МК БПМ 1.)

Т-триггер 4 предназначен для управления работой регистра 11 синхронизации, По заднему фронту сигнала с выхода третьего элемента ИЛИ 15 Т-триггер 4 переходит в противоположное предыдущему состояние,

Мультиплексор 5 адреса осуществляет передачу на информационный вход регистра 2 адреса со своего первого, второго, третьего информационных входов соответственно либо кода операции (Д1) с входа 32 модуля, либо адресного кода очередной МК (Д2) с выходов мультиплексора 6 ЛУ и поля 1,4 адреса БПМ 1, либо АКУ (ДЗ) с выхода младших разрядов регистра 10 приемника АКУ. На первый и второй адресные входы мультиплексора 5 поступают соответственно сигнал конца команды (Ач) с первого выхода дешифратора 7 признака и сигнал метки АКУ (А2) с выхода старшего разряда регистра 10 приемника АКУ. Функция pea- лизуется мультиплексором 5 адреса и описывается выражением:

Двых AiAaAl + А1А2Д2 + А1А2ДЗ.

Мультиплексор б ЛУ осуществляет передачу на свой выход со своего информационного входа либо значения младшего разряда поля 1.4 адреса БПМ 1 и (в случае считывания линейной МК), либо значения одного из ЛУ с входа 24 ЛУ модуля, либо значения ЛУ передачи АКУ с выхода 36 блока 9 передачи АКУ, либо значения ЛУ состояния блока 9 передачи АКУ с его выхода 37 (в случае считывания МК ветвления). Требу- емое значение ЛУ, передаваемое на выход мультиплексора 6, определяется кодом на адресном входе мультиплексора ЛУ б с выхода поля 1.3 кода ЛУ БПМ 1. Мультиплексор 6 ЛУ функционирует при отсутствии на его инверсном управляющем входе единичного сигнала с выхода старшего разряда 1.1 признака МК БПМ 1. В противном случае, т.е. при считывания из БПМ 1 специальных МК, на выходе мультиплексора 6 ЛУ будет всегда нулевым.

Дешифратор 7 предназначен для преобразования двухразрядного кода с выхода поля 1.1 признак БПМ 1 в унитарный код управления, С первого выхода дешифрато- ра 7 считывается сигнал конца команды, управляющий работой мультиплексора 5 адреса. С второго выхода дешифратора 7 считывается сигнал перевода модуля в режим ожидания АКУ, управляющий мульти- плексором 8 АКУ, счетчиком 12 ожидания АКУ и поступающий на выход 30 сигнала ожидания АКУ модуля. С третьего выхода дешифратора 7 считывается сигнал перевода модуля в режим подготовки передачи АКУ.

0 5 0

5

0 5 0 5

0 5

Мультиплексор 8 предназначен для передачи АКУ с одного из своих информационных входов на информационный вход регистра 10 приемника АКУ. Требуемый для соединения разряд информационного входа мультиплексора 8 адреса определяется кодов на его адресном входе с соответствующих разрядов выхода полей 1.2, 1.3 БПМ 1, Мультиплексор 8 адреса функционирует только при наличии на его управляющем входе единичного сигнала с второго выхода дешифратора 7.

Блок 9 передачи АКУ предназначен для реализации модулем автономной процедуры передачи АКУ другим модулем системы. Указанная процедура, благодаря блоку 9, может осуществлять независимо от основного алгоритма управления, который реализуется данным модулем.

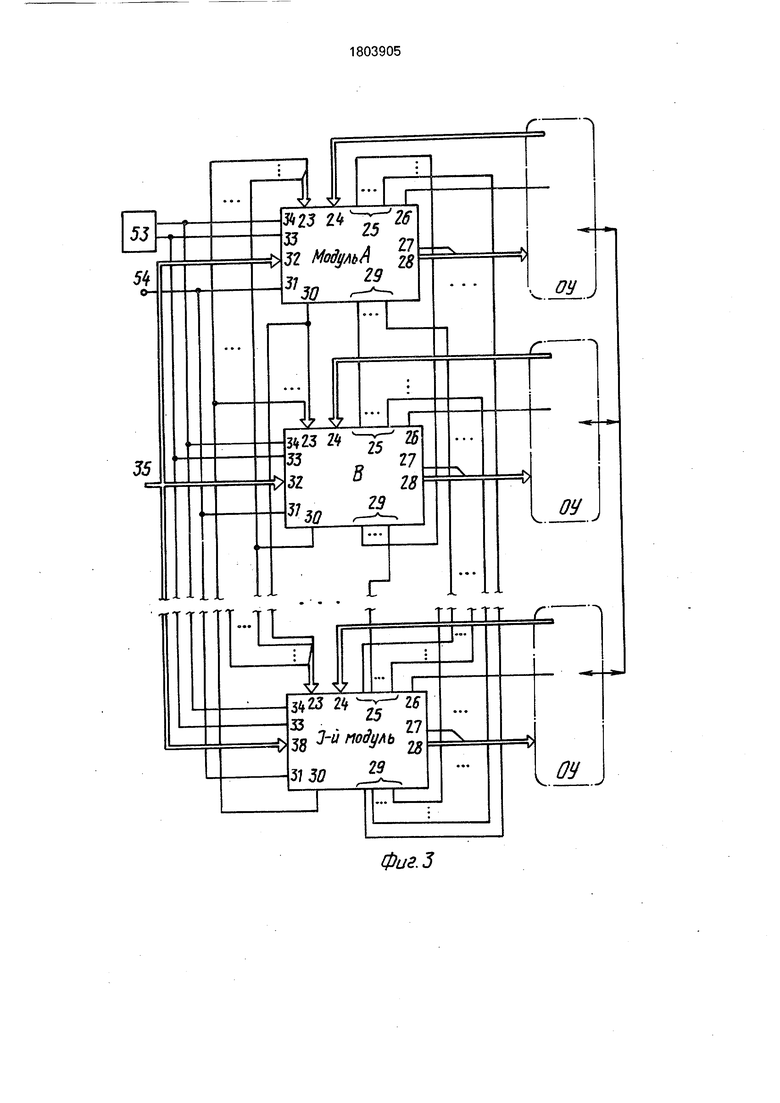

В исходном состоянии модуля все элементы памяти блока 9 находятся в нулевом состоянии. На инверсном выходе триггера 46 состояния блока передачи АКУ формируется единичный сигнал. Этот сигнал через элемент ИЛИ 50 присутствует на выходе 37 состояния блока 9 передачи АКУ, а также, поступая на инверсный второй управляющий вход счетчика 45, запрещает его работу в счетном режиме. Алгоритм процедуры передачи АКУ показан на рис. 4.

При необходимости выполнения модулем этой процедуры из БПМ 1 считывается специальная МКтипа А. Единичный сигнал с третьего выхода дешифратора 7, поступая на V-входы регистра 43 передатчика АКУ, регистра 44 кода модулей адресатов АКУ, первый управляющий вход счетчика 45 ожидания передачи, разрешает в них запись соответствующих кодов.

Код модулей адресатов АКУ, код ожидания передачи, АКУ который вход в состав кода передачи, записывается в полях 1.2,1.3 формата соответствующей МК типа А. Эти коды поступают с выхода полей 1,2, 1.3 БПМ 1 соответственно на информационные входы регистратора 44, счетчика 45 ожидания передачи, на младшие разряды информационного входа регистра 43 передатчика АКУ. На старший разряд информационного входа регистра 43 в момент записи всегда поступает нулевой сигнал с выхода элемента И 47, На предпоследний старший разряд информационного входа регистра 43 в момент записи всегда поступает единичный сигнал с третьего выхода дешифратора 7. Запись в счетчик 45, в регистр 43, в регистр 44 происходит по переднему фронту импульса с выхода элемента И 21. По переднему фронту этого же импульса в БПМ 1 меняется считываемая МК и сигнал на третьем выходе дешифратора 7 становится нулевым. Этот сигнал, поступая в блоке 9 также на 1-вход и через элемент ИЛИ 51 на вход синхронизации триггера 46 состояния. По заднему фронту этого сигнала, таким образом, триггер 46 переходит в противоположное исходному, т.е. в единичное состояние. Сигнал на инверсном выходе триггера 46 становится нулевым. Сигнал ЛУ состояния блока 9 на выходе 37 становится нулевым, что говорит о его занятости непереданным АКУ. Код модулей адресатов АКУ с выхода регистра 44 поступает поразрядно на первые входы соответствующих элементов ИЛИ блока 49. Число разрядов этого кода (число элементов ИЛИ в блоке 49) равно количеству модулей адресатов рассматриваемого модуля, т.е. модулей с которыми для рассматриваемого модуля системы предусмотрена процедура передачи АКУ. Обозначаем это количество Р, Значение разряда кода модулей адресатов АКУ единично, если соответствующему модулю адресату данный АКУ не передается и, наоборот, - нулевое, если этому модулю данный АКУ может понадобиться. На вторые входы Р-элементов ИЛИ блока 49 поступают сигналы состояния от соответствующих Р-модулей адресатов. Сигнал состояния единичен только тогда, когда соответствующий модуль-адресат ожидает АКУ.

Сигналы с инверсного выхода счетчика 45, с прямого выхода триггера 46, с выходов блока 49 элементов ИЛИ поступают на входы элемента И 47. Элемент И 47 формирует сигнал управления передачей АКУ. Он будет единичным, если будут выполняться условия:

1) счетчик 45 ожидания передачи не переполнен;

2) в блоке 9 хранится еще не переданный АКУ (т.е. триггер 46 в единичном состоянии);

3) все модули адресата данного АКУ (модули отмеченные нолями в коде модулей адресатов) формируют на своих выходах 30 единичные сигналы ЛУ ожидания АКУ.

Заметим, что в младших разрядах регистра 43 сдвига записан АКУ (его разрядность равна разрядности регистра 2 адреса), в предпоследнем старшем разряде записана единица - метка АКУ, в самом стар|шемм разряде - нуль. Этот нуль позволяет избежать появление единичной метки АКУ на выходе 29 блока 9 до формирования элементов И 47 сигнала управления Передачей АКУ.

Если на первом управляющем входе регистра 43 единичный сигнал уже исчез, то тактовые импульсы с входа 34 модуля, поступая на второй синхровход регистра 43, своим задним фронтом начинают сдвигать код передачи, записанный в регистре 43 сдвига АКУ. Таким образом, с выхода регистра 43 последовательно считывается на первые прямые входы элементов И блока 48 метка АКУ и сам АКУ. На вторые инверсные входы Р элементов И блока 48 поступает код с выхода регистра 44 кода модулей адреса0 тов АКУ. Это позволяет передавать код передачи далее, из блока 9 только модулям-адресатам данного-АКУ. Сдвиг кода в регистре 43 продолжается до полной его передачи и далее в регистре сдвигается

5 просто нулевой код. Это происходит до тех пор, пока на выходе 30 хотя бы одного модуля-адресата переданного АКУ перестает формироваться сигнал ожидания АКУ. В этом случае сигнал управления передачей

0 АКУ формируемый элементов И 47, становится нулевым, сдвиг в регистре запрещается. Триггер 46 по заднему фронту сигнала управления передачей АКУ переходит в нулевое состояние. На его инверсном выходе,

5 а следовательно, и на выходе 37 блока 9 формируется единичный сигнал. Этот сигнал информирует модуль о том, что блок 9 свободен для следующей процедуры передачи АКУ, а также блокирует увеличение со0 держимого счетчика 45 ожидания передачи. Реализация следующей процедуры передачи АКУ блоком 9 аналогична описанной. Отличие состоит лишь в том, что счетчик 45, регистры 43, 44 в момент записи в них соот5 ветствующих кодов могут быть в нулевом состоянии. В этом случае новые коды просто заменят старые. АКУ блоком 9 может быть не передан, если выйдет время ожидания готовности модулей адресатов данного АКУ

0 к его приему.

Контроль за временем ожидания готовности модулей-адресатов принять АКУ, т.е. контроль за временем появления от этих модулей на входе 23 данного модуля еди5 ничных сигналов состояния, в блоке 9 осуществляется с помощью счетчика 45. Записываемый в него при выполнении модулем МК типа А код ожидания передачи АКУ представляет собой запись в двоичной

0 системе считывания числа k0i, причем koi kcr - kcri, где kcr - коэффициент пересчета счетчика 42; kcri - количество МК, за время выполнения которых данным модулем допускается ожидание готовности мо5 дулей-адресатов принять i-й АКУ. (Заметим, что условием выбора коэффициента пересчета счетчика 45 должно быть неравенство: kCT k от макс.).

Счетчик 45 увеличивает свое содержи- мое на единицу при нулевом сигнале на

своем втором инверсном управляющем входе по переднему фронту тактового сигнала с второго выхода регистра 11 синхронизации, которой поступает на счетный вход счетчика 45. Таким образом, счетчик 45 работает в счетном режиме только при: 1) единичном состоянии триггера 46 состояния блока 9 (т.е. при ожидании блоком 9 готовности модулей-адресатов принять АКУ); 2) отсутствии сигнала переполнения счетчика 45 (т.е. при допустимости величины времени ожидания готовности модулей-адресатов). Иными словами, счетчик 45 подсчитывает каждую МК, считываемую из своего модуля после выполнения им МК типа А. Записанный в счетчик 45 код ожидания фактически определяет максимально допустимое количество таких МК, общее время выполнения которых равно максимально допустимому времени ожидания блоком 9 готовности модулей-адресатов получить АКУ. Если передача i-ro АКУ из блока 9 так и не началась, то по переднему фронту очередного тактового сигнала с второго выхода регистра 11 счетчика 45 переполняется. На его выходе появляется единичный сигнал, блокирующий через элемент ИЛИ 50 дальнейшую работу счетчика 45 в счетном режиме. Этот же единичный сигнал присутствует на выходах 37 и 36 блока 9 соответственно как ЛУ блок 9 не занят и АКУ передан не был, С инверсного выхода счетчика 45 нулевой сигнал, поступая на первый вход элемента И 47, исключает возможность формирования этим элементом сигнала управления передачей АКУ- после истечения максимального времени ожидания готовности модулей-адресатов данного АКУ, заданного в счетчике 45. В таком состоянии блок 9 может находиться вплоть до выполнения модулем очередной МК типа А, т.е. до очередной процедуры передачи АКУ.

Регистр 10 приемник АКУ предназначен для приема кодов передачи управления от других модулей управляющей системы и перевода из последовательного кода в параллельный. Регистр 10 представляет собой регистр сдвига. Код передачи управления поступает на информационный вход регистра 10 с выхода мультиплексора 8 адреса. Поразрядная запись и сдвиг кода передачи управления в регистре 10 производятся по заднему фронту тактовых импульсов Та, поступающих на вход синхронизации регистра 10 с второго выхода 34 синхронизации модуля.

При этом на инверсном управляющем входе регистра 10 должен отсутствовать

единичный сигнал с выхода старшего разряда регистра 10 приемника АКУ. С появление этого сигнала (сигнала метки АКУ) сдвиг и запись в регистре 10 прекращаются, АКУ в

параллельном коде с выходов младших разрядов регистра 10 поступает на третий информационный вход мультиплексора 5 адреса. Регистр 10 переходит в исходное нулевое состояние с исчезновением на своем инверсном обнуляющем R-входе единичного сигнала перевода модуля в режим ожидания АКУ с второго выхода дешифратора 7.

Регистр 11 синхронизации предназначен для синхронизации работы элементов модуля. Регистр 11 является двухразрядным регистром сдвига. Запись и сдвиг информации слева направо осуществляется при единичном сигнале на управляющем

входе регистра 11с выхода Т-триггера 4 по заднему фронту тактового импульса п, поступающего на синхровход регистра 11 с первого входа 33 синхронизации модуля. На первом выходе регистра 11 формируется

тактовый сигнал Ti, поступающий на прямой вход элемента И 17. При отсутствии на инверсном входе элемента И 17 единицы тактовый сигнал 12 с его выхода синхронизирует своим передним фронтом работу регистра 2 адреса в рабочем режиме модуля. На втором выходе регистра 11 формируется тактовый сигнал Та. Сигнал Та, пройдя через элемент ИЛИ 15 и 16, поступает соответственно на Т-вход Т-триггера 4 и информационный вход регистра 11. В этот момент Т-триггера 4 всегда в единичном состоянии сдвиге регистре 11 разрешен.

По очередному тактовому импульсу т сигнал Та с второго выхода регистра 11 переписывается в первый разряд регистра 11 и в результате сдвига исчезает. Своим задним фронтом он переводит Т-триггер 4 в нулевое состояние, сигнал на управляющем входе регистра 11 исчезает, С первого выхода регистра 11 постоянно считывается тактовый сигнал TI до поступления на второй вход элемента ИЛИ 15 единичного сигнала с выхода элемента И 19. Элемент ИЛИ 16 предназначен для обеспечения возможности в исходном нулевом состоянии регистра 11 записи в него исходного единичного сигнала - сигнала пуска с входа пуска 31 модуля. Этот сигнал поступает на второй вход элемента ИЛИ 16 в виде короткого импульса. Далее единица, записанная в регистр 11, постоянно в нем циркулирует, благодаря связи второго выхода регистра 11 с первым входом элемента ИЛИ 16. Циркуляция единицы в регистре 11 происходит в течение

всего времени работы модуля до формирования в нем управляющего сигнала конца работы. Этот сигнал формируется элемен- TONJ И 18 и, поступая на R-вход регистра 11 синхронизации, переводит его в исходное, т,е, нулевое состояние. Сигнал конца работы модуля формируется элементом И 18 как конъюнкция сигнала конца команды, с первого ыхода дешифратора 7, тактового сигнала Т2 f второго выхода регистра 11 единичного сигнала, с выхода 42 старшего разряда поля 1.4 адреса БПМ 1, тактового импульса с первого входа 33 синхронизации модуля.

. Счетчик 12 ожидания АКУ предназначен для) определения модулем максимального

вре сисчени ожидания АКУ от других модулей ем в соответствии с микропрограммно

задаваемым кодом ожидания АКУ. Этот код задает начальное значение счетчика 12 в режиме ожидания модулем АКУ и поступает на информационный вход счетчика 12 с соответствующих разрядов выхода полей 1.2, 1.3 эПМ 1. Запись кода ожидания АКУ осуществляется по заднему фронту тактового сигнала Та на синхровходе счетчика 12 при единичном сигнале на его управляющем V- вхо,Је. С этого момента счетчик 12 переходит в счетный режим. По заднему фронту каждого тактового импульса п на своем счетном входе счетчик 12 увеличивает свое содержимое на единицу. При этом на управляющем входе счетчика 12 должна сохра- нятьЬя единица. По получении модулем АКУ 1ли после выхода из режима его ожидания здиничный сигнал на управляющем вхо- де ис чезает, а на инверсном R-входе счетчика 12 появится единица, которая обнуляет его соде эжимое, запрещая дальнейшую работу в счетйом режиме. Записываемый в счетчик 12 при выполнении модулем МК типа В пред- ставляет собой запись в двоичной форме счисления числа K0i, причем

Koi Кет Коть

где Йет - коэффициент пересчета счетчика 12;

- количество тактовых импульсов п, поступающих на вход 33 синхронизации модуля,(время выполнения которых равно мак- симаАьному времени ожидания i-ro АКУ от другого модуля симстемы. (Заметим, что условием выбора коэффициента пересчета счетчика 12 должно быть не- равен)ство: Кет К0т макс).

При переполнении счётчик 12 формирует единичный сигнал на своем выходе, исчезающий только по очередному тактовому импу/jbcy на счетном входе счетчика 12.

0

5

0 5 0 5 0

5

0 5

Элементы ИЛИ 13, И 20 предназначены для формирования тактового импульса, синхронизирующего работу регистра 2 адреса при работе модуля в режиме ожидания АКУ.

Элемент И 21 предназначен для формирования тактового импульса, синхронизирующего регистр 2 адреса при возврате модуля из режима подготовки передачи АКУ в рабочий режим, т.е. после выполнения модулем специальной МК записи АКУ в блок 9 передачи АКУ.

Элемент И 22 предназначен для формирования сигнала готовности очередного микрооперационного кода, посылаемого объекту управления с выхода 27 модуля. Этот сигнал формируется по тактовому сигналу Т2 с второго выхода регистра 11 синхронизации при отсутствии единицы на втором разряде выхода поля 1.1 признака МК БПМ 1.

Рассмотрим работу предлагаемого модульного устройства в составе управляющей системы (фиг. 3).

В исходном состоянии все элементы памяти модуля установлены в нуль. (Цепи установки исходного условно не показаны). С выхода БПМ 1 считывается МК с нулевым адресом. В ее поле 1.1 записан код 1,0, по которому дешифратор 7 формирует единичный сигнал на своем первом выходе. Этот сигнал поступает на второй адресный вход мультиплексора 4, который по этому сигналу пропускает на информационный вход регистра 2 адресный код МП с входа 32 модуля. На входы 33, 34 модуля с выхода генератора 53 постоянно поступают последовательности сдвинутых друг относительно друга тактовых импульсов Ti и Г2 соответственно, которые в исходном состоянии модуля ни на какие элементы модуля не влияют. Для перехода модуля в рабочее состояние необходимо, чтобы на его вход 26 поступил от соответствующего ОУ сигнал готовности к приему управляющего микрооперационного кода. Этот сигнал в.виде короткого импульса поступает на S вход RS-триггера З и устанавливает его в единичное состояние. На инверсном входе элемента И 19 нулевой сигнал, следовательно, очередной тактовый импульс т-, с входа 33 модуля проходит через элемент И 19, обнуляет RS-триггер З, пройдя через элемент ИЛИ 15, своим задним фронтом переводит Т-триггер 4 нулевого в единичное состояние. Регистр 11 сдвига по единичному управляющему сигналу с выхода Т-триггера 4 начинает сдвигать по заднему фронту тактовых импульсов нулевой код. В таком состоянии модуль находится до поступления на вход 31 модуля сигнала Пуск.

Сигнал Пуск формируется синфазно с тактовым импульсом п. Таким образом, сигнал Пуск поступает через элемент ИЛ И 16 на информационный вход регистра 11 сдвига одновременно со сдвигом в нем ин- формации и записывается в его первый разряд. Модуль переходит в рабочее состояние. На первом выходе регистра 11 формируется единичный сигнал Ti, поступающий на син- хровход регистра 2 адреса. По переднему фронту сигнала в регистр 2 с входа 32 модуля записывается код операции, т.е. адресный код первой МК, требуемой операции (команд).

В соответствии с этим адресом с выхо- дом БПМ 1 начинает считываться первая МК операции. Пусть это будет обычная линейная МК. Формат такой МК следующий:

Поле 1.1 (ни один из обозначенных входов дешифратора 7 не возбуждается).

Поле 1.2 - микрооперационный код.

Поле 1.3 - нулевой код,

После 1,4 - адресный код очередной МК операции. Единичный сигнал на первом выходе дешифратора 7 исчезает.

По заднему фронту очередного тактового импульса Г| с входа 33 модуля регистра 11 сдвигает единицу из своего первого разряда во второй. На втором выходе регистра 11 формируется сигнал Та. Пройдя че- рез элемент И 17 (на инверсном входе которого нуль), этот сигнал поступает на объект управления, информируя его о сформированном считывании нового микропроцессорного кода с выхода 28 модуля. Сигнал Та через элемент ИЛИ 16 поступает на информационный D-вход регистра 11, а через элемент ИЛИ 15 - на Т-вход Т-триггера 4.

При считывании обычных линейных МК и МК ветвления на инверсном управляющем входе мультиплексора 6 сигнал всегда нулевой, т.е. разрешающий его функционирование.

Мультиплексор 6 ЛУ по нулевому коду на своем адресном входе пропускает на свой выход значение младшего разряда адресного кода с выхода поля 1.4 БПМ 1. Таким образом, при считывании из БПМ 1 обычной линейной МК на третий информационный вход мультиплексора 5 адреса поступает с выходов поля 1.4 БПМ 1 и мультиплексора 6 ЛУ адресный код очередной МК операции, полностью совпадающий с кодом, записанным в поле 1,4 формата считываемой МК. Так как на адресных входах мультиплексора 5 адреса единич- ные сигналы отсутствуют, от мультиплексор 5 пропускает на информационный вход регистра 2 адрес очередной МК со своего третьего информационного входа.

По заднему фронту очередного тактового импульса TI на синхровходе регистра 11 единица на его информационном D-входе записывается в первый разряд регистра 11. Единица во втором (последнем) разряде регистра 11 в результате сдвига исчезает.

На втором выходе регистра 11 исчезает тактовый сигнал Та, своим задним фронтом переводя Т-триггер 4 в противоположное, т.е. нулевое состояние. На управляющий вход регистра 11 сдвига с выхода Т-триггера 4 поступает нулевой, запрещающий запись и сдвиг, сигнал. Однако, в результате уже произведенной записи единицы в первый разряд регистра 11, на его первом выходе формируется тактовый сигнал Т, который поступает на синхровход регистра 2 адреса. По переднему фронту сигнала Т в регистр 2 записывается адресный код очередной операции МК. По этому коду БПМ 1 начинает формировать на своих выходах соответствующую очередную МК. В таком состоянии модуль будет находиться до тех пор, пока на выход 26 модуля от объекта управления не поступит сигнал готовности к приему микрооперационного кода. Исключением из этого является случай, когда очередная МК передачи АКУ другим модулем системы. Пусть очередная МК операции будет МК ветвления. Отличие от ее формата линейной МК в следующем:

Поле 1.3-код ЛУ,

Поле 1.4 - четный адрес одной из двух альтернативных МК. (т.е. в младшем разряде этого кода О).

По считываемому из поля 1.3 БПМ 1 коду ЛУ мультиплексор 6 ЛУ выделяет на свой выход значение требуемого для анализа ЛУ с соответствующего разряда своего информационного входа. Таким образом, младший разряд адресного кода МК следующей за МК ветвления будет определяться значением проверяемого ЛУ. Как только на вход 26 модуля поступит сигнал готовности объекта управления к приему следующего микрооперационного кода, Т-триггер 4 по его заднему фронту переходит в единичное состояние. Единичный сигнал на его выходе разрешает сдвиг в регистре 11. По очередному тактовому импульсу та единица из первого разряда регистра 11 сдвигается во второй разряд. Сигнал Ti на первом выходе регистра 11 сдвига исчезает, а на втором выходе формируется тактовый сигнал Та. Дальнейшая процедура считывания микрооперационного кода в ОУ, записи единицы в первый разряд регистра 11 сдвига, обнуления Т-триггера 4, записи адресного кода очередной МК операции в регистр 2

адреса аналогична той же процедуре при выполнении модулем линейной МК.

Возможны также следующие специальные типа МК. Рассмотрим их форматы,

МК типа А - МК передачи АКУ:

б) АКУ;

в) код модулей адресатов АКУ;

МК типа В - МК перевода модуля в режим ожидания АКУ;

б) код ожидания АКУ;

МКтипа С - последняя МК в непоследней операции программы работы система.

1, 0 (возбуждается 1 выход дешифратора 7);

МКтипа - последняя МК в последней операции программа работы модуля. - 1.

МК типов С и D по сути является частными случаями обычной линейной МК. Пусть по очередному тактовому сигналу TI в регистр 2 запишутся адрес последней МК не последней МП (адрес МК типа С). На первом выходе дешифратора 7 начинает формироваться единичный сигнал микрооперации конца команды. Как и в исходном состоянии модуля, по этому сигналу мультиплексор 5 адреса код очередной команды с входа 32 модуля. Сигнал микрооперации конца работы элементом И 18 не формируется, так как в поле 1.4 МК типа С код нул евой и на входе 42 БПМ 1 единица отсутствует. По очередному тактовому сигналу Т2 с второго выхода регистра 11 сдвига элемент И 17 начинает формировать на выходе 27 модуля сигнал готовности нового ми рооперационного кода для объекта уп- раврения. Последний микрооперационный

код выполняемой МП считывается в объект управления с выхода 28 модуля.

По переднему фронту очередного тактового сигнала TI на синхровходе регистра 2 адреса в него запишется с входа 32 модуля либо код новой МП, либо нулевой код, если код новой МП еще не сформирован. В последнем случае из БПМ 1 будет считываться МК с нулевым адресом. Дешифратор 7 по управляющему коду 1; 0 по-прежнему будет формировать единичный сигнал на своем первом выходе. По этому сигналу мультиплексор 5 по-прежнему будет пропускать на информационный вход регистра 2 адреса код с входа 32 операции модуля. На объект управления будет считываться нулевой микрооперационный код. По очередному текстовому сигналу TI в регистр 2 адреса снова записывается либо уже сформировавшийся код новой команды, либо опять нулевой код. В последнем случае и из БПМ 1 опять будет считывать МК с нулевым адресом. Так как сигнал готовности нового микрооперационного кода на выходе 27 при выполнении этой МК будут единичным, то, несмотря на нулевой микрооперационный код, объект управления сформирует новый сигнал готовности к приему следующего микрооперационного кода, поступающий на вход 26 модуля. Это позволяет избежать стирание единицы из регистра 11 сдвига. Таким образом после выполнения модулем последней МК не последней МП модуль до поступления на свой вход 32 кода новой МП реализует одну и ту же служебную МК с нулевым адресом.

В случае считывания из БПМ 1 последней МК последней команды в алгоритме работы модуля (МК канал D) дешифратор 7, как и при выполнении МК типа С, формирует единичный сигнал конца команды на своем первом выходе. С выхода 42 поля 1,4 БПМ 1 при реализации МК типа D считывается единица (такое считывание указанных единичных сигналов программируется только в последних МК последних операций). С началом формирования тактового сигнала Т2 с входа 28 модуля считывается уже описанным образом последний микрооперационный код алгоритма, запрограммированный в поле 1.2 формата МК канала D. Сигнал Т2 поступает на первый вход элемента И 18, на третьем и четвертом входах которого присутствуют единичные сигналы с выхода 42 поля 1.4 БПМ 1 и первого выхода дешифратора 7 соответственно. К моменту поступления единичного тактового сигнала Т2 на первый вход элемента И 18 тактовый импульс т- на его втором

входе с входа 32 модуля уже отсутствует, так как сигнал Т2 был сформирован по заднему фронту импульса TL С началом поступления очередного тактового импульса TI на вход 33 модуля элемента И 18 формирует сигнал конец работы модуля, который обнуляет регистры 11 сдвига и 2 адреса. Сдвиг в регистре 11 по этому же импульсу произойти не успевает, так как он осуществляет только по заднему фронту импульса п. Модуль реходит в исходное состояние.

Частным случаем рабочего режима модуля является режим ожидания АКУ от других модулей системы, В этот режим модуль переходит при реализации им МКтипа В. При считывании этой МК из БПМ 1 возбуждается второй выход дешифратора 7. Сформированный дешифратором единичный сигнал поступает на выход 30 модуля и да- лее на соответствующие разряды входом 23 остальных модулей системы, извещая их, таким образом, об ожидании рассматриваемым модулем АКУ, При реализации МКтипа В код с выхода 28 модуля объектом управ- ления не воспринимается, так как на инверсном входе элемента И 22 присутствует единица с второго выхода поля 1.1 БПМ 1 и сигнал готовности первого микрооперационного кода на выходе 27 модуля не форми- руется. Единичный сигнал с второго выхода дешифратора 7, поступая на управляющий вход счетчика 12, разрешает запись в него кода ожидания АКУ, Этот код поступает на информационный вход счетчика 12 с соот- ветствующих разрядов полей 1.2,1.3 БПМ 1. Оставшиеся разряды полей 1.2, 1.3 формата типа МК типа В определяют код номера модуля, от которого ожидается АКУ. Значение этих разрядов с выхода полей 1.2, 1.3 поступают на адресный вход мультиплексора 8 АКУ. На управляющий вход мультиплексора 8 поступает разрешающий его работу единичный сигнал с второго выхода дешифратора 7. По этому сигналу, в соответствие с кодом на его адресном входе, мультиплексор 8 пропускает на информационный вход регистра 10 АКУ сигналы с соответствующего разряда выхода 29 того модуля, от которого рассматриваемый модуль ожида- ет АКУ.

Рассмотрим синхронизацию элементов модуля при реализации им МК типа В.

Запись кода ожидания в счетчик 12 осуществляется по заднему фронту тактового сигнала Та с второго выхода регистра 11 синхронизации. Единичный сигнал Т2, как и при реализации других МК, по заднему фронту очередного тактового импульса TI

записывается в первый разряд регистра 11 синхронизации и своим задним фронтом переводит Т-триггер 4 в нулевое состояние. На первом выходе регистра 11 появится единичный тактовый сигнал TI. Однако, его поступление на синхровход регистра 2 адреса блокируется элементом И 17. На инверсном входе элемента И 17 при реализации модулем МК типа В присутствует единичный сигнал с второго разряда выхода поля 1.1 БПМ 1. Перевод Т-триггера 4 в единичное состояние сигналом с выхода RS-триггера З при реализации МКтипа В также блокируется тем же единичным сигналом с второго выхода поля 1.1 БПМ 1, поступающим на инверсный вход элемента И 19. Указанными блокировками достигается приостанов работы модуля, т.е. собственно его состояние ожидания АКУ. Заметим, что регистр 10 приемник АКУ до поступления на него метки АКУ по заднему фронту тактового сигнала Т2 постоянно сдвигает нулевой код. Это состояние модуля, т.е. постоянное считывание одной и той же МКтипа В, происходит до тех пор пока, согласно алгоритму работы модуля (см. фиг. 5), в модуль не поступит АКУ или пока не выйдет время его ожидания, задаваемое в счетчике 12, Рассмотрим оба случая.

Для удобства рассмотрения процесса взаимодействия модулей управляющей системы условно назовем модуль получатель АКУ А-модулем, а модуль, формируемый АКУ, -Б-модуль.

Итак, с началом считывания из БПМ 1 А-модуля МК типа В на соответствующем разряде входа 23 Б модуля появляется единичный сигнал с выхода 30 А-модуля. Этот сигнал информирует блок 9 Б-модуля о готовности А-модуля к приему, от него АКУ.

Пусть на момент выполнения А-модулем МК типа В Б-модуль уже сформировал в своем блоки 9 АКУ для А-модуля. В этом случае блок 9 по заднему фронту очередного тактового импульса ti на своем входе 41 начинает, согласно описанному ранее алгоритму своей работы, сдвигать сформированные в нем единичную метку АКУ и сам АКУ для сомодуля А, На соответствующем А-мо- дулю разряде выходе 29 блока 9 Б-модуля появляется единичный сигнал метки АКУ, который через мультиплексор 8 АКУ А-модуля поступает на информационный вход регистра 10 приемника АКУ, По заднему фронту следующего тактового импульса Т2, но уже на входе 34 синхронизации А-модуля единичный сигнал метки АКУ записывается в младший разряд регистра 10 приемника АКУ. Очередные тактовые импульсы ti приводят к дальнейшему сдвигу и, в конечном итоге, перезаписи кодов из регистра 43 сдвига блок 9 Б-модуля в регистр 10 приемник АКУ А-модуля. Как только эта перезапись заканчивается, на выходе старшего разряда выхода регистра 10 А-модуля появляется единичный сигнал метки АКУ. Для А-модуля этот сигнал инициирует переход в рабочий режим, Поступая на инверсный V- вход регистра 10, сигнал метки АКУ со своего третьего информационного входа на информационный вход регистр2 адреса МК. Сигнал метки АКУ с выхода последнего, старшего разряда регистра 10 поступает также через элемент ИЛИ 13 на первый вход элемента И 20. На втором входе этого элемента И 20 в этот момент присутствует единичный сигнал с второго выхода дешифратора 7, так как А-модуль реализует МК типа В. Таким образом единичный сигнал метки АКУ разрешает поступление через элемент И 20 очередного тактового импульса т на синхровход регистра 2 адреса М К. По переднему фронту этого импульса в регистр 2 в качестве адреса первой МК новой команды запишется АКУ с выхода мультиплексора 5. Из БПМ 1 начнет считываться соответственная МК, которая не должна быть МК типа В. Сигнал с второго входа дешифратора 7 исчезает. Соответственно обнуляется регистр 10 приемник АКУ, запрещается работа мультиплексора 8 АКУ, закрывается элемент И 20, открывается элемент И 19, обнуляется счетчик 13 ожидания АКУ.

А-модуль продолжает функционировать s рабочем режиме.

Рассмотрим альтернативный случай, когда на момент реализации 2-модулем МК типа В соответственный этой МКБ-модуль еще не сформировал требуемый А-модулю ДКУ. В этом случае регистр 10 приемник АКУ будет постоянно сдвигать нулевой код, а счетчик 12 по заднему фронту каждого тактового импульса t с входа 33 модуля будет увеличивать на единицу свое содержание. Как только время ожидания АКУ, заданное в счетчике 12 начальным кодом ожидания, выходит, счетчик 12 переполняется и на его выходе появляется единичный сигнал. Этот сигнал, пройдя через элемент ИЛИ 13, откроет элемент И 20 для очередного тактового импульса т с входа 33 А-модуля. Если к моменту поступления этого импульса TI через элемент И 20, на вход элемента ИЛИ 14 АКУ в полном объеме не успевает поступить в регистр 10, тот по переднему фронту п в регистр 2 запишется адресный код с второго информационного входа мультиплексора 5.

Младший разряд этого кода нулевой, так как считывается с выхода мультиплексора 6, на управляющему входе которого запрещающий единичный сигнал с второго входа поля

либо аварийная М К перераспределения ресурсов, либо аварийная сигнальная МК, либо просто очередная МК алгоритма функционирования А-модуль. При считывании этой МК, которая не должна .быть МК

типа В, сигнал на втором выходе дешифратора 7 исчезает, А-модуль переходит в рабочее состояние, регистр 10 приемник АКУ, даже если на него поступает ожидаемый ранее АКУ, обнуляется, мультиплексор

8 закрывается.

Заметим, что временный сдвиг между передним фронтом импульса т- и задним фронтом ближайшего предшествующего ему импульса га соответственно с входом 33 и 34

модуля должен быть больше суммарного времени срабатывания регистра 10 сдвига и мультиплексора 5. В этом случае исключается возможность записи адреса в регистр 2 в тот момент, когда мультиплексор 5 переключает

на свой вход вместо адресного кода со своего второго информационного кода АКУ с третьего информационного входа.

Рассмотрим последний режим работы модуля - режим подготовки к передаче АКУ

другим модулям системы. В этот режим модуль переходит в том случае, если его состояние или реализуемая им ветвь алгоритма управления могут заинтересовать другие модули (модуль) управляющей системы.

Здесь возможны два случая:

1) блок 9 передачи АКУ.в этот момент времени при любой предыстории работы модуля должен быть свободен (на его выхо- де 37 сигнал нулевой);

2) блок 9 может быть занят не переданным АКУ (на его выходе 37 сигнал нулевой).

В первом случае сигнал из БПМ 1 считывается МКтипа А. Причем эта МК програм- мируется по возможности следующей за МК, время выполнения которой объектом управления превышает такт работы генератора 53 синхронизации системы по своему первому выходу. Это позволит избежать за- держки реализации модулем основного алгоритма работы для подготовки передачи АКУ другим модулям системы.

Во втором случае из БПМ 1 считывается специальная МК ветвления с четным адресом - МК типа Е. В ее полях 1.1, 1.2 записаны нули, в поле 1.3 - код ЛУ с выхода 37 блока 9, в поле 1.4 - адресный код самой этой МК. Эта МК так же, как и в первом случае, программируется, по возможности, следующий за МК, время выполнения которой объектом управления как можно больше. МК типа Е будет считываться из БПМ 1 до тех пор, пока на выходе 37 блока 9 передачи АКУ не будет единичный сигнал; т.е. пока блок 9 не освободится от прежнего АКУ. В этом случае сигнал на выходе мультиплексора 6 становится единичным, четный адресный код очередной МК с выхода БПМ 1 модифицируется в нечетный, т.е. уве- личивается на единицу. Адрес на единицу больший адреса МК типа Е - это адрес МК типа А. Из БПМ 1 по очередному тактовому сигналу TI начинает считываться МК типа А, так же как и в первом случае, когда заня- тость блока 9 не проверяется,

При считывании МК передачи АКУ (МК типа А) происходит следующее. Единичный сигнал с второго разряда выхода поле 1.1 БПМ 1 закроет элементы И 17, 19, 22 и муль- типлексор 6 ЛУ. Тем самым, соответственно:

1) Сигнал микрооперации готовности очередного микрооперационного кода на выходе 27 модуля не формируется и код с выхода поля 1.2 БПМ 1 объектом управления данного модуля не воспринимается.

2) Перевод Т-триггера 4 в единичное состояние сигналов с входа 26 модуля (от объекта управления) блокируется. Благодаря этому, регистр 1.1 синхронизации до за- вершения- выполнения МК типа А все время формирует на своем первом выходе сигнал Тт.

3) Прохождение сигнала Тч на синхров- ход регистра 2 адреса блокируется. Стано- вится возможным запись в регистр 2 адреса по переднему фронту другого сигнала.

4) Сигнал на выходе мультиплексора 6 ЛУ, определяющий младший разряд адреса МК, следующей за МК типа А, нулевой неза- висимо от кодов на информационном и адресном входах мультиплексора 6.

При считывании из БПМ 1 МК типа А на третьем выходе дешифратора 7 появляется единичный сигнал, который, поступая на уп- равляющий вход 40 блока 9 передачи АКУ, разрешает запись в него кода с выходов полей 1.2, 1.3 БПМ 1. При этом составляющие этого кода: код ожидания передачи АКУ, код модулей адресатов АКУ, - с входа 39 блока 9 поступают соответственно на информационные вход счетчика 45 ожидания передачи АКУ, регистры сдвига 43 передачи АКУ, регистра 44 кода модулей адресатов

АКУ. Запись этих кодов происходит по переднему фронту очередного тактового импульса TI, который проходит через элемент И 21 (на втором входе этого элемента И 21 при реализации МК типа А присутствует единичный сигнал с третьего выхода дешифратора 7). Этот же тактовый импульс т с выхода элемента И 21 поступает через элемент ИЛ И 14 на синхровход регистра 2 адреса. По его переднему фронту в регистр 2 запишется четный адресный код очередной МК с выходов поля 1.4. БПМ 1 и мультиплексора 6 ЛУ. С выхода БПМ 1 считывается очередная МК управления объектом данного модуля, Сигналы на вторых выходах поля 1.1 БПМ 1 и дешифратора 7 исчезают. Соответственно разблокируются элементы И 17, 19, 22 и мультиплексор 6 ЛУ. Модуль переходит в обычный рабочий режим. Блок 9 ожидает готовности модулей-адресатов к приему АКУ и осуществляет передачу АКУ уже описанным ранее образом независимо от работы остальных блоков своего модуля и от алгоритма управления его объектом.

Заметим, что в предлагаемом модульном устройстве управления предусмотрена возможность проконтролировать факт передачи другим модулям системы наибольшее значительных АКУ. При необходимости такого контроля в алгоритме работы модуля после n-ного количества МК, следующих за соответственный МК типа А, за время выполнения которых АКУ должен быть обязательно передан адресатам, предусматривается МК проверки ЛУ с выхода 36 блока 9 передачи АКУ. Если это ЛУ единично, т.е. счетчик 45 в блоке 9 переполнен, то АКУ не передано. Если же оно нулевое, то АКУ передан. Здесь возможны два случая.

1) Если алгоритм работы после выполнения МКтипа А до момента проверки передачи АКУ не расходится на альтернативные ветви, то в формате одной из обычных линейных МК в поле 1.4 записывается четный адрес очередной МК, а поле 1.3 записывается код ЛУ с выхода 36 блока 9. После реализации модулем этой МК он перейдет к реализации либо очередной МК) сигнал на выходе 36 блока 9 нулевой), либо аварийной МК реакции на факт переданного АКУ (сигнал на выходе 36 блока 9 единичный).

2) Если алгоритм работы модуля к моменту проверки передачи АКУ расходится на альтернативные ветви, то в каждой ветви предусматривается специальная МК проверки ЛУ с выхода 36 блока 9 передачи АКУ.

Описанным образом организуется взаимодействие модулей системы и их согласованное функционирование.

Формула изобретения

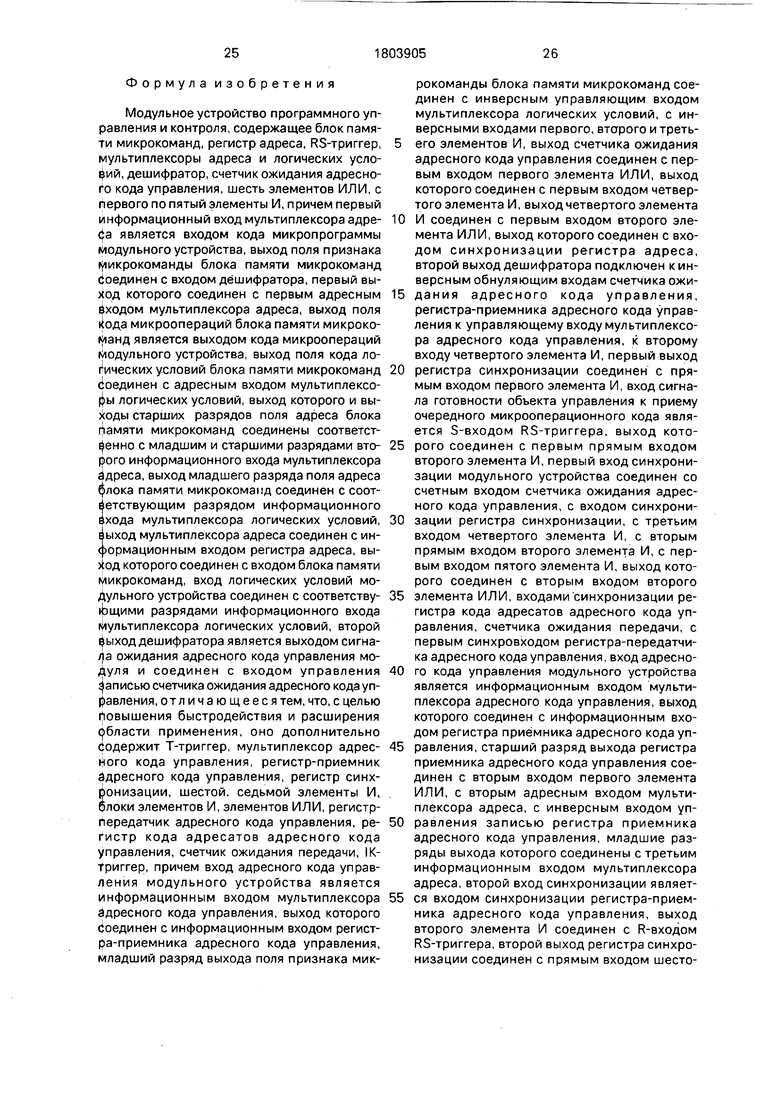

Модульное устройство программного управления и контроля, содержащее блок памя- tn микрокоманд, регистр адреса, RS-триггер, мультиплексоры адреса и логических условий, дешифратор, счетчик ожидания адресного кода управления, шесть элементов ИЛИ, с первого по пятый элементы И, причем первый информационный вход мультиплексора адреса является входом кода микропрограммы модульного устройства, выход поля признака Микрокоманды блока памяти микрокоманд соединен с входом дешифратора, первый выход которого соединен с первым адресным ходом мультиплексора адреса, выход поля микроопераций блока памяти микрокоманд является выходом кода микроопераций Модульного устройства, выход поля кода логических условий блока памяти микрокоманд Соединен с адресным входом мультиплексоры логических условий, выход которого и выходы старших разрядов поля адреса блока г амяти микрокоманд соединены соответст- $енно с младшим и старшими разрядами второго информационного входа мультиплексора адреса, выход младшего разряда поля адреса лока памяти микрокоманд соединен с соот- етствующим разрядом информационного хода мультиплексора логических условий, ыход мультиплексора адреса соединен с информационным входом регистра адреса, выход которого соединен с входом блока памяти микрокоманд, вход логических условий модульного устройства соединен с соответству- йэщими разрядами информационного входа мультиплексора логических условий, второй $ыход дешифратора является выходом сигна- /)а ожидания адресного кода управления модуля и соединен с входом управления Записью счетчика ожидания адресного кода управления, отличающееся тем, что, с целью повышения быстродействия и расширения области применения, оно дополнительно Содержит Т-триггер, мультиплексор адресного кода управления, регистр-приемник адресного кода управления, регистр синхронизации, шестой, седьмой элементы И, блоки элементов И, элементов ИЛИ, регистр- передатчик адресного кода управления, регистр кода адресатов адресного кода управления, счетчик ожидания передачи, IK- триггер, причем вход адресного кода управления модульного устройства является информационным входом мультиплексора адресного кода управления, выход которого соединен с информационным входом регистра-приемника адресного кода управления, младший разряд выхода поля признака микрокоманды блока памяти микрокоманд соединен с инверсным управляющим входом мультиплексора логических условий, с инверсными входами первого, второго итретьего элементов И, выход счетчика ожидания адресного кода управления соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, выход четвертого элемента

И соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом синхронизации регистра адреса, второй выход дешифратора подключен к инверсным обнуляющим входам счетчика ожидания адресного кода управления, регистра-приемника адресного кода управления к управляющему входу мультиплексора адресного кода управления, к второму входу четвертого элемента И, первый выход

регистра синхронизации соединен с прямым входом первого элемента И, вход сигнала готовности объекта управления к приему очередного микрооперационного кода является S-входом RS-триггера, выход которого соединен с первым прямым входом второго элемента И, первый вход синхронизации модульного устройства соединен со счетным входом счетчика ожидания адресного кода управления, с входом синхронизации регистра синхронизации, с третьим входом четвертого элемента И, с вторым прямым входом второго элемента И, с первым входом пятого элемента И, выход которого соединен с вторым входом второго

элемента ИЛИ, входами синхронизации регистра кода адресатов адресного кода управления, счетчика ожидания передачи, с первым синхровходом регистра-передатчика адресного кода управления, вход адресного кода управления модульного устройства является информационным входом мультиплексора адресного кода управления, выход которого соединен с информационным входом регистра приёмника адресного кода управления, старший разряд выхода регистра приемника адресного кода управления соединен с вторым входом первого элемента ИЛИ, с вторым адресным входом мультиплексора адреса, с инверсным входом управления записью регистра приемника адресного кода управления, младшие разряды выхода которого соединены с третьим информационным входом мультиплексора адреса, второй вход синхронизации является входом синхронизации регистра-приемника адресного кода управления, выход второго элемента И соединен с R-входом RS-триггера, второй выход регистра синхронизации соединен с прямым входом шестого элемента И, с входом синхронизации счетчика ожидания адресного кода управления, с первыми входами шестого элемента И, третьего, четвертого элементов ИЛ И, вход пуска модульного устройства является вторым входом четвертого элемента ИЛИ, выход которого соединен с информационным входом регистра синхронизации, выход второго элемента И соединен с вторым входом третьего элемента .ИЛИ, выход которого соединен с входом Т-триггера, выход Т-триггера соединен с входом управления записью регистра синхронизации, первый вход синхронизации, выход старшего разряда поля адреса блока памяти микрокоманд, первый выход дешифратора соединены соответственно с вторым, третьим и четвертым входами шестого элемента И, выход которого соединен с обнуляющими входами регистров адреса и синхронизации, соответственные разряды выхода по- лей кодов микроопераций и логических условий блока памяти микрокоманд соединены с адресным входом мультиплексора адресного кода управления, с информационным входом счетчика ожидания адресного ко- да управления, выход третьего элемента И является выходом сигнала готовности нового микрооперационного кода модульного устройства, третий выход дешифратора соединен с вторым входом пятого элемента И, с входом управления записью регистра кода адресатов адресного кода управления, с первым входом управления записью счетчика ожидания передачи, с первым входом управления записью регистра передатчика адрес- ного кода управления, с 1-входом IK-триггера, с первым входом управления записью регистра передатчика адресного кода управления, с первым входом шестого элемента ИЛИ, с предпоследним старшим разрядом информа- ционного входа регистра передатчика адресного кода управления, выход которого соединен с прямыми входами блока элементов И, соответственно разряды выхода полей кодов микроопераций и логических условий

блока памяти микрокоманд соединен соответственно с младшими разрядами информа- ционного входа регистра передатчика адресного кода управления, с информационными входами регистра кода адресатов адресного кода управления, счетчика ожидания передачи, инверсный выход которого соединен с первым входом седьмого элемента И, разрядные выходы регистра кода модулей адресатов адресного кода управления соединены соответственно с первыми входами элементов ИЛИ блока элементов ИЛИ, выходы которых соединены с группой входов седьмого элемента И, разрядные входы сигналов ожидания адресного кода управления модуля соединены соответственно с вторыми входами элементов ИЛИ блока элементов ИЛИ, выход седьмого элемента И соединен с вторым входом шестого элемента ИЛИ, с К-входом IK-триггера, с вторым входом управления записью, со старшим разрядом информационного входа регистра передатчика адресного кода управления, с обнуляющим входом счетчика ожидания передачи, прямой выход которого соединен с первым входом пятого элемента ИЛИ, выход шестого элемента ИЛИ соединен с входом синхронизации К-триггера, прямой выход которого соединен с третьим входом седьмого элемента И, инверсный выход IK- триггера соединен с вторым входом пятого элемента ИЛИ, выход которого соединен с вторым инверсным входом управления записью счетчика ожидания передачи, прямой выход счетчика ожидания передачи, выход пятого элемента ИЛИ соединены с соответственными разрядами информационного входа мультиплексора логических условий, разряды выхода регистра кода модулей адресатов адресного кода управления соединены соответственно с инверсными входами блока элементов И, выход которого является выходом адресного кода управления модуля, второй выход регистра синхронизации соединен со счетн ым входом счетчика ожидания передачи.

Фиг. 2

фиг.З

( наччкз )

opnw ofcouMwt Cu-гнала ЛУ «Блок съо5одш

С QHt4 j «Рлг.Ц

, %«шож- notmw ,ача АКУ, oD«upot H xi сигнала № smHtrvtpt- далвСчшпмани М mwva VC opwupotoMut- UUKUAU romobnovnu к npu-en« AW. satuvcb кода OIKVCAAHU .oпробка w- ивжности. 1ни.т 1ьанигА мги-х к. Настройка, на tvpvaw ЛКУ от гире- fatnort) .

iMaoAMtHivft HOW. aftoip uHOR пикро- wAnporpaviKw pta«,« Ku.orrvcyrncrrvkw.t mptfttnoro АКУ

r,S

&HrVOAHtHM.e- CAtA«K V4vt% ,tCl ww potvporpuHriw (nn)

С KQHt4 )

т

I СчитыВание из модуля ., а „, „ , „ „

пикроопера.& ° к( а№са МКямаА

кода 3аписб 8 № 2 адреса

очередной МК Фиг.6

| ТЕЛЕФОННОЕ УСТРОЙСТВО | 1926 |

|

SU6465A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Ьсновы построения микроконтроллеров ;АСКУ, Харченко B.C | |||

| и др | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| Монорельсовая транспортная система | 1988 |

|

SU1600994A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1993-03-23—Публикация

1990-10-29—Подача