Изобретение относится к вычислительной технике и может быть использовано для обнаружения и исправления ошибок при передаче данных в ЭВМ.

Цель изобретения - повышение быстродействия устройства.

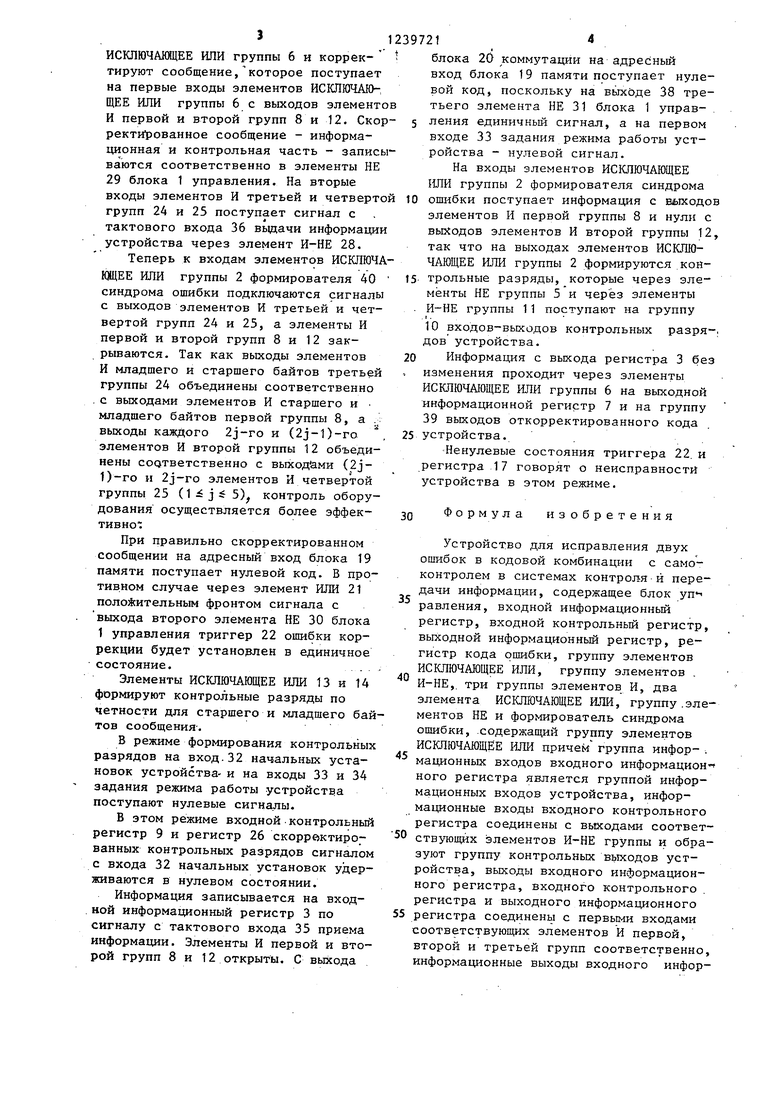

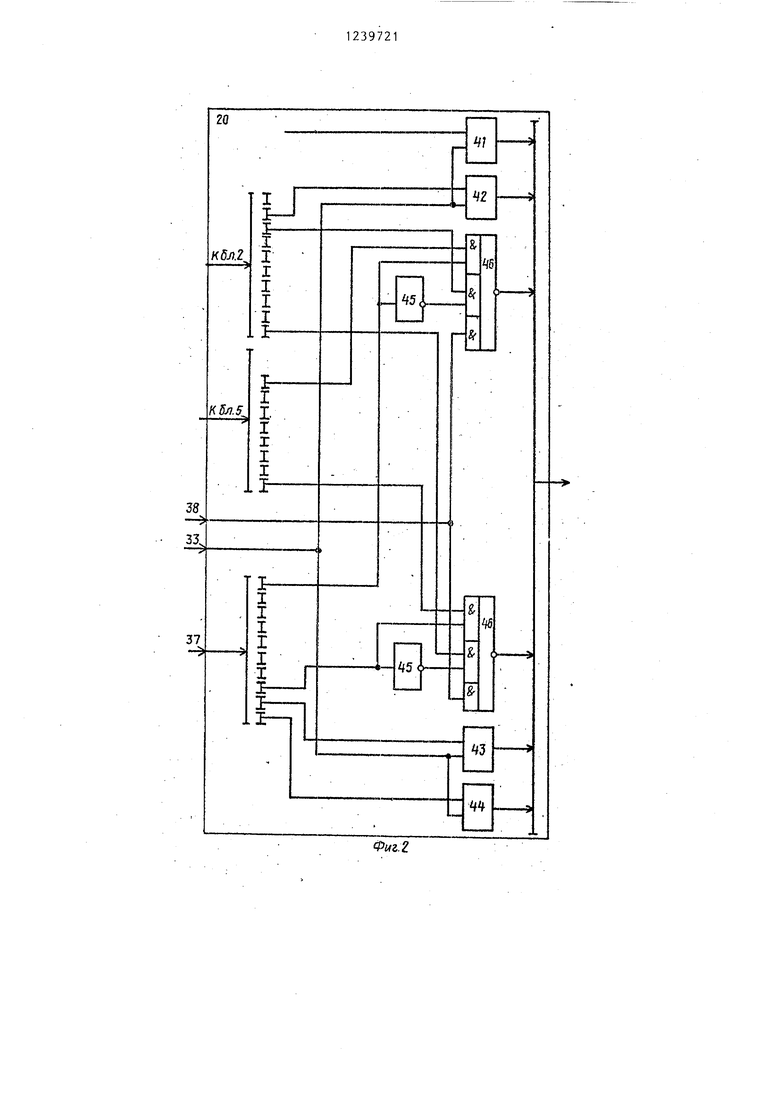

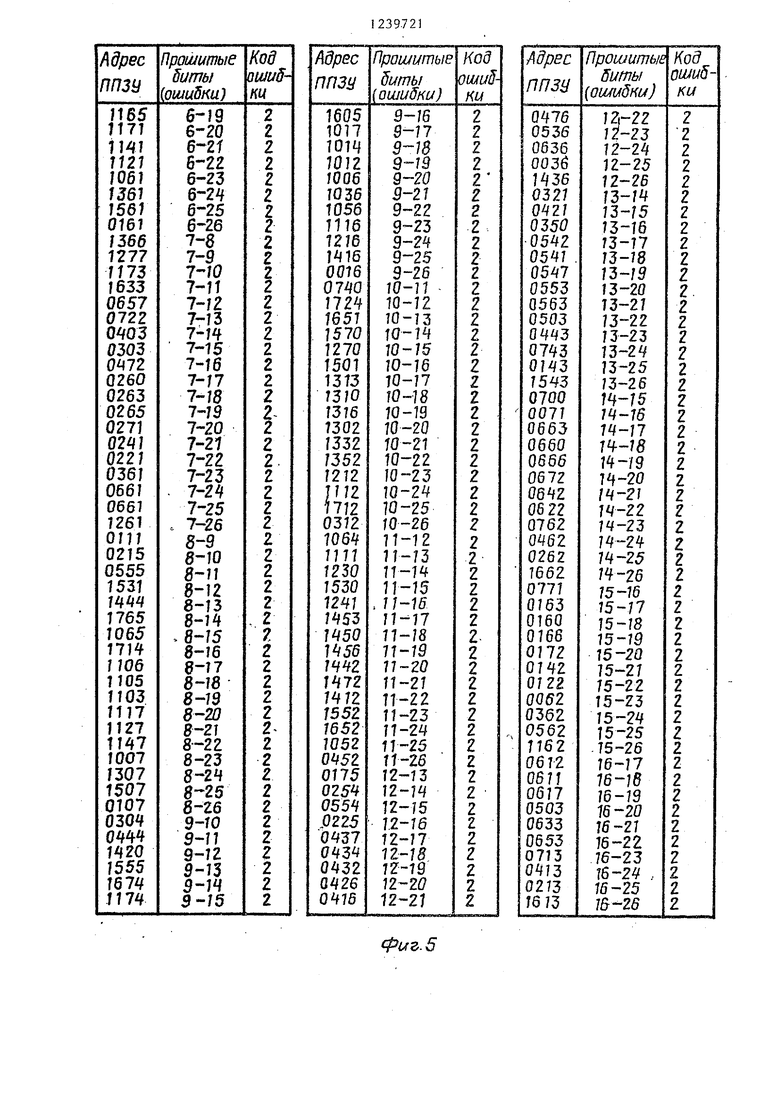

На фиг.1 приведена структурная схма устройства для исправления двух ошибок с самоконтролем; на фиг. 2 - функциональная схема блока коммутации; на фиг. 3 - матрица формирования синдрома ошибки кода (26,16); на фиг. 4-8 - таблица прошивки блока памяти.

Устройство для исправления двух ошибок в кодовбй .комбинации с самоконтролем (фиг.1) содержит блок 1 управления, группу 2 элементов ИСКЛЮ- ЧАЩЕЕ ИЛИ формирователя синдрома ошибки, входной информационный регистр 3, информационный вход 4 устройства, группу 5 элементов НЕ, группу 6 элементов ИСКПЮЧАЩЕЁ ИЛИ, вы- ходной информационный регистр 7, первую группу 8 элементов- И, входной контрольный регистр 9, группу 10 контрольных выходов устройства, группу 11 элементов И-НЕ, вторую группу 12 элементов И, элементов 13 и 14 ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы 15 и 16 паритета старшего и младшего байтов устройства, регистр 17 кода ошибки, выход 18 кода ошибки устройства, блок 19 памяти, блок 20 коммутации, элемент ИЛИ 21, триггер 22 ошибки, выход 23 ошибки устройства, третью и четвертую .группы 24 и 25 элементов И, регистр 26 скорректированных контрольных разрядов, элемент И 27 блока 1 управления, элемент И-НЕ 28 блока 1 управлений, элементы НЕ 29- 31 блока 1 управления, вход 32 начальной установки устройства, входы 33 и 34 задания режима работы устройства, тактовые входы 35 и 36 приема и вьщачи информации устройства соответственно, группу 37 входов контрольной свертки устройства, выход 3 третьего элемента НЕ 31 1 управления, группу 39 выходов откорректированного кода устройства, форми- рователь 40 синдрома ошибки.

Блок 20 коммутации (фиг.2) содержит элементы И 41-44, группу 45 элементов НЕ, группу 46 элементов И-ИЛИ-НЕ.

Устройство для исправления двух ошибок в кодовой комбинации с самоконтролем работает следующим образом.

Устройство работает с кодом (26, 12) в режиме чтения информации и в режиме формирования контрольных разрядов., При этом младшие 8 разрядов группы 37 входов контрольной свертки устройства соединены с шиной единичного потенциала, а два старших разряда- с шиной нулевого потенциала.

При работе в режиме чтения информации входы 33 и 34 задания режима работы устройства и вход 32 начальных

установок устройства соединяются с шиной единичного потенциала.

По сигналу, поступающему на тактовый вход 35 приема информации на входной информационный регистр 3 и

входной контрольный регистр 9, записываются соответственно 16 информационных и 10 контрольных разрядов(вы- ходы элементов И-НЕ группы 11 в это время закрыты единичным сигналом,

поступающим с второго входа 34 задания режима работы устройства и не шунтируют контрольные выходы группы 10 устройства). С вькодов входного информационного регистра 3 и входнрго контрольного регистра 9 через элементы И первой и второй групп В и 12 принятое сообщение поступает на входы элементов ИСКЛЮЧАЩЕЕ ИЛИ группы 2 формирователя синдрома ошибки, на выходах которых формируется синдром ошибки согласно матрице, приведенной на фиг.З.

Десятиразрядный код с выходов элементов ИСКЛЮЧАЩЕЕ ИЛИ группы 2 через элементы И 41 и 42 блока 20 коммутации, группу 5 элементов НЕ и группу 40 элементов И-ШШ-НЕ блока 20 коммутации, поступает на ад- ресньй вход блока 19 памяти и на входы элемента ИЛИ 21.

В ячейках блока 19 памяти прошиты заранее подсчитанные варианты одиночных и двойных ошибок. Число одиночных ошибок 26, число двойных ошибок - число сочетаний С. -235. По нулево

му адресу прошиты логические нули - признак отсутствия ошибок. Два разряда в каждой ячейке блока 19 памяти. - прошит код ошибки - одиночная или двойная ошибка. Эти разряды поступают

на регистр 17 ошибки.

Выходы информационных разрядов блока 19 памяти поступают на вторые входы соответствукмцих элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ группы 6 и коррек- тируют сообщение,которое поступает на первые входы элементов ИСКЛЮЧАЮ-, ЩЕЕ ИЛИ группы 6 с выходов элементо И первой и второй групп 8 и 12. Скор рект1фованное сообщение - информационная и контрольная часть - записываются соответственно в элементы НЕ 29 блока 1 управления. На вторые входы элементов И третьей и четверто групп 24 и 25 поступает сигнал с тактового входа 36 вьщачи информации устройства через элемент И-НЕ 28.

Теперь к входам элементов ИСКЛЮЧАВДЕЕ Р1ЛИ группы 2 формирователя 40 синдрома ошибки подключаются сигналы с выходов элементов И третьей и четвертой групп 2 и 25, а элементы И первой и второй групп 8 и 12 закрываются. Так как выходы элементов И младшего и старшего байтов третьей группы 24 объединены соответственно .с выходами элементов И старшего и младшего байтов первой группы 8, а .- выходы каждого 2j-ro и (2j-1)-ro элементов И второй группы 12 объединены соответственно с выходами (2j- 1)-го и 2j-ro элементов И четвертой группы 25 (1 i j i 5) контроль оборудования осуществляется более эффективно :

При правильно скорректированном сообщении на адресный вход блока 19 памяти поступает нулевой код. В противном случае череэ элемент ИЛИ 21 положительным фронтом сигнала с выхода второго элемента НЕ 30 блока 1 управления триггер 22 ошибки коррекции будет устаноэлен в единичное состояние.

Элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 13 и 14 формируют контрольные разряды по четности для старшего и младшего байтов сообщения-.

В режиме формирования контрольных разрядов на вход.32 начальных установок устройства- и на входы 33 и 34 задания режима работы устройства поступают нулевые сигналы.

В этом режиме входной контрольный регистр 9 и регистр 26 скоррйктиро- ванных контрольных разрядов сигналом с входа 32 начальных установок удерживаются в нулевом состоянии.

Информация записывается на вход- .ной информационный регистр 3 по сигналу с тактового входа 35 приема информации. Элементы И первой и второй групп 8 и 12 открыты. С выхода

39721

блока 20 коммутации на адресный

вход блока 19 памяти поступает нулевой код, поскольку на выхЬде 38 третьего элемента НЕ 31 блока 1 управ- .

5 ления единичный сигнал, а на первом входе 33 задания режима работы устройства - нулевой сигнал.

На входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 формирователя синдрома

10 ошибки поступает информация с выходов элементов И первой группы 8 и нули с выходов элементов И второй группы 12, так что на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы 2 формируются кон15- трольные разряды, которые через элементы НЕ группы 5 и через элементы . И-НЕ группы 11 поступают на группу

10 входов-выходов контрольных разря-, ДОН устройства.

20 Информация с выхода регистра 3 без изменения проходит через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ группы 6 на выходной информационной регистр 7 и на группу 39 выходов откорректированного кода

25 устройства.

Ненулевые состояния триггера 22. и регистра 17 говорят о неисправности устройства в этом режиме.

35

40

3Q Формула изобретения

Устройство для исправления двух ошибок в кодовой комбинации с самоконтролем в системах контроля-и передачи информации, содержащее блок уп- равления, входной информационный регистр, входной контрольный регистр, выходной информационный регистр, регистр кода ошибки, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу элементов . И-НЕ,. три группы элементов И, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, группу .элементов НЕ и формирователь синдрома ошибки, .содержащий группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ приче группа инфор- . мационных входов входного информацион ного регистра является группой информационных входов устройства, информационные входы входного контрольного регистра соединены с вь1ходами соответствующих :элементов И-НЕ группы и образуют группу контрольных вь1ходов устройства, выходы входного информационного регистра, входного контрольного регистра и выходного информационного 55 регистра соединены с первьми входами соответствующих элементов И первой, второй и третьей групп соответственно информационные выходы входного инфор45

50

25

мационного и входного контрольного регистров соединены с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, информационные входы вы- Ходкого информационного регистра сое- 5 динены с выходами соответствующих элементов. ИСКЛЮЧАЮЩЕЕ ШШ группы,

группа информ ационных выходов выходного информационного регистра является группой выходов откорректированного 10 кода устройства, выходы первого и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответственно выходами паритета старшего и младшего байтов устройства, выход регистра кода ошибки является ts выходом кода ошибки устройства, вход ,. синхронизации входного информационного регистра является тактовым входом устройства, отличающееся тем,

что, с целью повышения быстродействия,20 равления,

в него введены блок памяти, регистр с первыми

скорректированных контрольных разряг дов, четвертая группа элементов И, элемент ИЛИ, триггер ошибки и блок коммутации, блок, управления содер- н(ит три элемента НЕ, элемент И и элемент И-НЕ, причем входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, формирователя синдрома опшбки соединены с выходами соответствующих элементов И первой зо и второй групп в соответствии с матрч цей формирования контрольных разряг . дов, входы первой группы информацией- ных входов блока коммутации соединены с выходами соответствующих эле- 35 ментов ИСКЛЮЧАЮЩЕЕ ИЛИ группы формирователя синдрома ошибки, входы второй группы информационных уходов блока коммутации соединены с выходами соответствующих элементов НЕ группы, 40 входы которых соединены с выходами соответствующих элементов ИСКЛЮЧАЩЕЕ ИЛИ груцпы формирователя синдрома ошибки, выходы элементов НЕ группы соединены с прямыми входами соответствующих элементов И-НЕ группы, информационные входы регистра скорректированных контрольных раэрядов соединены с выходами соответствующих элементов ИСКЛЮЧАЩЕЕ ИЛИ группы, выходы регистра скорректированных . контрольных разрядов соединены с первыми входами соответствующих элементов И четвертой группы, вторые входы которых соединены с выходом элемента И-НЕ блока управления и вторыми входами элементов И третьей группы, группа выходов блока коммута45

50

S5

ции соедин мента- ИЛИ блока памя разрядов к входами со ИСКЛЮЧАЮЩЕ рядов приз соединены мационными ошибки, вх соединен с ходного ин и регистра рольных ра элемента Н которого о устройства гера ошибк ходом втор мента И-Н ключен к входы нача старших ра регистра и контрольн ключены к ва, вторые и второй элемента И вход кото третьего элемента дом начал ших разря регистра, блока ком вход зада ва, инвер вой групп рым входо ройства, ных входо группой в устройств блока ком третьего ния, выхо информаци выход кот ки коррек тринадцат выходного и выход п скорректи дов соеди дами перв выходы пя

25

5

10 ts ,.

20 равления,

с первыми

зо 5 0

5

0

5

ции соединена с группой входов эле мента- ИЛИ и группой адресных входов блока памяти, выходы информационных разрядов которого соединены с вторыми входами соответствуюшдх элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выходы разрядов признаков ошибки блока памяти соединены с соответствующими информационными .входами регистра хода ошибки, вход синхронизации которого соединен с входами синхронизации выходного информационного регистра и регистра скорректированных конт- : рольных разрядов и выходом первого элемента НЕ блока управления, вход которого объединен с тактовым входом устройства, вход синхронизации триггера ошибки коррекции соединен с выходом второго элемента НЕ блока уп- вход которого объединен входами элемента И и эле- :- мента И-НЕ блока управления и под ключен к тактовому входу устройства, входы начальной установки четырех старших разрядов входного контрольного регистра и регистра скорректированных контрольных разрядов объединены и подключены к установочному входу устройства, вторые входы всех элементов И первой и второй групп соединены с выходом элемента И блока управления, второй вход которого объединен с входом третьего элемента НЕ и вторым входом элемента И-НЕ блока управления, входом начальной установки шести млад- ших разрядов входного контрольного регистра, первым управляющим входом блока коммутации и образует первый вход задания режима работы устройства, инверсные входы элементов И первой группы объединены и являются вторым входом задания режима работы устройства, третья группа информационных входов блока коммутации является группой входов контрольной свертки устройства, второй управляющий вход блока коммутации соединен с выходом третьего элемента НЕ блока управления, выход элемента ИЖ соединен.с информационным входом триггера ошибки, выход которого является выходом ошибки коррекции устройства, выходы тринадцатого и шестнадцатого разрядов выходного информационного регистра и выход первого разряда регистра скорректированных контрольных разрядов соединены с соответствующими вхот- дами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы пятого и восьмого разрядов вы7 .1

ходного информационного регистра и второго разряда регистра скорректированных контрольных разрядов соединены с соответствующими входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход каждого i-ro элемента И первой группы объединен с выходом (i+8)-ro элемента И третьей группы (1 ), выход каждого 1-го элемента И третьей группы объединен с выходом (i+8)-ro элемента И первой группы, выход каждого 2j-ro элемента И второй группы

33

35 г

39721 8

объединен х: выходом (2j-1)-ro элемента И четвертой группы ( 5) , выход каждого (2j-1)-ro элемента И второй группы объединен с выходом 5 2j-ro элемента И четвертой группы, входы начальной установки четырех старших разрядов входного контрольного регистра и регистра скорректированных контрольных разря- 10 дов объединены и -подключены к входу начальной установки устройства.

ю

36

N)

Фиг.Ч

fpuz.5

Фиг.6

.Редактор Е.Папп

Составитель В.Гречнев .

Техред ОоСопко Ксфректор 0.Луговая

3398/50

-Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 1130355. Москва, , Раушская каб., д, 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

| Устройство для исправления двухкратных ошибок в блоках передачи и хранения информации | 1983 |

|

SU1173417A1 |

| Устройство для исправления ошибок в системах хранения и передачи информации в кодовой комбинации | 1984 |

|

SU1231503A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Устройство кодирования и декодирования информации | 1990 |

|

SU1783628A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1751762A1 |

| Декодер мажоритарных блоковых кодов | 1986 |

|

SU1349011A1 |

| Устройство для контроля и коррекции информации | 1980 |

|

SU940160A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Устройство для проверки схем контроля памяти | 1981 |

|

SU1015386A1 |

Изобретение относится к области вычислительной техники. Целью изобре- тения является повышение быстродействия устройства. Устройство содержит блок управления, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, входной информационный регистр, группу элементов НЕ, . ; формирователь синдрома ошибки, выходной информационный регистр, четыре группы элементов И, входной контрольный регистр, группу элементов И-НБ, два элемента ИС1ШЮЧАЮЩЕЕ ИЛИ., регистр кода ошибки, блок памяти, блок коммутации, элемент ИЛИ, элемент ошибки коррекции, регистр скорректированных контрольных разрядов. Повьш ение быстродействия достигается за счет введения блока памяти, с помощью которого по сигналам с выхода формирователя синдрома ошибки формируется константа, корректирующая принятый код с помощью группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Откорректированный код записывается на информационный выходной регистр, снабжается контрольными разрядами по модулю два и передается на информационный выход устройства. Самоконтроль устройства заключается в том, что откорректированный код подается на вход формирователя синдрома ошибки, который при неправильной корректировке на своем выходе формирует ненулевой сигнал, запоминаемый на тригере ошибки, С помощью формирователя синдрома ошибки могут формироваться контрольные разряды для инфор-, мационного кода и передаваться с помощью элементов И-НЕ на группу входов-выходов контрольных разрядов устройства. 8 ил. i СО С

| ГИДРАВЛИЧЕСКИЙ ТАРАН | 1921 |

|

SU533A1 |

| Каталог интегральных микросхем | |||

| - ЦНИИЭлектроника, 1983 | |||

| Expandable ТС finds and fixes er- Tojrs fast.- Electronic Desighn, 1982, Febr., p.177-186. | |||

Авторы

Даты

1986-06-23—Публикация

1984-11-22—Подача