(5) ЗАПОМИНАЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМ 01Ш1БОК

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Устройство для коррекции ошибок в блоках памяти с последовательным доступом | 1987 |

|

SU1510014A1 |

| Запоминающее устройство с исправлением ошибок | 1985 |

|

SU1297120A1 |

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| Запоминающее устройство с исправлением дефектов и ошибок | 1987 |

|

SU1536445A1 |

| Запоминающее устройство с исправлением ошибок | 1989 |

|

SU1667156A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

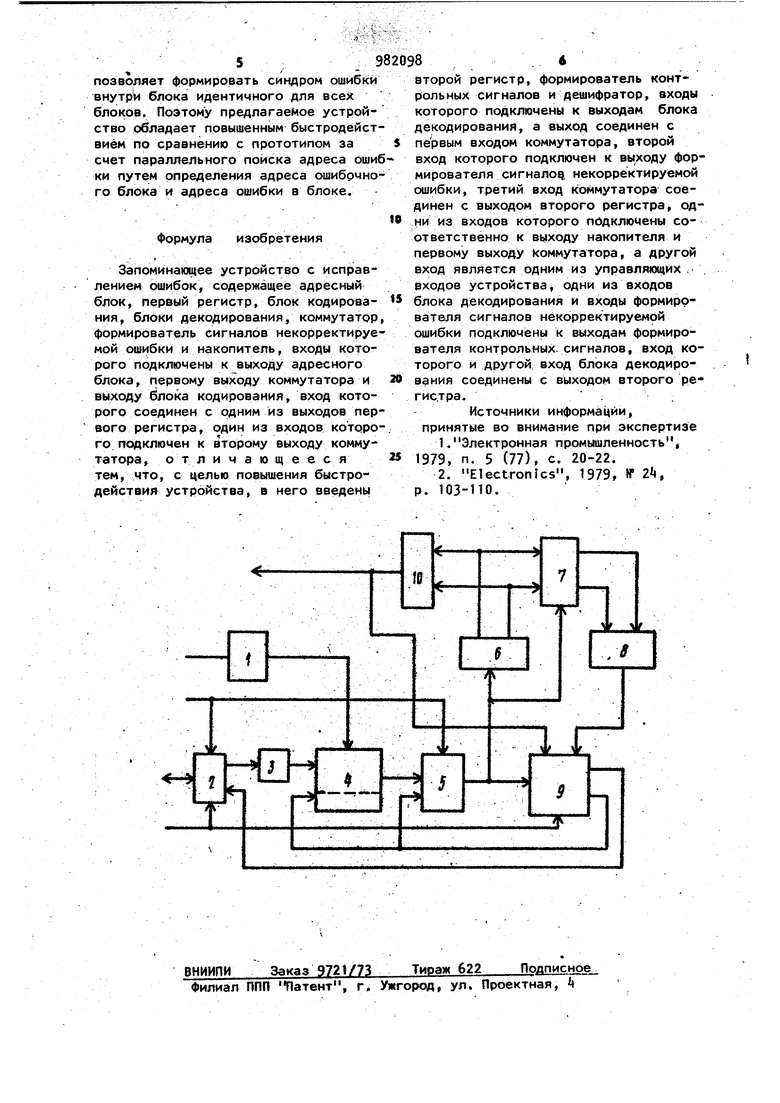

t . Изобретение относится к запоминаЪмцим устройствам. Известно запоминащее устройство (ЗУ) с исправлением ошибок, которое содержит основной накопитель, дополнительный накопитель, необходимый для хранения контрольных соотношений кодиру зщие и декодирующие устройства функционирующие соответственно при записи и при считывании О. Однако в этом ЗУ с ростом размера ин(|юрмационного слова ухудшается быс родёйствие. Это определяется необходимостью увеличения числа переменных используемых для формирования проверочных соотношений, которые, как пра вило, реализуются на сумматорах по модулю два, быстррдействие которых зависит от числа входов, т.е. числа ин(1юрмационных разрядов -и структуры кода. Например, при использовании ко дов Хемминга для исправления одиночных и обнаружения двойных ошибок чис ло входов сумматоров по модулю два кодирующего и декодирующего устройств увеличивается с трех (для инфррмацион ного слова размером четыре бита) до восемнадцати (для слова размером тридцать два бита). Известно, что данный класс с этой точки зрения является оптимальным, а другие классы обладают более худшими характеристиками. Таким образом, недостатком этого ЗУ является сложность обеспечения быстрого кодирования и декодирования двоичной информации на многоуровневых сумматорах по модулю два, т.е. существенное снижение быстродействия. Наиболее близким техническим решением к изобретению является запоминающее устройство с исправлением ошибок, содержащее накопитель, адресный блок, блоки кодирования и декодирования, ; коммутатор, формирователи сигналов. Принцип работы этого устройства основан на поразрядном сравнении контроль1НЫХ соотношений, формировании синдрома ошибки, определении адреса ошибки и инвертировании информационного содержания ячейки, определяемой данным. адресом. Формирование контрольных соотношений осуществляется с помощью многоуровневого сумматора по модулю два, В режиме считывания упомянутые многоуровневые сумматоры с последовательно подсоединеннь1м блоком двухвходовых сумматоров по модулюдва исполь зуются для формирования синдрома ошибки zj. Недостатком данного устройства является невысокой быстродействие, onpe деляемое задержками прохождения двоичного сигнала Ь многоуровневь х логиЧеских схемах кодирующего и декодирующего устройств. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в запоминающее устройство с исправлением ошибок, содержащее адресный блок, первый регистр, блок кодирЬвания,коммутатор, формирователь сигналов некорректируемой ошибки и накопитель, входы которого подключе ны к выходу адресного блока, первому выходу KOMMyTat9pa и выходу блока кодирования, вход которого соединен с одним из выходов первого регистра, один из входов которого подключен к второму выходу коммутатора, введены второй.регистр формирователь контроль ных сигналов и дешифратор, входы которого подключены к выходам блока декодирования, а выход соединен с первым входом коммутатора, второй вход которого подключен к выходу формирователя сигналов некорректируемой ошибки, третий вход коммутатора соединен с выходом второго регистра, одни из входов которого подключены соответственно к выходу накопителя и первому выходу коммутатора, а другой вход является одним из управляющих входов устройства, одни из входов бло ка декодирования и входы формирователя сигналов некорректируемой ошибки подключены к выходам формирователя контрольных сигналов, вход которого и другой вход блока декодирования соединены с вйходсда второго регистра. На чертеже изображена функциональная схема запоминающего устройства с исправлением ошибок. Устройство содержит адресный блок 1 первый регистр 2, служащий для (хранения входной информации, блок 3 кодирования, накопитель Ц, второй регистр 5, служащий для коррекции информации, формирователь 6 контрольных сигналов, выполненный в виде двухуровневого генератора синдрома ошибки, блок 7 декодирования, дешифратор 8, служащий для определения адреса ошибки и выполненный в виде двухуровневого блока, коммутатор 9 и формирователь 10 сигналов некорректируемой ошибки. Запись информации в ЗУ происходит следующим образом. Информационное слово заносится в регистр 2. Преобразованное слово из блока 3 записывается в накопитель по адресу, определяемому, блоком 1. Ни этом цикл записи заканчивается. В режиме считывания информации кодовое слово из накопителя 4 заносится в регистр 5, в котором происходит исправлением однократных ошибок, возникающих в ЗУ в процессе записи или хранения. В блоках 6 и 7 проиЬходит формирование синдрома ошибки, адрес которой определяется дешифратором 8. Формирование синдрома происходит путем разбиения информационного слова на блоки с последующим параллельным определением адреса ошибочного блока и адреса ошибочного разряда в блоке. Передача кода адреса ошибки на регистр 5 осуществляется через коммутатор 9. Данный коммутатор используется также для передачи исправленных выходных данных в регистр 2. Управление передачей данных через коммутатор 9 осуществляется формирователем 10 при наличии внешнего управляющего сигнала (не показан). Преобразованием информационного слова в блоках 6 и 7 производится в соответствии с модифицированным коДим Хемминга, представленным в матричной форме в таблице для информационного слова размером 16 бит. Структура кода, реализуемого в предлагаемом устройстве, такова, что позволяет формировать синдром ошибки внутри блока идентичного для всех блоков, Поэтому предлагаемое устройство обладает повышенным быстродейст вием по сравнению с прототипом за счет параллельного поиска адреса оши ки путем определения адреса ошибочно го блока и адреса ошибки в блоке. Формула изобретения Запоминающее устройство с исправлением ошибок, содержащее адресный блок, первый регистр, блок кодирования, блоки декодирования, коммутатор формирователь сигналов некорректируе мой ошибки и накопитель, входы которого подключены к выходу адресного блока, первому выходу коммутатора и выходу блока кодирования, вход которого соединен с одним из выходов пер вого регистра, один из входов котрро го подключен к второму выходу коммутатора, отличающееся тем, что, с целью повышения быстродействиям устройства, в него введены

швторой регистр, формирователь контрольных сигналов и дешифратор, входы которого подключены к выходам блока декодирования, а выход соединен с первым входом коммутатора, второй вход которого подключен к выходу формирователя сигналов, некорректируемой ошибки, третий вход коммутатора соединен с выходом второго регистра, одни из входов которого подключены соответственно к выходу накопителя и первому выходу коммутатора, а другой вход является одним из управляющих . входов устройства, одни из входов блока декодирования и входы формирователя сигналов некорректируемой ошибки подключены к выходам формирователя контрольных сигналов, вход которого и другой вход блока декодирования соединены с выходом второго регистра. . Источники информации, принятые во внимание при экспертизе 1.Электронная промышленность, 1979, п. 5 (77), с. 20-22. 2. ElectronJcs, 1979, № 2k, p. 103-110.

г-i

Авторы

Даты

1982-12-15—Публикация

1981-02-25—Подача