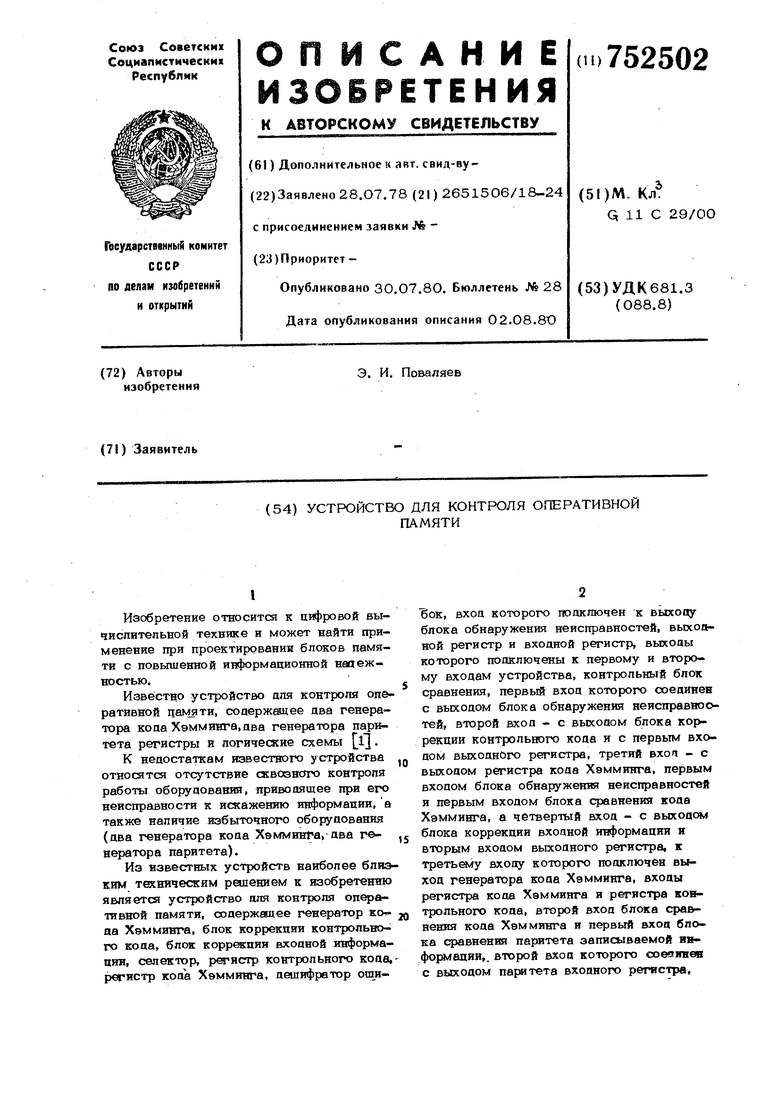

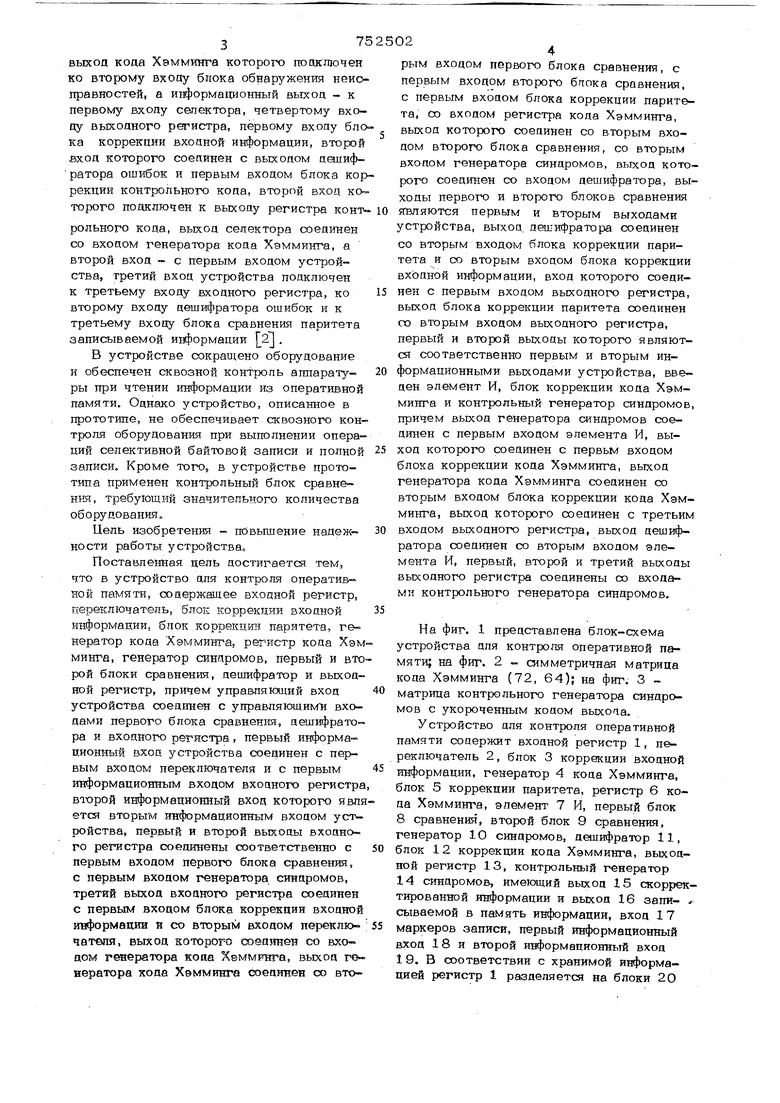

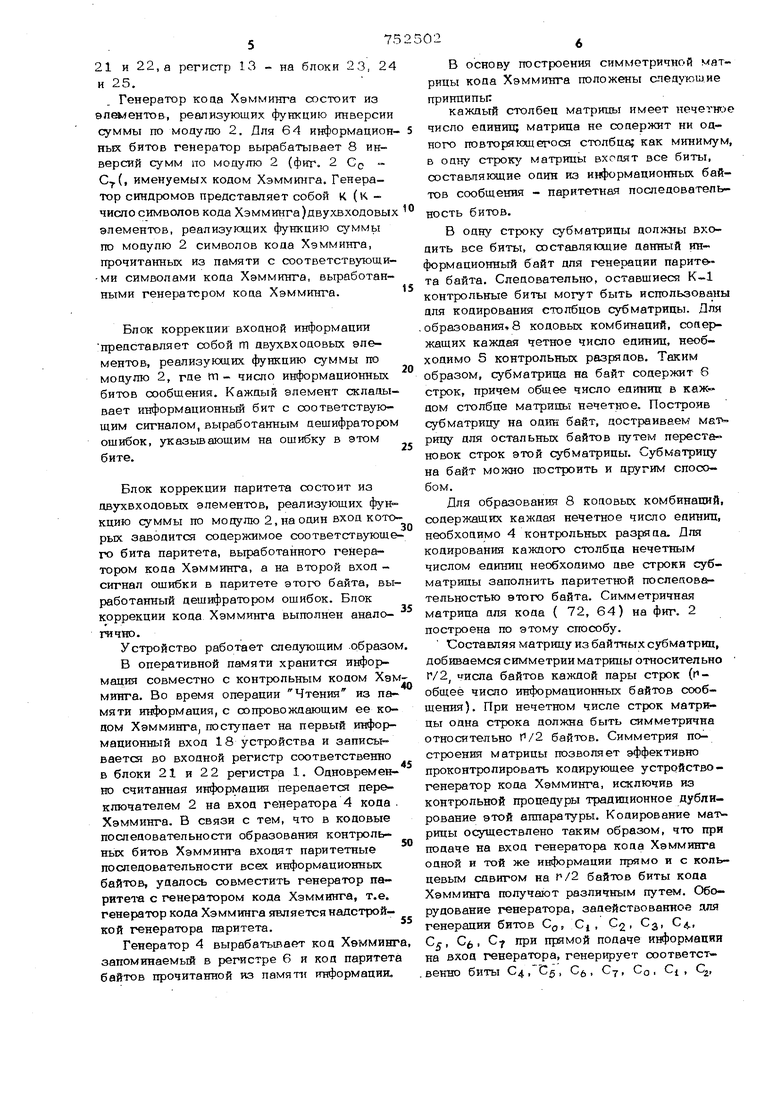

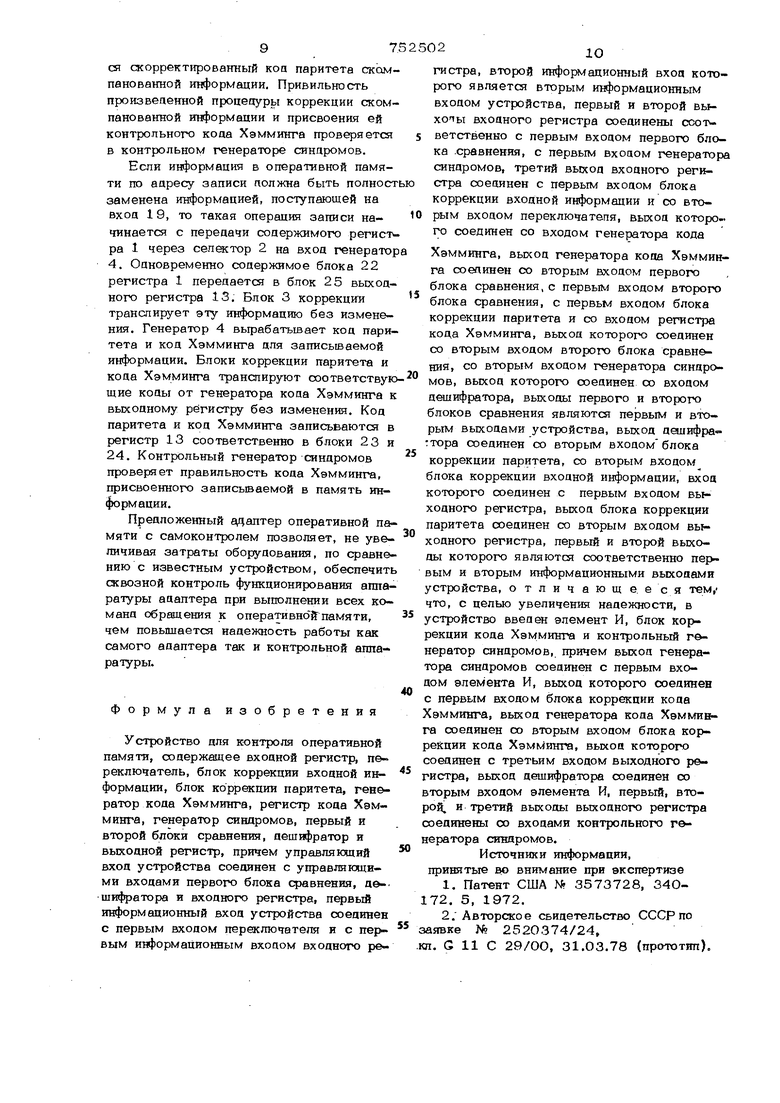

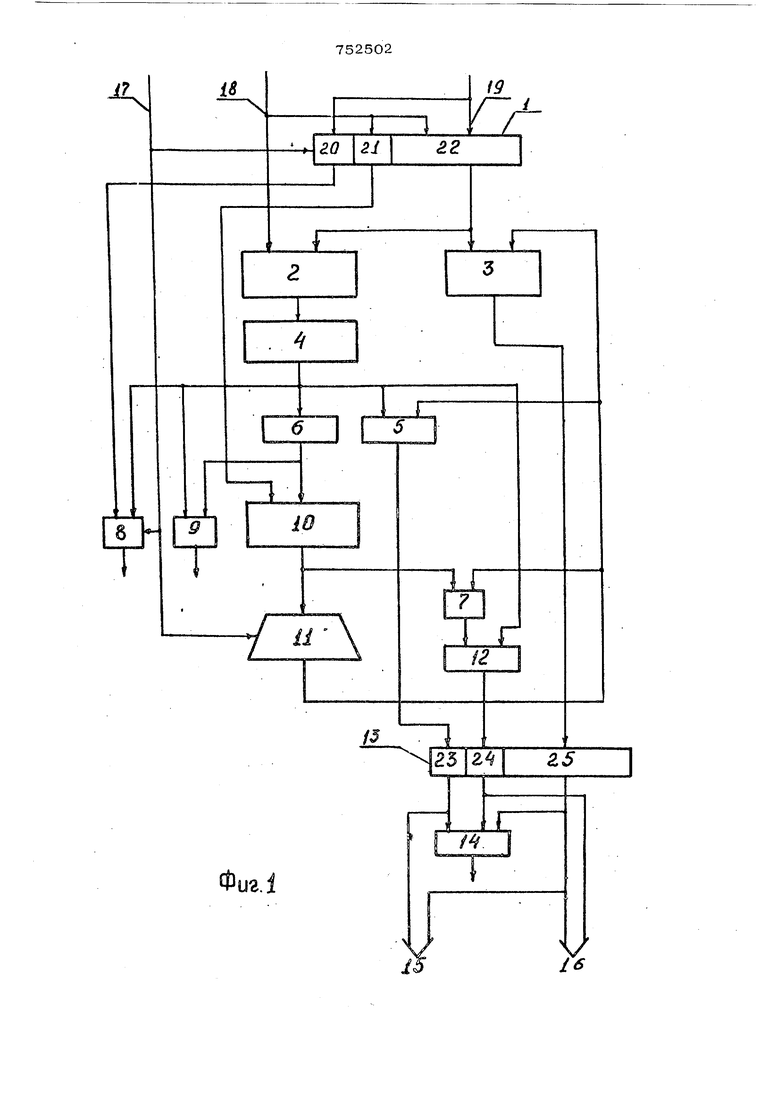

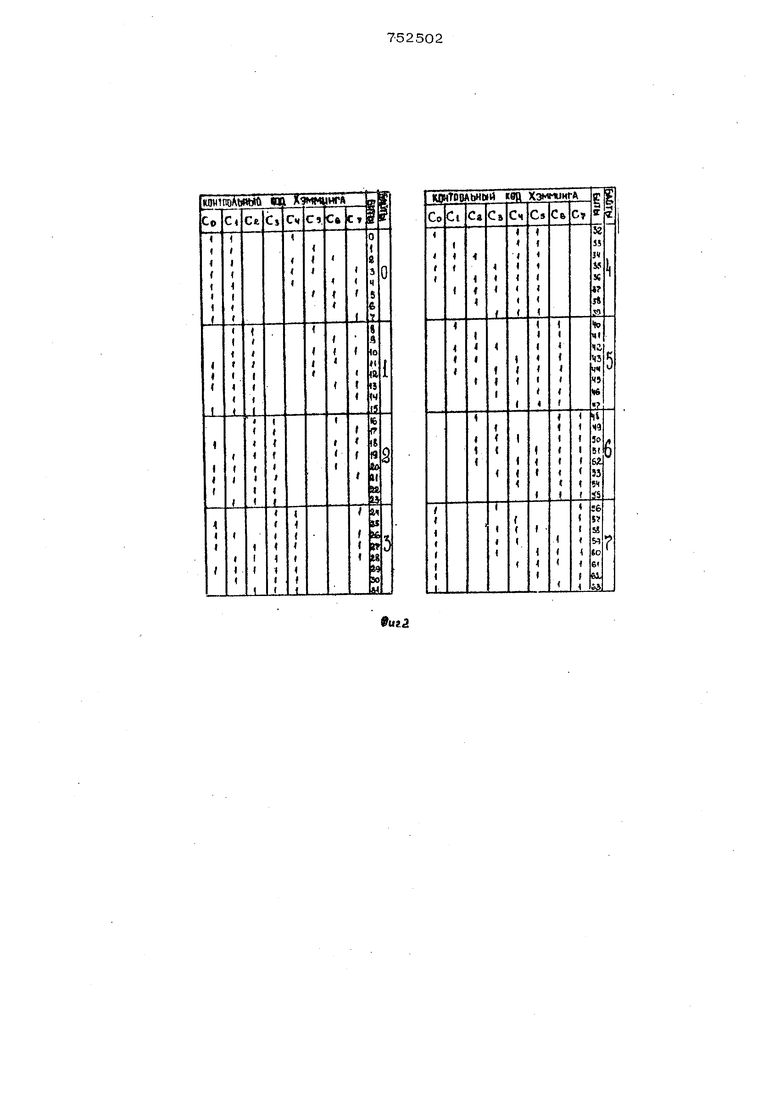

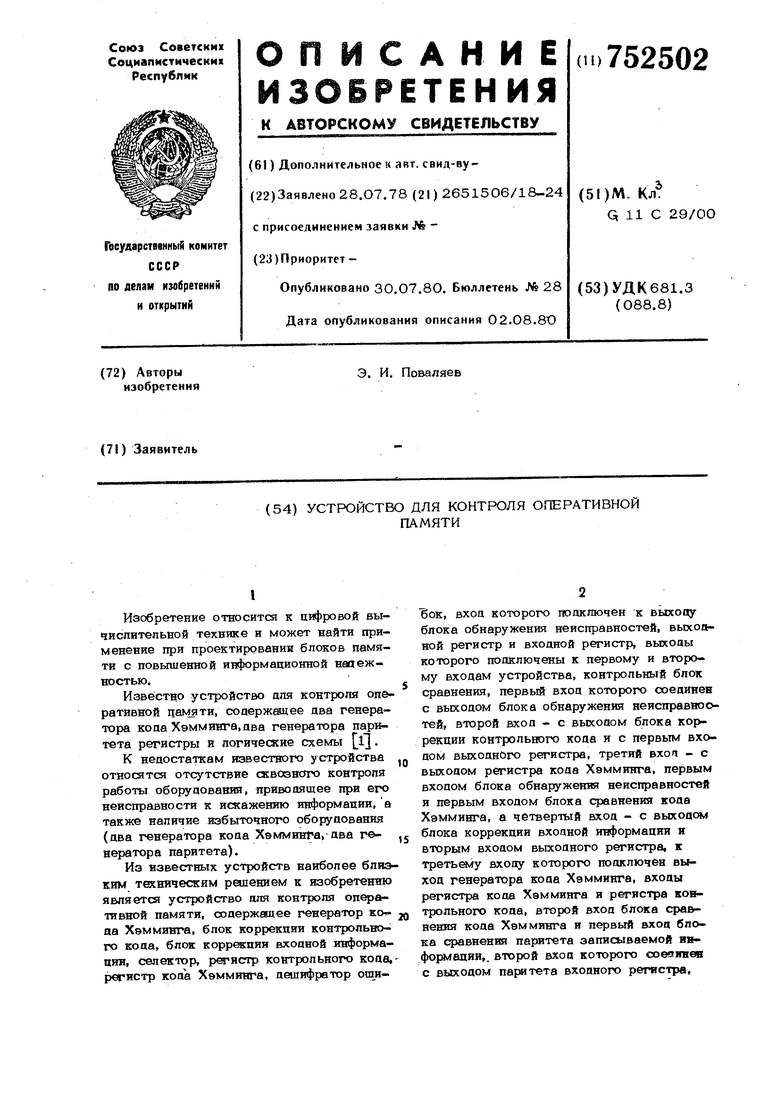

Изобретение относится к цифровой вычиспитепьной технике и может найти применение нрн проектировании блоков памяти с повышенной информационной надежностью. Известно устройство дпя контроля оперативной памяти, сооержещее два генератора копа Хэмминга, два генератора паритета регистры и логические схемы i. К недостаткам известного устройства относятся отсутствие сквазного контроля работы оборудования, приводящее при его неисправности к искажению информации, а также наличие избыточного оборудования (два генератора кода Хвммннга, два генератора паритета). Из известных устройств наиболее близ ким техническим решением к изобретению является устройство для контроля оп атавной памяти, со держан ее генератор ко аа Хэмминга, блок коррекции контрольного кода, блок входной информации, селектор, регистр контрольного кода, регистр кода Хемминга, дешифратор ошн- бок, вход которого подключен к выходу блока обнаружения неисправностей, выходной регистр и входной регистр, выходы которого подключены к первому и второму входам устройства, контрольный блок сравнения, первый вход которого соединен с выходом блока обнаружения неисправностей, второй вход - с выходом блока коррекции контрольнотх кода и с первым входом выходного регистра, третий вхоа - с выходом регистра кода Хэмминга, первым входом блока обнаружения неисправностей и первым входом блока сравнения кода Хэмминга, а четвертый вход - с выходом блока коррекции входной информации и вторым входом выходного регистра, к треть&лу входу которого подключен выход генератора кода Хэмминга, входы регистра кода Хэмминга и регистра контрольного кода, второй вход блока сра&нения кода Хэммннга и вход блока сравнения паритета записываемой ввформации,. второй вход которого соеаянея с выходом парттета входного регистра. ВЫХОД кода Хэмминга которого поокпючен ко в1Т)рому входу блока обнаружения неисправностей, а И1г})орма1шонный выход - к первому входу селектора, четвертому входу выходного регистра, первому входу бло ка коррекции входной информации, второй вход которого соединен с выходом дэциф ратора ошибок и первым входом блока кор рекции контрольного кода, второй вход которого подключен к выходу регистра контрольного кода, выход селектора соединен со входом генератора кода Хэмминга, а второй вход с первым входом устройства, третий вход устройства подключен к третьему входу входного регистра, ко второму входу дешифратора ошибок и к третьему входу блока сравнения паритета записываемой информации 2 . В устройстве сокращено оборудование и обеспечен сквозной контроль аппаратуры при чтении информации из оперативной памяти. Однако устройство, описанное в прототипе, не обеспечивает сквозного контроля оборудования при выполнении операций селективной байтовой записи и полной записи. Кроме того, в устройстве прототипа применен контрольный блок сравнеW-я, требующий значительного количества оборудования. Цель изобретения - пОвьппение надежности работы устройства Поставленная цель достигается тем, что в устройство для контроля оперативной памяти, содержащее входной регистр, Г(ереключатель, блок коррекции входной информации, блок коррекцш паритета, генератор кода Хэмминга, регистр кода Хэм минга, генератор синдромов, первый и вто рой блоки сравнения, дешифратор и выходной регистр, причем управляющий вход устройства соединен с управляющими входами первого блока сравненгет, дешифратора и входного регистра, первый информационный вход устройства соединен с первым входом переключателя и с первым информационным входом входного регистра вахзрой информационный вход которого явля ется вторым информационным входом уст ройства, первый и вторюй выходы входного регистра соединены соответственно с первым входом первого блока сравнения, с первым входом генератора синдромов, третий выход входного регистра соединен с первым входом блока коррекции входной информации и со вторым входом переключатепя, выход которого соединен со входом генератора кода Хвмминга, выход генератора кода Хэммннга соединен со вторым входом первого блока сравнения, с первым входом второго блока сравнения, с первым входом блока коррекции паритета, со входом регистра кода Хэмминга, выход которого соединен со вторым входом второго блока сравнения, со вторым входом генератора синдромов, выход которого соединен со входом дешифратора, выходы первого и второго блоков сравнения 5Гвляются первым и вторым выходами устройства, выход, дешифратора соединен со вторым входом блока коррекции паритета и со вторым входом блока коррекции входной информации, вход которого соединен с первым входом выходного регистра, выход блока коррекции паритета соединен со вторым входом выходного регистра, первый и второй выходы которого являются соответственно первым и вторым информационными выходами устройства, введен элемент И, блок коррекции кода Хэммипга и контрольный генератор синдромов, причем выход генератора синдромов соединен с первым входом элемента И, выход которого соединен с первьм входом блока коррекции кода Хэмминга, выход генератора кода Хэмминга соединен со вторым входом блока коррекции кода Хэмминга, выход которого соединен с третьим входом выходного регистра, вькод дешифратора соединен со вторым входом элемента И, первый, второй и третий выходы выходного регистра соединены со входами контрольного генератора синдромов. На фиг. 1 представлена блок-схема устройства для контроля оперативной памяти; на фиг. 2 - симметричная матрица кода Хэмминга (72, 64); на фиг. 3 матрица контрольного генератора синдромов с укороченным кодом выхода. Устройство для контроля оперативной памяти содержит входной регистр 1, переключатель 2, блок 3 коррекции входной информации, генератор 4 кода Хэмминга, блок 5 коррекции паритета, регистр 6 кода Хэмминга, элемент 7 И, первый блок 8 сравнения, вахэрой блок 9 сравнения, генератор Ю синдромов, дешифратор 11, блок 12 коррекции кода Хэмминга, выходной регистр 13, контрольный генератор 14 синдромов, имеющий выход 15 скорректированной ятформации и выход 16 записываемой в память информации, вход 17 маркеров записи, первый информационный вход 18 и второй информационный вход 19. В соответствии с хранимой информацией регистр 1 разделяется на блоки 20 21 и 22, а регистр 13 - на блоки 23, 2 и 25. Генератор кона Хэмминга сюстоит из 9па/(ентов, реализующих функцию инверсии суммы по модулю 2. Для 64 информацион ньк битов генератор вырабатывает 8 инверсий сумм по модулю 2 (фиг. 2 С Cf{, именуемых кодом Хэмминга. Генератор синдромов представляет собой к (К число символов кода Хэмминга )двухвходовы элементов, реализующих функцию суммы по моаупю 2 символов коаа Хэмминга, прочитанных из памяти с соответствующи ми символами кода Хэмминга, выработанными генератором кода Хэмминга. Блок коррекции входной информации представляет собой m двухвходовых элементов, реализующих функцию суммы по модулю 2, где m - число информационных битов сообщения. Каждый элемент склады вает информационный бит с соответствующим сигналом, выработанным дешифратором ошибок, указывающим на ошибку в этом бите. Блок коррекции паритета состоит из двухвходовых элементов, реализующих функцию суммы по модулю 2, на ооин вход кото рых заводится содержимое соответствующе го бита паритета, выработанного генератором кода Хэмминга, а на второй вход сигнал ошибки в паритете этого байта, вы работанный дешифратором ощибок. Бпок коррекции кода Хэмминга выполнен аналогично. Устройство работает следующим .образо В оперативной памяти хранится информация совместно с контрольным кодом Хэм минга. Во время операции Чтения из памяти информация, с сопровождающим ее кодом Хэмминга, поступает на первый информационный вход 18 устройства и записывается во входной регистр соответственно в блоки 21 и 2 2 регистра 1. Одновременно считанная информация передается переключателем 2 на вход генератора 4 коаа Хэмминга. В связи с тем, что в кодовые последовательности образования контрольных битов Хэмминга входят паритетные последовательности всех информационных байтов, удалось совместить генератор паритеа а с генератором кода Хэммттга, т.е. генератор кода Хэмминга является надстройкой генератора паритета. Генератор 4 вырабатывает код Хемминг запоминаемый в регистре 6 я код паритета байтов прочитанной из памяти ттнформации. В основу построения симметричной матрицы кода Хэмминга положены спедующие принципьк каждый столбец матрицы имеет нечегж е число единищ матрица не содержит ни одного повторяющегося столбца; как минимум, в одну строку матрицы входят все биты, составляющие один из и }юрмационных байтов сообщения - паритетная последовательность битов. В одну строку субматрицы должны входить все биты, составляющие данный информационный байт для генерации паритета байта. Следовательно, оставшиеся К-1 контрольные биты могут быть использованы для кодирования столбцов субматрицы. Для , образования 8 кодовых комбинаций, содер жащих каждая четное число единиц, необходимо 5 контрольных разрядов. Таким образом, субматрица на байт содержит 6 строк, причем общее число единиц в каждом столбце матрицы нечетное. Построив субматрицу на один байт, достраиваем мать рицу для остальных байтов путем перестановок строк этой субматрицы. Субматрицу на байт можно построить и другим способом. Для образования 8 кодовых комбинаций, содержащих каждая нечетное число единиц, необходимо 4 контрольных разряда. Для кодирования каждого столбца нечетным числом единиц необходимо две строки субматрицы заполнить паритетной последовательностью этого байта. Симметричная матрица для кода ( 72, 64) на фиг. 2 построена по этому способу. Составляя матрицу из байтных субматриц, добиваемся симметрии матрицы относительно r/2j числа байтов каждой пары строк (г общее число информационных байтов сообщения). При нечетном числе строк матрицы одна строка должна быть симметрична относительно /2 байтов. Симметрия построения матрицы позволяет эффективно проконтролировать кодирующее устройствогенератор кода Хэмминга, исключив из контрольной процедуры традиционное дублирование этой аппаратуры. Кодирование матрицы осуществлено таким образом, что при пояаче на вход генератора кода Хэмминга одной и той же информации прямо и с кольцевым сдвигом на байтов биты кода Хэмминга получают различным путем. Оборудование генератора, задействованное для енерации битов Сд, С , С2 i Сз, С., С, С, С- при прямой подаче информации а вход генератора, генерирует соответстенно биты С4, Cg , Cjs, Су, Со, С , С, С при подаче той же ин|)ормащ1и с кольцевым сдвигом. В генераторе 10 синдромов производится сравнение контрольного кода Хэммннга, прочитанного из памяти (блок 21 регистра 1) с выработанным генератором 4 кодом (регистр 6). Дш каждого контрольного бита вырабатьшается сигнал реаупьтата cpajB .нения, назьшаемый синдромом. Синдромные биты декодируются дешифратором 11.Сиг. нал ошибки определяет действительныйоши- бочный бит и инвертирует -его посредством блока 3, связанного с каждым битом. Обнаружение дешифратором 11 четного числа шстивизированных синдромных битов указывает на некорректируемую ошибку. При исправлении однобитной оцгибки исправляется также и паритет байта посредством блока 5 коррекции. Скорректированные паритет и информация записьюаются соответственно в блоки 23 и 25 регистра 13. Параллельно с вышеописанной процедурой исправления одиночной ошибки устройство выполняет следующие контрольные аействия. После записи в регистр 6 перекпюч-атель 2 подключает на вход генерато« пй 4 блок 22 регистра 1 с кольцевым cs&KTOM на Р/2 байтов. Результаты обеих генераций должны совпадать, если соответ ствующее оборудование устройства функционирует правильно. Сравнение результатов г-энераций осуществляется во втором бло-. ке 9 сравнения. Правильность коррекции информации про;-зрябтся контрольным генератором 14 синд-; pCMOBj который состоит изК/2 блоков сложе- . ния по модулю 2 Контрольный генератор 14 синдромов реапизует К/2 проверок (фиг. З). В общем виде при построении контрольного генератора синдромов принимают во внимание спедующее обстоятельство; Лю бые две генераций синдромных битов состоят из трех частей О Ь vi с в имеют следутощШ вгщ о + b О С + b 0, где а Ъ и с - суммы по модулю 2 группы символов сообщения, не входящие в другие части. Отсюда т.е. из каждой пары генераций синдромны битов можно исключить общую часть Ь. Кроме того, из каждой пары генераций MOJKEO ИСКЛЮЧИТЬ паритетные поспеаова-. тельюсти символов, заменив их величиной паритета ооответств тощего байта. В кон трольный генератор сяндромов поступает также скорректировавцый в блоке 12 псев яоэтапонный коп Хэмминга, который корректируется сигналами синдромов с генеpaixipa 10 через К элементов 7 И, при наличии команды Vj с дешифратора 11, подаваемой на второй вход элементов И У (ОШРр-ОШР....ОШ.Р УОШРо- xMQVOUP MiV.-.,) ОШСц- ошибка бите кода ХэммингаObiPf. - ошибка в паритете ( маркер записи Скорректированный.код Хэмминга записывается в блок 24 регистра 13. Активизированньй вькод контрольного генератора 14 синдромов указьшает на логическую ошибку в аппаратуре устройства. Операция селективной байговой записи в оперативную память начинается с функции чтения с последующей записью. Информация, подлежащая записи, поступает на второй информационный вход 19, сопровождаемая битами паритета и маркерами записи, поступающими на вход маркеров записи. Информационная часть сообщения записывается в блок 22, а паритет сообщения - в блок 2 О входного регистра 1. Считанная из памяти информация, сопровождаемая кодом Хэмминга, поступает на первый информационньй вход 18 и записььвается совместно с записьваемой информацией в блок 22 входного регистра под управлением марсеров записи, а код Хэмминга записывается в блок 21. Одновременно.считанная из памяти информация,коммутируется переключателем 2 на вход генератора 4 кода Хэммиига. Генератор вырабатывает контрольньй код, запоминаемый в регистре 6. Переключатель 2 коммутирует содержимое входного регистра 1 на вход генератора 4. Выработанный генератором код Хэмминга поступает в блок 12 коррекции, а код паритета сравнивается в первом блоке 8 сравнения с паритетом информации входа 19 под управлением маркеров записи. Аналогично вышеописанной процеду1эе чтения блок 10 и дешгя{)ратор 11 ошибок вьфабатывают синдромный код и сигнал ошибки бита сообщения. Однако, еспи ошибочньй бит находится в байте, который не перезаписан в память, он не корректируется. Коррекции записываемой в память информации и присяэоенного ей коаа Хэмминга.осуществляется блоком 3 и блоком 12, которые передают скорректрфованное сообшение в блоки 25 и 24. выходного регистра 13. В блок 23 регистра 13 записывается скоррекпфованный коп паритета скомпанованной информации. Привильность произведенной процеоуры коррекции скомпанованной информации и присвоения ей контрольного кода Хэмминга проверяется в контрольном генераторе синдромов. Если информация в оперативной памяти по адресу записи должна быть полност заменена информацией, поступающей на вход 19, то такая операция записи начинается с передачи содержимого регистра 1 через селектор 2 на вход генератор 4. Одновременно содержимое блока 22 регистра 1 передается в блок 25 выходного регистра 13. Блок 3 коррекции транслирует эту информацию без изменения. Генератор 4 вьфабатьшает код паритета и код Хэмминга для записываемой информации. Блоки коррекции паритета и кода Хэмминга транслируют соответствую щие коды от генератора кода Хэмминга к выходному регистру без изменения. Код паритета и код Хэмминга зацисьваются в регистр 13 соответственно в блоки 23 и 24. Контрольный генератор синдромов проверяет правильность кода Хэмминга, присвоенного записьшаемой в память информации. Предложенный адаптер оперативной памяти с самоконтролем позволяет, не увеличивая затраты оборудования, по сравнению с известным устройством, обеспечить сквозной контроль функционирования аппаратуры адаптера при выполнении всех команд обращения к оперативно памяти, чем повышается надежность работы как самого адаптера так и контрольной аппаратуры. формула изобретения Устройство для контроля оперативной памяти, содержащее входной регистр, переключатель, блок коррекции входной информации, блок коррекции паритета, ген&ратор кода Хэмминга, регистр кода Хэмминга, генератор синдромов, первый и второй блоки сравнения, дешифратор и выходной регистр, прячем управляющий вход устройства соединен с управляющими входами первого блока сравнения, де-. шифратора и входного регистра, первый информационный вход устройства соединен с первым входом переключателя и с первым информационным входом входного ре702.Q гистра, второй информационный вход которого является вторым информационным входом устройства, первый и второй выходы входного регистра схэеаинены ссот ветственно с первым входом первого блока .сравнения, с первым входом генерагора синдромов, третий выход входного регистра соединен с первым входом блока коррекции входной информации и со вторым входом переключателя, выход которого соединен со входом генератора кода Хэмминга, выход генератора кода Хэмминга соединен со вторым входом первого блока сравнения, с первым входом второго блока сравнения, с первьм входом блока коррекции паритета и со входом регистра кода Хэмминга, выход которого соединен со вторым входом второго блока сравнения, со вторым входом генератора синдромов, вькод которого соединен со входом дешифратора, выходы первого и второго блоков сравнения являются первым и вторым выходами устройства, выход дешифраттора соединен со вторым входом блока коррекции паритета, со вторым входом блока коррекции входной информации, вход которого соединен с первым входом выходного регистра, выход блока коррекции паритета соединен со вторым входом вььходного регистра, первый и второй выходы которого являются соответственно и вторым информационными выходами устройства, отличающееся тем,что, с целью увеличения надежности, в устройство введен элемент И, блок коррекции кода Хэмминга и контрольный г&нератор синдромов, причем выход генератора синдромов соединен с первым входом элемента И, выход которого соединен с первым входом блока коррекции кода Хэмминга, выход генератора кода Хэмминга соединен со вторым входом блока коррекции кода ХэмМинга, выхоа которого соединен с третьим входом выходного регистра, выход дешифратора соединен со вторым входом элемента И, первый, второй, и третнй выходы выходного регистра соединены со входами контрольного г&нератора синдромов. Источники информации, принятые ЕЮ внимание при экспертизе 1.Патент США № 3573728, 34О172. 5, 1972. 2.Авторское свидетельство СССР по аявке М 2520374/24, п. G 11 С 29/ОО, 31.03.78 (прототип).

iS

го

19

EZH

&г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи и воспроизведения информации из блоков оперативной памяти с коррекцией ошибки | 1977 |

|

SU974410A1 |

| Устройство для контроля оперативной памяти | 1977 |

|

SU720515A1 |

| Устройство для коррекции ошибокС САМОКОНТРОлЕМ | 1977 |

|

SU796847A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Устройство для обнаружения и коррекции одиночных ошибок | 1982 |

|

SU1075313A1 |

| Устройство для обнаружения и ис-пРАВлЕНия ОшибОК B блОКАХ ВычиСли-ТЕльНОй МАшиНы | 1979 |

|

SU840912A1 |

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

| Устройство для контроля блоков оперативной памяти | 1980 |

|

SU940242A1 |

| Устройство для коррекции микрокоманд | 1984 |

|

SU1164709A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

ГТП 15

Фи.д

Авторы

Даты

1980-07-30—Публикация

1978-07-28—Подача