Изобретение относится к импульсной технике и предназначено для автоматической поверки цифроаналоговых преобразователей (ЦАП).

Известно устройство для контроля параметров цифроаналогового преобразователя, содержащее генератор тактовых импульсов, логическую схему, двоичный счетчик, блок согласования, многовходную логическую схему, контролируемый ЦАП, дифференциатор, импульсный усилитель, запоминающий бло переключатель, двухпороговую схему и блок управления Lll .

Недостатк 1ми этого устройства явЛяются низкая точность и невозможнос непосредственного определения дифференциальной нелинейности ЦАП.

Наиболее близким по технической сущности к изобретению является устройство для измерения погрешности ли нейности цифроаналогового преобразователя, содержащее генератор импульсов, счетчик, выход которого соединен с входом контролируемого цифроаналогового преобразователя (ЦАП), выход которого подключен к первому входу компаратора, генератор линейно изменяюшегося напряжения (ГЛИН), выход которого соединен с вторым входом компаратора, выход которого подключен к входу триггера С2 .

Недостатками известного устройств являются низкое быстродействие и ограниченная точность, обусловленные тем,что за одну развертку изменяющегося эталонного напряжения производится определение одного значения выходного сигнала контролируемого IJlAn, при этом нелинейность ГЛИН полностью входит в погрешность измерения.

Цель изобретения - повввиение быстродействия и точности.

Поставленная цель достигается тем что в измеритель нелинейности цифроаналоговых преобразователей, содержа щий генератор импульсов, счетчик, выход которого соединен с входом и контролируемого цифроаналогового преобразователя, выход которого подключен к первому входу компаратора, генератор линейно изменяющегося напряжения, выход которого соединен с вторым входом компаратора, выход которого подключен к входу триггера, введены два коммутатора, два реверсивных счетчика, блок памяти, переключатель и элемент задержки причем вход первого коммутатора соединен с выходом генератора импульсов, первый и второй выходы первого коммутатора соединены с первым и вторым вхо дами первого реверсивного счетчика, а третий и четвертый выходы - с первым и втopы /I входами второго реверсивного счетчика, выходы реверсивных счетчиков подключены к соответствующим входам второго коммутатора, выход которого подключен к первому входу блока памяти, при этом выход триггера соединен с управляющими входами первого коммутатора и переключателя и с первым управляющим входом второго коммутатора, второй управляющий вход которого соединен с входами триггера, счетчика и через элемент задержки - с входом переключателя, первый и второй выходы которого соединены с управляющими входа ми соответствующих реверсивных счетчиков, кроме того, выход счетчика подключен к второму входу блока памяти.

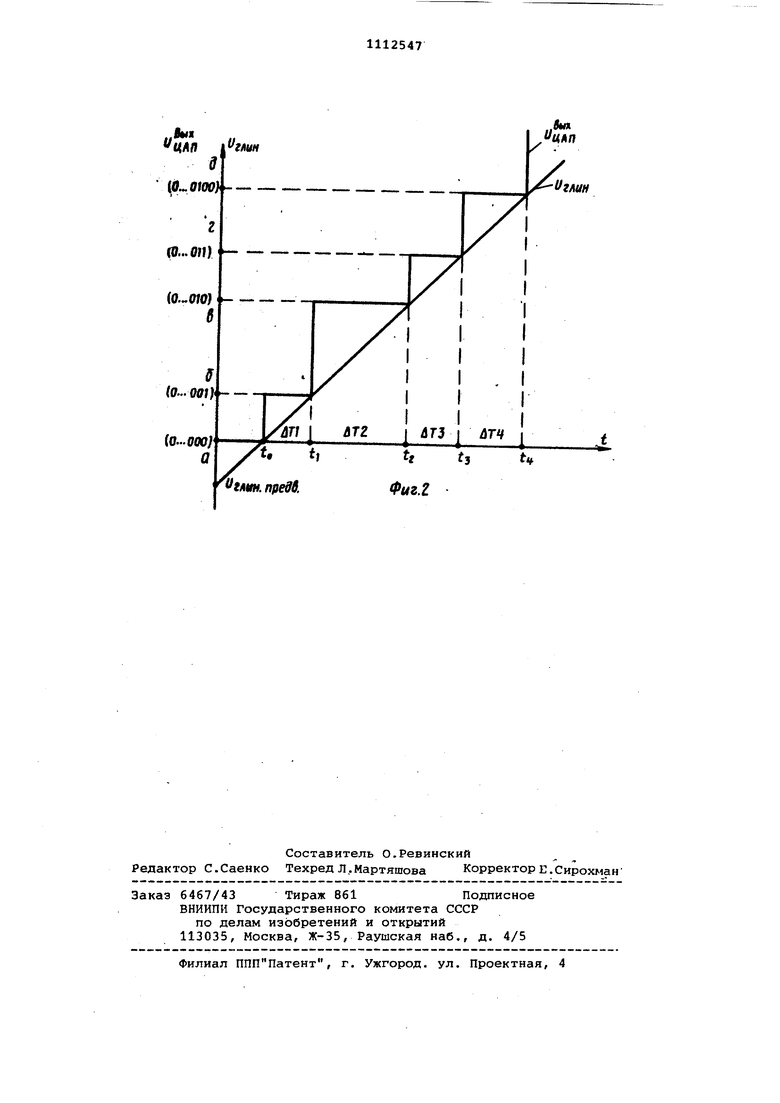

На фиг. 1 представлена функциональная схема устройстваi на фиг. 2 временная диаграмма, поясняющая принцип его действия.

Устройство содержит генератор 1 .ИМПУЛЬСОВ , счетчик 2, контролируе Пый цифроаналоговый преобразователь (ЦАП) 3, компаратор 4, генератор 5 линейно изменяющегося напряжения (ГЛИН), триггер б, коммутаторы 7 и 8 реверсивные счетчики 9 и 10, блок 11 памяти, переключатель 12 и элемент 13 задержки.

Выход счетчика 2 подключен к вход ЦАП 3, выход которого соединен с первым входом компаратора 4, второй вхо которого подключен к выходу генератора 5 линейно изменяющегося напряжения, а выход через триггер б - к управляющим входам первого коммутатора 7, переключателя 12 и первому управляющему входу второго коммутатора 8. В то же время вход триггера 6 соединен с вторым управляющим входом коммутатора 8, счетным входом счетчика 2 и через элемент 13 задержки с входом переключателя 12.

Выход генератора 1 импульсов подсоединен к входу первого коммутатора 7, первый и второй выходы которого подключены соответственно к суммирующему и вычитающему входам первого реверсивного счетчика 10, а третий и четвертый выходы - к суммирующему и вычитающему входам второго реверсивного счетчика 9. Входы Сброс реверсивных счетчиков 9 и 10 соединены с соответствующими выходами переключателя- 12, а выходы - с соответствующими входами коммутатора 8, подключенного выходом к первому входу блока 11 памяти, второй вход которого подключен к выходу счетчика 2 Устройство работает следующим образом.

В исходном состоянии все счетчики 2, 9 и 10 сброшены, триггер б находится в нулевом состоянии, импульсы с выхода генератора 1 через коммутатор 7 на вход счетчиков 9 и 10 не поступают. На выходе контролируемо1:о ЦАП 3 присутствует напряже ние Uutn (0...000), соответствующее коду О,..000 на его входе (фиг. 2а .

Нч1 второй вход компаратора 4 с выхода ГЛИН 5 поступает постоянное напряжение иклинпрел: причем минимально возможное значение uj (О...000) ирдц (фиг. 2а). С момента запуска с выхода генератора 1 на вход коммутатора 7 начинают поступать счетные импульсы, напряжение на выходе ГЛИН 5 начинает линейно нарастать, ив момент равенства Оглиц (to) U (0...000) компаратор 4 переходит в единичное состояние, перебрасывая из нулевого состояния триггер б. Одновременно в младший разряд счетчика 2 заносится счетный импульс. Изменившийся код.подаваемый на вход ЦАП 3, формирует на выходе последнего сигнал Uyl (0...001). При этом компаратор 4 возвращается в нулевое состояние. Единичное состояние на выходе триггера 6 подключает выход генератора 1 к суммирующему входу реверсивного счетчика 10, разрешая заполнение его счетными импульсами в течение интервала дТ (фиг. 26 , оканчивающегося в момент t равенст(ва , (ti) и (0...001), т.е. Ь течение интервала лТ в счетчике 10 формируется код, пропорцинальный приращению iUi напряжения на выходе ЦАП 3 при смене его входного кода от 0...000 до 0...001. Аналогично моменту to в момент ti на выходе компаратора 4 формируется управляющий импульс, возвращающий триггер б в нулевое состояние. О на выходе триггера б управляет коммутатором 7 таКИМ образом, что в течение интервала ATt. до момента рвенства ирду, (tj ) uS5i (0...010) импульсы с генератора 1 поступают на суммирующий вход счетчика 9 и вычитающий вход счетчика 10 Таким образом, в момент tj в счетчике 9 формируется код, пропорционал ный приращению iUj, а в счетчике 10 пропорциональный разности ли л - U ,

т.е. дифференциальной нелинейности ЦАП 3 в точке, соответствующей коду 0.,.001. В момент tj действия импульса на выходе компаратора 4, согласно управляющему уровню на выходе триггера 6, коммутатор 8 разрешает занесение в блок 11 памяти оценки дифференциальной нелинейности, сформированной в счетчике 10, после чего с задержкой, определяемой элементом 13, с соответствующего выхода переключателя 12 на счетчик 10 поступает сбросовый импульс. В течение следующего интервала дТ} тактовые импульсы с выхода генератора 1 поступают через коммутатор 7 на суммирующий вход счетчика 10 и вычитающий вход счетчика 9, Таким образом, в реверсивных счетчиках 9 и 10 поочередно формируются оценки дифференциальной нелинейности ЦАП 3 в соответствующих точках шкалы, также заносимых в блок 11 памяти с выхода счетчика 2.

Повышение точности измерителя обусловлено уменьшением зависимости получаемой оценки от нелинейности и временной нестабильности в скорости нарастания ,так как для определения дифференциальной нелинейности преобразователей используется не полный размах , а сравниваются значения двух соседних квантов, т.е. лишь незначительный участок развер- ки, перекрывающий два соседние кванта ЦАП 3, поэтому, поскольку линейность на малом участке значительно выше, чем при полном размахе , при использовании одного и того же генератора линейно изменяющегося напряжения погрешность оценки из-за нелинейности эталонного напряжения существенно меньше.

Повышение быстродействия предлагаемого измерителя обусловлено тем, что в нем за одну развертку UOM« определяется дифференциальная нелинейность во всех точках шкгшы контролируемого ЦАП, а не в одной точке.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| Устройство контроля цифро-аналоговых преобразователей | 1980 |

|

SU949801A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР СИНУСОИДАЛЬНЫХ СИГНАЛОВ | 1991 |

|

RU2010414C1 |

| Устройство для измерения характеристик случайных погрешностей аналого-цифровых преобразователей | 1987 |

|

SU1443174A2 |

| Устройство для измерения времени установления выходного напряжения цифроаналоговых преобразователей | 1986 |

|

SU1332530A1 |

| Устройство для измерения дифференциальной нелинейности быстродействующих аналого-цифровых преобразователей | 1985 |

|

SU1282323A1 |

| Нелинейный преобразователь | 1988 |

|

SU1674172A1 |

| Устройство для управления технологическим объектом | 1985 |

|

SU1275377A1 |

ИЗМЕРИТЕЛЬ НЕЛИНЕЙНОСТИ ЦИФРОАНАЛОГОВЫХ ПРЕОБРАЗОВАТЕЛЕЙ, содержащий генератор импульсов, счетчик, выход которого соединен с входом контролируемого цифроаналогового преобразователя, выход которого подключен к первому входу компаратора, генератор линейно изменяющегося напряжения, выход которого соединен с вторым входом компаратора, выход которого подключен к входу триггера, отличающийся тем, что, с целью повышения быстродействия и точности, в него введены два коммутатора, два реверсивных счетчика, блок памяти, переключатель и элемент задержки, причем вход первого коммутато ра соединен с выходом генератора .импульсов, первый и второй выходы первого коммутатора соединены с первым и вторым входами первого реверсивного счетчика, а третий и четвертый выходы - с первым и вторым входами второго реверсивного счетчика, выход 1 реверсивных счетчиков подключены к соответствующим входам второго коммутатора, выход которого подключен к первому входу блока памяти, при этом выход триггера соединен с управляющими входами первого коммутатора и переключателя и с первым управляющим входом второго коммутатора, вто- § рой управляющий вход которого соединен с входами триггера, счетчика и через элемент задержки - с входом переключателя, первый и второй выходы которого соединены с управляющими входс1ми соответствующих реверсивных счетчиков, кроме того, выход счетчика подключен к второму входу блока памяти.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР 754330, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для измерения погрешности линейности цифро-аналогового преобразователя | 1980 |

|

SU884123A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-09-07—Публикация

1983-04-13—Подача