ю ел

ел

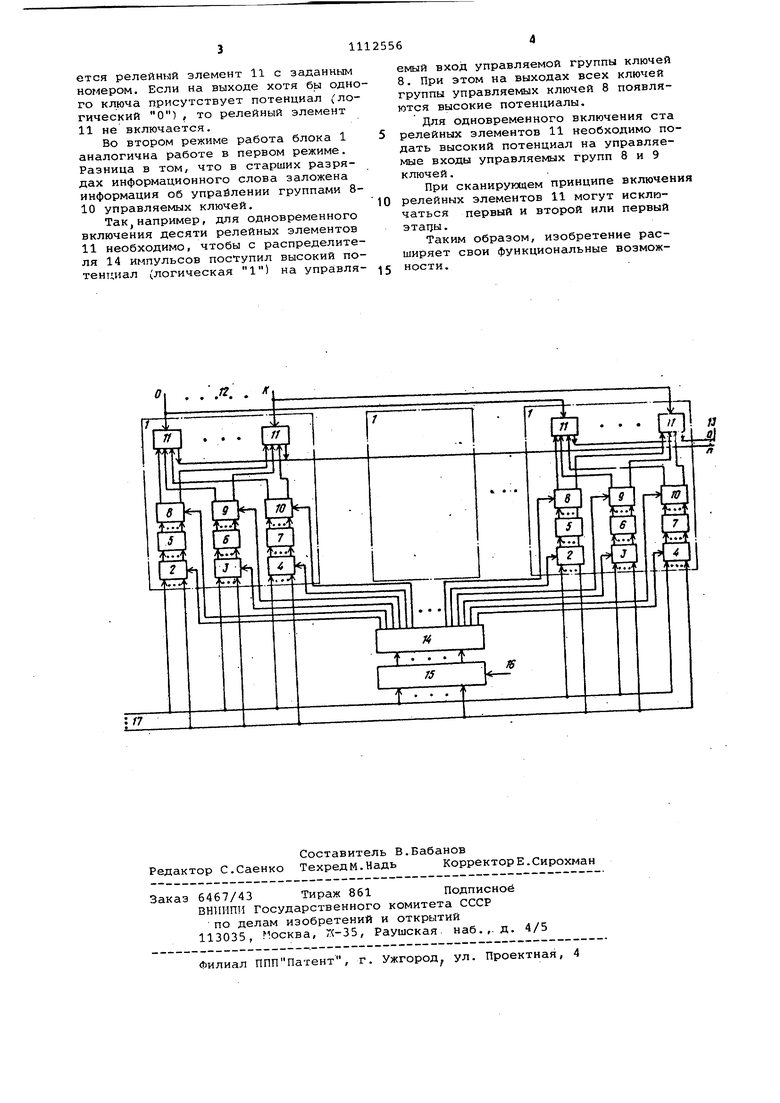

о: Изобретение относится к импульсной технике и может быть использовано при диагностике и контроле электронных схем. Известен многоканальный коммутатор, состоящий из п блоков, каждый из которых выполнен на счетчике, де шифраторах, релейных элементах, например ключах, и блоках управления L Недостаток этого устройства - пе реключение любого входа коммутатора только на один выход. Наиболее близким по технической сущности к предлагаемому является многоканальный коммутатор, содержащий п блоков, каждый из которых содержит счетчик, дешифратор, К релей ных элементов, выходы которых объединены и подключены к соответствующ выходной шине, регистр памяти и распределитель, информационные шины, W ну синхронизации, входные шины и ши записи С2. Недостаток известного устройства невозможность включить в блоке п гр пу реле одновременно. Цель изобретения - расширение фу циональных возможностей. Поставленная цель достигается те что в многоканальный коммутатор, содержащий п блоков, каждый из которых содержит дешифратор и К релей .ных элементов, выходы которых объединены и подключены к соответствующей шине, а входные шины релейных элементов всех блоков соответственн объединены, последовательно соединенные распределитель импульсов и р гистр памяти, входы которого подклю чены к информационным шинам, в каждый блок введены регистрыпамяти ед ниц, десятков, сотен и управляемые группы ключей единиц, десятков, сотен, а дешифратор выполнен в виде , дешифраторов единиц, десятков, сотен , причем выходы регистров памяти единиц, десятков, сотен подключены соответственно через дешифраторы еди ниц, десятков, сотен и управляемые группы ключей единиц, десятков, сотен к входам релейных элементов, управляемые входы регистров памяти единиц, десятков, сотен и управляемых групп ключей подключены к распределителю импульсов, а информационные входы регистров памяти еди ниц, десятков, сотен всех блоков сое динены параллельно и подключены к входньм информационным шинам. На чертеже представлена функциональная схема предлагаемого коммутаМногоканальный коммутатор состоит из п блоков 1, каждый из которых содержит регистры 2-4 памяти соответственно единиц,десятков,сотен,дешифраторы 5-7 соответственно единиц,десятков,сотен,управляемую группу 8-10 ключей соответственно единиц,десятков сотен, К релейных элементов 11, входных К шин 12 коммутатора, выходных п (ЛИН 13, распределителя 14 импульсов, регистра 15 памяти, шины 16 записи, информационной шины 17. Выходы регистров 2-4 памяти подключены соответственно через дешифраторы 5-7 и через управляемые группы 8-10 ключей к входам релейных элементов 11, управляемые входы регистров 2-4 памяти и управляемых групп 8-10 ключей подключены к распределителю 14 импульсов, входы которого подключены к регистру 15 памяти, входы регистров 2-4 памяти всех п блоков 1 и входы регистра 15 памяти подключены к информационным шинам 17, входы релейных элементов 11, всех блоков 1 соответственно объединены во входные шины 12, а выходы релейных элементов 11 объединены и подключены к соответствующей выходной шине 13. Устройство работает следующим образом. Каждый блок 1 имеет два режима работы. В первом режиме включен один релейный элемент 11. Во втором режиме включены группы релейных элементов кратных числу 10 или 100. В первой режиме работы управление блоком 1 производится в три этапа. На первом этапе по информационным 1-чинам 17 подается информационное слово, в младших четырех разрядах которого записано число сотен в двоично-десятичной форме, а в старших разрядах информационного слова записывается число, определяющее прохождение управляквдего импульса в регистр памяти сотен 4. При приходе импульса записи с шины 16 в регистр 15 памяти записываются старшие разряды информационного слова. Регистр 15 памяти через распределитель 14 импульсов подает импульс на управляющий вход регистра памяти сотен 4. По этому импульсу регистр памяти сотен 4 запоминает младшие разряды информационного слова. Дешифратор сотен 7 через ключ группы управляемых ключей 10 подает высокий потенциал на шину соответствующей сотни (логическая 1). На втором этапе записываются десятки. Это происходит аналогично записи сотен, при этом по информационным шинам в младших и старших разрядах меняется информация, а импульс записи через распределитель 14 импульсов поступает на управляющий вход регистра 3 памяти десятков. На третьем этапе аналогично записывается число единиц. Таким образом, на соответствующих заданному числу шинах единиц, десятков, сотен присутствуют высокие потенциалы и включается релейный элемент 11 с заданным номером. Если на выходе хотя бы одного ключа присутствует потенциал (логический О), то релейный элемент 11 не включается.

Во втором режиме работа блока 1 аналогична работе в первом режиме. Разница в том, что в старших разрядах информационного слова заложена информация об управлении группами 810управляемых ключей.

Так,например, для одновременного включения десяти релейных элементов

11необходимо, чтобы с распределителя 14 импульсов поступил высокий потенциал (логическая 1) на управляемый вход управляемой группы ключей 8. При этом на выходах всех ключей группы управляемых ключей 8 появляются высокие потенциалы.

Для одновременного включения ста 5 релейных элементов 11 необходимо подать высокий потенциал на управляемые входы управляемых групп 8 и 9 ключей.

При сканирующем принципе включения 10 релейных элементов 11 могут исключаться первый и второй или первый этацы.

Таким образом, изобретение расширяет свои функциональные возмож5 ности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор | 1980 |

|

SU940301A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОВ И ПРОВАЛОВ НЕСТАЦИОНАРНОГО НАПРЯЖЕНИЯ | 2000 |

|

RU2189631C2 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИЙ МОМЕНТОВ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1998 |

|

RU2178202C2 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

МНОГОКАНАЛЬНЫЙ KOtlMVTATOP . содержащий п блоков, каждый из которых содержит дешифратор и К релейных элементов, выходы которых объединены и подключены к соответствующей выходной шине, а входные шины релейных элементов всех блоков соответственно объединены, последовательно соединенные распределитель импульсов и регистр памяти, входы которого подключены к информационным шинам, отличающийся тем, что, с целью расширения функциональных возможностей, в каждый блок введены регистры памяти единиц, десятков, сотен и управляемые группы ключей единиц, десятков, сотен, а дешифратор выполнен в виде дешифраторов единиц, десятков, сотен, причем выходы регистров памяти единиц, десятков, сотен подключены соответственно через дешифраторы единиц, десятков, сотен и через управляемые группы ключей единиц, десятков, сотен к входам релейных элементов, управляемые входы регистров памяти единиц, десятков, сотен и управляемых групп ключей подключены к рас9 пределителю импульсов, а информацион ные входы регистров памяти единиц десятков, сотен всех блоков соединены параллельно и подключены к входным информационным шинам.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Моногоканальный коммутатор | 1973 |

|

SU474938A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Многоканальный коммутатор | 1980 |

|

SU940301A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-09-07—Публикация

1983-04-12—Подача