Изобретение относится к вычислительной технике и может быть использовано в устройствах сопряжения кана лов с периферийным устройствами. Известно устройство обмена данными, содержащее регистр управляющих сигналов, регистр информации, входы выходы которых соединены с каналом и периферийными устройствами, узел контроля, соединенный с информационным регистром и регистром управляющих сигналов Cl3 . Однако это устройство осуществляет контроль передаваемой и принимаемой информации только по мод 2. Наиболее близким к предлагаемому по технической сущности и достигаемому эффекту является устройство обмена данными, содержащее шифратор, регистр текущего состояния, первьй коммутатор, триггер ошибки, дешифратор, группа выходов которого соединена с первой группой входов шифрато ра и является группой информационных выходов устройства, вторая группа входов шифратора соединена с входом первого коммутатора и является первой группой информационных входов устройства, третья группа входов шиф ратора является второй группой инфор мационных входов устройства, нечетные выходы шифратора соединены с входами триггеров регистра текущего состояния, четные выходы шифратора соединены с входами триггеров регистра текущего состояния, входы синхронизации и сброса регистра текущего состояния и триггера ошибки соединены с шестым и седьмым входами второй группы информационных входов устройства, выходы регистра текущего состояния соединены с соответствзпощими входами дешифратора, выход первого коммутатора соединен с установочным входом триггера ошибки выход триггера ошибки является выходом индикации устройства. Шифратор содержит восемь селекто.ров и четьфе элемента ИЛИ, причем выходы первого, третьего, пятого и седьмого селекторов являются соответ ствующими выходами пшфратора и соеди нены с первыми входами первого, второго, третьего и четвертого элементо ИЛИ, выходы второго, четвертого, шес того и восьмого селекторов соединены с вторыми входами первого, второго, третьего и четвертого элементов ИЛИ, выходы первого, второго, третьего и четвертого элементов ИЛИ являются вторыми, четвертыми, шестыми и восьмыми выходами шифратора. Данное устройство обеспечивает контроль передаваемой и принимаемой информации по мод 2, а также контроль входных управляющих сигналов, поступающих от периферийных устройств на недопустимое сочетание С2. Однако при нарушении последовательноети входных управляющих сигналов регистр текущего состояния может оказаться в непредсказуемом состоянии, поэтому локализация неисправности затруднена; неизвестно в какой последовательности произошел сбой, так как регистр текущего состояния не всегда показывает достоверное состояние, а предшествующее состояние не фиксируется. Цель изобретения - повышение достоверности передаваемой информации. Поставленная цель достигается тем, что, в устройство для обмена данными между каналом и периферийными устройствами, содержащее шифратор, регистр текущего состояния, первьй коммутатор, триггер ошибки, дешифратор, группа выходов которого соединена с первой группой входов шифратора и является группой информационных выходов устройства, вторая группа входов шифратора соединена с группой входов первого коммутатора и является первой группой информационных входов устройства, третья группа входов шифратора является второй группой информйционных устройства, нечетные выходы шифратора соединены с первой группой информационных входов регистра текущего состояния, четные выходы шифратора соединены с второй группой информационных входов регистра текущего состояния соответственно, входы синхронизации и сброса регистра текущего состояния и триггера ошибки соединены с соответствующими входами второй группы информационных входов устройства, выходы регистра текущего состояния соединены с соответствующими входами дешифратора, выход триггера ошибки является первым выходом индикации .устройства, введены первый и второй элементы ИЛИ, элемент И, второй коммутатор, регистр преды- . дущего состояния, выходы которого образуют второй выход индикации устройства, ныходы регистра текущего состояния соединены соответственно с информационными входами регистра предьщущего состояния, выходы шифратора через первый элемент ИЛИ подключены к первому входу элемента И, второй вход которого соединен с соответствующим входом второй группы информационных входов устройства, выход элемента И соединен с входом синхронизации регистра предьщущего состояния, вход сброса регистра предьщущего состояния соединен с соответствующим входом второй группы информационных входов устройства, группа выходов дешифратора соединена с первой группой входов второго коммутатора, вторая группа входов второго коммутатора соединена с первой группой информационных входов устройства, выходы первого и второго коммутаторов через второй элемент ИЛ соединены с установочным входом триггера ошибки., 1

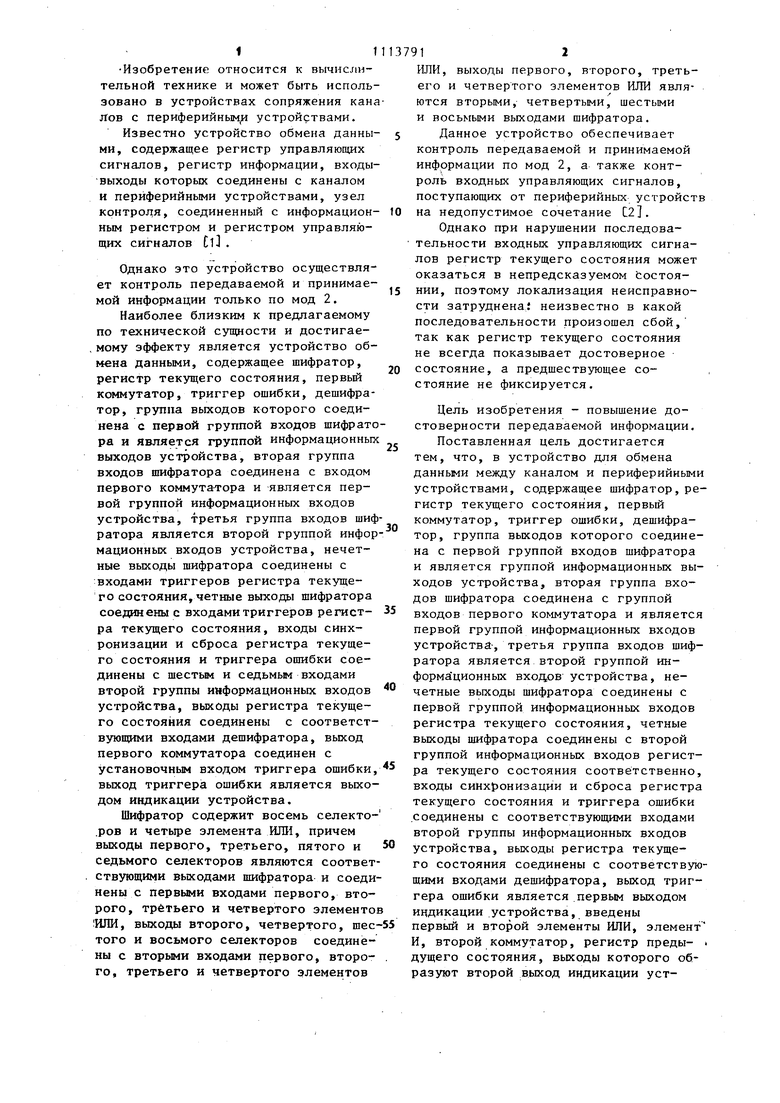

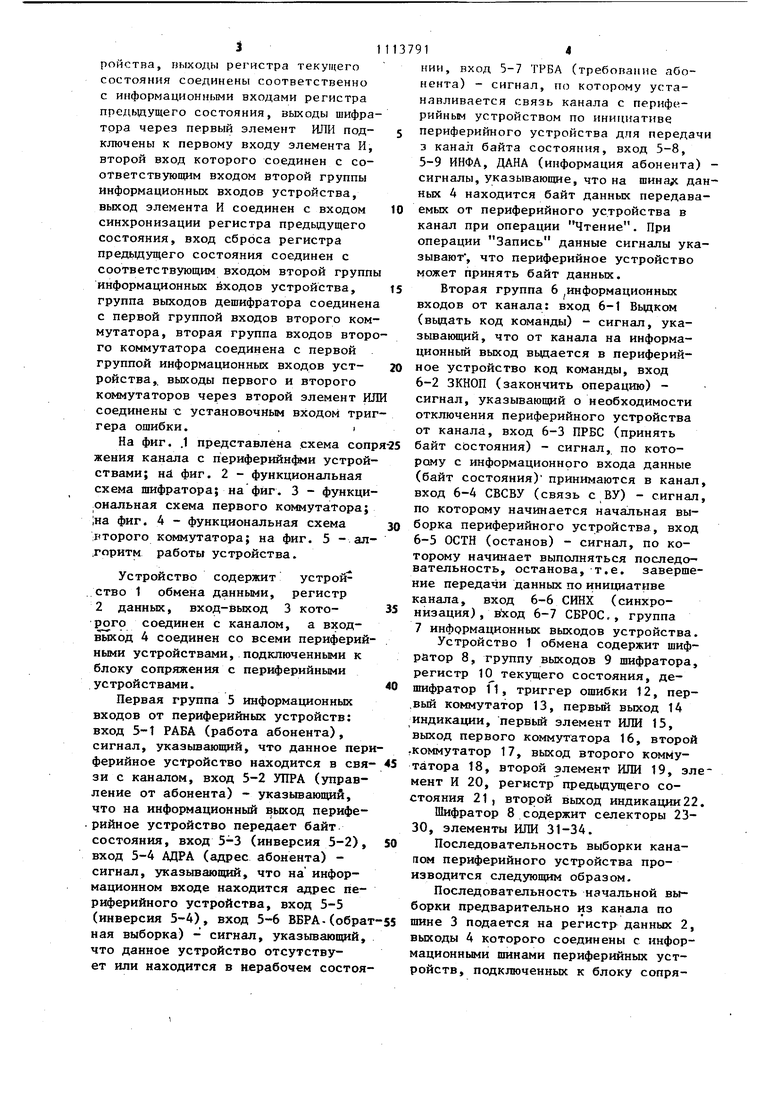

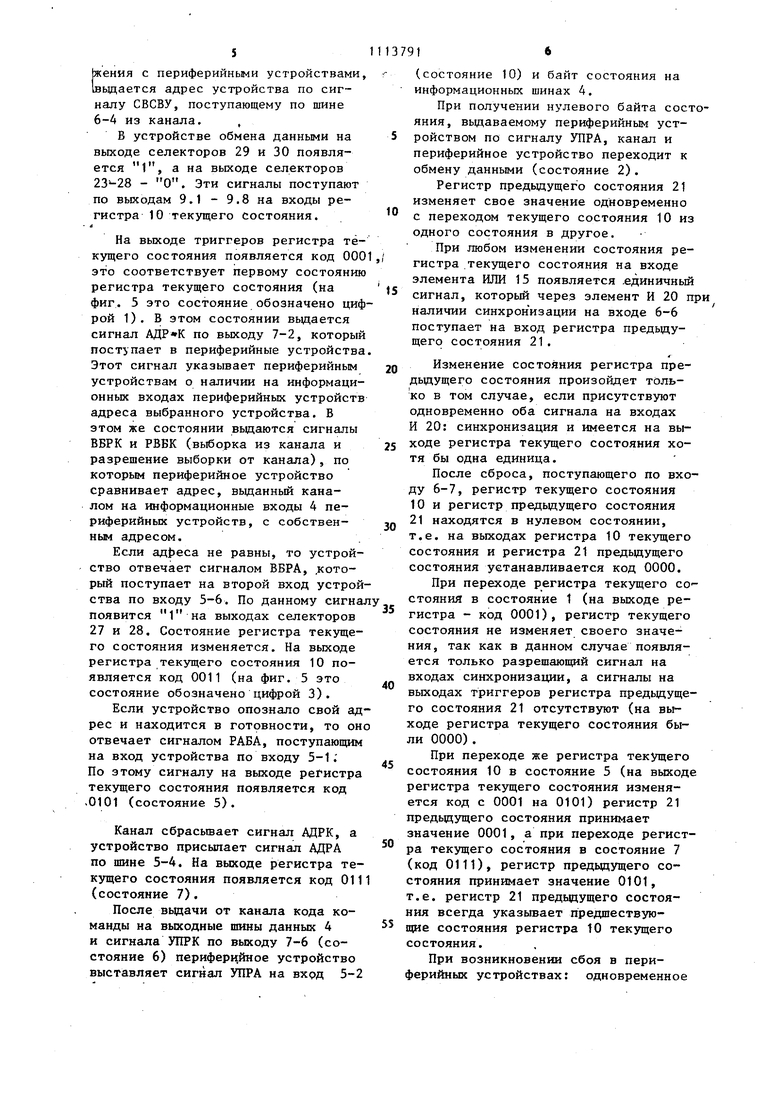

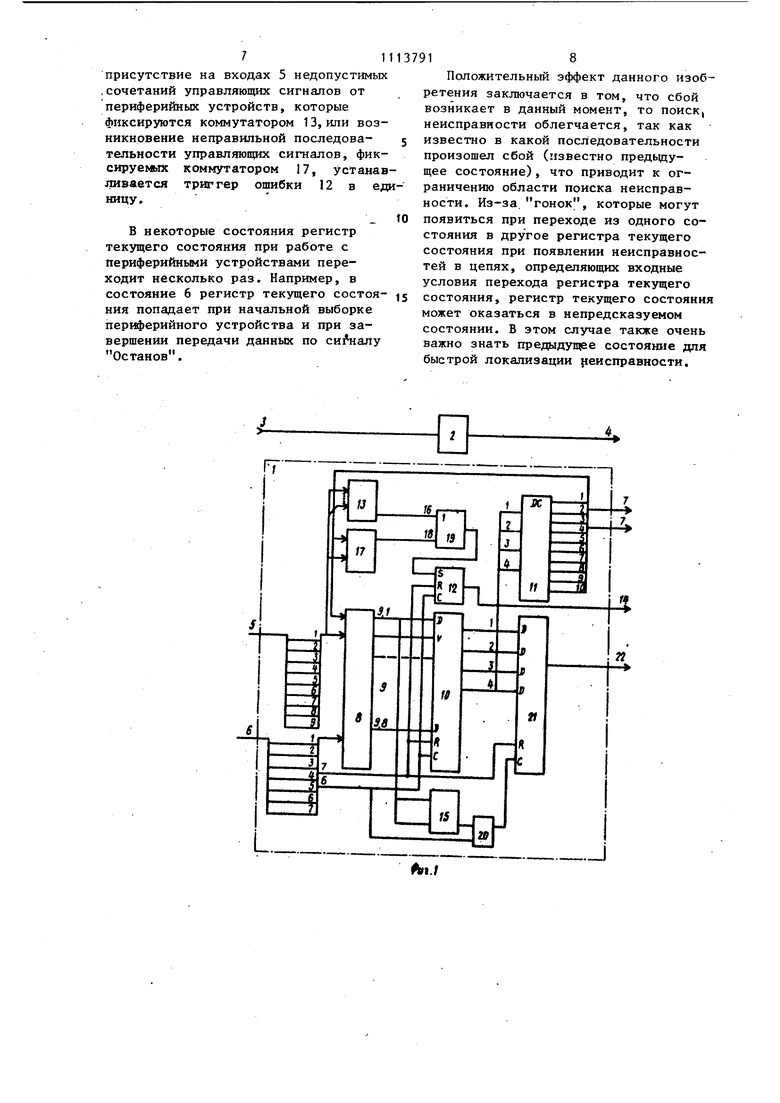

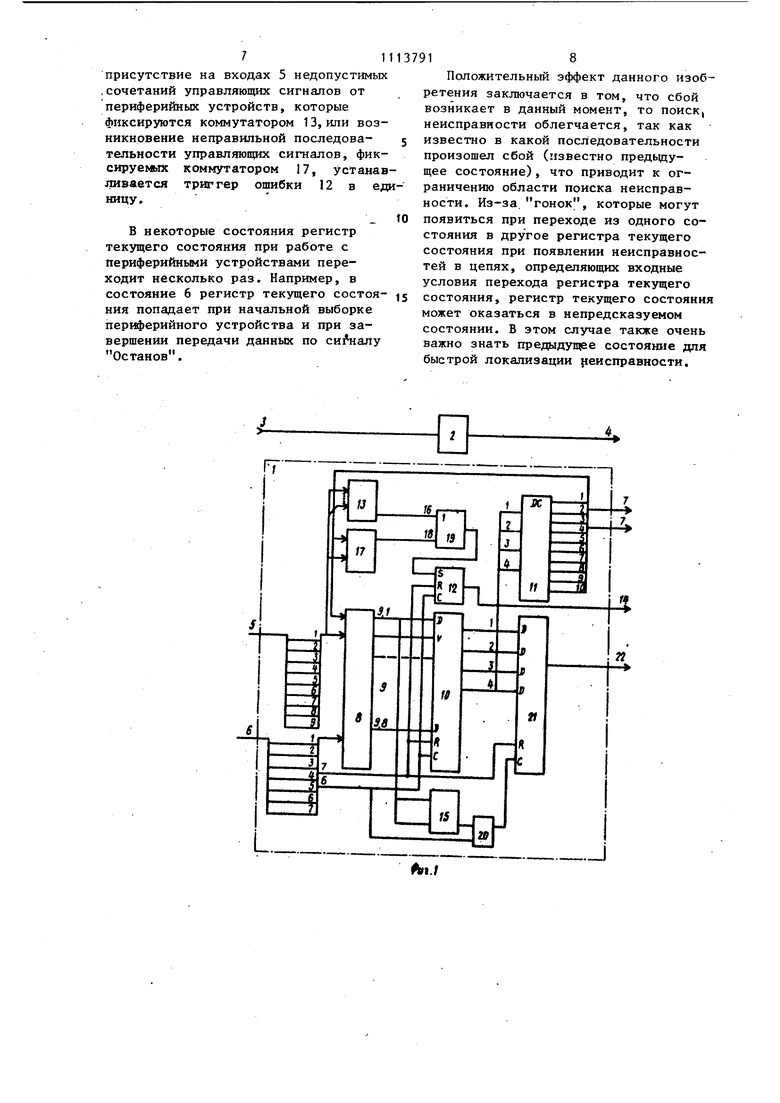

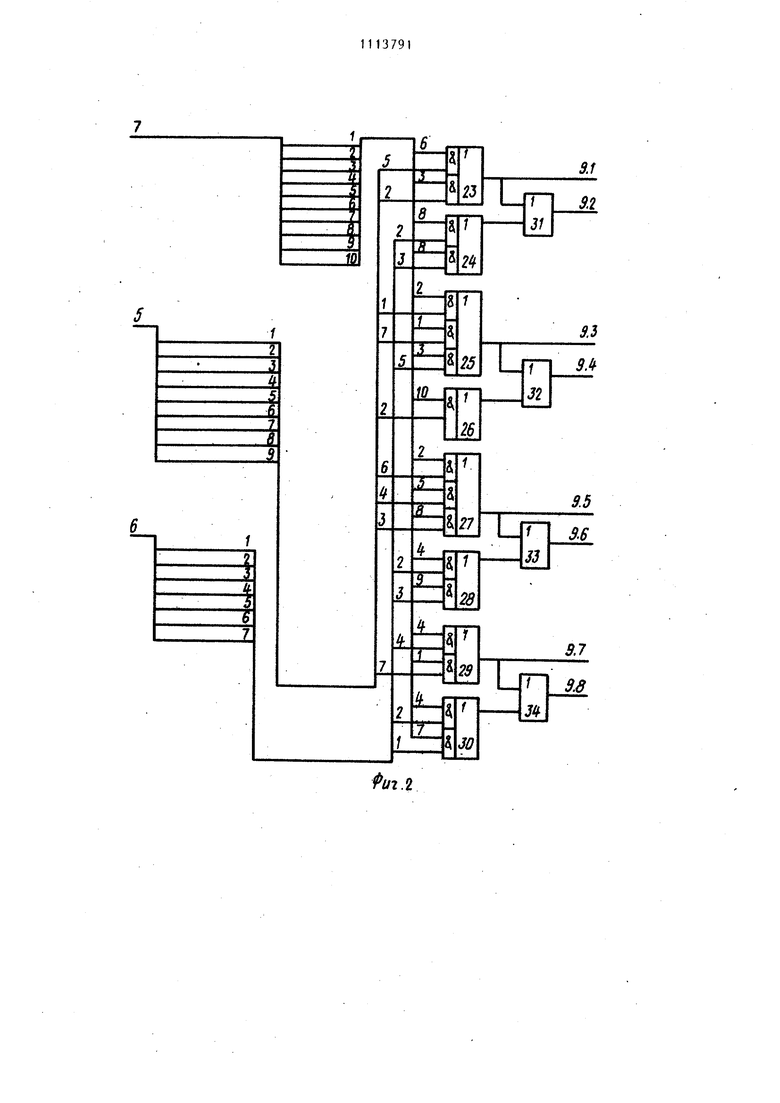

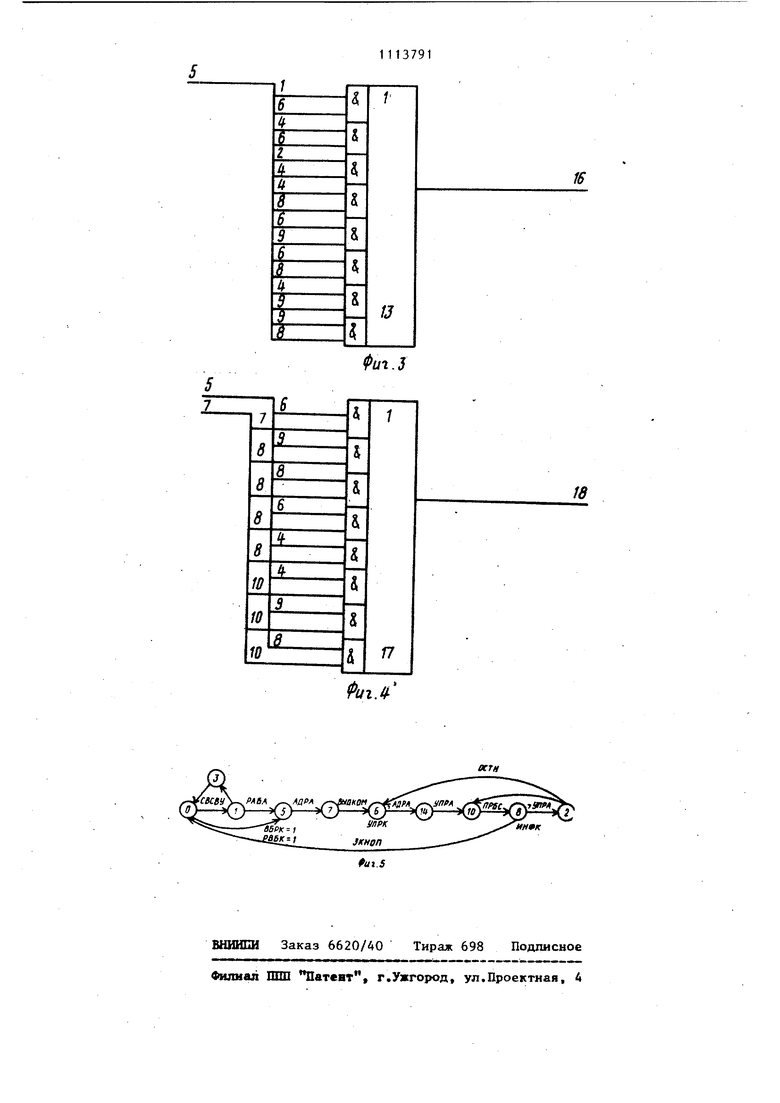

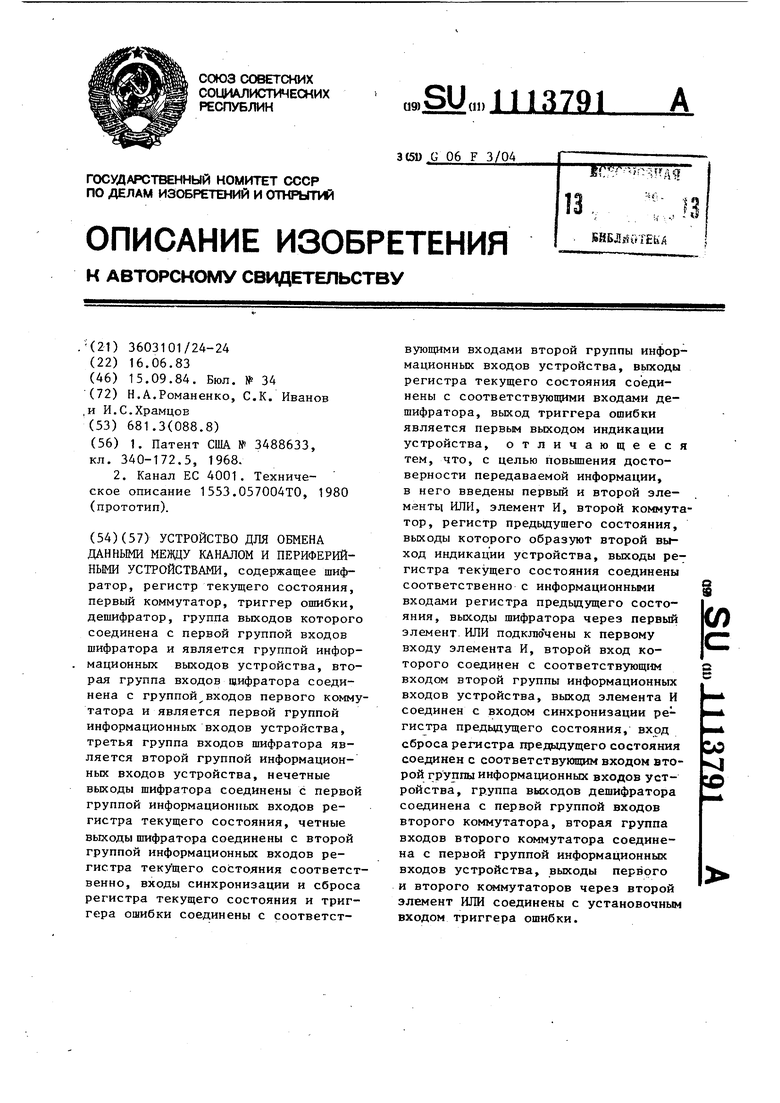

На фиг. .1 представлена схема сопр жения канала с периферийными устройствами; ни фиг. 2 - функциональная схема шифратора; на фиг. 3 - функциональная схема первого коммутатора; ;на фиг. 4 - функциональная схема второго коммутатора; на фиг. 5 - алгоритм работы устройства.

Устройство содержит устройство 1 обмена данными, регистр 2 данных, вход-выход 3 которого соединен с каналом, а входвыход 4 соединен со всеми периферийными устройствами, подключенными к блоку сопряжения с периферийными устройствами.

Первая группа 5 информационных входов от периферийных устройств: вход 5-t РАБА (работа абонента), сигнал, указывающий, что данное периферийное устройство находится в свяаи с каналом, вход 5-2 УТГРА (управление от абонента) - указывающий, что на информационный выход перифе- рийное устройство передает байт состояния, вход 5-3 (инверсия 5-2), вход 5-4 АДРА (адрес абонента) сигнал, указывающий, что на информационном входе находится адрес периферийного устройства, вход 5-5 (инверсия 5-4), вход 5-6 ВБРА-(обрат ная выборка) - сигнал, указьшающий, что данное устройство отсутствует или находится в нерабочем состояFfHH, ВХОД 5-7 ТРБА (требопапие абонента) - сигнал, по которому устанавливается связь канала с периферийньм устройством по инициативе периферийного устройства для передач 3 канал байта состояния, вход 5-8, 5-9 ИНФА, ДАНА (информация абонента) сигналы, указывающие, что на даньк 4 находится байт данных передаваемых от периферийного устройства в канал при операции Чтение. При операции Запись данные сигналы указывают, что периферийное устройство может принять байт данных.

Вторая группа 6 информационных входов от канала: вход 6-1 Бьщком (вьщать код команды) - сигнал, указьшающий, что от канала на информационный выход вьщается в периферийное устройство код команды, вход 6-2 ЗКНОП (закончить операцию) сигнал, указывающий о необходимости отключения периферийного устройства от канала, вход 6-3 ПРЕС (принять байт состояния) - сигнал, по которому с информационного входа данные (байт состояния) принимаются в канал вход 6-4 СВСВУ (связь с ВУ) - сигнал по которому начинается начальная выборка периферийного устройства, вход 6-5 ОСТИ (останов) - сигнал, по которому начинает выполняться последовательность, останова, т.е. завершение передачи данных по инициативе канала, вход 6-6 СИНХ (синхронизация) , вЬс од 6-7 СБРОС,, группа 7 информационных выходов устройства.

Устройство 1 обмена содержит шифратор 8, группу выходов 9 шифратора, регистр 10 текущего состояния, дешифратор 11, триггер ошибки 12, пер,вый коммутатор 13, первый выход 14 индикации, первый элемент ИЛИ 15, выход первого коммутатора 16, второй коммутатор 17, выход второго коммутатора 18, второй элемент ИЛИ 19, элмент И 20, регистр предьщущего состояния 21, второй выход индикации 22

Шифратор 8 содержит селекторы 2330, элементы ИЛИ 31-34.

Последовательность выборки канагаом периферийного устройства производится следующим образом.

Последовательность начальной выборки предварительно из канала по шине 3 подается на регистр данных 2, выходы 4 которого соединены с информационными шинами периферийных устройств, подключенных к блоку сопря|жения с периферийными устройствами 1выдается адрес устройства по сигналу СВСВУ, поступающему по шине 6-4 из канала. , В устройстве обмена данными на выходе селекторов 29 и 30 появляется 1, а на выходе селекторов 23-28 - О. Эти сигналы поступают по выходам 9.1 - 9.8 на входы регистра 10 текущего состояния. На выходе триггеров регистра текущего состояния появляется код 000 это соответствует первому состоянию регистра текущего состояния (на фиг. 5 это состояние обозначено циф рой 1). В этом состоянии выдается сигнал по выходу 7-2, который поступает в периферийные устройства Этот сигнал указывает периферийным устройствам о наличии на информационных входах периферийных устройств адреса выбранного устройства. В этом же состоянии вьдаются сигналы ВБРК и РВБК (выборка из канала и разрешение выборки от канала), по которым периферийное устройство сравнивает адрес, выданный каналом на информационные входы 4 периферийных устройств, с собственным адресом. Если не равны, то устройство отвечает сигналом ВБРА, который поступает на второй вход устрой ства по входу 5-6. По данному сигна появится 1 на выходах селекторов 27 и 28. Состояние регистра текущего состояния изменяется. На выходе регистра текущего состояния 10 появляется код 0011 (на фиг. 5 это состояние обозначено цифрой 3). Если устройство опознало свой ад рес и находится в готовности, то он отвечает сигналом РАБА, поступающим на вход устройства по входу 5-1. По этому сигналу на выходе регистра текущего состояния появляется код .0101 (состояние 5). Канал сбрасьшает сигнал АДРК, а устройство присылает сигнал АДРА по шине 5-4. На выходе регистра текущего состояния появляется код 01 (состояние 7). После вьщачи от канала кода команды на выходные щины данных 4 и сигнала УПРК по выходу 7-6 (состояние 6) периферийное устройство выставляет сигнал ЗШРА на вхрд 5(состояние 10) и байт состояния на информационных шинах 4. При получении нулевого байта состояния, выдаваемому периферийным устройством по сигналу УПРА, канал и периферийное устройство переходит к обмену данными (состояние 2). Регистр предьщущего состояния 21 изменяет свое значение одновременно с переходом текущего состояния 10 из одного состояния в другое. При любом изменении состояния регистра .текущего состояния на входе элемента ИЛИ 15 появляется .единичный сигнал, которьй через элемент И 20 при наличии синхронизации на входе 6-6 поступает на вход регистра предьщущего состояния 21. Изменение состояния регистра предьщущего состояния произойдет только в том случае, если присутствуют одновременно оба сигнала на входах И 20: синхронизация и имеется на выходе регистра текущего состояния хотя бы одна единица. После сброса, поступающего по входу 6-7, регистр текущего состояния 10 и регистр предьщущего состояния 21 находятся в нулевом состоянии, т.е. на выходах регистра 10 текущего состояния и регистра 21 предьщущего состояния устанавливается код 0000. При переходе регистра текущего состояния в состояние 1 (на выходе регистра - код 0001), регистр текущего состояния не изменяет своего значения, так как в данном случае появляется только разрешающий сигнал на входах синхронизации, а сигналы на выходах триггеров регистра предьщущего состояния 21 отсутствуют (на выходе регистра текущего состояния были 0000). При переходе же регистра текущего состояния 10 в состояние 5 (на выходе регистра текущего состояния изменяется код с 0001 на 0101) регистр 21 предьщущего состояния принимает значение 0001, а при переходе регистра текущего состояния в состояние 7 (код 0111), регистр предьщущего состояния принимает значение 0101, т.е. регистр 21 предьщущего состояния всегда указывает предшествующие состояния регистра 10 текущего состояния. При возникновении сбоя в периферийных устройствах: одновременное

присутствие на входах 5 недопустимых .сочетаний управляющих сигналов от периферийных устройств, которые фиксируются коммутатором 13, или возникновение неправильной последовательности управляющих сигналов, фикcиpye в nc коммутатором 17, устанавливается триггер ошибки 12 в едницу.

В некоторые состояния регистр текущего состояния при работе с периферийными устройствами переходит несколько раз. Например, в состояние 6 регистр текущего состояния попадает при начальной выборке периферийного устройства и при завершении передачи данных по сигналу Останов.

Положительный эффект данного изобретения заключается в том, что сбой возникает в данный момент, то поиск, неисправности облегчается, так как известно в какой последовательности произошел сбой (известно предьщущее состояние), что приводит к ограничению области поиска неисправности. Из-за, гонок, которые могут

появиться при переходе из одного состояния в другое регистра текущего состояния при появлении неисправностей в цепях, определяющих входные условия перехода регистра текущего состояния, регистр текущего состояния может оказаться в непредсказуемом состоянии. В этом случае также очень важно знать предыдущее состояние для быстрой локализации |1еисправности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля каналов ввода-вывода | 1980 |

|

SU935964A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для сопряжения | 1981 |

|

SU968798A1 |

| Устройство для диагностики каналов ввода-вывода | 1977 |

|

SU669921A1 |

| Устройство для сопряжения | 1979 |

|

SU805295A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для управления вводом-выводом информации | 1979 |

|

SU780694A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

УСТРОЙСТВО ДЛЯ ОБМЕНА ДАННЫМИ МЕВДУ КАНАЛОМ И ПЕРИФЕРИЙНЫМИ УСТРОЙСТВАМИ, содержащее шифратор, регистр текущего состояния, первый коммутатор, триггер ошибки, дешифратор, группа выходов которого соединена с первой группой входов шифратора и является группой информационных выходов устройства, вторая группа входов шифратора соединена с группой входов первого коммутатора и является первой группой информационных входов устройства, третья группа входов шифратора является второй группой информационных входов устройства, нечетные выходы шифратора соединены с первой группой информационных входов регистра текущего состояния, четные выходы шифратора соединены с второй группой информационных входов регистра текущего состояния соответственно, входы синхронизации и сброса регистра текущего состояния и триггера ошибки соединены с соответствующими входами второй группы информационных входов устройства, выходы регистра текущего состояния соединены с соответствующими входами дешифратора, выход триггера ошибки является первым выходом индикации устройства, отличающееся тем, что, с целью повьшзения достоверности передаваемой информации, в него введены первый и второй элементы ИЛИ, элемент И, второй коммутатор, регистр предыдущего состояния, выходы которого образуют второй выход индикации устройства, выходы регистра текущего состояния соединены соответственно с информационными входами регистра предьщущего состоО) яния, выходы шифратора через первый элемент ИЛИ подключены к первому С входу элемента И, второй вход которого соединен с соответствующим входом второй группы информационных входов устройства, выход элемента И соединен с входом синхронизации регистра предьщущего состояния, вход DO сброса регистра предыдущего состояния соединен с соответствующим входом второй группы информационных входов уст:о ройства, группа выходов дешифратора соединена с первой группой входов второго коммутатора, вторая группа входов второго коммутатора соединена с первой группой информационных входов устройства, выходы первого и второго коммутаторов через второй элемент ИЛИ соединены с установочным входом триггера ошибки.

Риг.г

ФигЛ

ЯТН

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3488633, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ПРИСПОСОБЛЕНИЕ ДЛЯ ПРЕДОХРАНЕНИЯ РАБОЧИХ ОТ ОЖОГОВ ПРИ ПЕЧАХ | 1925 |

|

SU4001A1 |

| Подвижной аппарат для подъема жидкостей и густых масс помощью образования вакуума сжиганием горючей смеси | 1924 |

|

SU1553A1 |

Авторы

Даты

1984-09-15—Публикация

1983-06-16—Подача