Изобретение относится к области вычислительной техники и может быть использовано для диагностики каналов ввода-вывода, выполненных в виде самостоятельного устройства, а также для диагностики других устройств.

Известно устройство для диагностики каналов ввода-вывода, содерЖ|ащее процессор, блок памяти и , где в его местную память заносятся большая диагностическая программа и информация для проведения диагностики 1.

Недостатком является значительное увеличение количества оборудования местной памяти за счет записи в нее диагностических программ и информации.

Наиболее близким техническим решением к изобретению является устройство для диагностики каналов ввода-вывода, содерж-ащее процессор и :блок оперативной памяти, причем первые выходы и входы всех каналов соединены соответственно с первым выходом и входом процессора, второй выход и вход процессора соедннены со вторым входом и выходом каждого контролируемого канала и с первым выходом и входом блока памяти 2.

Недостатком устройства является введение специальных каналов для обнаружения неисправностей.

Целью изобретения является сокращение количества оборудования устройства. Поставленная цель достИ(Лается тем, что в устройство введены блок управления 5 диагностикой, блок задания режимов, входной регистр управляющей информации, блок переключения, информационный регистр, регистр тактов, блок сравнения, счетчик тактов, первый, входной и треп;и

элементы И, блок управления индикацией, коммутатор и индикационное табло. Третий выход процессора соединен с первым входом блока управления диагностикой первый, второй, третий, четвертый, пятыг,

5 шестой и седьмой выходы которого соединены соответственно с первым входом первого элементна И, с первым входом входного регистра управляющей информации, с третьим входом всех контролируемых каналов, с первым входом второго элемента И, с первым входом третьего элемента И, с входом счетчика тактов и первым входом коммутатора. Выход коммутатора соединен с первым входом блока управления индикацией, первый и второй выходы которого соединены соответственно с вторым входом третьего элемента И и с входом нндикацнонного табло. Выход индикационного табло соединен с вторым входом

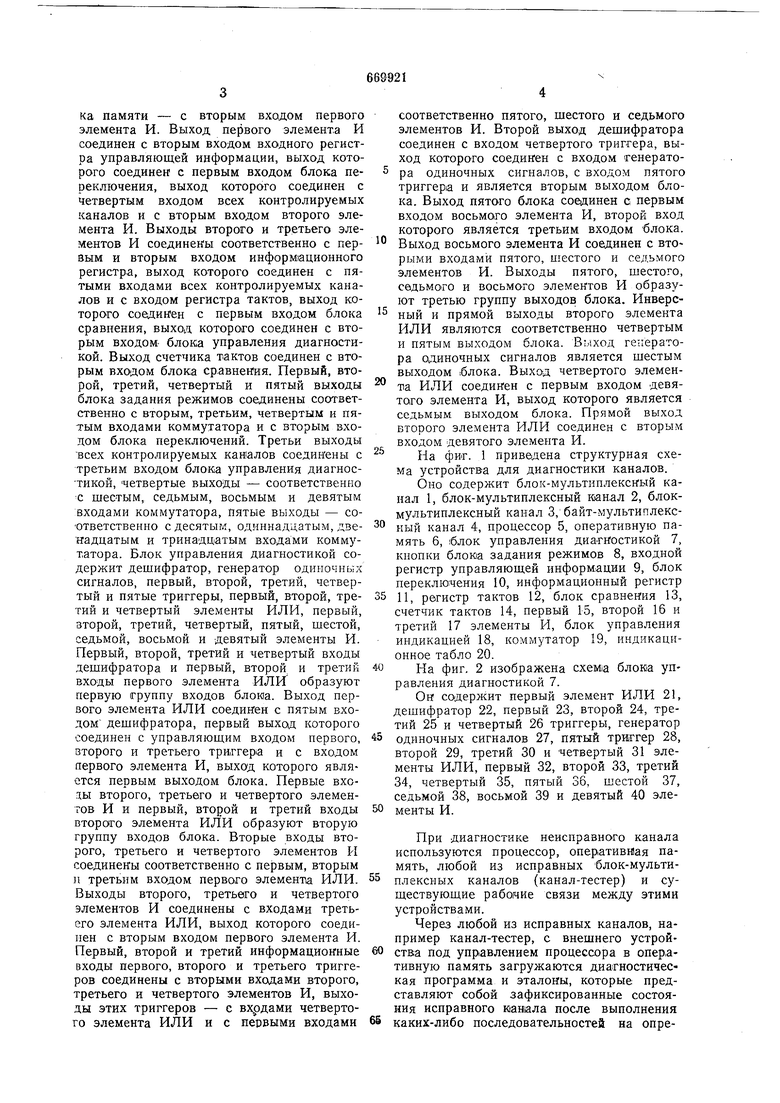

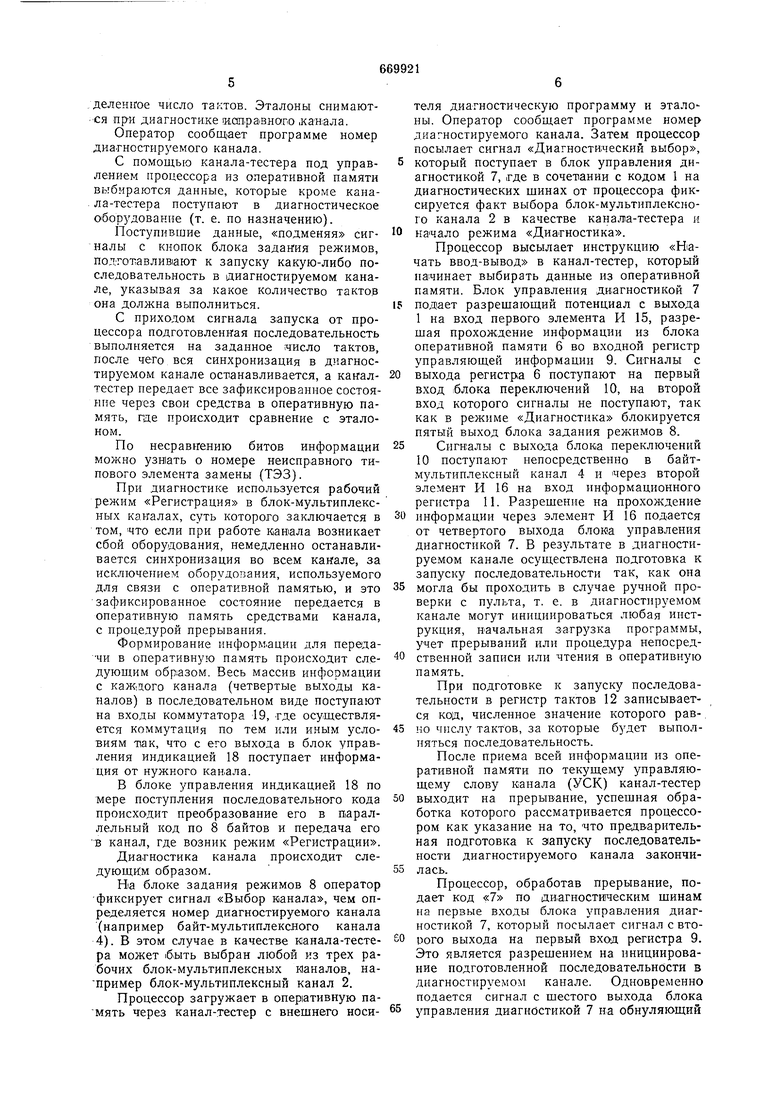

0 блока управления индикацией, выход блока памяти - с вторым входом первого элемента И. Выход первого элемента И соединен с вторым входом входного регистра управляющей информации, выход которого соединен с первым входом блока переключения, выход которого соединен с четвертым входом всех контролируемых каналов и с вторым входом второго элемента И. Выходы второго и третьего элементов И соединекы соответственно с перзым и вторым входом информ(ационного регистра, выход которого соединен с пятыми входами всех контролируемых каналов и с входом регистра тактов, выход которого соединен с первым входом блока сравнения, выход которого соединен с вторым входом- блока управления диагностикой. Выход счетчика тактов соединен с вторым входом блока сравнения. Первый, второй, третий, четвертый и пятый выходы блока задания режимов соединены соответственно с вторым, третьим, четвертым и пятым входами коммутатора и с вторым входом блока переключений. Третьи выходы всех контролируемых каналов соединены с третьим входом блока управления диагностикой, четвертые выходы - соответственно с шестым, седьмым, восьмым и девятым входами коммутатора, пятые выходы - соответственно с десятым, одиннадцатым, двенадцатым и тринадцатым входами коммутатора. Блок управления диагностикой содержит дешифратор, генератор одиночных сигналов, первый, второй, третий, четвертый и пятые триггеры, первый, второй, третий и четвертый элементы ИЛИ, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И. Первый, второй, третий и четвертый входы дешифратора и первый, второй и третий входы первого элемента ИЛИ образуют первую группу входов блок1а. Выход первого элемента ИЛИ соединен с пятым входом дешифратора, первый выход которого соединен с управляюшим входом первого, второго и третьего триггера и с входом первого элемента И, выход которого является первым выходом блока. Первые входы второго, третьего и четвертого элементов И и первый, второй и третий входы второго элемента ИЛИ образуют вторую группу входов блока. Вторые входы второго, третьего и четвертого элементов И соединены соответственно с первым, вторым и третьим входом первого элемента ИЛИ. Выходы второго, третьего и четвертого элементов И соединены с входами третьего элемента ИЛИ, выход которого соединен с вторым входом первого элемента И. Первый, второй и третий информационные входы первого, второго и третьего триггеров соединены с вторыми входами второго, третьего и четвертого элементов И, выходы этих триггеров - с входами четвертого элемента ИЛИ н с первыми входами соответственно пятого, шестого и седьмого элементов И. Второй выход дешифратора соединен с входом четвертого триггера, выход которого соединен с входом генератора одиночных сигналов, с входом пятого триггера и является вторым выходом блоica. Выход пятого блока соединен с первым входом восьмого элемента И, второй вход которого является третьим входом блока. Выход восьмого элемента И соединен с вторыми входами пятого, шестого и седьмого элементов И. Выходы пятого, шестого, седьмого и восьмого элементов И образуют третью группу выходов блока. Инверсный и прямой выходы второго элемента ИЛИ являются соответственно четвертым и пятым выходом блока. Вь.ход генератора одиночных сигналов является шестым выходом 1блока. Выход четвертого элемента ИЛИ соединен с первым входом девятого элемента И, выход которого является седьмым выходом блока. Прямой выход второго элемента ИЛИ соединен с вторым входом девятого элемента И. На фиг. 1 приведена структурная схема устройства для диагностики каналов. Оно содержит блок-мультиплексный канал 1, блок-мультиплексный канлл 2, блокмультиплексный канал 3,байт-мультиплексный канал 4, процессор 5, оперативную память 6, блок управления диагностикой 7, кнопки блок/а задания режимов 8, входной регистр управляющей информации 9, блок переключения Ю, информационный регистр 11, регистр тактов 12, блок сравнения 13, счетчик тактов 14, первый 15, второй 16 и третий 17 элементы И, блок управления индикацией 18, коммутатор 19, индикационное табло 20. На фиг. 2 изображена схемка блока управления диагностикой 7. Он содержит первый элемент ИЛИ 21, дешифратор 22, первый 23, второй 24, третий 25 и четвертый 26 триггеры, генератор одиночных сигналов 27, пятый три1ггер 28, второй 29, третий 30 и четвертый 31 элементы ИЛИ, первый 32, второй 33, третий 34, четвертый 35, пятый 36, шестой 37, седьмой 38, восьмой 39 и девятый 40 элементы И. При диагностике неисправного канала используются процессор, оперативная память, любой из исправных блок-мультиплексных каналов (канал-тестер) и существующие рабоние связи между этими устройствами. Через любой из исправных каналов, например канал-тестер, с внешнего устройства под управлением процессора в оперативную память загружаются диагностическая программа и эталоны, которые представляют собой зафиксированные состояния исправного канала после выполнения каких-либо последовательностей на опре, деленное число тактов. Эталоны снимают-ся при диагностике и.ап.ра.в,наг.о .канала.

Оператор сообщает программе номер диагностируемого канала.

С помощью канала-тестера под управлением процессора из оперативной памяти выбираются данные, которые кроме канала-тестера поступают в диагностическое оборудование (т. е. по назначению).

Поступившие данные, «подменяя сигналы с кнопок блока задан-ия режимов, подготавливают к запуску какую-либо последовательность в диагностируемом канале, указывая за какое количество тактов она должна выполниться.

С приходом сигнала запуска от процессора подготовленная последовательность выполняется на заданное число тактов, после чего вся синхронизация в диагностируемом канале останавливается, а какалтестер передает все зафиксированное состояние через свои средства в оперативную память, где происходит сравнение с эталоном.

По несравнению битов информации можно узнать о номере неиспр авного типового элемента замены (ТЭЗ).

При диагностике используется рабочий режим «Регистрация в блок-мультиплексных каналах, суть которого заключается в том, что если при работе канала возникает сбой оборудования, немедленно останавливается синхронизация во всем канале, за исключением оборудотзания, используемого для связи с оперативной памятью, и это зафиксированное состояние передается в оперативную память средствами канала, с процедурой прерывания.

Формирование информ.ации для передачи в оперативную память происходит следующим обр1азом. Весь массив информации с каждого канала (четвертые выходы каналов) в последовательном виде поступают на входы коммутатора 19, где осуществляется коммутация по тем или иным условиям Т1ак, что с его выхода в блок управления индикацией 18 поступает информация от нужного канала.

В блоке управления индикацией 18 по мере поступления последовательного кода происходит преобразование его в параллельный код по 8 байтов и передача его В канал, где возник режим «Регистрации.

Диагностика канала происходит следующН.м образом.

На блоке задания режимов 8 оператор фиксирует сигнал «Выбор канала, чем определяется номер диагностируемого канала (например байт-мультиплексного канала 4). В этом случае в качестве канала-тестера может быть выбран любой из трех рабочих блок-мультиплексных К1аналов, например блок-мультиплексный канал 2.

Процессор загружает в опер|ативную память через канал-тестер с внещнего носителя диагностическую программу и этало ны. Оператор сообщает программе номер диагностируемого канала. Затем процессор посылает сигнал «Диагностический выбор, который поступает в блок управления диагностикой 7, где в сочетании с кодом 1 на диагностических шинах от процессора фиксируется факт выбора блок-мультиплексного канала 2 в качестве канала-тестера и

начало режима «Диагностика.

Процессор высылает инструкцию «Начать ввод-вывод в канал-тестер, который начинает выбирать данные из оперативной памяти. Блок управления диагностикой 7

подает разрешающий потенциал с выхода 1 на вход первого элемента И 15, разрешая прохождение информации из блока оперативной памяти 6 во входной регистр управляющей информации 9. Сигналы с

выхода регистра 6 поступают на первый вход блока переключений 10, на второй вход которого сигналы не поступают, так как в режиме «Диагностика блокируется пятый выход блока задания режимов 8.

Сигналы с выхода блока переключений 10 поступают непосредственно в байтмультиплексный канал 4 и через второй элемент И 16 на вход информационного регистра 11. Разрешение на прохождение

информации через элемент И 16 подается от четвертого выхода управления диагностикой 7. В результате в диагностируемом канале осуществлена подготовка к запуску последовательности так, как она

могла бы проходить в случае ручной проверки с пульта, т. е. в диагностируемом канале могут инициироваться любая инструкция, начальная загрузка программы, учет прерываний или процедура непосредственной записи или чтения в оперативную память.

При подготовке к запуску последовательности в регистр тактов 12 записывается код, численное значение которого равно числу тактов, за которые будет выполняться последовательность.

После приема всей информации из оперативной памяти по текущему управляющему слову канала (УСК) канал-тестер

выходит на прерывание, успешная обработка которого рассматривается процессором как указание на то, что предварительная подготовка к запуску последовательности диагностируемого канала закончилась.

Процессор, обработав прерывание, подает код «7 по диагностическим шинам на первые входы блока управления диагностикой 7, который посылает сигнал с второго выхода на первый вход регистра 9. Это является разрешением на инициирование подготовленной последовательности в диагностируемом канале. Одновременно подается сигнал с шестого выхода блока

управления диагностикой 7 на обнуляющий

вход счетчика тактов 14, который начинает отсчет тактов инициированной носледовательности в диагностируемом канале.

Когда коды в регистре тактов 12 и счетчике тактов 14 ср.авняются, срабатывает блок сравнения 13 и сигнал с его выхода ностун.ает на третий вход блока управления диагностикой 7, который посылает сигнал останова синхронизации в диагностируемый канал. В канал-тестер посылается сигнал, который принудительно переводит его в режим «Регистрация, после чего он выставляет в процессор запрос на прерывание. Работа канала в режиме «Регистрация уже была описана. Отличие от работы в диагностическом режиме заключается в том, что с выхода коммутатора 19 на вход блока, управления индикацией 18 поступает информационный массив не от канала-тестера, как в режиме «Регистрация, а от диагностируемого байт-мультиплексного канала 4.

Блок управления индикацией 18 после того, как канал-тестер получит сигнал удовлетворения запроса на прерывание по режиму «Регистрация по мере поступления последовательного кода преобразует его в парраллельный код по 8 байтов и через третий элемент И .17 посылает их в информационный регистр 11 пульта. Разрешение на третий элемент И 17 поступает с выхода 5 блока управления диагностикой 7. Информация с регистра 11, представляющая собой зафиксированное состояние ди агностируемО:Го канала, поступает в каналтестер, а с него в оперативную память, где происходит сравн ение с эталоном.

Если диагностируемый канал работает без имитатора оперативной памяти, происходит проверка реальных связей с oneратиБной памятью, а при работе без имитатора периферийного устройства возможна проверка реальных связей с перифериййым устройством.

Блок -управления диагностикой 7 работает следующим образом. На первые входы блока (входы дешифратора 22) поступают сигналы от процессора по четырем диагностическим шинам, а на вход первого элемента ИЛИ 21 - сигналы «Диагностический выбор. На выходе дешифратора 22 будет сигнал в том случае, если подан хотя бы один из сигналов «Диагностический выбор. В этом случае с выхода схемы ИЛИ 21 подается разрешение на дешифратор 22.

Триггеры 23, 24, 25 служат для фиксации номера канала-тестера, так что с приходом сигнала с выхода узла сравнения 13 принудительно будет переведен в режим «Регистрация только канал-тестер.

При коде «7 от процессора четырех диагностических шинах с выхода дешифратора 22 поступает сигнал на триггер 26, выходной потенциал с которого имитирует

начало операции в диагностируемом , поступая на первый вход регистра 9.

Одновременно сигнал с выхода триггера 26 запускает генератор одиночных им-пульсов 27, который обнуляет счетчик тактов 14. Сигнал с выхода триггера 26 через задерживающий триггер 28 поступает также на элемент И 39, разрешая прохождение сигнала от блока сравнентия .13.

Сигналы «Днагностический выбор поступают на элементы И 33, 34 и 35, где «подсвечиваясь сигналами «Обмен данных от канала-тестера и при наличии кода «1 на четырех диагностических шинах, поступают через первый выход на вход элемента И 15.

Когда канал-тестер перейдет в режим «Регистрация, через второй вход на один из контактов (четвертый, пятый, шестой) поступает сигнал, который сн:имает разрешающий потенциал со второго элемента И 16 и подает разрешающий потенциал на, третий элемент И 17. И если при этом есть сигнал с элемента ИЛИ 31, то подается разрешающий потенциал с элемента И 40 на вход коммутатора 19, по которому с его выхода будет поступать информация о зафиксированном состоянии диагностируемого канала.

Использование рабочих каналов, а не специальных при диагностике неисправногоканала позволяет уменьшить количество оборудования, так как введенное диагностическое оборудование невелико по объему, является общим для четырех каналов и практически полностью используется при ручной настройке и диагностике каналов..

Формула изобретения

1. Устройство для диагностики каналов ввода-вывода, содержащее процессор и блок оперативной памяти, причем первые выходы и входы всех каналов соединенысоответственно с первым входом и выходом процессора, второй выход и вход процессора соединен с вторым входом и выходом каждого контролируемого канала и с первым входом и выходом блока памяти, отличающееся тем, что, с целью сокращения количества оборудования, в устройство введены блок управления диагностикой, блок задания режимов, входной регистр управляющей информации, блок переключения, информационный регистр, регистр тактов, блок сравнения, счетчик тактов, первый, второй и третий элементы И, блок управления индикацией, коммутатор и индикационное табло, причем третий выход процессора соединен с первым входом блока управления диагностикой, первый, второй, третий, четвертый, пятый, шестой и седьмой выходы которого соединены соответственно с первым входом первого элемента И, с первым входом входного регисг

9

-pa управляющей информации, с третьим -аходом всех контролируемых каналов, с первым входом второго элемента И, с пер-вым входом третьего элемента И, со входом счетчика тактов и первым входом коммутатора, выход коммутатора соединен с первым входом блока управления индика.цией, первый и второй выход которого соединены соответственно с вторым входом третьего элемента И и с входом индикациопного табло, выход икдикациопного табло соединен с вторым входом блока управления индикацией, выход блока памяти соединен с вторым входом первого элемента И, выход первого элемента И соединен с вторым входом входного регистра управляющей информации, выход которого соединен с первым входом блока переключения, выход блока переключения соединен с четвертым входом всех контролируемых каналов и с вторым входом второго элемента И, выходы второго и третьего элементов И соединены соответственно с первым и вторым входами информ.ационного регистра, выход которого соединен с пятыми входами всех контролируемых каналов и с входом регистра тактов, выход которого соединен с первым входом блока сравнения, выход которого соединен с вторым входом блока управления диагностикой, выход счетчика тактов соединен с вторым входом блока сравнения, первый, второй, третий, четвертый и пятый выходы блока задания режимов соединены соответственно с вторым, третьим, четвертым и пятым входами коммутатора и с вторым входом блока переключений, третьи выходы всех контролируемых каналов соединены с третьим входом блока управления диагностикой, четвертые выходы всех контролируемых каналов соединены соответственно с шестым, седьмым, восьмым и девятым входами коммутатора, пятые выходы всех контролируемых каналов соединены соответственно с десятым, одиннадцатым, двенад. цатым и тринадцатым входами коммутатора.

2. Устройство, по п. 1, отличающеес я тем, что блок управления диагностикой содержит дешифратор, -генератор одиночных сигналов, первый, второй, третий, четвертый и пятый триггеры, первый, второй, третий и четвертый элементы ИЛИ, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, причем первый, второй, третий и четвертый входы дешифратор,а и первый, второй

10

и третий входы первого элемента ИЛИ образуют первую группу входов блока, выход первого элемента ИЛИ соединен с пятым входом дешифратора, первый выход 6 которого соединен с управляюш;им входом первого, второго и третьего триггеров и а входом первого элемента И, выход которого является первым выходом блока, первые входы второго, третьего и четвертого ментов И и первый, второй и третий входы второго элемента ИЛИ образуют вторую группу входов блока, вторые входы второго, третьего и четвертого элементов И соединены соответственно с первым, вторым и

15 третьим входом первого элемента ИЛИ, выходы второго, третьего и четвертого элементов И соединены с входами третьего элемента ИЛИ, выход которого соединей с вторым входом первого элемента И, первый, второй и третий информационные входы первого, второго и третьего триггеров соединены с вторыми входами второго, третьего и четвертого элементов И, выходы первого, второго и третьего триггеров соединены с входами четвертого элемента ИЛИ и с первыми входами соответственно пятого, шестого и седьмого элементов И, второй выход дешифратора соединен с входом четвертого триггера, выход которого соединен с входом генератора одиночных сигналов с входом пятого триггера и является вторым выходом блока, выход пятого блока соединен с первым входом восьмого элемента И, второй вход которого является третьим входом блока, выход восьмого элемента И соединен с вторыми входами пятого, Щестого и седьмого элементов И, выходы пятого, шестого, седьмого и восьмого элементов И образуют третью

° группу выходов блока, инверсный и прямой выходы второго элемента ИЛИ являются соответственно четвертым и пятым выходом блока, выход генератора одиночных сигналов является шестым выходом

5 блока, выход четвертого элемента ИЛИ соединен с первым входом девятого элемента И, выход которого является седьмым выходом блока, прямой выход второго элемента ИЛИ соединен с вторым входом

девятого элемента И.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР 5 № 516033, кл. G 06 F 11/00, 1975.

2.Патент Англии jNb 1434186, кл. G Q6 F 11/00, 26.04.72 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления диагностикой каналов | 1973 |

|

SU526876A1 |

| Блок-мультиплексный канал | 1979 |

|

SU833076A2 |

| Устройство для ввода информации | 1980 |

|

SU907540A1 |

| Процессор цифровой вычислительной системы | 1971 |

|

SU475897A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для управления вводом-выводом информации | 1979 |

|

SU780694A1 |

| Устройство для сопряжения памяти с процессором | 1982 |

|

SU1136176A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1256036A1 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957278A1 |

| Устройство для сопряжения оперативной памяти с процессором и каналами ввода-вывода | 1977 |

|

SU689439A1 |

Авторы

Даты

1982-01-07—Публикация

1977-04-12—Подача