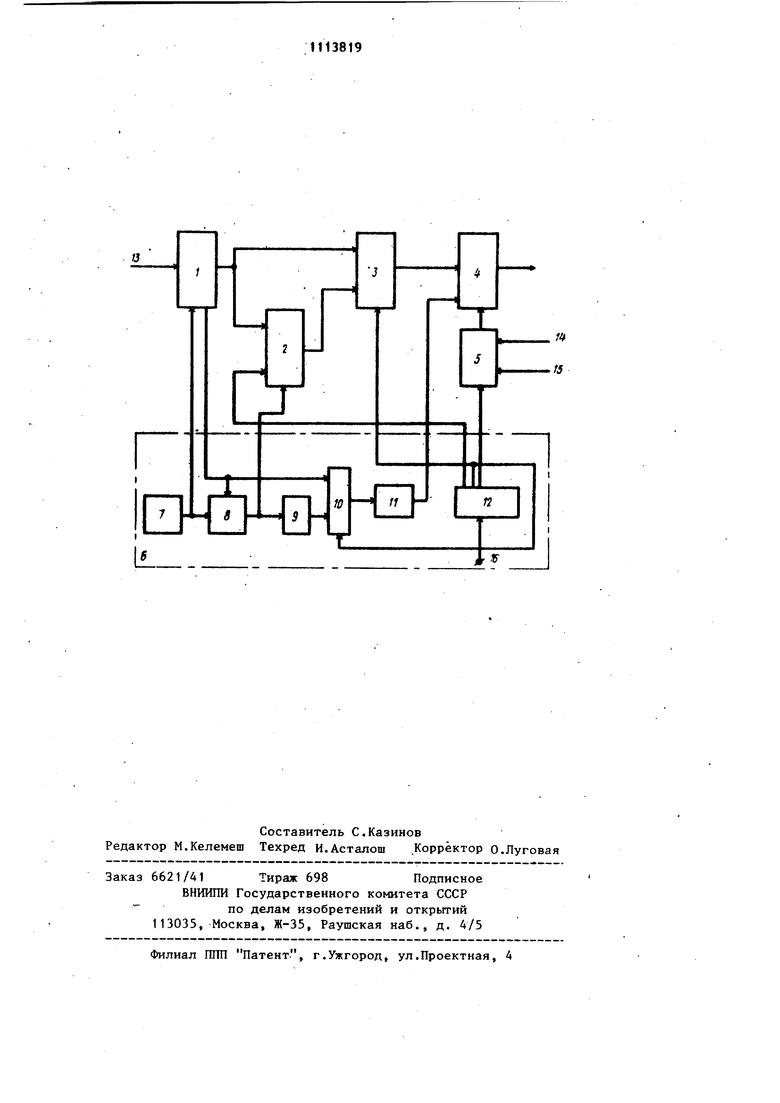

Изобретение относится к автомаТЧГ ке и вычислительной технике и может найти применение, в частности, в гиб ридных процессорах, связанных с реше нием нелинейных систем дифференциальны уравнений, для воспроизведения функциональных за1висимостей, выполнения операций умножения, деления и возведения в квадрат аналоговых сигналов. Известно гибридное вычислительное устройство, с.одержащее аналого-циф-ровой и цифроаналоговые преобразователи, сумматоры, блок адресации, блок памяти, инвертор, счетчик и блок синх эонизации 1 , Известно также гибридное вычислительное устройство, содержащее аналого-цифровой и цифроаналоговый преобразователи, блок адресации, блок памяти, coммyтaтop, блок формирования скважности импульсов и усредняющий усилитель 2. Обтп1лй недостаток известных устройств - пониженная производительность работы. Наиболее близким к изобретению является гибридное вычислительное устройство, содержащее аналого-цифровой преобразователь, подключенный информационным входом к первому входу устройства, управляющим входом - к первому выходу блока синхро низации, а цифровым выходом - к пер вому адресному входу блока памяти, соединенного вторым адресным входом с вторым выходом блока синхронизации подключенного третьим выходом купра лякяцему входу аналогового коммутатора, а четвертым выходом - к управляющему входу цифрцаналогового преобразователя, выход которого является выходом устройства, а цифровой (ВХОД соединен с цифровым выходом ан лого-цифрового преобразователя, соединенного информационным входом с выходом аналогового коммутатора. t3j Указанное устройство при подаче на его первый вход и на аналоговый (опорный) вход цифроаналогового преобразователя соответствующих аналоговых сигналов х и Xrt позволяет в общем случае осуществлять функциональное преобразование вида . f(x), что позволяет использовать его также для вьтолнения операций деления (при f(x)), умножения и возведения в квадрат (при f(x)XY и х.х аналоговых сигналов. Недостатками прототипа являются пониженная производительность работы и конструктивная сложность. Цель изобретения - повьппение производительности устройства и его упрощение за счет сокращения объема памяти. Поставленная цель достигается тем, что гибридное вычислительное устройство, содержащее аналого-цифровой преобразователь, подключенный информационным входом к первому входу устройства, управляющим входом к первому выходу блока синхронизации, а цифровьгм выходом - к первому адресному входу блока памяти, соединенного вторым адресным входом с вторым вькодом блока синхронизации, подключенного третьим выходом к управляющему входу аналогового коммутатора, а четвертым вькодом - к управляющему входу цифроаналогового преобразователя, выход которого является выходом устройства, содержит цифровой коммутатор, соединенный первым информационным входом с .цифровым выходом аналого-цифрового преобразователя, вторым информационным входом - с выходом блока памяти, управляющим входом - с пятым вьпсодом блока синхронизации, а выходом - с цифровым входом цифроаналогового преобразователя, подключенного аналоговым входом к выходу аналогового коммутатора, соединенного информационными входами с вторым входом устройства и с шиной ввода опорного напряжения, причем блок синхронизации подключен шестым выходом к входу управления считыванием блока памяти, а стробирующим входом - к выходу окончания цикла преобразования аналого-цифрового преобразователя. При этом блок синхронизации содержит регистр, коммутатор, формирователи импульсов записи и считывания, элемент задержки и генератор тактовых импульсов, подключенный выходом к первому выходу блока синхронизации и первому ВХОДУ формирователя нмпульсов считывания, соединенного BTopbw входом со стробирующим входом блока синхронизации и с первым входом коммутатора, а выходом - с шестьп выходом блока синхронизации и с входон элемента задержки, подключенного .1 выходом к второму входу коммутатора, соединенного управляющим входом с первым выходом регистра и с пятым выходом блока синхронизации, а выходом - с входом формирователя импульсов записи, выход которого соединен с четвертым выходом блока синхрониза ции, причем регистр подключен входом к шине ввода .кода режима работы, а вторым и третьим выходами - к второму и третьему выходам блока синхро низации соответственно. На чертеже изображена блок-схема гибридного вычислительного устройства. Схема содержит аналого-цифровой преобразователь 1, блок 2 (который может быть вьтолнен, например, в виде перепрограммируемЪго 1ОСТОЯИНОГО запоминающего устройства) цифровой коммутатор 3, цифроаналоговый преобразователь А, аналоговый коммутатор 5 и блок 6 синхронизации. Блок 6 может быть выполнен содержапщм генератор 7 тактовых импульсов, формирователь 8 импульсов считывания, элемент 9 задержки, коммутатор 10, формирователь 11 импульсов .записи и регистр 12. Аналого-цифровой преобразователь подключен информационным входом к первому входу 13 устройства, управ ляющим входом - к первому выходу блока 6 синхронизации, а цифровым выходом - к первому адресному входу блока 2 памяти. Блок 2 соединен вторым адресным входом с вторым выходом блока 6 синхронизации, подключенного третьим выходом к управляющему входу коммутатора 5, а четвертым выходом к управляющему входу цифроанапоговог преобразователя, выход которого является выходом устройства. Коммутатор 3 соединен первым информационньм входом с цифровым выходом аналогоцифрового преобразователя 1, вторым информационным входом - с выходом блока 2 памяти, управляющим входом с пятым выходом блока 6 синхронизации, а выходом - с цифровым входом цифроаналогового преобразователя 4. Аналоговый вход последнего подключен к выходу коммутатора 5, соединенного информационными входами с вторым вхо дом 14 устройства и с шиной 15 ввода опорного напряжения. Блок 6 синхрони зации подключен шестым выходом к вхо ду управления считыванием блока 2 194 памяти, а стробирующим входом - к выходу окончания цикла преобразования преобразователя 1. Устройство работает следующим образом. В режиме воспроизведения функций на выходе устройства вырабатывается аналоговый сигнал (х), изменяющийся в заранее заданной нелинейной зависимости от аналогового сигнала ,х (аргумент), подаваемого на вход 13. В режиме умножения, деления и возведения в квадрат устройство вьфабатывает на выходе аналоговый сигнал, равный произведению ( . Xj), делению () и возведению в квадрат (, при х ) ,, двух независимых входных аналоговых сигналов X, и Xj, подаваемых на входы 13 и 14. Использование устройства в одном из указанных режимов преобразования осуществляется посредством записи информации,поступающей на шину 16 ввода кода режима работы в регистр 12. Входной аналоговый сигнал х. поступает на вход 13 устройства и вход аналогоцифрового преобразователя 1, вырабатывающий на информационных выходах двоичный код. Запуск аналого-цифрового преобразователя 1 осуществляется генератором 7 тактовых импульсов, поступающих с первого выхода блока 6 с интервалом времени не менее времени преобразования ,, аналогоцифрового преобразователя 1. Кодовая информация на выходе аналого-цифрового преобразователя 1 сохраняется от конца предьщущего до начала следующего преобразования. По окончании цикла преобразования аналогоцифровой преобразователь 1 вьщает управляюпщй сигнал Конец преобразования, поступающий на стробирующий вход формирователя 8 импульсов считывания, который формирует импульсы определенной длительности. Кодовая информация на выходах аналого-цифрового преобразователя 1, пропорциональная входному сигналу, поступает на первый адресный вход блока 2 па-, мяти, а также на первый информацион-1 ный вход коммутатора 3. Выбор нужной группы участков памяти блока 2 осуществляется кодовой информацией со второго выхода регистра 12, котоая поступает на второй адресный ВХОД (вход Выбор интегральной схемы) блока 2 памяти. Считывание кодовой.информации из ячеек памяти, являющейся значением воспроизводимой функциональной зависимости, производится последовательно число за числом с интервалом времени выборки tj по сигналам импульсов считывания, поступающих с выхода формирователя 8 импульсов считывания на вход управления блока 2 памяти. Кодовая информация с выходов блока 2 памяти поступает на второй информаФ1ОННЫЙ вход коммутатора 3 и проходит через него на вход ш роаналогового преобразователя 4, если устройство работает в режимах воспроизведения функциональных зависимостей или деления. В последнем случае блок 2 памяти воспроизводит цию -, Х4 / В других режимах работы устройства (умножения или возведения в квадрат) коммутатор 3 пропускает кодовую информацию с выхода аналого-цифрового преобразователя 1 .и запрещает про хождение кодовой информации с выхода блока 2 памяти. Состояние коммутатора 3 (прохождение информации с выходов аналого-цифрового преобразователя или блока 2 памяти), а также коммутатора 5 (т.е. прохождение сигнала с входа 14 или с входа 15 на аналого вый вход цифроаналогового преобраз рвателя 4) определяется состоянием соответствующих ячеек регистра 12. В режиме воспроизведения функциональных зависимостей шина 15 ввода опорного напряжения подключается через коммутатор 5 к аналоговому входу цифроаналогового преобразователя 4. В режиме умножения, деления и возвед ния в квадрат к аналоговому входу 1 ФУН 19 цифроаналогового преобразователя подключается вход 14 аналоговой переменной Xj. Кодовая информация с выхода коммутатора 3 во всех режимах работы устройства поступает на цифровой вход цифроаналогового преобразователя 4, вырабатывакяций за время преобразования t,,, аналоговый выходной сигнал у под управлением импульсов записи, поступающих с периодом t на управляющий вход цифроаналогового преобразователя 4 с выхода формирователя 11 импульсов записи. Временная задержка на время осуществляется элементом .ржки. В режиме воспроизведения функциональной зависимости и деления быстродействие устройства определяется как . -bt|+tM,i ® режиме умножения и возведения в квадрат .и Ч достигается использованием коммутатора 10, при помощи которой исключается временная задержка t|. , Таким образом, предлагаемое устройство за счет исключения потерь временина выборку tj в блоке 2 памяти в режимах умножения и возведения в квадрат и упрощения перехода с одного режима работы на другой позволяет повысить производительность работы по отношению к прототипу. При этом происходит упрощение устройства за счет уменьшения объема блока 2 памяти, так как при работе устройства нет необходимости в хранении в блоке 2 кодов линейной функции f (Xjj) х., используемой в прототипе при выполнении операций умножения и возведения в квадрат. Указанные преимзпцества определяют технико-экономическую эффективность возможного применения предлагаемого устройства.

.

./5

1

ю

п

И

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля аналоговых объектов | 1989 |

|

SU1718189A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ АНАЛОГОВЫХ ОБЪЕКТОВ | 2004 |

|

RU2262128C1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ СО СЖАТИЕМ | 1984 |

|

SU1177836A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1157552A1 |

| УСТРОЙСТВО СБОРА, ПРЕОБРАЗОВАНИЯ И ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2079882C1 |

| Формирователь повторяющихся частотно-модулированных сигналов | 1988 |

|

SU1555806A1 |

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1986 |

|

SU1327174A1 |

| Функциональный генератор | 1980 |

|

SU883931A1 |

1. ГИБРИДНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее аналого-цифровой преобразователь, подключенный информационным входом к первому входу устройства, управлякнцим входом к первому выходу блока синхронизации, а цифровым выходом - к первому адресному входу блока памяти, соединенного вторым адресным входом с вторым выходом блока синхронизации, подключенного третьим выходом к управляющему входу аналогового коммутатора, а четвертым РМХОДОМ - к управляющему входу цифроаналогового преобразователя, выход которого является выходом устройства, отличающеес я тем, что, с целью повьпиения производительности устройства и его упрощения за счет сокращения объема памяти, оно содержит цифровой коммутатор, соединенный первым информационным входом с цифровым выходом аналого-цифрового преобразователя, вторым информационным входом - с выходом блока памяти, управляющим входом - с пятым выходом блока синхронизации, а выходом - с цифровым входом цифроаналогового преобразователя, подключенного аналоговым входом к выходу аналогового коммутатора, соединенного информационными входами с вторым входом устройства и с шиной ввода опорного напряжения, причем блок синхронизации подключен шестым выходом к входу управления считыванием блока памяти, а стробирующим входом - к выходу окончания цикла преобразования аналогоцифрового преобразователя. 2. Устройство по п. 1, отли- .. чающееся тем, что блок синхронизации содержит регистр, коммута(Л тор, формирователи импульсов записи и считывания, элемент задержки и генератор тактовых импульсов, подключенный выходом к первому выходу блока синхронизации и первому входу формирователя импульсов считывания, соединенного вторым входом со стробирующим входом блока синхронизации и с первым входом коммутатора, а выхоDO 30 дом - с щесть1м выходом блока синхронизации и с входом элемента задержки, подключенного выходом к второму входу коммутатора, соединенного управляющим входом с первым выходом регистра и с пятым выходом блока синхронизации, а быходом - с входом формирователя импульсов записи, выход которого соединен с четвертым выходом блока синхронизации, причем регистр подключен входом к шине ввода кода режима работы, а вторым и третьим выходами - к второму и третьему выходам блока синхронизации соответственно.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для воспроизведения функций | 1974 |

|

SU537356A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-15—Публикация

1983-05-24—Подача