база подключена к первому выводу двенадцатого резистора и базе второго стабилизирующего транзистора, эмиттер которого соединен с первым выводом тринадцатого резистора, второй вывод которого подключен к первому выводу четырнадцатого резистора, второй вывод которого соединен с базой третьего и коллектором четвертого стабилизирующих транзисторов, коллектор третьего стабилизирующего транзистора подключен к первым выводам шестнадцатого и семнадцатого резисторов, а эмиттер - к первому выводу пятнадцатого резистора и базам четвертого и пятого стабилизирующих транзисторов, эмиттеры которых, второй вывод пятнадцатого резистора и первый вывод третьего источника тока соединены с шиной нулевого потенциала, коллектор пятого стабилизирующего транзистора подключен к катоду диода, анод которого соединен с базой первого переключающего транзистора и вторым вы1аодом шестнадцатого резистора, коллекторы первого и второго стабилизирующих транзисторов и вторые выводы двенадцатого и семнадцатого реаисторов подключены к шине питания, эмиттеры управляющих транзисторов с второго по четвертый соединены с вторыми выводами источников тока с первого по третий, а базы являются третьим управляющим входом формирователя, базы пятого и шестого управляющих транзисторов подключены к второму выводу одиннадцатого резистора и коллектору второго управля1ощего транзистора, коллекторы к шине питания, а эмиттеры - соответственно к коллекторам второго и четвертого управляющ;их транзисторов и эмиттером двенадцатого и десятого переключающих транзисторов и являются адресными выходами формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

| Программируемый приемник сигналов для коммутационных сред | 1988 |

|

SU1718236A1 |

| Коммутатор | 1975 |

|

SU832721A1 |

| Мостовой троичный триггер Богдановича (его варианты) | 1984 |

|

SU1238206A1 |

| Мостовой троичный триггер | 1987 |

|

SU1448390A1 |

| Инверторная схема с минимальной асимметрией | 1985 |

|

SU1311016A1 |

| Мостовой троичный триггер (его варианты) | 1983 |

|

SU1150735A1 |

| Устройство для интегрирования произведения двух сигналов | 1984 |

|

SU1211764A1 |

| Генератор пилообразного напряжения | 1980 |

|

SU905992A1 |

| Преобразователь пикового индикатора магнитофона | 1979 |

|

SU1005181A1 |

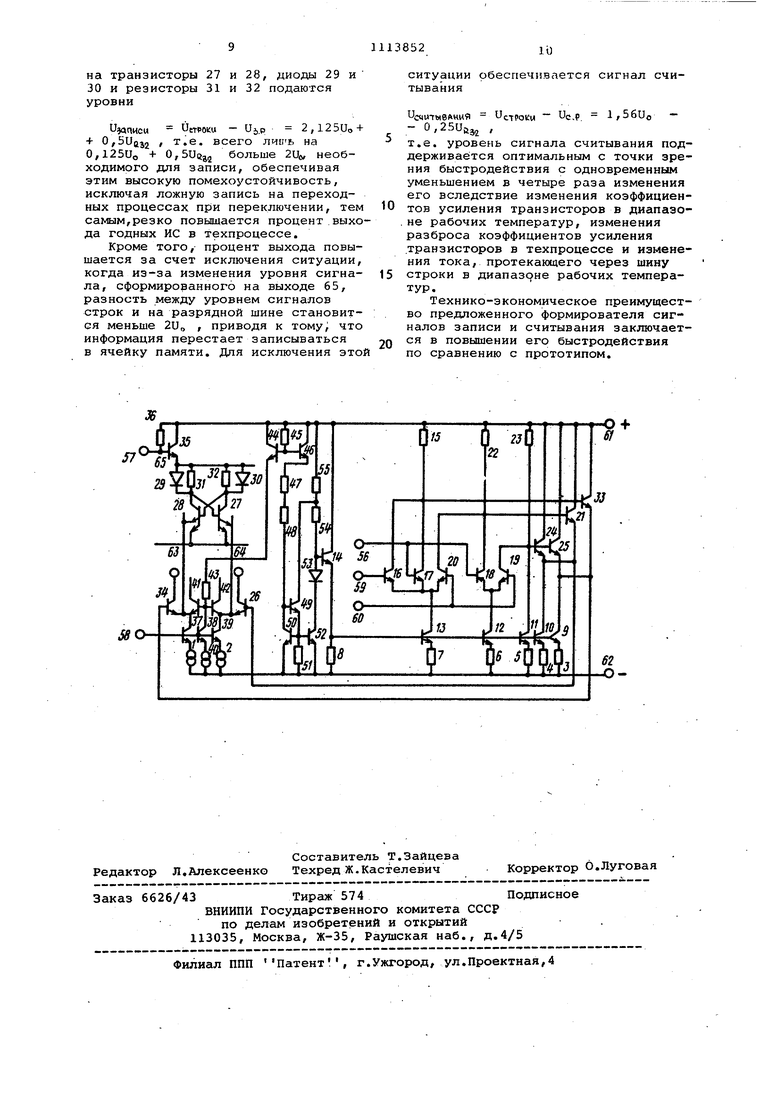

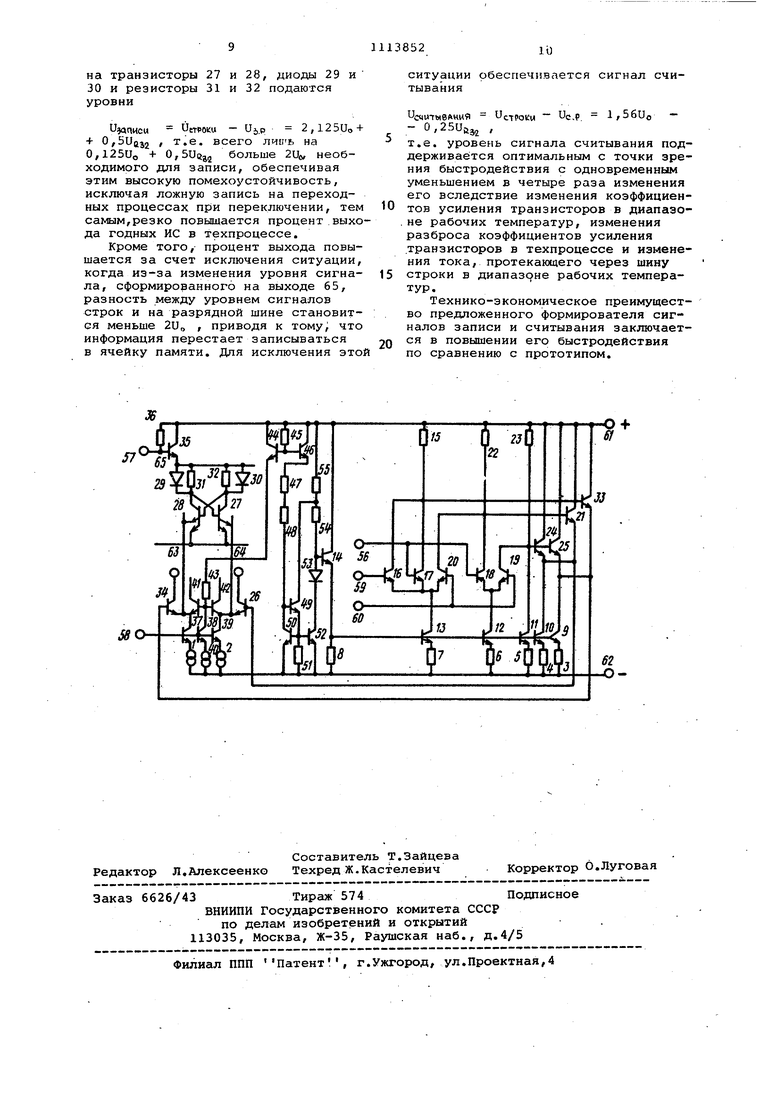

ФОРМИРОВАТЕЛЬ СИГНАЛОВ ЗАПИСИ И СЧИТЫВАНИЯ, содержащий переключающие транзисторы спервого по двенадцатый, первый управляющий транзистор, источники тока, резисторы и усилительные транзисторы с первого по пятый, эмиттеры которых соединены с первьдми выводами резисторов с первого по пятый, а базы с первым выводом шестого резистора и эмиттером первого переключающего резистора, коллектор которого соединен с первыми выводами резисторов с седьмого по девятый, коллекторами седьмого, восьмого, девятого и одиннадцатого переключающих транзисторов и шиной питания, причем второй вывод седьмого резистора подключен к базе одиннадцатого переключающего транзистора и коллекторам второго и третьего переключающих транзисторов, эмиттеры которых соединены с коллекторами пятого усилительного транзистора и эмиттером шестого переключающего транзистора,коллектор которого подключен к второму выводу восьмого резистора, базе седьмого переключающего транзистора и коллектору четвертого переключающего транзистора, эмиттер которого соединен с коллектором четвертого усилительного транзистора и эмиттером пятого переключающего транзистора, коллектор которого подключен к второму выводу девятого резистора, коллектору третьего усилительного транзистора и базам восьмого и переключающих транзисторов, эмиттеры которых соединены соответственно с эмиттером второго усилительного, эмиттером седьмого переключающего и базой десятого переключающего транзисторов и с эмиттером первого усилительного, эмиттером одиннадцатого переключающего и базой двенадцатого переключающего транзисторов , первые выводы первого и второго источника тока и вторые выводы резисторов с первого по шестой подключены к шине нулевого потенциала, база второго переключающего транзис(Л тора является информационным входом формирователя, базы третьего и четвертого переключающих транзисторов являются первым управляющим входом формирователя, базы пятого и шестого переключающих транзисторов являются входом опорного напряжения, первый вывод десятого резистора соединен с шиной питания и коллектором первого управляющего транзистора, база которой и второй вывод десятого резисто00 00 СП tsP ра- являются вторым управляющим входом формирователя,а эмиттер является одним из адресных выходов формирователя, коллекторы десятого и двенадцатого переключающих транзисторов являются соответственно единичным и нулевым контрольными выходами формирователя/ отличающийс я тем, что, с целью повышения быстродействия формирователя, в него введены управляющие транзисторы с второго по шестой, стабилизирующие транзисторы с первого по пятый, третий источник тока, диод и резисторы с одиннадцатого по семнадцатый, причем эмиттер первого стабилизирующего транзистора соединен с первым выводом одиннадцатого резистора, а

Изобретение относится к вычислитель ней технике и может быть использовано при создании полупроводниковых интегральных схем памяти.

Известен формирователь сигналов записи и считывания, содержащий транзисторы с первого по восьмой и резисторы, причем коллекторы первого и второго транзисторов подключен соответственно к первым выводам первого и второго резисторов, вторые выводы которых, коллекторы транзисторов с третьего по шестой и первые выводы третьего и четвертого резисторов соединены с шиной нулевого потенциала, эмиттеры первого и второго транзисторов соединены с первым выводом пятого резистора, а баз соответственно с базами третьего и четвертого транзисторов, эммитеры которых подключены к первым выводам шестого и седьмого резисторов, эмиттеры пятого и шестого транзисторов соединены с первыми выводами восьмого и девятого резисторов, а базы соответственно с вторыми выводами третьего и четвертого резисторов и коллекторами седьмого и- восьмого транзисторов, эмиттеры KOTOptax подключены к первому выводу десятого резистора, а базы являются одними из входов формирователя, вторые выводы ре зисторов с пятого по десятый подключены к шине питания, другими входами формирователя являются базы первого и второго транзисторов,

а выходами - эмиттеры транзисторов с третьего по шестой СП .

Недостатком этого формирователя является низкое быстродействие.

Наиболее близким к предагаемому является формирователь сигналов записи и считывания, состоящий из первого и второго источников тока, первые концы которых соединены с шиной

0 земля, которая подключена к первым концам первого - шестого резисторов, вторые концы которых соединены соответственно к эмиттерам первого - пятого транзисторов, базы

которых соединены с вторым концом шестого резистора и эмиттером шестого транзистора, коллектор которого соединен с шиной питания и седьмым резистором, второй конец которой соединен с коллектором седьмого

0 транзистора, база которого соединена с входом Э, а эмиттер - с коллектором пятого транзистора и эмиттером восьмого транзистора, коллектор которого соединен с коллектором

5 седьмого транзистора, а база - с входом ЗП/СЧ и базой девятого транзистора, эмиттер которого соеди. ней с коллектором четвертого транзистора и эмиттером десятого транзис0 тора, база которых соединена с входом и базой одиннадцатого транзистора, эмиттер которого соединен с эмиттером восьмого транзистора, а коллектор - с коллектором девятого

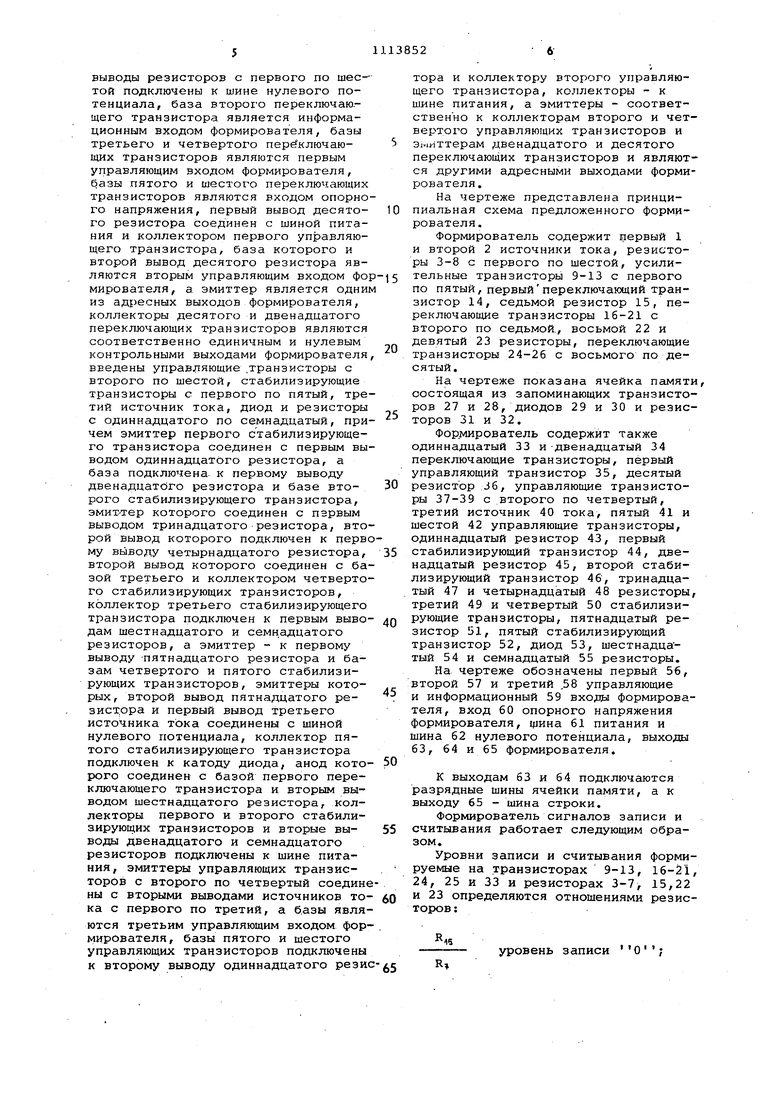

5 транзистора, базой двенадцатого транзистора и восьмым резистором, второ конец которого соединен с шиной пимания и первым концом девятого резистора, второй конец которого соед нен с коллектором десятого и третье го транзисторов, а также с базами тринадцатого и четырнадцатого транзисторов, коллекторы которых соединены с шиной питания и коллектором двенадцатого транзистора, эмиттер которого соединен с эмиттером тринадцатого транзистора, коллектором второго транзистора и базой пятнадцатого транзистора, коллектор которого соединен с выходом , а эмиттер - с первой разрядной шиной, к которой подключен первый эмиттер первого двухэмиттерного транзистора второй эмиттер которого включен в цепь хранения, а база соединена с коллектором второго двухэмиттерного транзистора, катодом первого дио да и десятым резистором, второй конец которого соединен с анодом перв го диода, шиной строки и эмиттером шестнадцатого транзистора, база котого соединена с входом рез одиннадцатый резистор с коллектором шестнадцатого транзистора, шиной питания и коллектором семнадцатого транзистора, база которого соединена с коллектором восьмого транзистора, а эмиттер - с эмиттером четырнадцатого транзистора, кол лектором первого транзистора и базо восемнадцатого транзистора, коллектор которого соединен с выходом О , а эмиттер -с второй разрядкой шиной,к к торой подключен первый эмиттер второг двухэмиттерного транзистора, второй эмиттер которого включен в цепь хра нения, а база соединена с катодом второго диода и первым концом двенадцатого резистора, второй конец которого соединен с анодом второго диода и шиной строка, кроме того первая разрядная шина соединена с вторым концом первого источника тока и эмиттером девятнадцатого транзисто ра, коллектор которого соединен с ши ной питания, а база с выходом Y и базой двадцатого транзистора, эмиттер которого соединен с вторалм концом второго источника тока и второй разрядной шкной, а коллектор с шиной питания и коллектором шестого транзистора, база которого соединена через тринс1дцатый резистор с шиной питания, а через три последова тельно включенных в прямом направлении диода - с шиной земля С 21. Недостатками этого формирователя сигналов записи и считывания являются низкие быстродействие при считывании и процент выхода годных ИС при их изготовлении, связанные с тем, что разность уровней напряжения, формируемая цепью строка разрядная шина на ячейку памяти, сильно меняется от образца к образцу, а также в диапазоне рабочих температур из-за того, что большой ток выбранной строки, протекая через транзистор, формирующий сигнал записи и считывания строки, создаст своим базовым током довольно значительное падение напряжения на резисторе в цепи его базы, .сильно за-п сящее от тока записи и считывания строки, который сильно меняется в диапазоне рабочих температур, от разброса коэффициента усиления транзистора. Цель изобретения - повышение быстродействия формирователя при считывании. Поставленная цель достигается тем, что в формирователь сигналов записи и считывания, содержащий переключающие транзисторы с первого по двенадцатый, первый управляющий транзистор, источники тока, резисторы и усилительные транзисторы с первого по пятый, эмиттеры которых соединены с первыми выводами резисторов с первого по пятый, а базы с первым выводом шестого резистора и эмиттером первого переключающего транзистора, коллектор которого соединен с первыми выводами резисторов с седьмого по девятый, коллекторги и седьмого, восьмого, девятого и одиннадцатого переключающих транзисторов и шиной питания, причем вывод седьмого резистора подключен к базе одиннадцатого Переключающего транзистора и коллекторам второго и третьего переключающих транзисторов эммитеры которых соединены с коллектором пятого усилительного транзистора и эмиттером шестого переключающего транзистора, коллектор которого 11одключен к второму выводу восьмого резистора, база седьмого переключающего транзистора и коллектору четвертого переключающего транзистора, эмиттер которого соединен с коллектором четвертого усилительного транзистора и эмиттером пятого переключающего транзистора, коллектор которого подключен к второму выводу девятого резистора, коллектору третьего усилительного транзистора и базам восьмого и девятого переключающих транзисторов, эмиттеры которых соединены соответственно с эмиттером второго усилительного, эмиттером седьмого переключающего и базой десятого переключающего транзисторов и с эмиттером первого усилительного, эмиттером одиннадцатого переключающего и базой двенадцатого переключающего транзисторов, первые выводы первого и вторюго источников тока и вторые выводы резисторов с первого по шестой подключены к шине нулевого потенциала, база BTOpoio переключаю.щего транзистора является информационным входом формирователя, базы третьего и четвертого переключаютих транзисторов являются первым управляющим входом формирователя, базы пятого и шестого переклюушющих транзисторов являются входом опорно го напряжения, первый вывод десятого резистора соединен с шиной питания и коллектором первого управляющего транзистора, база которого и второй вывод десятого резистора являются вторым управляющим входом фо мирователя, а эмиттер является одни из адресных выходов формирователя, коллекторы десятого и двенадцатого переключающих транзисторов являются соответственно единичным и нулевым контрольными выходами формирователя введены управляющие .транзисторы с второго по шестой, стабилизирующие транзисторы с первого по пятый, тре тий источник тока, диод и резисторы с одиннадцатого по семнадцатый, при чем эмиттер первого стабилизирующего транзистора соединен с первым вы водом одиннадцатого резистора, а база подключена к первому выводу двенадцатого резистора и базе второго стабилизирующего транзистора, эмиТТер которого соединен с пэрвым выводом тринадцатого резистора, вто рой вывод которого подключен к перв му выводу четырнадцатого резистора, второй вывод которого соединен с ба зой третьего и коллектором четверто го стабилизирующих транзисторов, коллектор третьего стабилизирующего транзистора подключен к первым выво дам шестнадцатого и семнадцатого резисторов, а эмиттер - к первому выводу пятнадцатого резистора и базам четвертого и пятого стабилизирующих транзисторов, эмиттеры которых, второй вывод пятнадцатого резистрра и первый вывод третьего источника тока соединены с шиной нулевого потенциала, коллектор пятого стабилизирующего транзистора подключен к катоду диода, анод кото рого соединен с базой первого переключающего транзистора и вторым выводом шестнадцатого резистора, коллекторы первого и второго стабилизирующих транзисторов и вторые выводы двенадцатого и семнадцатого резисторов подключены к шине питания, эмиттеры управляющих транзисторов с второго по четвертый соедин ны с вторыми выводами источников то ка с первого по третий, а б.азы явля ются третьим управляющим входом фор мирователя, базы пятого и шестого управляющих транзисторов подключены к второму выводу одиннадцатого резн тора и коллектору второго управляющего транзистора, коллекторы - к шине питания, а эмиттеры - соответственно к коллекторам второго и четвертого управляющих транзисторов и Э1.1иттерам двенадцатого и десятого переключающих транзисторов и являются другими адресными выходами формирователя. На чертеже представлена принципиальная схема предложенного формирователя. Формирователь содержит щервый 1 и второй 2 источники тока, резисторы 3-8 с первого по шестой, усилительные транзисторы 9-13 с первого по пятый, первыйпереключающий транзистор 14, седьмой резистор 15, переключающие транзисторы 16-21 с второго по седьмой., восьмой 22 и девятый 23 резисторы, переключающие транзисторы 24-26 с восьмого по десятый. На чертеже показана ячейка памяти, состоящая из запоминающих транзисторов 27 и 28, диодов 29 и 30 и резисторов 31 и 32. Формирователь содержит также одиннадцатый 33 и-двенадцатый 34 переключающие транзисторы, первый управляющий транзистор 35, десятый резистор 36, управляющие транзисторы 37-39 с второго по четвертый, третий источник 40 тока, пятый 41 и шестой 42 управляющие транзисторы, одиннадцатый резистор 43, первый стабилизирующий транзистор 44, двенадцатый резистор 45, второй стабилизирующий транзистор 46, тринадцатый 47 и четырнадцатый 48 резисторы, третий 49 и четвертый 50 стабилизирующие транзисторы, пятнадцатый резистор 51, пятый стабилизирующий транзистор 52, диод 53, шестнадцатый 54 и семнадцатый 55 резисторы. На чертеже обозначены первый 56, второй 57 и третий .58 управляющие и информационный 59 входы формирователя, вход 60 опорного напряжения формирователя, щина 61 питания и шина 62 нулевого потенциала, выходы 63, 64 и65 формирователя. К выходам 63 и 64 подключаются разрядные шины ячейки памяти, а к выходу 65 - шина строки. Формирователь сигналов записи и считывания работает следующим образом. Уровни записи и считывания формируемые на .транзисторах 9-13, 16-21, 24, 25 и 33 и резисторах 3-7, 15,22 и 23 определяются отношениями резисторов : уровень записи О; уровень записи уровень считывания с учетом напряжения на объединенны базах транзисторов 11,12 и 13, задаваемого транзисторами 46, 49 и 5 диодом 53 и резисторами 48, 47, 51 54 и 55. Учитывая сдвиг этих уровней на транзисторах 26 и 34, уровни сигна лов, формируемые на разрядных выхо дах 63 и 64 можно записать в виде )--J - ил Uj.o. -ЕПЙТ - gy (уровень сигнала записи) ; UC.P. ЕП«Т -C(UR -Ud3,i)----:i - сТэгв RS - UjjJypoBeHb сигнала считывания) , где ЕПЩ-- напряжение питания на Iшине 61; напряжение на базах транзисторов 11, 12 -йзз %эзц, падение напряжения на переходах база-эмиттер транзисторов 33, 34 и 35. С учетом того,что падение напря жения UQ на переходах база-эмиттер различных транзисторов в интеграль ной технологии с большой степенью точности выдерживается одинаковыми можно записать iP. ЕПИТ. - и«8 ° UC.P. ЕПМТ. - (Ui28 - и,) - 2и„ где ,Uo - падение напряжения на переходах база-эмиттер транзисторов. Напряжение UR определяется источником стабилизирующего напряжения на транзисторе 44 и резисторе 45, которые применяются в качестве отслеживающего элемента, моделирующего сдвиг уровня строки ячейки памяти за счет изменения тока строки в диапазоне рабочих температур, изменения коэффициента усиления транзи торов в диапазоне рабочих температур также от разброса коэффициента усиления транзисторов, получаемого в техпроцессе. Транзистор с резистором 32 формируют уровень сигнала на выходе 65, позволяя отслеживать уро вень сигнала синхронно с изменением уровня, сформированного на шине строки, тем самым повышая быстродей ствие формирователя и, кроме того, (а это является самым главным) выбирая ток, задаваемый в эмиттер транзистора 44 со всех выбранных разрядов ячеек памяти (показан лишь один разряд, выполненный на транзисторах 27 и 2И, равный току через транзистор 35, получим на резисторе 45 падение напряжения, абсолютно идентичное падению напряжения на резис-/ торе 36 в любых условиях и для любого экземпляра ИС. Таким образом, напряжение на коллекторе транзистора 52 будет повторять напряжение на его коллекторе,равное 2Uo,Ho превышая его на величину падения напряжения на резисторе 45, так как в цепи коллектора транзистора 52 нагрузка идентична нагрузке в цепи коллектора транзистора 50 за вычетом цепи, моделирующей падение напряжения на резисторе 36. .Поэтому напряжение на базе транзистора 14 равно зи - и«. -&ic u «з& Для того, чтобы исключить в дальнейшем при работе формирователя в диапазоне рабочих температур насыщение транзисторов 16-20 (что снизило бы его быстродействие), сдвигают первоначальный уровень сигнала записи и считывания на 0,25 UQ путем подключения коллектора транзистора 49 к общей точке резисторов 54 и 55, Таким образом, напряжение на базе транзистора 14 равно 2,75Uo + Цоз , а отсюда % 1,75и„ + и С учетом того, что R 1,5; 0,75, получается уровень записи на разрядной шине U5.P. Е„„ - (3,125U l,5U«j), уровень считывания на разрядной шине Ut.P, Erwr - (2,5би„ . 0, С учетом уровня сформированног иа шине строки, т.е. выходе 65 UCTPOICU Eqy - (Ue - V } ,

на транзисторы 27 и 28, диоды 29 и 30 и резисторы 31 и 32 подаются уровни

UWHHCU OerfOKU Ujp - 2,125Uo + + 0,5Uaj2 т «б- всего лиц-ь на 0,125Uo + 0,50832

больше 2Цу необходимого для записи, обеспечивая этим высокую помехоустойчивость, исключая ложную запись на переходных процессах при переключении, тем самым,резко повышается процент выхода годных ИС в техпроцессе.

Кроме того, процент выхода повышается за счет исключения ситуации, когда из-за изменения уровня сигнала, сформированного на выходе 65, разность между уровнем сигналов строк и на разрядной шине становится меньше 21}„ , приводя к тому; что информация перестает записываться в ячейку памяти. Для исключения это

ситуации обеспечивпется сигнал считывания

исчи ывлния ОСТРОКИ UC.P l,56Uo - 0,25Uu32 ,

т.е. уровень сигнала считывания поддерживается оптимальным с точки зрения быстродействия с одновременным уменьшением в четыре раза изменения его вследствие изменения коэффициентов усиления транзисторов в диапаэо. не рабочих температур, изменения разброса коэффициентов усиления транзисторов в техпроцессе и изменения тока, протекающего через шину строки в диапазоне рабочих температур.

Технико-экономическое преимущество предложенного формирователя сиг- налов записи и считывания заключается в повьпиении его быстродействия по сравнению с прототипом.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| и др | |||

| Справочник по интегральным микросхемам | |||

| М., Энергия, 1981, с | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| и др | |||

| Быстродействующие БИС на переключателях тока | |||

| М., Радио и связь, 1982, с | |||

| Устройство для автоматического управления клапаном для дозировки жидкости | 1952 |

|

SU100105A1 |

Авторы

Даты

1984-09-15—Публикация

1983-05-27—Подача