Изобретение относится А импульсной технике и может бмть использовано при построении различных цифровых ИС с парафазьыми выходами.

Целью изобретения является уменьшение аси метри:и выходных сигналов путем введения обратной связи между выходными каскадами.

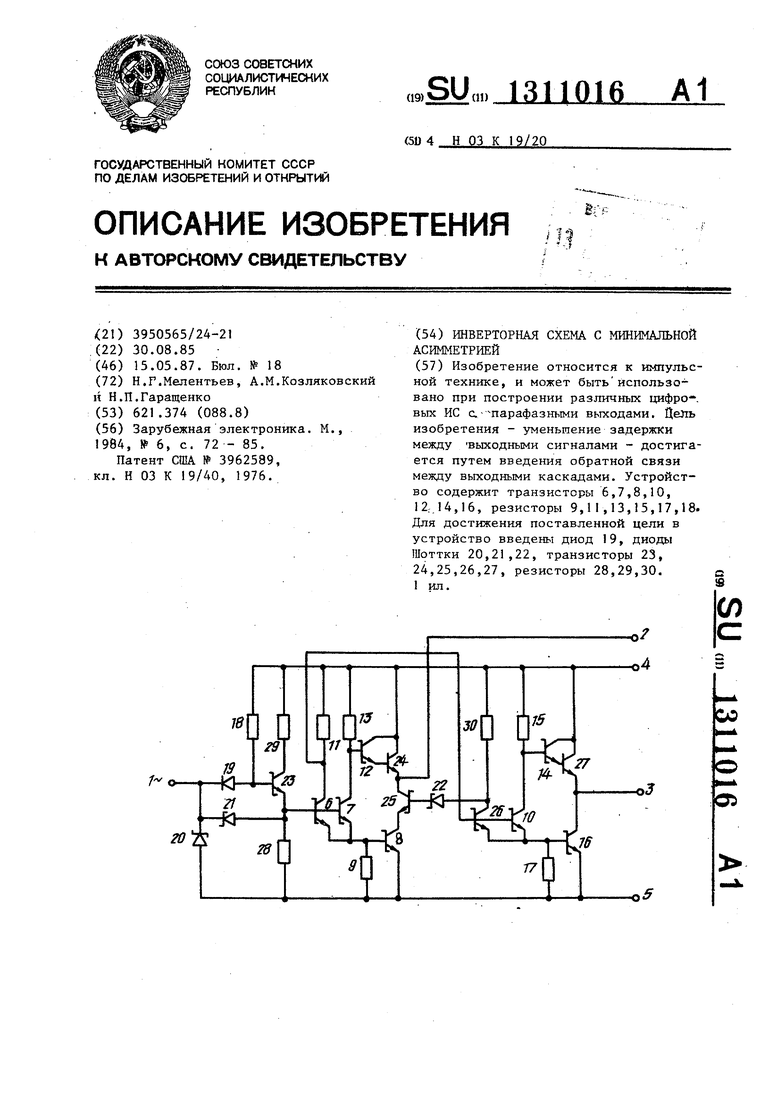

На чертеже представлена электрическая принципиальная схема инвер- торной схемы с минимальной асимметрией .

Инверторная схема с минимальной асимметрией содержит входн,то иину 1 инверсную выходную сиину 2., прямую выходную гаину 3, гаину питания 4, обш.ую 5, первый и второй тран зисторь; 6 и 7, базы которых соединены вместе, а эмиттеры сое/1;ир ены с базой третьего транзистора 8 и через первый резистор 9 с общей шиной

5и эмиттерами ранзисто- ра 8,, коллектор первого транзистора

6соединен с базой четвертого транзистора 10 и через торой резистор

11 с шиной питания А, коллектор второго транзистора 7 соединен с базой пятого транзистора 12 и через третий резистор 13 с шиной питание 4-и коллектором пятого транзистора 12, коллектор четвертого ч ранэисто- ра 10 соединен с базой шестого транзистора 14 и через четве1: тый резистор 15 - с FjHftoft питания 4 и с коллектором шестого транзистора 14, эмиттер четвертого транзистора 10 соединен с базой сед,ьмого транзистора 16 и через пятьш резистор 1 7 - с общей шиной 5 и эмиттером седьмо о транзистора 16, коллектор которого соединен с прямой вьуходной шиной 3, первый вьшод гаестого резистора 18 соединен с пшной питания 4, диод 19 первь й, второй и третий диоды 20,21 и 22. восьмой, девятый, десятый, одиннадпатьш и двенадцатый транзисторы 23,24,25,26 и 27 седьмой,, восьмой и девятый резисторы 28,29 и 30. Катоды диода 19,, первого и второго диодов lUoTTKH 20 и 21 соединены с входной шиной 1. анод первого диода (1оттки 20 соединен с общей гш- ной 5, анод второго диода 1оттки 21 соединен с эмиттером восьмого траг:- зистора 23, базой первого транзистора 6 и через седьмой резистор 28 - с общей шиной 5,, анод диода 1 9 динен с базой восьмого транзисторе. 23 и вторым выводом luecToro резисто7

3110162

ра 18, коллектор восьмого транзистора 23 че1зез восьмой резистор 29 соединен с шиной питания 4, эмиттер пятого транзистора 12 соединен с базой девятого транзистора 24, эмиттер которого соединен с коллектором десятого транзистора 25 и с инверсной выходной шиной 2, а коллектор - с шиной питания 4, эмиттер десятого транзистора 25 сое71инен с коллектором третьего транз:истора 8, а база - с катодом третьего диода Чоттки 22, анод которого соединеЕ с коллектором одиннадцатого транзистора 26 и через девятый резистор 30 с шиной питания 4, базы и эмитт фы одиннадцатого и четвертого транзисторов 26 и 10 соединены попарно,, З Миттер и коллектор того транз,исгора ; 4 соединены соот- зетственно с базой и коллектором двенадцатого трс.Ртзис гора 27, эмиттер которого соединен с прямой выходной 1,аиной 3, первый ,, второй, третий, четвертый, пятый, шестой, седьмой, зосьмО й, десятый и одиннадцатый транзисторы 6 ,, 7 5 8,, 1 0, 1 2 ,1 4 ,1 6, 23 , 25 , 26 1 1меют переходы Шоттки.

Схема работает следующим образом. Если тга шину 1 подан низкий уро30 ;зень aпpяжeния, то диод 19 открыт, а транзисторь; 23,6,7 и 8 закрыты, так как отсутствуе;т ток в базовых цепях этих Т :анзисторов. На шине 2 сформируете;- высокий уровень напря-

35 жения5 так как транзисторы 12 и 24 йудут открыть:,. Высокий уровень напряжения на коллекторе закрь.того транзистора 6 приво, к появлению тока I базовых цепях транзисторов 26 и 0.

40 Транзисторы 26 и 10 открьгоаются, и ;ачинают протекать, токи через резисторы 30 и 15, образзлощие базовый ок транзистора 16. Открытый транзистор 16 формирует на шине 3 кий уровень напряжения. Транзистор 25 закрыт 5 так как закрыт транзистор 8 и отсутс-,иует замкнутая цепь для протеканкя базового тока транзистора 25. Следовател)зно, при наличии на

50 lUHHe 1 низкого уг)овня напряжения на шине 2 форми :-уется высокийуровень напряжения, а напине 3 -низкий уровень )- а 1ряженкя, При и:зме 1ении на гаине рапряжания с иу зкого уровня на высо-55 кий диод 19 закрывается, в базу тран- зи;;тора 23 поступает ток от шины пи313

лекторных цепях этих транзисторов появляются токи, определяемые резисторами 11,13 и открывается транзистор 8. Таким образом, на коллекторе транзистора 8 формируется низкий ровень напряжения. Однако на шине 2 сохраняется высокий уровень напряжения до момента, пока не откроется транзистор 25, т.е. пока не закроется транзистор 26, и потенциал на его коллекторе не возрастет и станет достаточным для протекания тока через диод 22 в базу транзистора 25. Транзистор 16 выключается через резистор 17, а открытые транзисторы 14 и 27 образуют на шине 3 высокий уровень напряжения. Низкий уровень напряжения на коллек- ,торе транзистора 8 передается через открытый транзистор 25 на шину 2.

Таким образом, введение обратной связи между первым и вторым инверторами приводит к тому, что низкий уровень напряжения на шине 2 не может сформироваться раньше, чем на шине 3

начнет формироваться высокий уровень 25 восьмого транзистора, базой первого

напряжения. Следовательно, устраняется задержка между сигналом на шине 3 и сигналом на шине 2. Антизвонный диод 20 в схеме предназначен для ограничения величины отрицательных помех на входе схемы. Рассасывающий диод 21 и резистор 28 образуют цепь выключения транзисторов 6 и 7, резистор 9 выключает транзистор 8.

Формула изобретения

Инверторная схема с минимальной асимметрией, содержащая входную шину, инверсную выходную шину, прямую выходную шину, шину питания, общую шину, первьй и второй транзисторы, базы которых соединены вместе, а эмиттеры соединены с базой третьего транзистора и через первый резистор с общей шиной и эмиттером третьего транзистора, коллектор первого транзистора соединен .с базой четвертого транзистора и через второй резистор с шиной питания, коллектор второго транзистора соединен с базой пятого транзистора и через третий резистор с шиной питания и коллектором пятого

ВНИИПИ Заказ 1902/55 Тираж 902 Подписное Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

164

транзистора, коллектор четвертого транзистора соединен с базой шестого транзистора и через четвертый резистор - с шиной питания и с коллекто- ром шестого транзистора, эмиттер , четвертого транзистора соединен с

базой седьмого транзистора, коллектор которого соединен с прямой выходной шиной и через пятый резистор - с общей шиной и эмиттером седьмого транзистора, первый вьгоод шестого резистора соединен с шиной питания, отличающаяся тем, что, с целью уменьшения асимметрии выходных сигналов, в него введены диод, первый, второй и третий диоды Шоттки; восьмой, девятый, десятый, одиннадцатью и двенадцатый транзисторы, седьмой,восьмой и девятый резисторы, катоды диода, первого и второго дов Шоттки соединены с входной шиной, анод первого диода Иоттки соединен с общей шиной, анод- второго диода Шоттки соединен с эмиттером

транзистора и через седьмой резистор с общей шиной, анод диода соединен с базой восьмого транзистора и вторым вьгоодом шестого резистора, коллектор

Bot bMoro транзистора через восьмой резистор соединен с шиной питания, эмиттер пятого транзистора соединен с-базой девятого транзистора, эмиттер которого соединен с коллектором;

десятого транзистора и с инверсной выходной шиной, а коллектор - с ной питания, эмиттер десятого транзистора соединен с коллектором третьего транзистора, а база - с катодом .

третьего диода Чоттки, анод которого соединен с коллектором одиннадцатого транзистора и через девятый резистор с шиной питания, базы и эмиттеры одиннадцатого и четвертого транзисторов соединены попарно, эмиттер и коллектор шестого транзистора соединен .соответственно с базой и коллектором двенадцатого транзистора, эмиттер, которого соединен с прямой выходной шиной, первый, второй, третий, четвертый, пятьм, шестой, седьмой, восьмой, десятый и одиннадцатый транзисторы имеют переходы Чоттки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двойной инвертор с минимальной асимметрией | 1987 |

|

SU1499484A1 |

| Устройство задержки | 1989 |

|

SU1793535A1 |

| Двойной инвертор с минимальной асимметрией | 1984 |

|

SU1499483A1 |

| Полный троичный сумматор | 1979 |

|

SU826342A1 |

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| Схема согласования уровней ТТЛ-ЭСЛ | 1985 |

|

SU1309301A1 |

| JK-триггер | 1989 |

|

SU1713091A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324104A1 |

Изобретение относится к импульсной технике, и может быть использовано при построении различных цифро-. вых ИС с.- парафазными выходами. Цель изобретения - уменьшение задержки между ВЫХОДНЫМИ сигналами - достигается путем введения обратной связи между выходными каскадами. Устройство содержит транзисторы 6,7,8,10, 12; 14,16, резисторы 9,11,13,15,17,18. Для достижения поставленной цели в устройство введены диод 19, диоды Шоттки 20,21,22, транзисторы 23, 24,25,26,27, резисторы 28,29,30. 1 ил. i (Л /-0 С5 о

| Зарубежная электроника | |||

| М., 1984, № 6, с | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

| Патент США № 3962589, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-05-15—Публикация

1985-08-30—Подача