Изобретение относится к усилительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Целью изобретения является повышение помехоустойчивости.

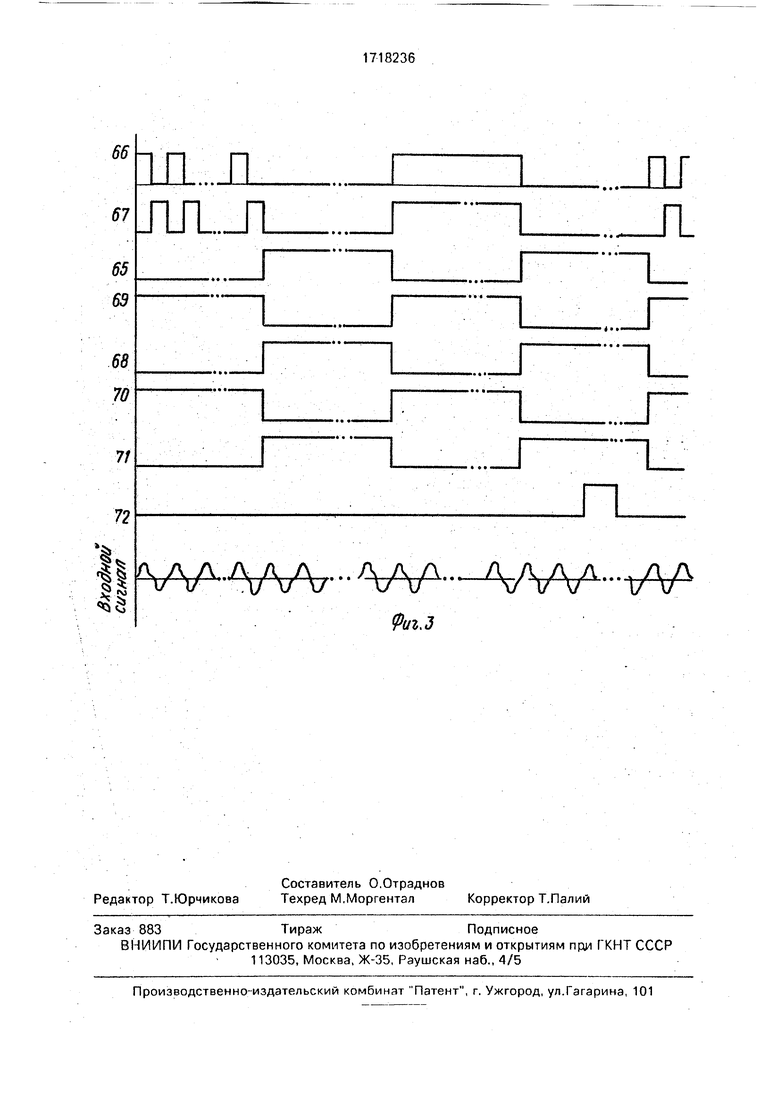

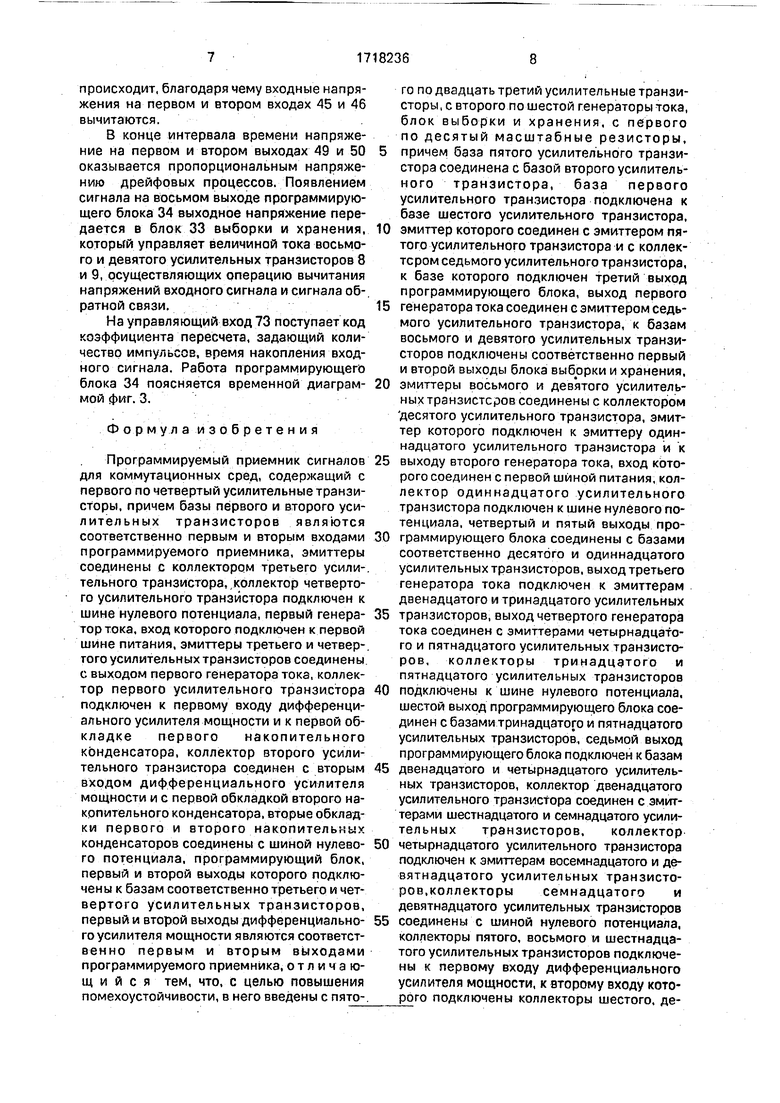

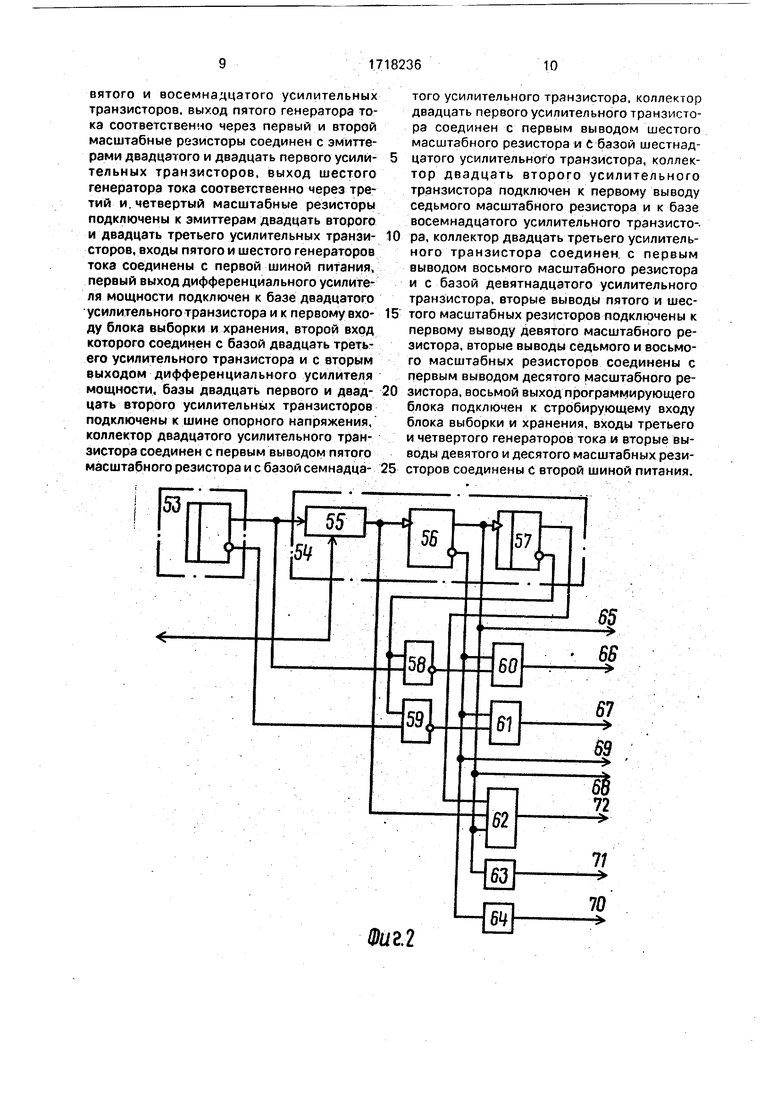

На фиг. 1 изображена схема приемника; на фиг. 2 -схема программирующего блока; на фиг. 3 - временная диаграмма его работы.

Приемник содержит с первого по двадцать третий усилительные транзисторы 1...23, с первого по шестой генераторы 24...29 тока, первый и второй накопительные конденсаторы 30 и 31, дифференциальный усилитель 32 мощности, блок 33 выборки и хранения, программирующий блок 34, с первого по десятый масштабные резисторы 35...44, первый и второй входы 45 и 46, первую и вторую шины 47 и 48 питания, первый и второй выходы 49 и 50, шину 51 опорного напряжения, шину 52 нулевого потенциала.

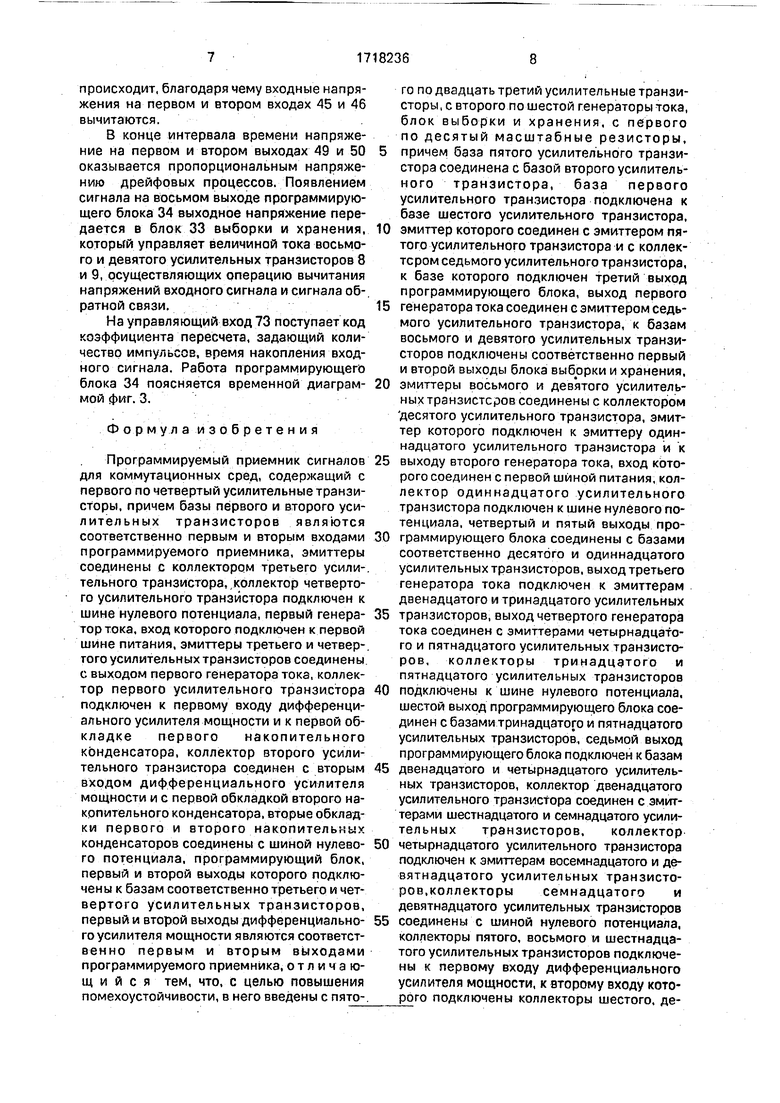

На фиг. 2 изображен один из возможных вариантов функциональной схемы программирующего, блока. Он содержит генератор 53 импульсов с триггерным выхо-. дом, Счетчик 54 импульсов, счетчик 55, первый и второй разрядные счетные триггеры 56 и 57, первый и второй элементы И-НЕ 58 и 59, первый, второй и третий элементы И 60, 61 и 62, первый и второй блоки 63 и 64 согласования уровней, первый выход 65, второй, третий, четвертый, пятый, шестой, седьмой, восьмой выходы 66, 67, 68, 69, 70, 71, 72, управляющий вход 73. Программируемый приемник сигналов для коммутационных сред работает следующим образом.

В исходном состоянии четвертый, одиннадцатый, тринадцатый и пятнадцатый усилительные транзисторы 4, 11, 13 и 15, являющиеся управляющими переключателями токов/открыты сигналами с второго, пятого и шестого выходов программирующего блока 34. Токи первого, второго, третьего и четвертого генераторов 24. 25, 26 и 27 тока ответвляются в эти усилительные транзисторы. Первый, второй, пятый, шестой, восьмой, девятый и с шестнадцатого по де-. вятнадцатый усилительные транзисторы 1, 2, 5Г 6, 8, 9, 16,. 17, 18 и 19 дифференциальных пар заперты ввиду отсутствия токов эмиттеров. Первый и второй накопительные конденсаторы 30 и 31 разряжены, напряжение на первом и втором выходах 49,50 рав- но нулю. При появлении на первом, третьем, четвертом и седьмом выходах программирующего блока 34 разрешающих сигналов токи с первого по четвертый генераторов 24...27 тока переключаются соответственно в третий, седьмой, десятый, двенадцатый и четырнадцатый усилительные транзисторы 3, 7, 10, 12 и 14. Появление токов эмиттеров усилительных транзисторов дифференциальных пар отпирает эти транзисторы. Напряжение между первым и вторым входами 45 и 46 равно нулю. Коллекторные токи первого, второго, пятого и шестого усилительных транзисторов 1, 2, 5 и 6

0 разряжают первой и второй накопительные транзисторы 30 и 31. Заряд накопительных конденсаторов выполняется токами третьего и четвертого генераторов 26 и 27 тока и шестнадцатого и восемнадцатого усили5 тельных транзисторов 16 и 18. Равенство токов заряда и разряда первого и второго накопительных конденсаторов 30 и 31 поддерживается цепями отрицательной обратной связи, содержащими схемы сравнения

0 на двадцатом, двадцать первом, двадцать втором и двадцать третьем усилительных транзисторах 20, 21, 22 и 23. Благодаря отрицательной обратной связи напряжение на первом и втором накопительных конден5 саторах 30 и 31 поддерживается равным напряжению с шины 51 спорого напряжения, поскольку дифференциальный усилитель 32 мощности имеет коэффициент передачи по напряжению, равный единице.

0 Особенность описываемого приемника состоит в том, что поступление сигнала про- изволвной формы на первый и второй входы 45 и 46 при идентичных первом, втором, пятом и шестом усилительных транзисторах

5 1, 2, 5 и 6 не вызывает изменение напряжения на первом и втором выходах 49 и 50. Относительно входного сигнала выходы дифференциальных пар на первом, втором и пятом, шестом усилительных транзисто0 pax 1, 2 и 5, 6 включены встречно. Поэтому входной сигнал вызывает перераспределение коллекторного тока между усилительными транзисторами, подключенными к одному и тому же накопительному конден5 сатору. Если одну из пар усилительных транзисторов отключить с помощью управляющих сигналов с первого или третьего выходов программирующего блока 34, то каждая пара усилительных транзисторов

0 работает как дифференциальный усилитель, коллекторные токи которого обеспечивают разряд первого и второго накопительных конденсаторов 30 и 31 Программируемый приемник сигналов

5 осуществляет накопление усиленных по напряжению импульсов. Режим накопления разнополярных элементов входного сигнала осуществляется в результате переключения тока первого генератора 24 тока третьим и седьмым усилительными транзисторами 3 и 7, выполняющими функцию переключателя тока, между дифференциальными парами первого, второго и пятого, шестого усилительных транзисторов 1, 2 и 5, 6 при каждой смене полярности элементов входного сигнала. При этом длительность включения тока в дифференциальную пару равна длительности элемента входно-г го сигнала. Совпадение элементов входного сигнала и импульсов тока осуществляется в результате синхронизации с помощью программирующего блока 34.

При поступлении на первый и второй входы 45 и 46 элемента входного сигнала Положительной полярности открываются первый и второй усилительные транзисторы 1 и 2, что приводит к появлению разности напряжений заряда первого и второго накопительных конденсаторов 30 и 31. Если следующие элементы входного сигнала имеют ту же полярность, то третий усилительный транзистор 3, выполняющий функцию проходного, остается открытым. При измене нии полярности элементов входного сигнала закрывается третий усилительный транзистор 3 и открывается седьмой усилительный транзистор 7. Благодаря этому изменение полярности входного сигнала не вызывает изменение полярности приращения напряжения на первом и втором выходах 49 и 50. Следовательно, режим накопления элементов входного сигнала выполняется при условии программирования блока 34 в соответствии с принимаемым сигналом.

Помехоустойчивость к импульсным воздействиям достигается благодаря тому, что. время накопления элементов входного сигнала выбирается значительно больше длительности импульсной помехи.

Помехоустойчивость к периодическим воздействиям обеспечивается благодаря введению второй дифференциальной пары из пятого и шестого усилительных транзисторов 5 и 6, включение которых производится периодически. Благодаря этому избирательность к входным сигналам фиксированной частоты отсутствует, что приводит к ослаблению входных периодических сигналов по сравнению с программируемым сигналом.

Помехоустойчивость к воздействию дрейфовых процессов в усилительных транзисторах, характеризуемых постоянной смещения на первом и втором входах 45 и 46, получена в результате подключения третьей дифференциальной пары на восьмом и девятом усилительных транзисторах 8 и 9, управление которыми осуществляется с первого и второго выходов 49 и 50 через.

блок 33 выборки и хранения. Особенность умножения входного сигнала на знакопеременную функцию, реализуемая управляемыми первой и второй дифференциальными 5 парами, состоит в том, что включение цепей обратной связи на первый и второй входы 45 и 46 для компенсации постоянных смещений исключается, так как любая отрицательная обратная связь для одной пары.

10 транзисторов является положительной для другой пары, что приводит к неустойчивой работе. Поэтому компенсирующая обратная связь включается с помощью дополнительной дифференциальной пары по схеме сум15 мирования токов непосредственно на

накопительных конденсаторах. Работа такой схемы состоит в следующем.

На интервале времени действия входного сигнала восьмой и девятый усилитель0 ные транзисторы 8 и 9 открыты ввиду переключения второго генератора 25 тока в десятый усилительный транзистор 10, выполняющий функцию проходного. Разность выходных токов восьмого и девятого усили5 тельныхтранзисторов8и9 имеет обратный знак и пропорциональна выходному напряжению на выходах 49 и 50. которое передается через блок 33 выборки и хранения. В конце интервала программируемый прием0 ник сигналов переводится в режим запоминания выходного напряжения. При этом четвертый, одиннадцатый, тринадцатый и пятнадцатый усилительные транзисторы 4, 11, 13, 15 открываются, что приводит к вы5 ключению токов заряда и разряда первого и

второго накопительных конденсаторов 30 и 31. Благодаря большому выходному сопротивлению выключенных дифференциальных пар и большому входному

0 сопротивлению дифференциального усилителя 32 мощности напряжение на первом и втором выходах 49 и 50 поддерживается неизменным при минимально возможных величинах емкости первого и второго

5 накопительных конденсаторов 30 и 31. В этом режиме осуществляется съем напряжения выходного сигнала, а блок 33 выборки и хранения хранит предыдущее значение входного напряжения, так как сигнал на

0 восьмом выходе программирующего блока 34 отсутствует.

После режима запоминания.осуществляется режим компенсации выходного напряжения при нулевом входном

5 напряжении. В этом режиме открываются третий, седьмой, десятый, двенадцатый и четырнадцатый усилительные транзисторы 3,7, 10, 12 и 14. Переключения тока первого генератора 24 тока между третьим и седьмым усилительными транзисторами 3 и 7 не

происходит, благодаря чему входные напряжения на первом и втором входах 45 и 46 вычитаются.

В конце интервала времени напряжение на первом и втором выходах 49 и 50 оказывается пропорциональным напряжению дрейфовых процессов. Появлением сигнала на восьмом выходе программирующего блока 34 выходное напряжение передается в блок 33 выборки и хранения, который управляет величиной тока восьмого и девятого усилительных транзисторов 8 и 9, осуществляющих операцию вычитания напряжений входного сигнала и сигнала об-, ратной связи.

На управляющий вход 73 поступает код коэффициента пересчета, задающий количество импульсов, время накопления входного сигнала. Работа программирующего блока 34 поясняется временной диаграммой фиг. 3.

Ф о р м у л а и з о б р е т е н и я

Программируемый приемник сигналов для коммутационных сред, содержащий с первого по четвертый усилительные транзисторы, причем базы первого и второго уси- лительных транзисторов являются соответственно первым и вторым входами программируемого приемника, эмиттеры соединены с коллектором третьего усили-. тельного транзистора,,коллектор четвертого усилительного транзистора подключен к шине нулевого потенциала, первый генератор тока, вход которого подключен к первой шине питания, эмиттеры третьего и четвер-. того усилительных транзисторов соединены с выходом первого генератора тока, коллектор первого усилительного транзистора подключен к первому входу дифференциального усилителя мощности и к первой обкладке первого накопительного конденсатора, коллектор второго усилительного транзистора соединен с вторым входом дифференциального усилителя мощности и с первой обкладкой второго накопительного конденсатора, вторые обкладки первого и второго накопительных конденсаторов соединены с шиной нулевого потенциала, программирующий блок, первый и второй выходы которого подключены к базам соответственно третьего и четвертого усилительных транзисторов, первый и второй выходы дифференциального усилителя мощности являются соответст- венно первым и вторым выходами программируемого приемника, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены с пятого по двадцать третий усилительные транзисторы, с второго по шестой генераторы тока, блок выборки и хранения, с первого по десятый масштабные резисторы,

причем база пятого усилительного транзистора соединена с базой второго усилительного транзистора, база первого усилительного транзистора подключена к базе шестого усилительного транзистора.

0 эмиттер которого соединен с эмиттером пятого усилительного транзистора и с коллектором седьмого усилительного транзистора, к базе которого подключен третий выход программирующего блока, выход первого

5 генератора тока соединен с эмиттером седьмого усилительного транзистора, к базам восьмого и девятого усилительных транзисторов подключены соответственно первый и второй выходы блока выборки и хранения,

0 эмиттеры восьмого и девятого усилительных транзисторов соединены с коллектором десятого усилительного транзистора, эмиттер которого подключен к эмиттеру одиннадцатого усилительного транзистора и к

5 выходу второго генератора тока, вход кОто- рого соединен с первой шиной питания, коллектор одиннадцатого усилительного транзистора подключен к шине нулевого потенциала, четвертый и пятый выходы про0 граммирующего блока соединены с базами соответственно десятого и одиннадцатого усилительных транзисторов, выход третьего генератора тока подключен к эмиттерам двенадцатого и тринадцатого усилительных

5 транзисторов, выход четвертого генератора тока соединен с эмиттерами четырнадцатого и пятнадцатого усилительных транзисторов, коллекторы тринадцатого и пятнадцатого усилительных транзисторов

0 подключены к шине нулевого потенциала, шестой выход программирующего блока соединен с базами тринадцатого и пятнадцатого усилительных транзисторов, седьмой выход программирующего блока подключен к базам

5 двенадцатого и четырнадцатого усилительных транзисторов, коллектор двенадцатого усилительного транзистора соединен с эмиттерами шестнадцатого и семнадцатого усили- тельных транзисторов, коллектор

0 четырнадцатого усилительного транзистора подключен к эмиттерам восемнадцатого и девятнадцатого усилительных транзисторов,коллекторы семнадцатого и девятнадцатого усилительных транзисторов

5 соединены с шиной нулевого потенциала, коллекторы пятого, восьмого и шестнадцатого усилительных транзисторов подключены к первому входу дифференциального усилителя мощности, к второму входу которого подключены коллекторы шестого, девятого и восемнадцатого усилительных транзисторов, выход пятого генератора тока соответственно через первый и второй масштабные резисторы соединен с эмиттерами двадцатого и двадцать первого усилительных транзисторов, выход шестого генератора тока соответственно через третий и. четвертый масштабные резисторы подключены к эмиттерам двадцать второго и двадцать третьего усилительных транзисторов, входы пятого и шестого генераторов тока соединены с первой шиной питания, первый выход дифференциального усилителя мощности подключен к базе двадцатого усилительного транзистора и к первому входу блока выборки и хранения, второй вход которого соединен с базой двадцать третьего усилительного транзистора и с вторым выходом дифференциального усилителя мощности/базы двадцать первого и двадцать второго усилительных транзисторов подключены к шине опорного напряжения, коллектор двадцатого усилительного транзистора соединен с первым выводом пятого масштабного резистора и с базой семнадцатого усилительного транзистора, коллектор двадцать первого усилительного транзистора соединен с первым выводом шестого масштабного резистора и с базой шестнадцатого усилительного транзистора, коллектор двадцать второго усилительного транзистора подключен к первому выводу седьмого масштабного резистора и к базе восемнадцатого усилительного транзистора, коллектор двадцать третьего усилительного транзистора соединен с первым выводом восьмого масштабного резистора и с базой девятнадцатого усилительного транзистора, вторые выводы пятого и шестого масштабных резисторов подключены к первому выводу Девятого масштабного резистора, вторые выводы седьмого и восьмого масштабных резисторов соединены с первым выводом десятого масштабного резистора, восьмой выход программирующего блока подключен к стробирующему входу блока выборки и хранения, входы третьего и четвертого генераторов тока и вторые выводы девятого и десятого масштабных резисторов соединены с второй шиной питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для интегрирования произведения двух сигналов | 1984 |

|

SU1211764A1 |

| Компаратор напряжения | 1989 |

|

SU1653149A1 |

| Устройство для измерения электрической проводимости и магнитной проницаемости | 1989 |

|

SU1659928A1 |

| Балансный модулятор | 1980 |

|

SU907765A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Множительное устройство | 1982 |

|

SU1119037A1 |

| Стереодекодер для системы стереофонического радиовещания с полярной модуляцией | 1991 |

|

SU1748269A1 |

| Операционный усилитель | 1989 |

|

SU1721614A1 |

| Аналоговый перемножитель | 1989 |

|

SU1709353A1 |

| Балансный модулятор | 1980 |

|

SU904197A1 |

Изобретение относится к усилительным устройствам и может быть использовано в аналоговых вычислительных машинах. W о Целью изобретения является повышение помехоустойчивости. Программируемый приемник сигналов для коммутационных сред содержит с первого по двадцать третий усилительные транзисторы 1...23, с первого по шестой генераторы 24...29 тока, первый и второй накопительные конденсаторы 30 и 31, дифференциальный усилитель 32 мощности, блок 33 выборки и хранения, программирующий блок 34, с первого по десятый масштабные резисторы 35...44, первый и второй входы 45 и 46, первую и вторую шины 47 и 48 питания, первый и второй выходы 49.и 50, шину 51 опорного напряжения, шину 52 нулевого потенциала. Работа устройства основана на накоплении входного сигнала. 3 ил. Щ. Ё X ь со 1Ч СА) О Фаг. I

Фиг.2

66

67

65 69

68 70

71

72 &

it

Is.

т.л

Ш1.Л

МЛ. VW-

fe.j

Ш

я

д...л

| Операционный усилитель | 1972 |

|

SU468254A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1177827, кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1992-03-07—Публикация

1988-06-20—Подача