триггера, первым входом установки в 1 - с выходом третьего элемента И, а вторым входом установки в 1 с инверсным выходом третьего триггера подключенного прямым выходом к первому входу четвертого элемента И, входом установки в О - к выходу тре тьего вычитающего счетчика, а вторым входом установки в 1 - к выходу второго элемента И, соединенного первым входом с первым входом третьего :элемента И, прямым выходом первого триггера, вторыми входами четвертого элемента И и пятого элемента И, связйнного третьим входом с выходом делителя частоты и третьим входом четвертого элемента И, подключенного выходом к счетному входу второго вычитающего счетчика, связанного выходом с вторым управляющим входом второго счетчика, счетным входом третьего вычитающего счетчика и первым входом элемента ИЛИ, подключенного выходом к счетному входу реверсивного счетчика, а вторым входом - к счетному входу четвертого вычитающего счетчика, второму управляющему входу первого вычитающего счетчика и выходу первого вычитающего счетчика, соединенного счетным входом с выходом пятого элемента И, вторые входы второго и третьего элементов И подключены соответственно к прямому и инверсному выходам второго триггера, соединенного вторым входом установки в 1 с выходом второго блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линейный интерполятор | 1980 |

|

SU875341A1 |

| Линейный интерполятор | 1988 |

|

SU1522157A1 |

| Цифровой линейный интерполятор | 1986 |

|

SU1322233A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

| Цифровой линейный интерполятор с оценочной функцией | 1981 |

|

SU991375A1 |

| Цифровой интерполятор | 1985 |

|

SU1259217A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Цифровой линейный интерполятор | 1982 |

|

SU1065825A1 |

| Устройство для отображения информации | 1988 |

|

SU1543443A1 |

| Интерполятор | 1983 |

|

SU1089551A1 |

ЦИФРОВОЙ ИНТЕРПОЛЯТОР, содержащий реверсивный счетчик, соединенный выходом с выходом интерполятора, а управляющим входом - со знаковым выходом второро регистра, подключенного управляющим входом к управляющему входу первого регистра, входам установки первого и второго счетчиков, к входу установки в О первого триггера и выходу первого блока сравнения, соединенного первым информационным входом с выходом первого регистра, а вторым информационным входом - с выходом перW вого счетчика, связанного счетным входом с выходом делителя частоты, подключенного BxojqoM к выходу генератора импульсов, причем выход второго счетчика подключен к входу второго блока сравнения, информационный вход первого регистра подключен к первому входу интерполятора, а информационный вход второго регистра - к второму входу интерполятора, отличающийся тем, что.,с целью повьпиения точности интерполирования, в него введены третий и четвертый регистры, третий блок сравнения, второй третий и четвертьй триггеры, четыре вычитающих счетчика, пять элементов И, элемент ИЛИ и вычислительный блок, соединенный первым и вторым входами с выходами соответственно первого и второго регистров, третьим входомс выходом второго счетчика, подключенного счетнйгм входом к выходу пер-, вого элемента И, соединенного первым входом с выходом генератора импульсов, а вторьм входом - с первым выходом вычислительного блока, входом установки в 1 первого триггера, первыми управляющими входами первого и второго вычитающих счетчиков, управляющими входами третьего и четвер(Л того вычитаю1 гх счетчиков и управляющими входами третьего регистра и четвертого регистра, связанного выходом с первым входом третьего блока сравнения, подключенного первым выходом к входу установки в О второго триггера,вторым выходом - кперво-; му входу установки в 1 в торого три ггера, а вторым входом - к информацион Hor.iy входу четветрого регистра и выСП ходу третьего регистра, соединенного информационным входом с информацион;о ным входом первого вычитающего счетчика и вторым выходом вычислительного блока, связанного третьим, четвертым и пятым выходами с информационными входами соответственно второго и третьего вычитающих счетчиков и четвертого вычитающего счетчика, подключенного выходом к входу установки в четвертого триггера, связанного прямым выходом с первым входом пятого элемента И, инверсным выходом - с первым входом установки в 1 третьего

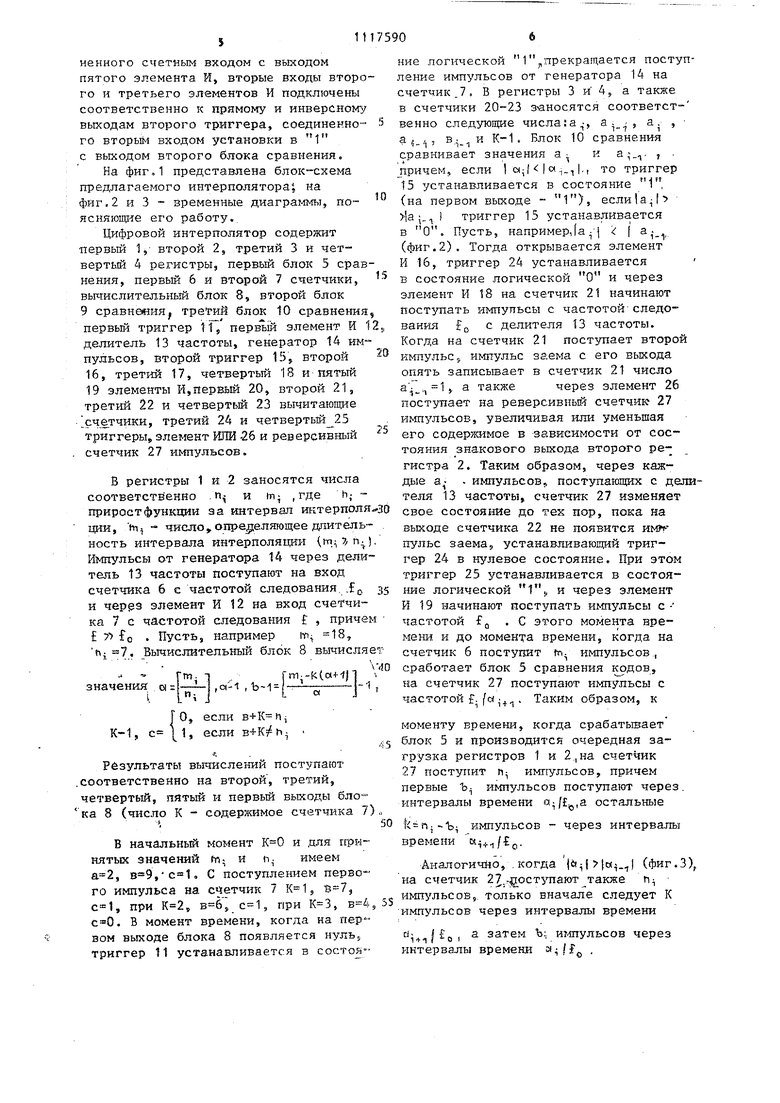

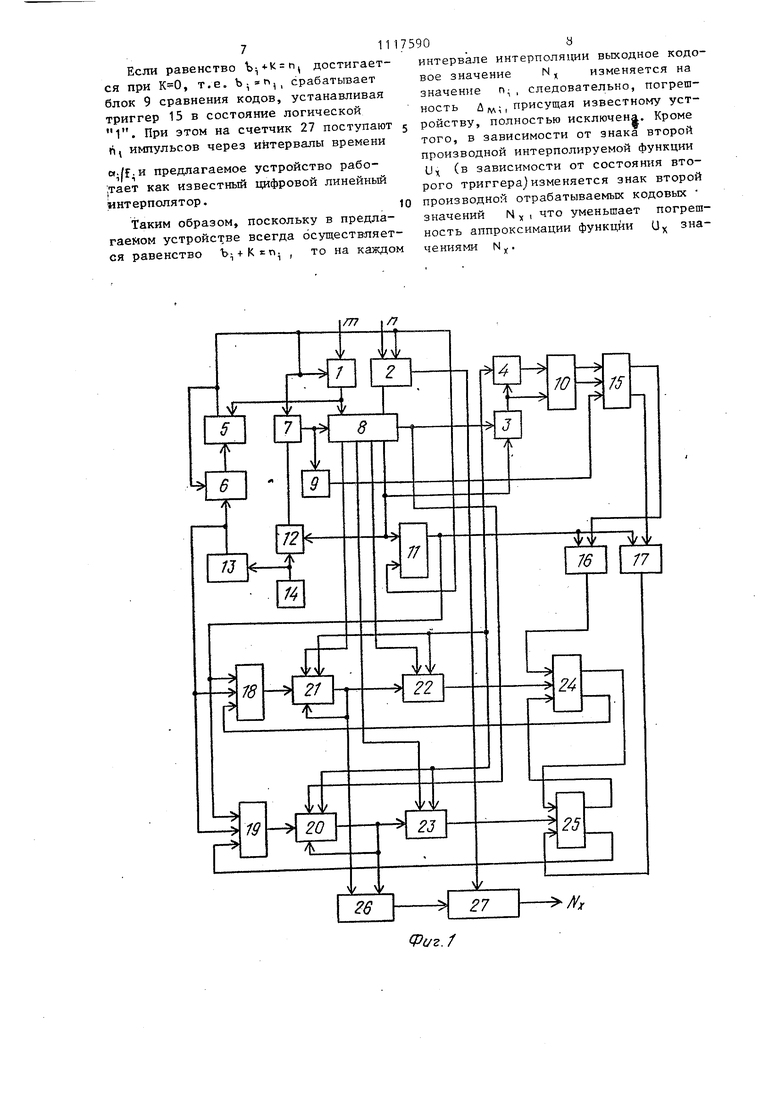

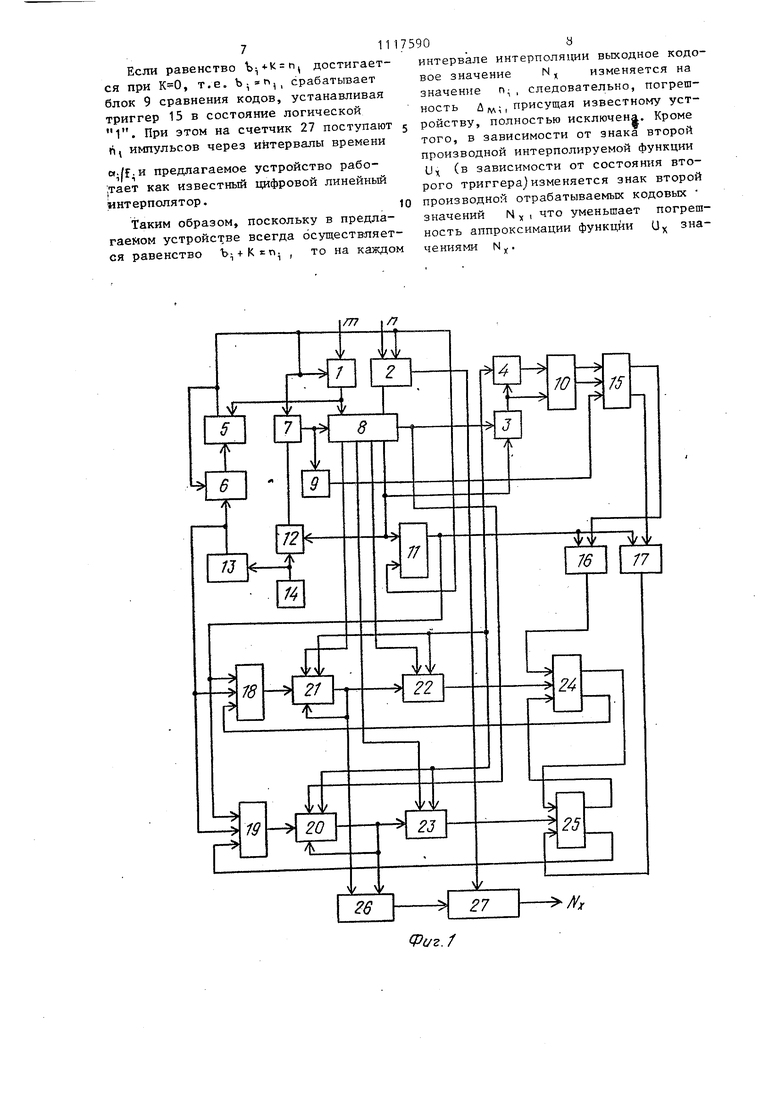

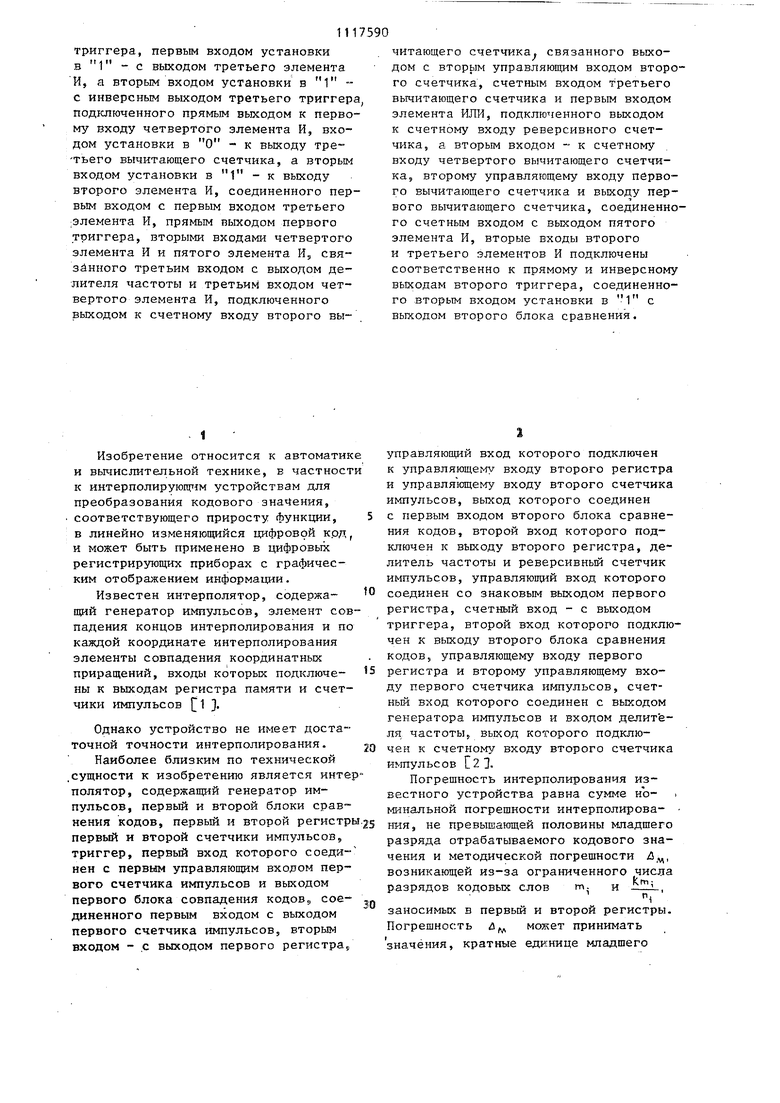

Изобретение относится к автоматик и вычислительной технике, в частност к интерполирующ м устройствам для преобразования кодового , соответствующего приросту функции, в линейно изменяюпщйся цифровой крд и может быть применено в цифровых регистрирующих приборах с графическим отображением информации. Известен интерполятор, содержащий генератор импульсов, элемент сов падения концов интерполирования и по каждой координате интерполирования элементы совпадения координатных приращений, входы которых подключены к выходам регистра памяти и счетчики импульсов 1 . Однако устройство не имеет достаточной точности интерполирования. Наиболее близким по технической .сущности к изобретению является инте полятор, содержащий генератор импульсов, первый и второй блоки сравнения кодов, первый и второй регистр первый и агорой счетчики импульсов триггер, первый вход которого соединей с первым управляющим входом первого счетчика импульсов и выходом первого блока совпадения кодов, соединенного первым входом с выходом первого счетчика импульсов, вторым входом - с выходом первого регистра управляющий вход которого подключен к управляющему входу второго регистра и управляющему входу второго счетчика импульсов, вькод которого соединен с первым входом второго блока сравнения кодов, второй вход которого подключен к выходу второго регистра, делитель частоты и реверсивный счетчик импульсов, управляющий вход которого соединен со знаковым выходом первого регистра, счетный вход - с выходом триггера, второй вход которого подключен к выходу второго блока сравнения кодов, управляющему входу первого регистра и второму управляющему входу первого счетчика импульсов, счетный вход которого соединен с выходом генератора импульсов и входом делителя, частоты выход которого подключен к счетному входу второго счетчика импульсов С2 . Погрещность интерполирования известного устройства равна сумме но- минальной погрешности интерполирования, не превышающей половины младшего разряда отрабатываемого кодового значения и методической погрещности Л,, возникающей из-за ограниченного числа разрядов кодовых слов т. м заносимых в первый и второй регистры. Погрешность л может принимать значения, кратные единице младшего разряда отрабатываемого кода, и опре Km; деляется вьфажением где - операция вьщеления целой час ти. Например, для значений п, &5j . Г 128 при , л, run L LbsJ, Увеличивая коэффициент К, можно умен шить погрешность Л Для тех же т. и п при значениях и и имеем соответственно Недостаток известного устройства заключается в том, что с возрастание коэффициента К значительно уменьшает ся быстродействие. Цель изобретения - повышение точности интерполирования путем исключе НИН погрешности Л без понижения быстродействия устройства. Поставленная цель достигается тем что в цифровой интерполятор, содержа щий реверсивный счетчик, соединенный выходом с выходом интерполятора, а у равляющим входом - со знаковым выходом второго регистра, подключенного управляющим входом к управляющему вх ду первого регистра, входам установки первого и второго счетчиков, входу установки в О первого триггера и выходу первого блока сравнения, соединенного первым информационным входом с выходом первого регистра, а вторым информационным входом - с в ходом первого счетчика, связанного счетным входом с выходом делителя частоты, подключенного входом к выходу генератора импульсов, причем вы ход второго счетчика.подключен к входу второго блока сравнения, инфор мационный вход первого регистра подключен к первому входу интерполятора а информационный вход второго регист ра - к второму входу интерполятора, введены третий и четвертьй регистры, третий блок сравнения, второй, трети и четвертьй триггеры, четыре вычитаю щих счетчика, пять элементов И, элемент ИЛИ и вычислительный блок, соединенный первым и вторым входами с выходами соответственно первого и вт рого регистров, третьим входом - с выходом второго счетчика, подключенкого счетным входом к выходу первого элемента И, соединенного первым входом с выходом генератора импульс.ов. а вторым входом - с первым выходом вычислительного блока, входом установки в 1 первого триггера, первь ш управляющими входами первого и второго вычитaюD иx счетчиков, управляющими входаьш третьего и четвертого вычитаю11Ц1х счетчиков и управляющими входами третьего регистра и четвертого регистра, связанного выходом с первым входом третьего блока сравнения, подключенного первым выходом к входу установки в О второго триггера. вторым выходом - к первому входу установки в 1 второго триггера, а вторым входом - к информационному входу четвертого регистра и выходу третьего регистра, соединенного информационным входом с информационным входом первого вычитающего счетчика и вторым выходом вычислительного блока, связанного третьим, четвертым и пятьп выходами с информационными входами соответственно второго и третьего вычитающих счетчиков и четвертого вычитающего счетчика, подключенного выходом к входу установки в О четвертого Т15иггера, связанного пр5шым выходом с первым входом пятого элемента И, инверсным выходом - с первым входом установки в 1 третьего триггера, первым входом установки в 1 - с выходом третьего элемента И, а вторым входом установки в 1 с инверсным выходом третьего триггера, подключенного прямым выходом к первому входу четвертого элемента И, входом установки в О - к выходу третьего вычитающего счетчика, а вторым входом установки в 1 - к выходу второго элемента И, соединенного пер вым входом с первым входом третьего элемента И, прямым выходом первого триггера, вторыми входами четвертого элемента И и пятого элемента И, связанного третьим входом с выходом делителя частоты и третьим входом четвертого элемента И, подключенного выходом к счетному входу второго вычитающего счетчика, связанного выходом с вторым управляющим входом второго счетчика, счетным входом третьего вычитающего счетчика и первым входом элемента ИЛИ подключенного выходом к счетному входу реверсивного счетчика, а вторым входом - к счетному входу четвертого вычитающего счетчика, второму управляющему входу первого вычитающего счетчика и выходу первого вычитающего счетчика, соединенного счетным входом с выходом пятого элемента И, вторые входы втор го и третьего элементов И подключены соответственно к прямому и инверсному выходам второго триггера, соединенно го вторьм входом установки в 1 с выходом второго блока сравнения. На фиг.1 представлена блок-схема предлагаемого интерполятора, на фиг,2 и 3 - временные диаграммы, поясняющее его работу.. Цифровой интерполятор содержит первый 1, второй 2, третий 3 и четвертый 4 регистры, первый блок 5 срав нения, первый 6 и второй 7 счетчики, вычислительный блок 8, второй блок 9 сравнеиия третий блок 10 сравнени первьй триггер И, элемент И делитель 13 частоты, генератор 14 им пульсов, второй триггер 15j второй 16, третий 17, четвертый 18 и пятый 19 элементы И,первый 20, второй 21, третий 22 и четвертьй 23 вычитающие счетчики, третий 24 и четвертый 25 триггеры, элемент ИЛИ -26 и реверсивный счетчик 27 импульсов. В регистры 1 и 2 заносятся числа соответственно .п и (я- , где h прирост функции за интервал иктерпол цин, fti, - число, определяющее длитель ность интервала интерполяции (щ У/ п Импульсы от генератора 14 через дели таль t3 частоты поступают на вход счетчика 6 е частотой следования, ,-E(j и черэз элемент И 12 на вход счетчика 7 с частотой следования t , приче fo . Пусть, например iti 18, ti; 7. Вычислительный блок 8 вычисля m--K(a-Hj Гт. т , :,,,-,i.b-iHзначенияI О, если К-1, с М, если ,j результаты вычислений поступают .соответственно на второй, третий, четвертый, пятый и первый выходы бло ка 8 (число К - содержимое счетчика 7 В начальный момент и для принятых значений т и TI. имеем , ,. С поступлением первого импульса на счетчик 7 , , при , , при , . В момент времени, когда на пер вом выходе блока 8 появляется нуль,, триггер 11 устанавливается в состоя т .1 Г прекращается поступление импульсов от генератора 14 на счетчик.7. В регистры 3 и 4, а также в счетчики 20-23 з аносятся соответственно следующие числа: а - а , а. Блок 10 сравнения в.,,. и К-1 к а,. , . сравнивает значения а причем, если I «; I « .,-11., то триггер 15 устанавливается в состояние 1, (на первом выходе 1), если|а 1 1а;. 1 триггер 15 устанавливается в О. Пусть, например, (а 1 а. (фиг.2). Тогда открывается элемент И 16, триггер 24 устанавливается в состояние логической О и через элемент И 18 на счетчик 21 начинают поступать импульсы с частотойследования о с делителя 13 частоты. Когда на счетчик 21 поступает второй им-пульс импульс заема с его выхода опять записывает в счетчик 21 число 1i 3 также через элемент 26 поступает на реверсивньй счетчик 27 импульсов, увеличивая или уменьшая его содержимое в зависимости от состояния знакового выхода второго регистра 2. Таким образом, через каждые а- импульсов, поступающих с делителя 13 частоты, счетчик 27 изменяет свое состояние до ч-ек пор, пока на выходе счетчика 22 не появится имзг пульс заема, устанавливающий триггер 24 в нулевое состояние. При этом триггер 25 устанавливается в состояние логической 1,, и через элемент И 19 начинают поступать импульсы счастотой f. С этого момента времени и до момента времени, когда на счетчик 6 поступит tn импульсов,, сработает блок 5 сравнения кодов, на счетчик 27 поступают кмпупъсы с частотой f. fa . . Таким образом, к моменту времени, когда срабатывает блок 5 и производится очередная загрузка регистров 1 и 2,,на счетчик 27 поступит п импульсов, причем первые Ъ;| импульсов постзтают через. интервалы времени ,а остальные Hj-b импульсов - через интервалы i+i/- oвремени К; Аиэлогичйо, , когда .;-) (Фиг.З), на счетчик 27.гД ост5Т1ают также п, „ п -льсов,, только вначале следует К импульсов через интервалы времени -i-fil oi затем Ъ:, ш-шульсов через и; интервалы времени . Если равенство Ъ:|+ п, достигается при К-0, т.е. Ь.п, срабатывает блок 9 сравнения кодов, устанавливая триггер 15 в состояние логической 1. При этом на счетчик 27 поступают п импульсов через ийтервалы времени с(./.и предлагаемое устройство рабо;тает как известный цифровой линейный интерполятор. Таким образом, поскольку в предлагаемом устройстве всегда осуществляет ся равенство Ъ- + Кгп. , то на каждо

1/7

(Уг. / интервале интерполяции выходное кодовое значение N изменяется на значение п- , следовательно, погрешность д , присущая известному устройству, полностью исключена. Кроме того, в зависимости от знака второй производной интерполируемой функции Ux (в зависимости от состояния второго триггера)изменяется знак второй производной отрабатываемых кодовых значений N , что уменьшает погрешность аппроксимации функции чениями N V

Л

Xt4

1 А,АААААДЛААДААДЛАААД.

Фиг.З

Фе/г.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ЦИФРОВОЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 0 |

|

SU344415A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой линейный интерполятор | 1980 |

|

SU875341A1 |

| G, 05 В .19/18, 1981. | |||

Авторы

Даты

1984-10-07—Публикация

1983-03-04—Подача