Изобретение относится к автоматике и вычислительной технике и может быть использовано в различных системах программного управления и управляющих машин, в частности в устройствах отображения графической информации на экране электроннолуче- ,вой трубки (ЭЛТ) или на графопостроителе .

Цель изобретения - повышение

быстродействия и упрощение устройства.

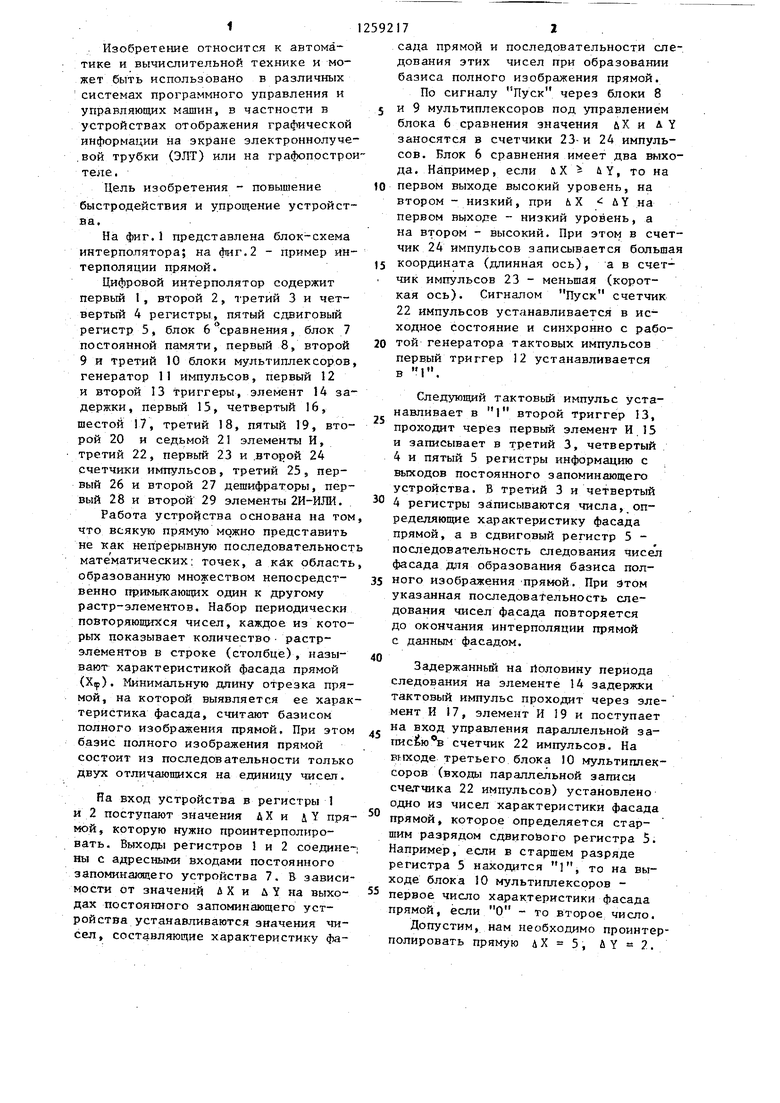

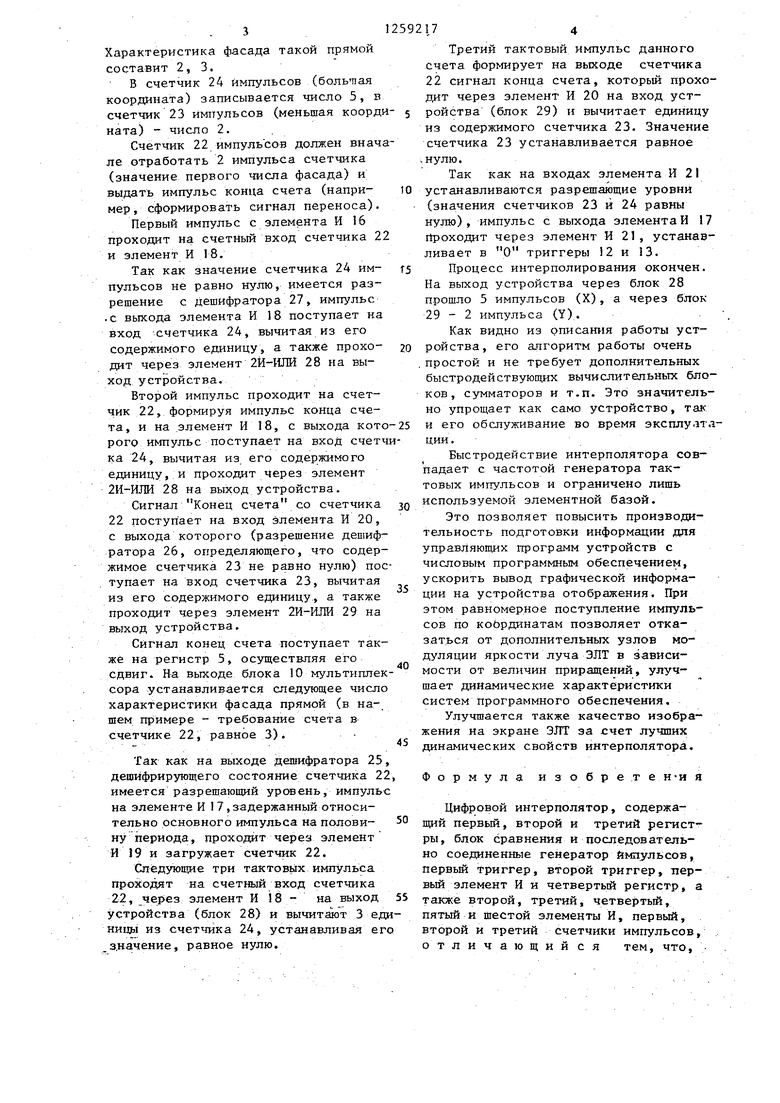

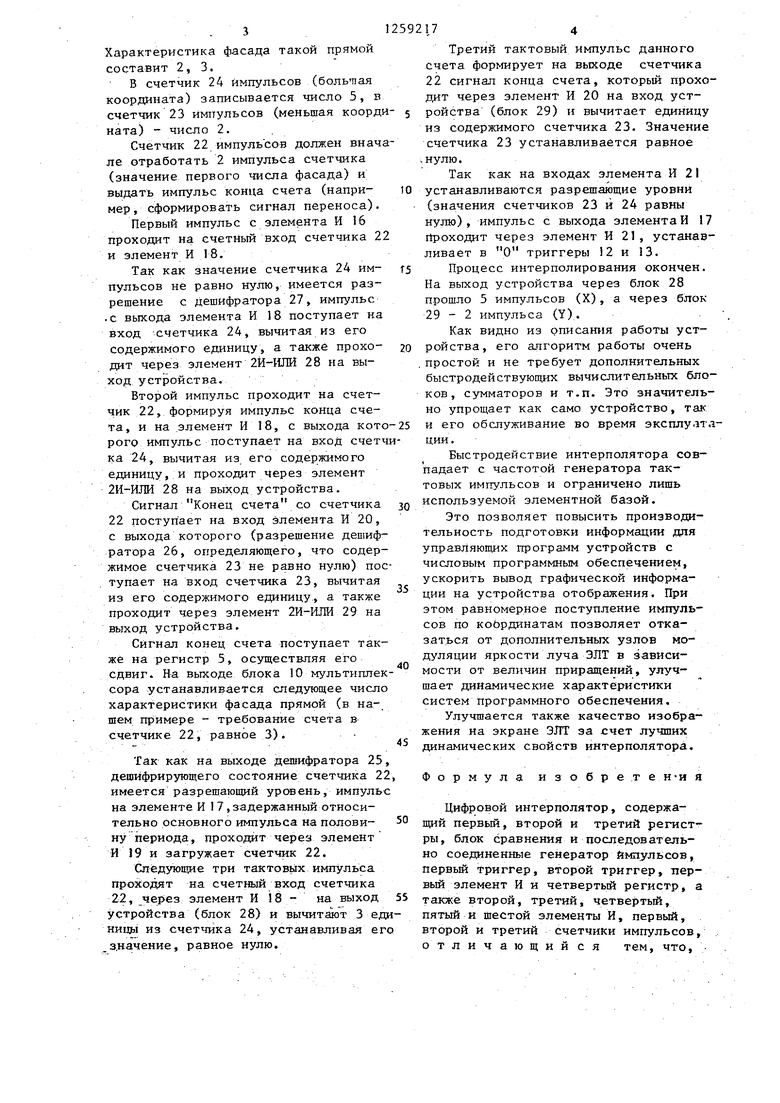

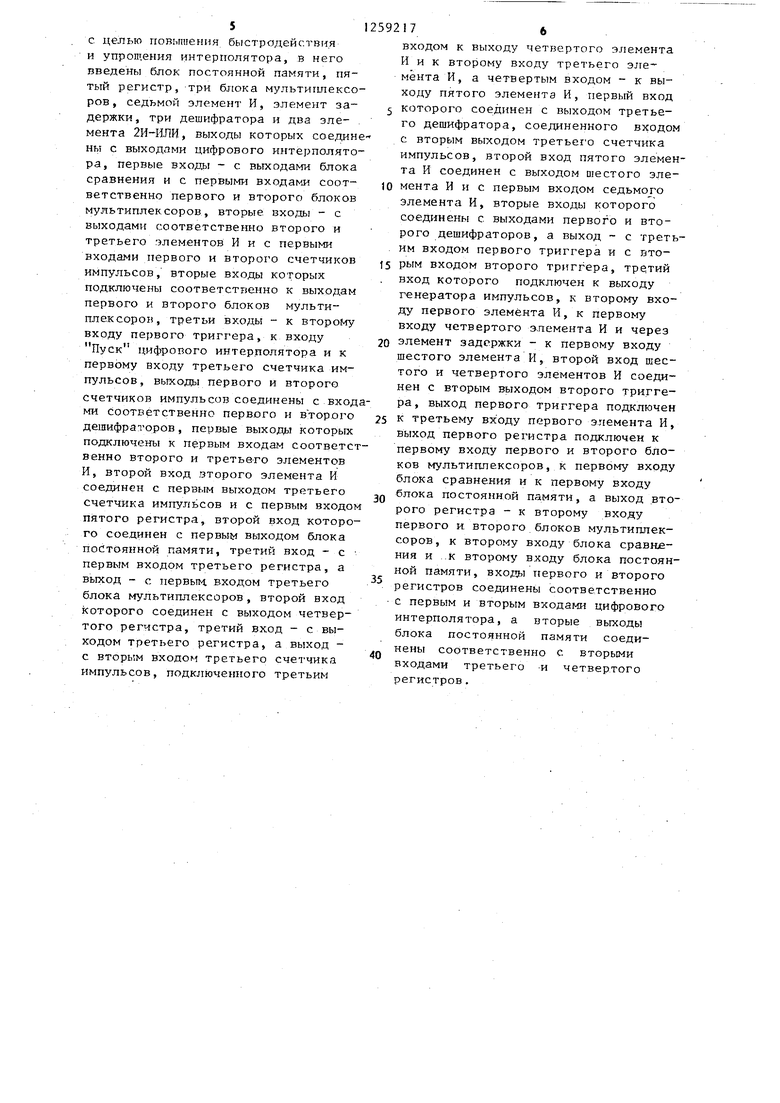

На фиг.1 представлена блок-схема интерполятора; на фиг.2 - пример йн- терполяции прямой.

Цифровой интерполятор содержит первый 1, второй 2, третий 3 и четвертый 4 регистры, пятый сдвиговый регистр 5, блок 6 сравнения, блок 7 постоянной памяти, первый 8, второй 9 и третий 10 блоки мультиплексоров, генератор П импульсов, первый 12 и второй 13 триггеры, элемент 14 задержки, первый 15, четвертый 16, шестой , третий 18, пятый 19, второй 20 и седьмой 21 элементы И, третий 22, первый 23 и .второй 24 счетчики импульсов, третий 25, первый 26 и второй 27 дешифраторы, первый 28 и второй 29 элементы 2И-ИЛИ.

Работа устройства основана на том что всякую прямую можно представить не как непрерывную последовательност мате матических; точек, а как область образованную множеством непосредст- венно примыкающих один к другому растр-элементов. Набор периодически повторяющихся чисел, каждое из которых показывает количество растр- элементов в строке (столбце), назы- вают характеристикой фасада прямой (Х(р). Минимальную длину отрезка прямой, на которой выявляется ее характеристика фасада, считают базисом полного изображения прямой. При этом базис полного изображения прямой состоит из последовательности только двух отличающихся на единицу чисел.

На вход устройства в регистры 1 и 2 поступают значения ДХ и 4Y пря- мой, которую нужно проинтерполиро- вать. Выходы регистров 1 и 2 соедине ны с адресными входами постоянного запоминакяцего устройства 7. В зависимости от значений йХ и д Y на выхо- дах постоянного запоминающего устройства устанавливаются значения чисел, составляющие характеристику фа5

20 30

2592172

сада прямой и последовательности следования этих чисел при образовании базиса полного изображения прямой. По сигналу Пуск через блоки 8 и 9 мультиплексоров под управлением блока 6 сравнения значения йХ и А Y заносятся в счетчики 23-и 24 импульсов. Блок 6 сравнения имеет два выхода. Например, если аХ uY, то на первом выходе высокий уровень, на втором - низкий, при &Х AY на первом выходе - низкий уровень, а на втором - высокий. При этом в счетчик 24 импульсов записывается большая координата (длинная ось), а в счетчик импульсов 23 - меньшая (короткая ось). Сигналом Пуск счетчик 22 импульсов устанавливается в исходное состояние и синхронно с работой генератора тактовых импульсов первый триггер 2 устанавливается в

1.

Следующий тактовьй импульс устанавливает в 1 второй триггер 13, проходит через первый элемент И 15 и записывает в третий 3, четвертый 4 и пятый 5 регистры информацию с выходов постоянного запоминающего устройства. В третий 3 и четвертый 4 регистры записываются числа, определяющие характеристику фасада прямой, а в сдвиговый регистр 5 - последовательность следования чисел фасада для образования базиса полного изображения прямой. При этом указанная последовательность следования чисел фасада повторяется до окончания интерполяции прямой с данным фасадом.

Задержанный на йоловину периода следования на элементе 14 задержки тактовьгй импульс проходит через элемент И 17, элемент И 19 и поступает на вход управления параллельной за- писЙю в счетчик 22 импульсор. На виходе третьего блока 10 мультиплексоров (входы параллельной записи сче.тчика 22 импульсов) установлено одно из чисел характеристики фасада прямой, которое определяется стар- щим разрядом сдвиго&ого регистра 5. Например, если в старщем разряде регистра 5 находится 1, то на выходе блока 10 мультиплексоров - первое число характеристики фасада прямой, если О - то второе число.

Допустим, нам необходимо проинте полировать прямую АХ 5, UY 2.

арактеристика фасада такой прямой составит 2, 3.

В счетчик 24 Импульсов (боль пая координата) записывается число 5, в счетчик 23 импульсов (меньшая коорди- 5 ната) - число 2.

Счетчик 22 импульсов должен вначале отработать 2 импульса счетчика (значение первого числа фасада) и выдать импульс конца счета (напри- 10 мер, сформировать сигнал переноса).

Первый импульс с элемента И 16 проходит на счетный вход счетчика 22 и элемент И 18.

Так как значение счетчика 24 им- Г5 пульсов не равно нулю, имеется разрешение с дешифратора 27, импульс с выхода элемента И 18 поступает на вход счетчика 24, вычитая из его содержимого единицу, а также прохо- 20 дит через элемент 2Й-ИЛИ 28 на выход устройства.

Второй импульс проходит на счетчик 22, формируя импульс конца счета, и на элемент И 18, с выхода кото-25 рого импульс поступает на вход счетчи- ка 24, вычитая из его содержимого единицу, и проходит через элемент 2И-ИЛИ 28 на выход устройства.

Сигнал Конец счета со счетчика зо 22 поступает на вход элемента И 20, с выхода которого (разрешение дешифратора 26, определяющего, что содержимое счетчика 23 не равно нулю) поступает на вход счетчика 23, вычитая из его содержимого единицу, а также проходит через элемент 2И-И1Ш 29 на выход устройства.

Сигнал конец счета поступает также на регистр 5, осуществляя его сдвиг. На выходе блока 10 мультиплексора устанавливается следующее число характеристики фасада прямой (в нашем примере - требование счета в

счетчике 22, равное 3).

-45

Так как на выходе дешифратора 25, дешифрирующего состояние счетчика 22, имеется разрешающий урсжень, импульс на элементе И 1 7 , задержанный относительно основного импульса на полови- 50 ну периода, проходит через элемент И 19 и загружает счетхшк 22.

Сл1Едующие три тактовых импульса проводят на счетный вход счетчика 22, через элемент И 18 - на выход 55 стройства (блок 28) и вычитают 3 еди- иць из счетчика 24, устанавливая его з.начение, равное нулю.

35

40

5

10

Г5 0

5

о

5

0

5

0

Третий тактовый импульс данного счета формирует на вькоде счетчика 22 сигнал конца счета, который проходит через элемент И 20 на вход устройства (блок 29) и вычитает единицу из содержимого счетчика 23. Значение счетчика 23 устанавливается равное .нулю.

Так как на входах элемента И 2I устанавливаются разрешающие уровни (значения счетчиков 23 и 24 равны нулю), импульс с выхода элемента И 17 йроходит через элемент И 21, устанавливает в О триггеры 12 и 13.

Процесс интерполирования окончен. На выход устройства через блок 28 прошло 5 импульсов (X), а через блок 29 - 2 импульса (Y).

Как видно из описания работы устройства, его алгоритм работы очень , простой и не требует дополнительных быстродействующих вычислительных блоков, сумматоров и т.п. Это значительно упрощает как само устройство, так и его обслуживание во время эксплу.этл- ции.

Быстродействие интерполятора совпадает с частотой генератора тактовых импульсов и ограничено лишь используемой элементной базой.

Это позволяет повысить производительность подготовки информацш для управляющих программ устройств с числовым программным обеспечением, ускорить вывод графической информации на устройства отображения. При этом равномерное поступление импульсов по кобрдинатам позволяет отказаться от дополнительных узлов модуляции яркости луча ЭЛТ в зависимости от величин приращений, улучшает динамические характеристики систем программного обеспечения.

Улучшается также качество изображения на экране ЭЛТ за счет лучших да1намических свойств интерполятора.

Формула изобретен ия

Цифровой интерполятор, содержащий первый, второй и третий регистры, блок сравнения и последовательно соединенные генератор импульсов, первый триггер, второй триггер первый элемент И и четвертый регистр, а также второй, третий, четвертый, пятый и шестой элементы И, первый, второй и третий счетчики импульсов, отличающий ся тем, что,

5

с целью повышения быстродействия и упрощения интерполятора, в него введены блок постоянной памяти, пятый регистр, три блока мультиплексоров, седьмой элемент И, элемент за- держки, три дешифратора и два эле- мента 2И-И,ПИ, выходы которых соедин ны с выходами цифрового интерполятора, первые входы - с выходами блока сравнения и с первыми входами соот- ветственно первого и второго блоков мультиплексоров, вторые входы - с выходами соответственно второго и третьего элементов И и с первыми входами первого и второго счетчиков импульсов, вторые входы которых подключены соответственно к выходам первого и второго блоков мультиплексоров, третьи входы - к второму входу первого триггера, к входу Пуск цифрового интерполятора и к первому входу третьего счетчика импульсов, выходы первого и второго счетчиков импульсов соединены с входми соответственно первого и второго дешифраторов, первые выходы которых подключены к первым входам соответсвенно второго и третье-го элементс1В И, второй вход второго элемента И соединен с первым выходом третьего

счетчика импульсов и с первым входом пятого регистра, второй вход которого соединен с первым выходом блока постоянной памяти, третий вход - с первым входом третьего регистра, а вьрсод - с первый входом третьего блока мультиплексоров, второй вход которого соединен с выходом четвертого регистра, третий вход - с выходом третьего регистра, а выход - с вторым входом третьего счетчика импульсов, подключенного третьим

JQ 0 5

0

5

0

176

входом к выходу четвертого элемента И и к второму входу третьего элемента И, а четвертым входом - к выходу пятого элемента И, первый вход которого соединен с выходом третьего дешифратора, соединенного входом с вторым выходом третьег о счетчика импульсов, второй вход пятого элемента И соединен с выходом aiecroro элемента И и с первым входом седьмого элемента И, вторые входы которого соединены с выходами первого и второго дешифраторов, а выход с третьим входом первого триггера и с вторым входом второго триггера, третий вход которого подключен к выходу генератора импульсов, к второму входу первого элемента И, к первому входу четвертого элемента И и через элемент задержки - к первому входу шестого элемента И, второй вход шестого и четвертого элементов И соединен с вторым выходом второго триггера, выход первого триггера подключен к третьему вх оду первого элемента И, выход первого регистра подключен к первому входу первого и второго блоков мультиплексоров, к первому входу блока сравнения и к первому входу блока постоянной памяти, а выход второго регистра - к второму входу первого и второго блоков мультиплексоров, к второму входу блока сравнения и -К второму входу блока постоянной памяти, входы первого и второго регистров соединены соответственно с первым и вторым входами цифрового интерполятора, а вторые вьпсоды блока постоянной памяти соединены соответственно с вторыми входами третьего -и четвертого регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор | 1985 |

|

SU1413600A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для программного управления | 1986 |

|

SU1423981A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

| Устройство для ввода информации | 1981 |

|

SU1005019A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1988 |

|

SU1606991A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1989 |

|

SU1626251A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1441399A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах программного управления и управляющих машин, в частности в устройст: вах отобргьжения графической информа- . ции на экране электроннолучевой трубки или на графопостроителе. Цель изобретения - повьш1ение быстродействия и упрощение устройства. Цифровой интерполятор содержит пять регистров, блок сравнения, блок постоянной памяти, три блока мультиплексоров , генератор импульсов, два триггера, элемент задержки, элементы И, 2И-ИЛИ, три счетчика и два дешифратора. Данный цифровой интерполятор позволяет повысить производитель- ность подготовки информации для управляющих программ устройств с числовым программным обеспечением, ускорить вывод графической информ -- ции на устройства отображения. При этом равномерное поступление импульсов по координатам позволяет отказаться от дополнительных узлов модуляции яркости луча ЭЛТ в зависимости от величин приращений, улучшает динамические характеристики систем программного обеспечения. 2 ил. (Л С

| Цифровой линейный интерполятор | 1976 |

|

SU579599A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Фролов с.А | |||

| Автоматизация процесса графического решения задач | |||

| Минск.: Высшая школа, 1980, с.96- 100 | |||

| Цифровой интерполятор | 1983 |

|

SU1117590A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-09-23—Публикация

1985-04-11—Подача