Изобретение относится к автоматике и вычислительной технике,в частности к интерполирующим устройствам для преобразования кодового значения, соответствующего приросту функции, в линейно изменяющийся цифровой код, и может быть применено в цифровых регистрирующих приборах с графическим отображением информации.

Цель изобретения - повышение быст- родействия интерполятора при сохранении точности,

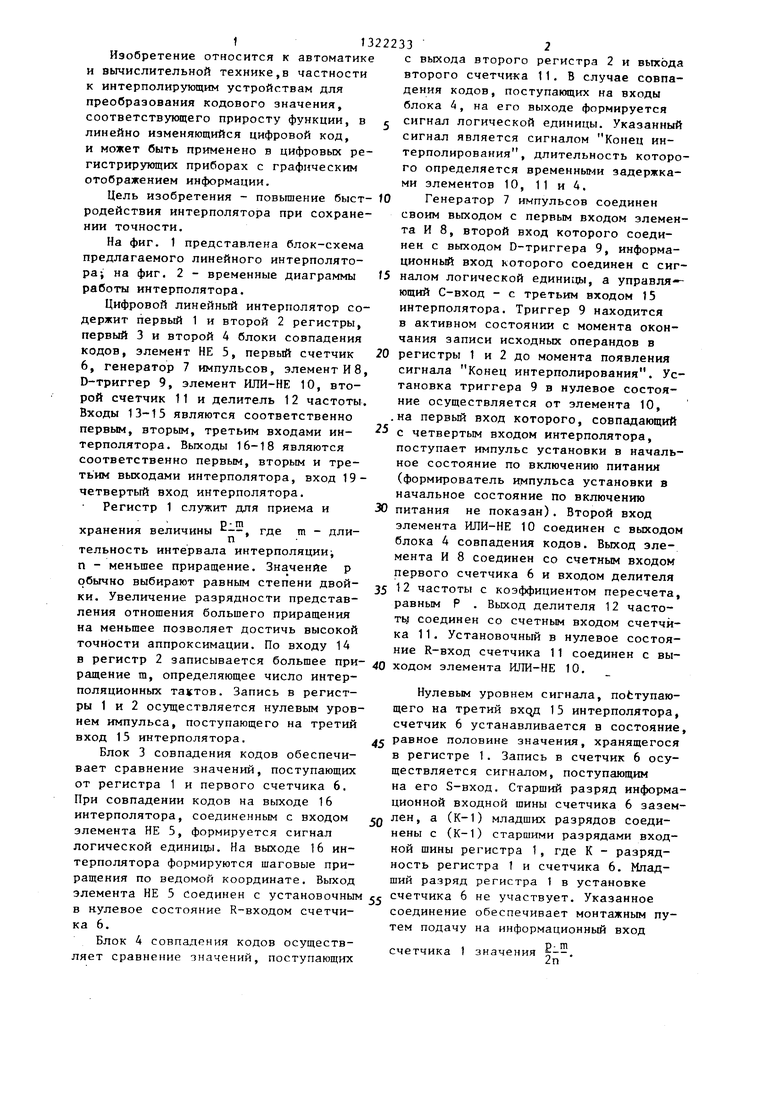

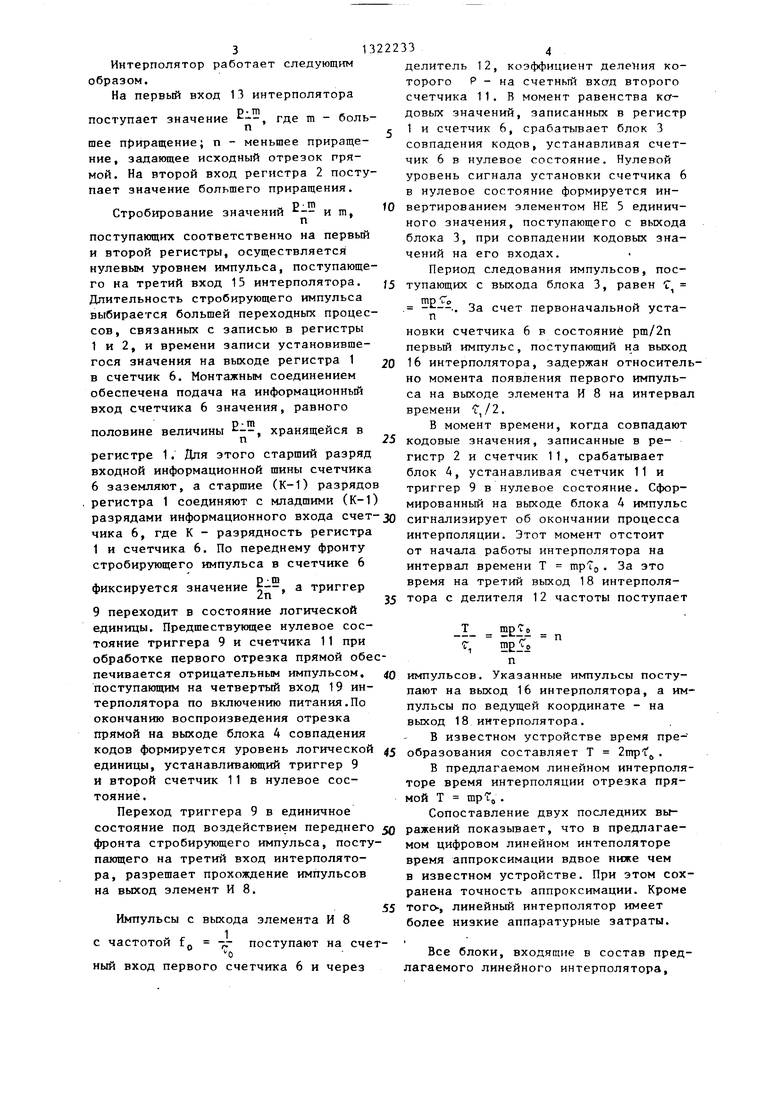

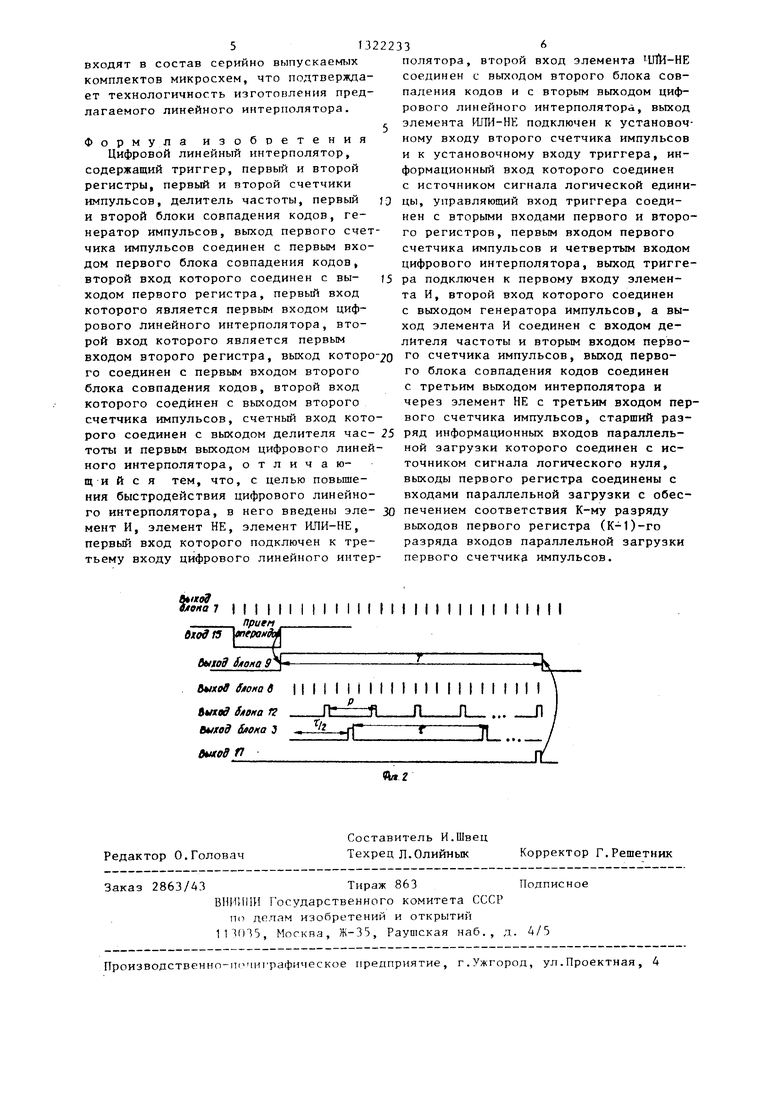

На фиг, 1 представлена блок-схема предлагаемого линейного интерполятора; на фиг, 2 - временные диаграммы работы интерполятора.

Цифровой линейный интерполятор содержит первый 1 и второй 2 регистры, первый 3 и второй 4 блоки совпадения кодов, элемент НЕ 5, первый счетчик 6, генератор 7 импульсов, элемент И 8, D-триггер 9, элемент ИЛИ-НЕ 10, второй счетчик 11 и делитель 12 частоты. Входы 13-15 являются соответственно первым, вторым, третьим входами интерполятора. Выходы 16-18 являются соответственно первым, вторым и третьим выходами интерполятора, вход 19- четвертый вход интерполятора,

Регистр 1 служит для приема и

хранения величины

п

где m - длиэлемента ИЛИ-НЕ 10 соединен с выход блока 4 совпадения кодов. Выход эле мента И 8 соединен со счетным входо первого счетчика 6 и входом делител 12 частоты с коэффициентом пересчет равным Р , Выход делителя 12 часто ты соединен со счетным входом счетч ка 11, Установочный в нулевое состо ние R-вход счетчика 11 соединен с в

35

тельность интервала интерполяции п - меньшее приращение, Зна ченйе р обычно выбирают равным степени двойки. Увеличение разрядности представления отношения большего приращения на меньшее позволяет достичь высокой точности аппроксимации. По входу 14

в регистр 2 записывается большее при- о ходом элемента ИЛИ-НЕ 10, ращение т, определяющее число интерполяционных тактов. Запись в регистры 1 и 2 осуществляется нулевым уровнем импульса, поступающего на третий вход 15 интерполятора.

Блок 3 совпадения кодов обеспечивает сравнение значений, поступающих от регистра 1 и первого счетчика 6, При совпадении кодов на выходе 16 интерполятора, соединенным с входом элемента НЕ 5, формируется сигнал логической единицы. На выходе 16 интерполятора формируются шаговые приращения по ведомой координате. Выход

Нулевым уровнем сигнала, поётупа щего на третий Bxqfl 15 интерполятор счетчик 6 устанавливается в состоян с равное половине значения, хранящего в регистре 1, Запись в счетчик 6 ос ществляется сигналом, поступающим на его S-вход, Старший разряд инфор ционной входной шины счетчика 6 заз лен, а (К-1) младших разрядов соеди нены с (К-1) старшими разрядами вхо ной шины регистра 1, где К - разряд ность регистра 1 и счетчика 6. Мпад ший разряд регистра 1 в установке

50

элемента НЕ 3 Соединен с установочным 55 счетчика 6 не участвует. Указанное

в нулевое состояние R-входом счетчика 6.

Блок 4 совпадения кодов осуществляет сравнение значений, поступающих

соединение обеспечивает монтажным п тем подачу на информационный вход

счетчика 1 значения

2п

0

5

0

с выхода второго регистра 2 и выхода второго счетчика 11, В случае совпадения кодов, поступающих на входы блока 4, на его выходе формируется сигнал логической единицы. Указанный сигнал является сигналом Конец интерполирования, длительность которого определяется временньми задержками элементов 10, 11 и 4,

Генератор 7 импульсов соединен своим выходом с первым входом элемента И 8, второй вход которого соединен с выходом D-триггера 9, информационный вход которого соединен с сигналом логической единицы, а управля-- ющий С-вход - с третьим входом 15 интерполятора. Триггер 9 находится в активном состоянии с момента окончания записи исходных операндов в регистры 1 и 2 до момента появления сигнала Конец интерполирования. Установка триггера 9 в нулевое состояние осуществляется от элемента 10, на первый вход которого, совпадающий с четвертьм входом интерполятора, поступает импульс установки в начальное состояние по включению питания (формирователь импульса установки в начальное состояние по включению 0 питания не показан), Второй вход

элемента ИЛИ-НЕ 10 соединен с выходом блока 4 совпадения кодов. Выход элемента И 8 соединен со счетным входом первого счетчика 6 и входом делителя 12 частоты с коэффициентом пересчета, равным Р , Выход делителя 12 частоты соединен со счетным входом счетчика 11, Установочный в нулевое состояние R-вход счетчика 11 соединен с вы5

5

о ходом элемента ИЛИ-НЕ 10,

ходом элемента ИЛИ-НЕ 10,

Нулевым уровнем сигнала, поётупаю- щего на третий Bxqfl 15 интерполятора, счетчик 6 устанавливается в состояние, равное половине значения, хранящегося в регистре 1, Запись в счетчик 6 осуществляется сигналом, поступающим на его S-вход, Старший разряд информационной входной шины счетчика 6 заземлен, а (К-1) младших разрядов соединены с (К-1) старшими разрядами входной шины регистра 1, где К - разрядность регистра 1 и счетчика 6. Мпад- ший разряд регистра 1 в установке

счетчика 6 не участвует. Указанное

соединение обеспечивает монтажным путем подачу на информационный вход

счетчика 1 значения

2п

Интерполятор работает следующим образом.

На первый вход 13 интерполятора

р. m

поступает значение --, где m - больп

шее приращение; п - меньшее приращение, задающее исходный отрезок прямой. На второй вход регистра 2 поступает значение больщего приращения.

jj

Р П

Стробирование значений - и

т,

поступающих соответственно на первый и второй регистры, осуществляется нулевым уровнем импульса, поступающего на третий вход 15 интерполятора. Длительность стробирующего импульса выбирается большей переходных процессов, связанных с записью в регистры 1 и 2, и времени записи установившегося значения на выходе регистра 1 в счетчик 6. Монтажным соединением обеспечена подача на информационный вход счетчика 6 значения, равного

р-тп

половине величины --, хранящейся в

п

регистре 1. Для этого старщий разряд входной информационной щины счетчика 6 заземляют, а старщие (К-1) разрядов регистра 1 соединяют с младшими (К-1)

jj

разрядами информационного входа счет-зо сигнализирует об окончании процесса

чика 6, где К - разрядность регистра 1 и счетчика 6. По переднему фронту стробирующего импульса в счетчике 6

интерполяции. Этот момент отстоит от начала работы интерполятора на интервал времени Т трТ;, . За это время на третий выход 18 интерполя- 35 тора с делителя 12 частоты поступает

g -m

m

фиксируется значение --, а триггер

9 переходит в состояние логической единицы. Предшествующее нулевое состояние триггера 9 и счетчика 11 при обработке первого отрезка прямой обепечивается отрицательным импульсом, поступающим на четвертый вход 19 интерполятора по включению питания.По окончанию воспроизведения отрезка прямой на выходе блока 4 совпадения кодов формируется уровень логической единицы, устанавливающий триггер 9 и второй счетчик 11 в нулевое состояние.

Переход триггера 9 в единичное

состояние под воздействием переднего 50 ражений показывает, что в предлагае- фронта стробирующего импульса, посту- мом цифровом линейном интеполяторе пающего на третий вход интерполятовремя аппроксимации вдвое ниже чем в известном устройстве. При этом сох ранена точность аппроксимации. Кроме 55 того, линейный интерполятор имеет более низкие аппаратурные затраты.

ра, разрешает прохождение импульсов на выход элемент И 8.

Импульсы с выхода элемента И 8

с частотой

,-i

55

поступают на счетный вход первого счетчика 6 и через

22334

делитель 12, коэффициент деле ния которого Р - на счетный вход второго счетчика 11, В момент равенства кадовьгх значений, записанных в регистр 5 1 и счетчик 6, срабатывает блок 3 совпадения кодов, устанавливая счетчик 6 в нулевое состояние. Нулевой уровень сигнала установки счетчика 6 в нулевое состояние формируется ин- 10 вертированием элементом НЕ 5 единичного значения, поступающего с выхода блока 3, при совпадении кодовых значений на его входах.

Период следования импульсов, пос15 тупающих с выхода блока 3, равен Т,

. - ---.. За счет первоначальной устап

новки счетчика 6 в состояние pm/2n первый импульс, поступающий на выход 16 интерполятора, задержан относительно момента появления первого импульса на выходе элемента И 8 на интервал времени Г,/2.

В момент времени, когда совпадают кодовые значения, записанные в регистр 2 и счетчик 11, срабатывает блок 4, устанавливая счетчик 11 и триггер 9 в нулевое состояние. Сформированный на выходе блока 4 импульс

интерполяции. Этот момент отстоит от начала работы интерполятора на интервал времени Т трТ;, . За это время на третий выход 18 интерполя- тора с делителя 12 частоты поступает

Т mg5

Г SEb

п

импульсов. Указанные импульсы поступают на выход 16 интерполятора, а импульсы по ведущей координате - на выход 18 интерполятора.

В известном устройстве время пре- образования составляет Т .

В предлагаемом линейном интерполяторе время интерполяции отрезка прямой Т трТ, .

Сопоставление двух последних выражений показывает, что в предлагае- мом цифровом линейном интеполяторе

время аппроксимации вдвое ниже чем в известном устройстве. При этом сохранена точность аппроксимации. Кроме того, линейный интерполятор имеет более низкие аппаратурные затраты.

Все блоки, входящие в состав предлагаемого линейного интерполятора.

51322233

дят в состав серийно выпускаемых плектов микросхем, что подтверждатехнологичность изготовления предаемого линейного интерполятора.

по с п эл н и с ц н г сч ц ра т с х л

Форм у л а изобретения

Цифровой линейный интерполятор, содержащий триггер, первый и второй регистры, первый и второй счетчики импульсов, делитель частоты, первьй и второй блоки совпадения кодов, генератор импульсов, выход первого счетчика импульсов соединен с первым входом первого блока совпадения кодов, второй вход которого соединен с вы- ходом первого регистра, первый вход которого является первым входом цифрового линейного интерполятора, второй вход которого является первым входом второго регистра, выход которого соединен с первым входом второго блока совпадения кодов, второй вход которого соединен с выходом второго счетчика импульсов, счетный вход которого соединен с выходом делителя час- тоты и первым выходом цифрового линейного интерполятора, отличающийся тем, что, с целью повьппе- ния быстродействия цифрового линейного интерполятора, в него введены эле- мент И, элемент НЕ, элемент ИЛИ-НЕ, первый вход которого подключен к третьему входу цифрового линейного интерор О.Головач 2863/43

Составитель И.Швец Техред Л.Олийнык

Корр

.„

Подп

Тираж 863 ВНИИПИ Государственного комитета СССР

П(1 долам изобретений и открытий 1Пт5, Москва, Ж-35, Раушская наб., д. А/5

Производственно-прчит рафическое предприятие, г.Ужгород, ул.Проектная, 4

полятора, второй вход элемента Ufti-HE соединен с выходом второго блока совпадения кодов и с вторым выходом цифрового линейного интерполятора, выход элемента ИЛИ-НЕ подключен к установочному входу второго счетчика импульсов и к установочному входу триггера, информационный вход которого соединен с источником сигнала логической единицы, управляющий вход триггера соединен с вторыми входами первого и второго регистров, первым входом первого счетчика импульсов и четвертым входом цифрового интерполятора, выход триггера подключен к первому входу элемента И, второй вход которого соединен с выходом генератора импульсов, а выход элемента И соединен с входом делителя частоты и вторым входом первого счетчика импульсов, выход первого блока совпадения кодов соединен с третьим выходом интерполятора и череэ элемент НЕ с третьим входом первого счетчика импульсов, старший разряд информационных входов параллельной загрузки которого соединен с источником сигнала логического нуля, выходы первого регистра соединены с входами параллельной загрузки с обеспечением соответствия К-му разряду выходов первого регистра (К-1)-го разряда входов параллельной загрузки первого счетчика импульсов.

Корректор Г.Решетник

.„..-..i - .--. - Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интерполятор | 1983 |

|

SU1117590A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Функциональный генератор | 1983 |

|

SU1120364A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1675849A1 |

| Цифровой линейный интерполятор | 1980 |

|

SU875341A1 |

| Линейный интерполятор | 1989 |

|

SU1695267A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к интерполирующим устройствам преобразования кодов. Цель изобретения - повьппение быстродействия интерполятора при сохранении точности.Цифровой линейный интерполятор содержит два входных регистра 1 и 2, два блока 3 и 4 совпадения, генератор 7 импульсов, усилитель 12 частоты, два счетчика 6 и 11 импульсов, в него введены элемент ИЛИ-НЕ 10 и элемент НЕ 5, кроме этого И-НЕ-вьсходы первого регистра соединены с К-1-входами предварительной загрузки первого счетчика. В данном устройстве вдвое ниже, чем в устройстве-прототипе, время аппроксимации. 2 ил. (Л и

| Цифровой линейный интерполятор | 1974 |

|

SU525057A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Цифровой линейный интерполятор | 1980 |

|

SU875341A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-19—Подача