Kj

ас ел

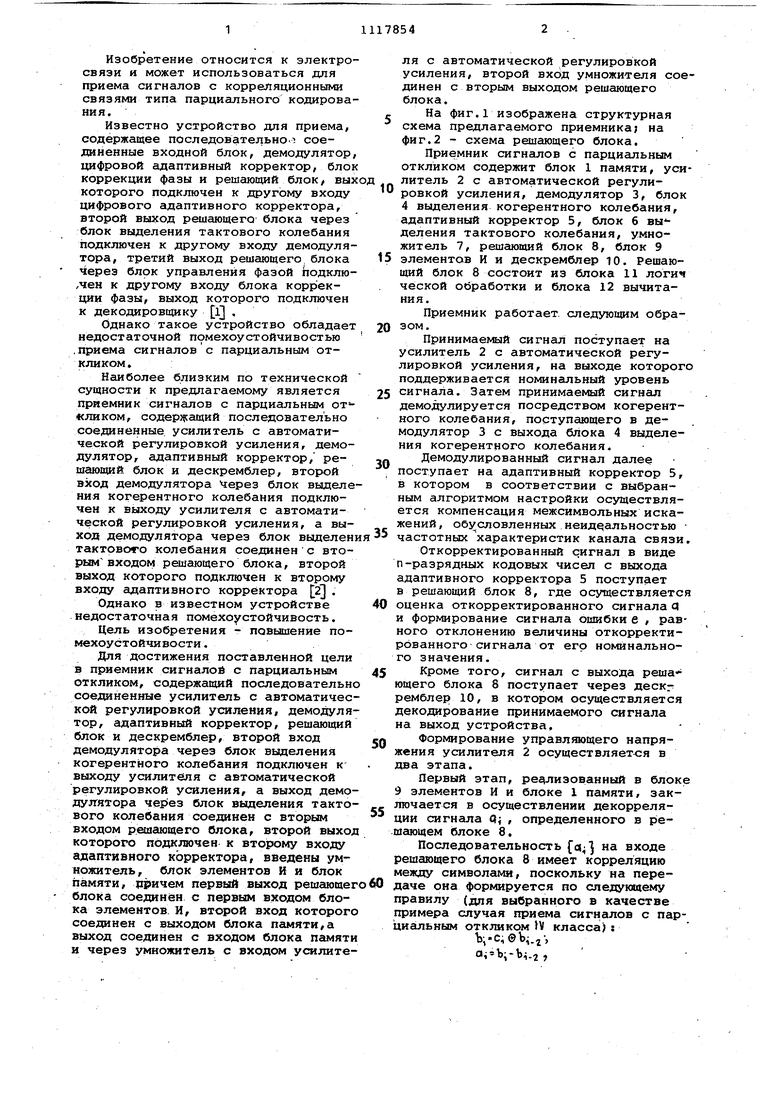

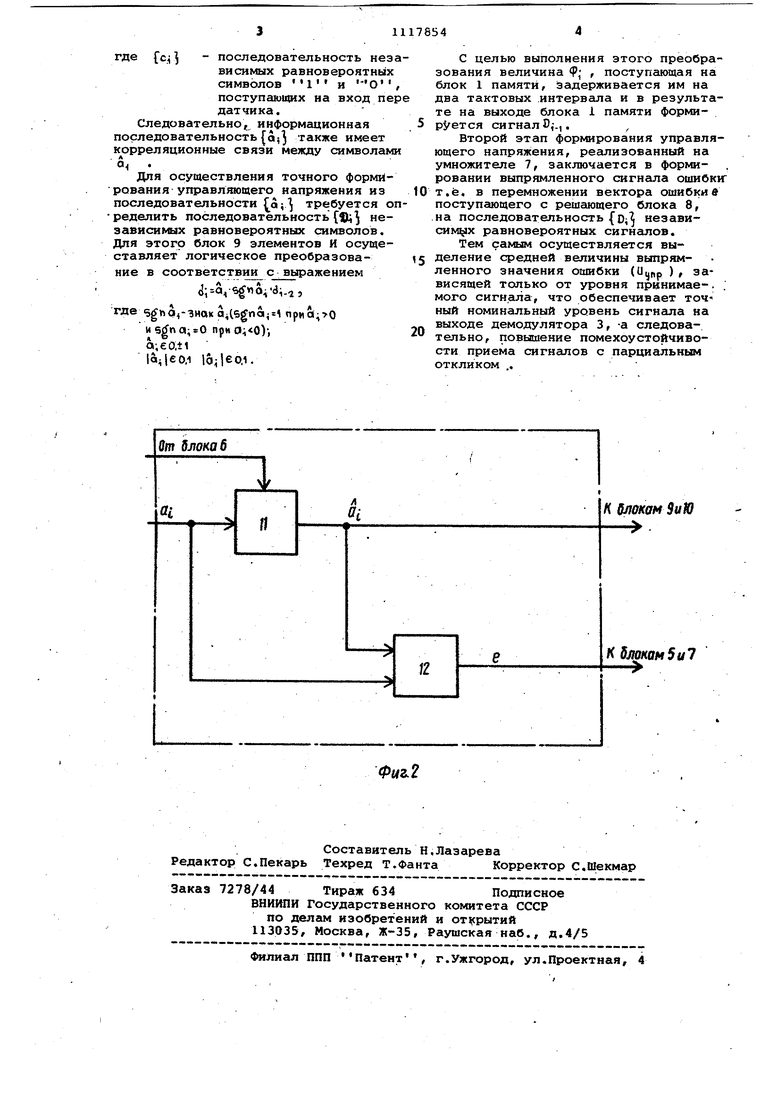

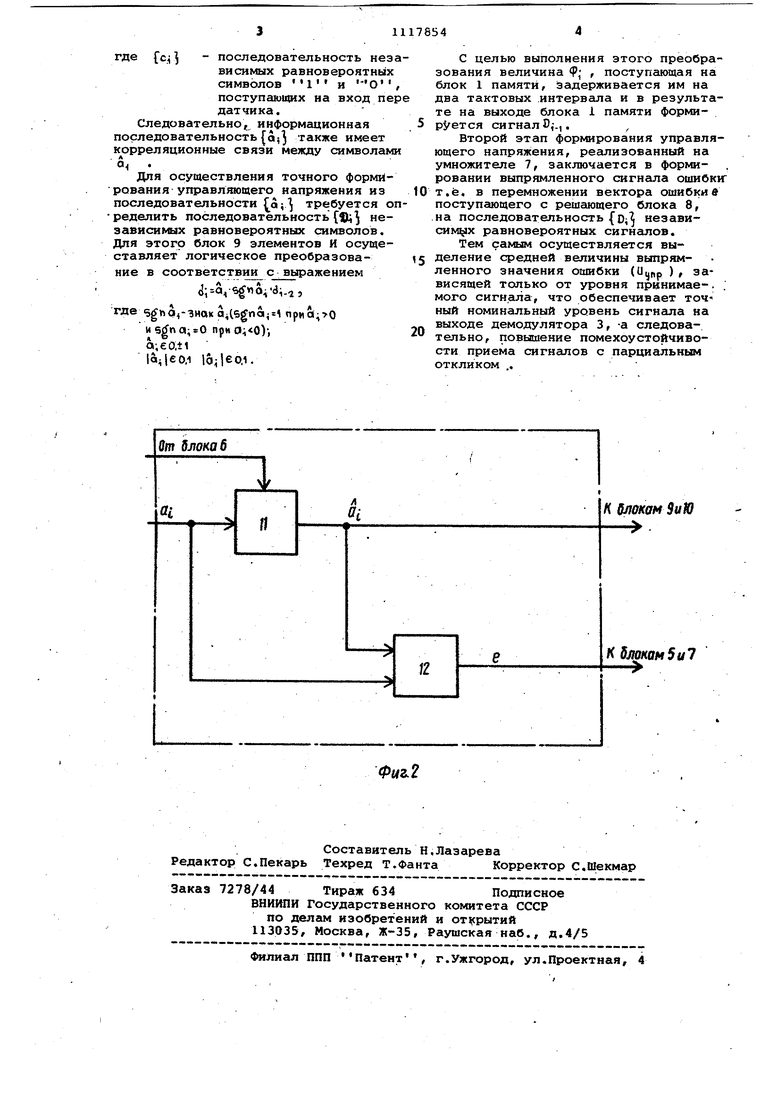

4 Изобретение относится к электросвязи и может использоваться для приема сигналов с корреляционными связями типа парциального кодирования. Известно устройство для приема, содержащее последовательно- соединенные входной блок, демодулятор, цифровой адаптивный корректор, блок коррекции фазы и решаюсций блок/ вых которого подключен к другому входу цифрового адаптивного корректора, второй выход решающего блока через блок выделения тактового колебания подключен к другому входу демодулятора, третий выход решающего блока через блок управления фазой подклю,чен к другому входу блока коррекции фазы, выход которого подключен к декодировщику l Однако такое устройство обладает недостаточной помехоустойчивостью .приема сигналов с парциальным откликом. Наиболее близким по технической сущности к предлагаемому является приемник сигналов с парциальным от «ликом, содержащий последовательно соединенные, усилитель с автоматической регулировкой усиления, демодулятор, адаптивный корректор/ решающий блок и дескремблер, вторюй вход демодулятора ерез блок выделе ния когерентного колебания подключен к выходу усилителя с автоматической регулировкой усиления, а выход демодулятора через блок вьщелен тактового колебания соединен с втоptaviвходом ретаающего блока, второй выход которого подключен к второму входу адаптивного корректора 2. Однако в известном устройстве недостаточная помехоустойчивость. Цель изобретения - повьиаение помехоустойчивости . Для достижения поставленной цели в приемник сигналов с парциальным откликом, содержащий последовательн соединенные усилитель с автоматичес кой регулировкой усиления, демодуля тор, адаптивный корректор, решающий блок и дескремблер, второй вход демодулятора через блок вьщеления когерентного колебания подключен к выходу усилителя с автоматической регулировкой усиления, а выход демо дулятора через блок выделения такто вого колебания соединен с вторым входом решающего блока, второй выхо которого подключен к второму входу адаптивного корректора, введены умножитель, блок элементов И и блок памяти, первый выход решающе блока соединён с первым входом блока элементов И, второй вход которог соединен с выходом блока памяти,а выход соединен с входом блока памят и через умножитель с входом усилите ля с автоматической регулировкой усиления, второй вход умножителя соединен с вторым выходом решающего блока. На фиг.1 изображена структурная схема предлагаемого приемника; на фиг.2 - схема решсоощего блока. Приемник сигналов с парциальным откликом содержит блок 1 памяти, усилитель 2 с автоматической регулировкой усиления, демодулятор 3, блок 4 вьаделения когерентного колебания, адаптивный корректор 5, блок 6 выделения тактового колебания, умножитель 7, решающий блок 8, блок 9 элементов И и дескремблер 10. Решающий блок 8 состоит из блока 11 логич ческой обработки и блока 12 вычитания. Приемник работает, следующим образом. Принимаемый сигнал поступает на усилитель 2 с автоматической регулировкой усиления, на выходе которого поддерживается номинальный уровень сигнала. Затем принимаемый сигнал демодулируется посредством когерентного колебания, поступающего в демодулятор 3 с выхода блока 4 выделения когерентного колебания. Демодулированный сигнал далее поступает на адаптивный корректор 5, в котором в соответствии с выбранным алгоритмом настройки осуществляется компенсация межсимвольных искажений, обу словленных неидцальностью частотных характеристик канала связи. Откорректированный сигнал в виде п-разрядных кодовых чисел с выхода адаптивного корректора 5 поступает в решающий блок 8, где осуществляется оценка откорректированного сигнала с| и формирование сигнала ошибки е , равного отклонению величины откорректированного сигнала от его номинального значения. Кроме того, сигнал с выхода решающего блока 8 поступает через дескг ремблер 10, в котором осуществляется декодирование принимаемого сигнала на выход устройства. Формирование управляющего напряжения усилителя 2 осуществляется в два этапа. Первый этап, реализованный в блоке 9 элементов И и блоке 1 памяти, заключается в осуществлении декорреляции сигнала ац , определенного в решающем блоке 8. Последовательность на входе решающего блока 8 имеет корреляцию между символапда, поскольку на передаче она формируется по следующему правилу (для выбранного в качестве примера случая приема сигналов с парциальным откликом tV класса) : bi-c;0b.j-, ai b;-bi.2j где ci(} - последовательность нез висимых равновероятных символов 1 и поступающих на вход пе датчика. Следовательно, информационная последовательность{а5 также имеет корреляционные связи между символам Для осуществления точного формирования управляющего напряжения из последовательности 0( требуется о ределить последовательность (Щ независимых равновероятных символов. Для этого блок 9 элементов И осущеставляет логическое преобразование в соответствии с выражением (,e «0;d..j, где б пр -знак np«a; o и приоиО); a;€0,t1 |а,|ео,1 .i. С целью выполнения этого преобразования величина Р; , поступающая на блок 1 памяти, задерживается им на два тактовых интервала и в результате на выходе блока 1 памяти формир1ется сигнал О,-.,. Второй этап формирования управляющего напряжения, реализованный на умножителе 7, заключается в формировании выпрямленного сигнеша ошибки т.е. в перемножении вектора ошибки поступающего с решающего блока 8, на последовательность {ъ независим х равновероятных сигналов. Тем самым осуществляется выделение средней величины выпрям- ленного значения ошибки (U,jnp ) , зависящей только от уровня принимае-. . мого сигнала, что обеспечивает точный номинальный уровень сигнала на выходе демодулятора 3, -а следовательно, повьпаение помехоустойчивости приема сигналов с парциальным откликом ..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема сигналов с парциальным откликом | 1983 |

|

SU1117855A1 |

| Цифровой приемник многопозиционных сигналов | 1982 |

|

SU1062890A1 |

| Устройство для приема дискретной информации | 1981 |

|

SU1007213A1 |

| Приемник многоуровневого фазоманипулированного сигнала | 1983 |

|

SU1146826A1 |

| Цифровой приемник многопозиционных сигналов | 1986 |

|

SU1417208A1 |

| Устройство для приема дискретной информации | 1978 |

|

SU790358A1 |

| Устройство для преобразования сигналов | 1984 |

|

SU1234991A1 |

| ЦИФРОВОЙ АДАПТИВНЫЙ ПРИЕМНИК ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2039416C1 |

| Устройство преобразования сигналов для передачи данных по первичному сетевому тракту | 1989 |

|

SU1739503A1 |

| Устройство для приема фазоманипулированных сигналов с одной боковой полосой | 1983 |

|

SU1164903A1 |

ПРИЕМНИК СИГНАЛОВ С ПАРЦИАЛЬНЫМ ОТКЛИКОМ, содержащий последовательно соединенные усилитель, с автоматической регулировкой усиления, демодулятор, адаптивный корректор, решающий блок и дескремблер, второй вход демодулятора через блок выделения когерентного колебания подключен к выходу усилителя с автоматической регулировкой усиления, а выход демодулятора через блок выделения тактового колебания соединен с вторым входом решающего блока, второй выход которого подключен к второму входу адаптивного корректора, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены умножитель, блок элементов И и блок памяти, причем первый выход решающего блока соединен с первым входом блока элементов И, второй вход которого соединен с выходом блока памяти, а выход соединен с входом блока памяти и через умножиi тель с входом усилителя с автоматической регулировкой усиления, второй W вход умножителя соединен с вторым выходом решающего блока.

0т длокаб

as

К блокам ЗиЮ

-.

К6шам5и7

Фиг.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| и др | |||

| Устройства преобразования сигналов передачи данны | |||

| М., Связь , 1979,с.120-121 рис.8.5 (прототип). | |||

Авторы

Даты

1984-10-07—Публикация

1983-06-21—Подача