00

со

09 О9

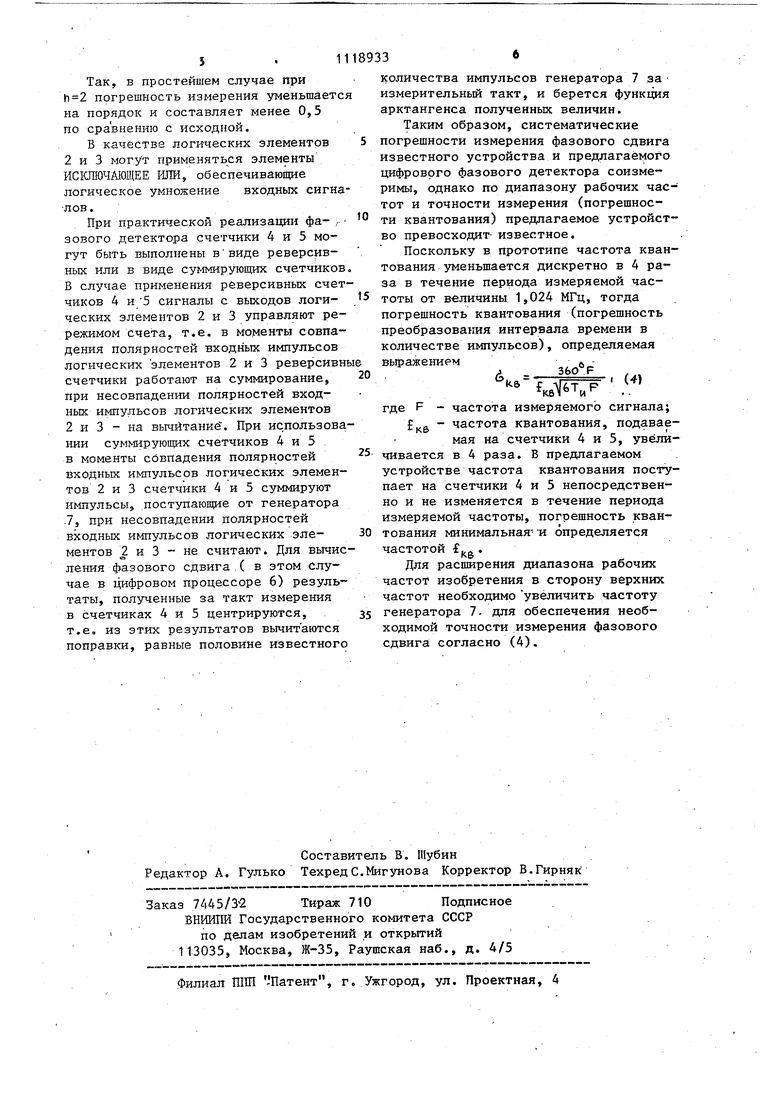

И 1 Изобретение относится к измерительной технике и может быть испол зовано для измерения фазового сдвиг сигналов в широком динамическом и частотном диапазоне. Известен измеритель сдвига фаз электрических сигналов, содержащий два ключа, соединенных с входом и выходом формирователя сигнала орт гональрого опорному, выходы ключей соединены с интеграторами, подключенными к вычислителю, соединенному с регистратором Однако известное устройство имее большую погрешность измерения фазов сдвигов за счет использования анало говых интеграторов и вычислителя. Известен также цифровой фазовый детектор, содержащий ограничитель, подключенный к первым входам перво и второго логических элементов, пер вый и второй измерительные счетчики соединенные с цифровым процессором блок памяти, последовательно соеднненные генератор, первый (программный) и второй (фиксированный) делители частоты и эталонный счетчик, выходы которого соединены с вторыми входами первого и второго логических элементов,.выходы логических элементов соединены соответственно с входами управления пе вого и второго измерительных счетчиков, другие входы которых подклю чены к выходу первого делителя час тоты, входы управления первого дели теля частоты соединены с блоком па мяти, входы которого подключены к второму делителю частоты С23« Недостатки данного фазового детектора заключаются в узком диапазоне рабочих частот, ограниченном сверху максимально возможной скорос тью управления коэффициентом деле- ния первого делителя частоты, и низкой точности измерения фазовых сдвигов, обусловленной изменением в широких пределах частоты счетных импульсов, поступающих на счетчики. Цель изобретения - расширение диапазона рабочих частот и повьшение точности измерения фазового сдвига. Указанная цель достигается тем, что в цифровой фазовый детектор, J держащий ограничитель, первый и рой логические элементы, первый и втррбй счетчики, цифровой про3 . 2. цёссор, последовательно соединенные Генератор, первый и второй делители частоты и эталонный счетчик, блок памяти, причем выходы второго делителя частоты соединены с блоком памяти, первые входы первого и второго логических элементов соединены с С ограничителем,- выходы логических элементов соединены соответственно с входами управления первого и второго счетчиков, выходы которых .подключены к цифровому процессору, введен KOMMytaTop, причем выходы коммутатора соединены с вторыми входами,первого и второго логических элементов, первые входы коммутатора подключены к эталонному счетчику, а вторые входы - к блоку памяти, выход генератора импульсов соединен с входами первого и второго счетчиков. Использование коммутатора, управляемого блоком памяти, позволяет расширить диапазон рабочих частот и повысить точность измерения, поскольку исключается процесс управления коэффициентом деления первого делителя частоты, а частота счетнбк импульсов, поступающих на измерительные счетчики, остается постоянной и равной частоте генератора импульсов . На чертеже приведена структурная схема цифрового фазового детектора. Устройство содержит ограничитель 1, соединенньй с первыми входами первого 2 и второго 3 логических элементов, первый 4 и второй 5 счетчики, соединенные с цифровом процессором 6, последовательно соединенные генератор 7, первый 8 и второй 9 делители частоты, эталонный счетчик 10, коммутатор 11, блок памяти 12. Устройство работает следукщим образом. Ограничитель 1 преобразует входной сигнал известной частоты в прямоугольные импульсы, поступающие на логические элементы 2 и 3 С выхода коммутатора 11 два прямоугольных эталонных колебания известной частоты, равной частоте входного сигнала, перемножаются в логических элементах 2 и 3 с прямоугольными импульсами входного сигнала, причем первое колебание поступает на логический элемент 2, второе, сдвинутое на 90 относительно первого. на логический элемент 3. Импульсные сигналы с выходов логических элементов 2 и 3 используются для управлени режимом работы счетчиков А и 5, которые обеспечивают пвдсчет количества импульсов генератора 7. Количество импульсов, поступивших в счетчики 4 и 5, пропорционально косинусу и синусу измеряемого фазово го сдвига. В цифровом процессоре 6 по окончании цикла измерения вычисляется отношение кодов чисел, накопленных в счетчиках 4 и 5, и -берется функция арктангенса от этого отношения. Синхронизация измерений осуществляется от генератора 7, а анализ смены информации счетчиков производится процессором 6 по состоянию мпадших разрядов. Поскольку характеристика, в соответствий с которой работает фазовый детектор, не гармоническая, а треугольная, результат вычисления фазового сдвига через арктангенс двух негармонических величин содержит погрешность измерения, максимальная величина которой йревьш1ает 4°, а пе риод повторения знакопеременной зависимости погрешности измерения от фазового сдвига составляет 90°. Для уменьшения указанной погрешности измерения сигнал с выхода генератор 7 поступает через первый делитель частоты 8 на второй делитель частоты 9. К выходу второго делителя частоты 9 подключен эталонный счетчик 10, который формирует п пар квадратурных эталонных сигналов, сдвинутых относительно друг друга на угол 4 90°/п. При известной длительности време измерения фазового детектора (Т) последнее разбивается на h тактов Т., (для п 2 формируется 1 причем два такта измерения Т 1 и Т Т|-1- ) . Формирование тактов измерения осуществляется блоком памяти 12 пзгг опроса адресов блока памяти 12 сигн лами с выходов второго делителя час тоты 9. Блок памяти 12 управляет коммутатором 11, в соответствии с сигналами управления. Длительность времени измерения Т„ фазового детект ра разбивается на такты (Т Tj Tj), в течение которых коммутатором 11 к входам логических элементов 2 и 3 подключаются соответствующие па ры квадратурных составляющих эталонного колебания. По окончании первого такта измерелия в счетчиках 4 и 5 зафиксированы коды чисел, пропорциональные соответственно косинусу 1 синусу измеряемого фазового сдвига f,, значение которого определяется через арктангенс отношения измеренных величин в цифровом процессоре 6. В течение второго такта измерения Т, коммутатор 11 подключает к логическим элементам 2 и 3 пару квадратурных эталонных Сигналов, сдвинутых относительно эталонньв сигналов в первом такте измерения на угол V 90°/n. По накопленной в счетчиках 4 и 5 информации по окончании второго такта измерения цифровым процессором 6 определяется измеренный фазовый сдвиг ifx . Таким образом, в каждом последующем такте,измерения коммутатор 11 подключает к логическим элементам 2 и 3 два квадратурных эталонных сигнала, сдвинутых относительно эталонных сигналов предыдущего такта измерения на угол 90 /п, и в цифровом процессоре 6 определяется измеренный фазовый сдвиг. Результат измерения среднего значения фазового сдвига за время Т определяется цифровым процессором 6 по формуле %-() 90 (2) Для случаев среднее значе иие фазового сдвига равно .-tf U - 1 Cf 2 Таким образом, усредняя измерения за п тактов при различных значениях фазовых сдвигов эталонных сигналов, можно уменьшить погрешность измерения фазовых сдвигов обусловленную негармонической характеристикой фазового детектора. Так, в простейшем случае при погрешность измерения уменьшаетс на порядок и составляет менее 0,5 по сравнению с исходной, В качестве логических элементов 2 и 3 могут применяться элементы ИСКЛЮЧАЮЩЕЕ I-fflH, обеспечивающие логическое умножение входных сигна лов. При практической реализации фа- , зового детектора счетчики 4 и 5 могут быть выполнены ввиде реверсивных или в виде суммирующих счетчиков В случае применения реверсивных счет чиков 4 и/5 сигналы с выходов логических элементов 2 и 3 управляют рережимом счета, т.е. в моменты совпадения полярностей входных импульсов логических элементов 2 и 3 реверсивн счетчики работают на суммирование, при несовпадении полярностей входных импульсов логических элементов 2 и 3 - на вычитание. При ис.пользова нии суммирующих счетчиков 4 и 5 . в моменты совпадения полярностей входных импульсов логических элементов 2 и 3 счетчики 4 и 5 суммируют импульсы, поступающие от генератора .7, при несовпадении полярностей входных импульсов логических элементов 2 и 3 - не считают. Для вычис ления фазового сдвига ( в этом случае в цифровом процессоре 6) результаты, полученные за такт измерения в счетчиках 4 и 5 центрируются, т.е. из этих результатов вычитаются поправки, равные половине известного количества импульсов генератора 7 за измерительньш такт, и берется функция арктангенса полученных величин. Таким образом, систематические погрешности измерения фазового сдвига известного устройства и предлагаемого цифрового фазового детектора соизмеримы, однако по диапазону рабочих частот и точности измерения (погрешности квантования) предлагаемое устройство превосходит известное. Поскольку в прототипе частота квантования з еньшается дискретно в 4 раза в течение периода измеряемой частоты от величины 1,024 МГц, тогда погрешность квантования (погрешность преобразования интервала времени в количестве импульсов), определяемая выражением , где F - частота измеряемого сигнала; кв частота квантования, подаваемая на счетчики 4 и 5, увеличивается в 4 раза. В предлагаемом устройстве частота квантования поступает на счетчики 4 и 5 непосредственно и не изменяется в течение периода измеряемой частоты, погрешность квантования минимальная- и определяется частотой f Для расширения диапазона рабочих частот изобретения в сторону верхних частот необходимо увеличить частоту генератора 7. для обеспечения необходимой точности измерения фазового сдвига согласно (4),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство измерения параметров дисбаланса | 1990 |

|

SU1795318A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЕВИАЦИИ ЧАСТОТЫ | 1998 |

|

RU2138828C1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Цифровой фазовый дискриминатор | 1975 |

|

SU602881A1 |

| ИЗМЕРИТЕЛЬ ХАРАКТЕРИСТИК ФАЗОВЫХ ФЛУКТУАЦИЙ | 1992 |

|

RU2041469C1 |

| Анализатор частотного спектра | 1980 |

|

SU900209A1 |

| Устройство для измерения амплитуды и фазы радиосигнала | 1989 |

|

SU1665811A1 |

| Устройство фазовой автоподстройки частоты | 1986 |

|

SU1443173A1 |

ЦИФРОВОЙ ФАЗОВЫЙ ДЕТЕКТОР, содержащий ограгничитель, первьй и вто рой логические элементы, первый и второй счетчики, цифровой процессор последовательно соединенные генератор первый и второй делители частоты и эталонный счетчик, блок памяти, при, чем выходы второго делителя частоты соединены с блоком памяти, lepBt входы первого и второго логических элементов соединены с ограничителем, выходы логических элементов соединены . соответственно С- входами управления первого и второго счетчиков, выходы которых подключены к цифpoвo €y процессору, о т л и ч a ю щ и и с я тем, что, с целью расширения диапазона рабочих частот и повышения точности, в него введен коммутатор, причем выходы коммутатора соединены с вторыми входами первого и второго логических эглементов, первые входы коммутатора подключены к эталонному счетчику, a вторые входы - к блоку памяти, выход генератора импульсов соединен с входами первого и второго счетчиков.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Измеритель сдвига фаз электрических сигналов | 1978 |

|

SU773517A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| , 2 | |||

| АЭРОЗОЛЬНЫЙ ФИЛЬТР | 2009 |

|

RU2417116C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-10-15—Публикация

1983-05-30—Подача