фиг.1

Изобретение относится к радиотехнике и может бьггь использовано в устройствах авторегулирования частоты и фазы сигналов.

Цель изобретения - повышение точности подстройки фазы при вьтолнении фазового детектора.с релейной характеристикой,

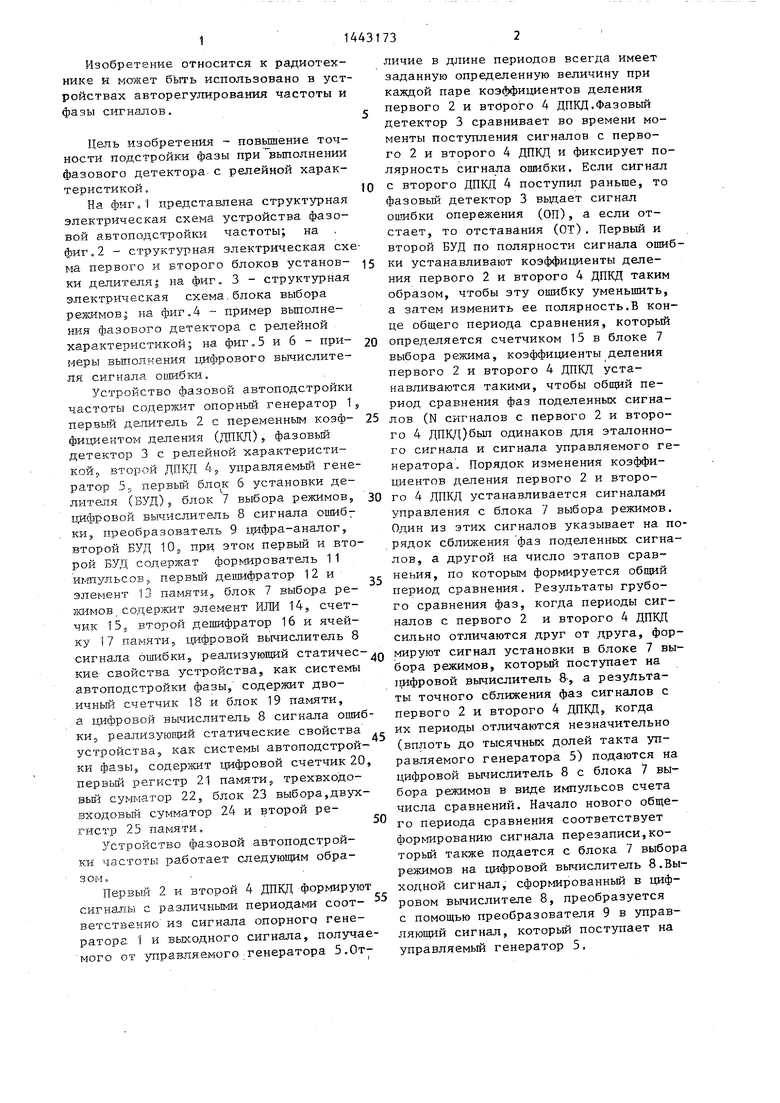

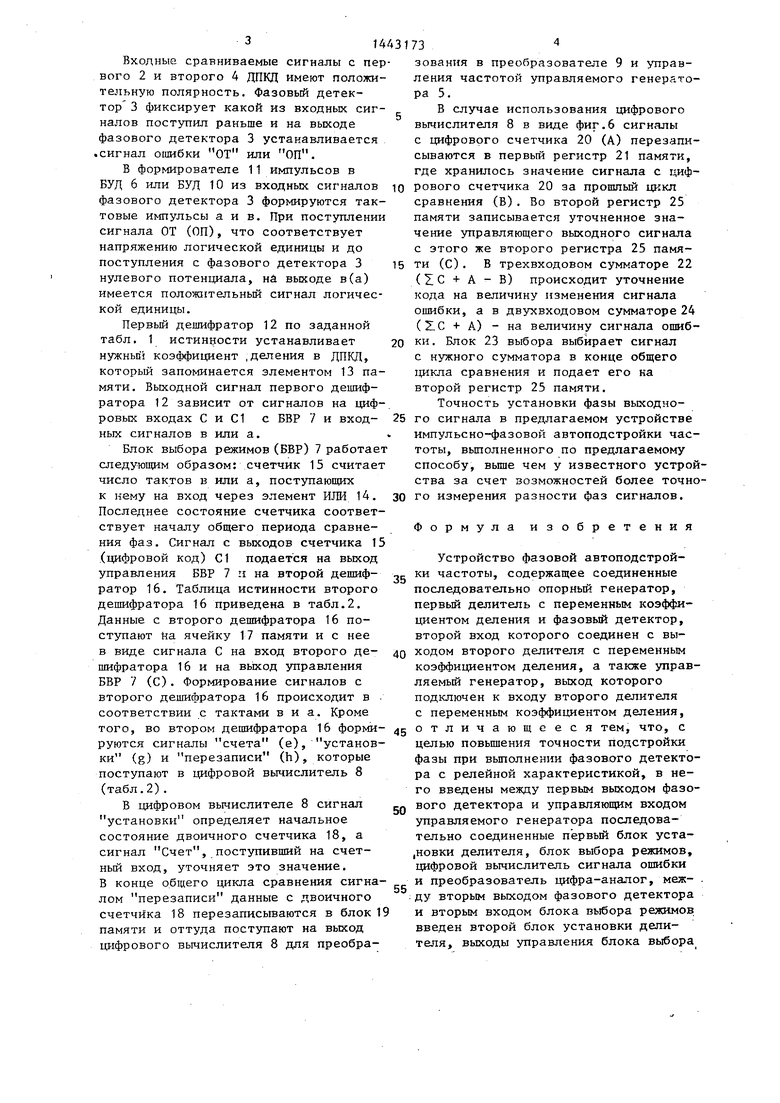

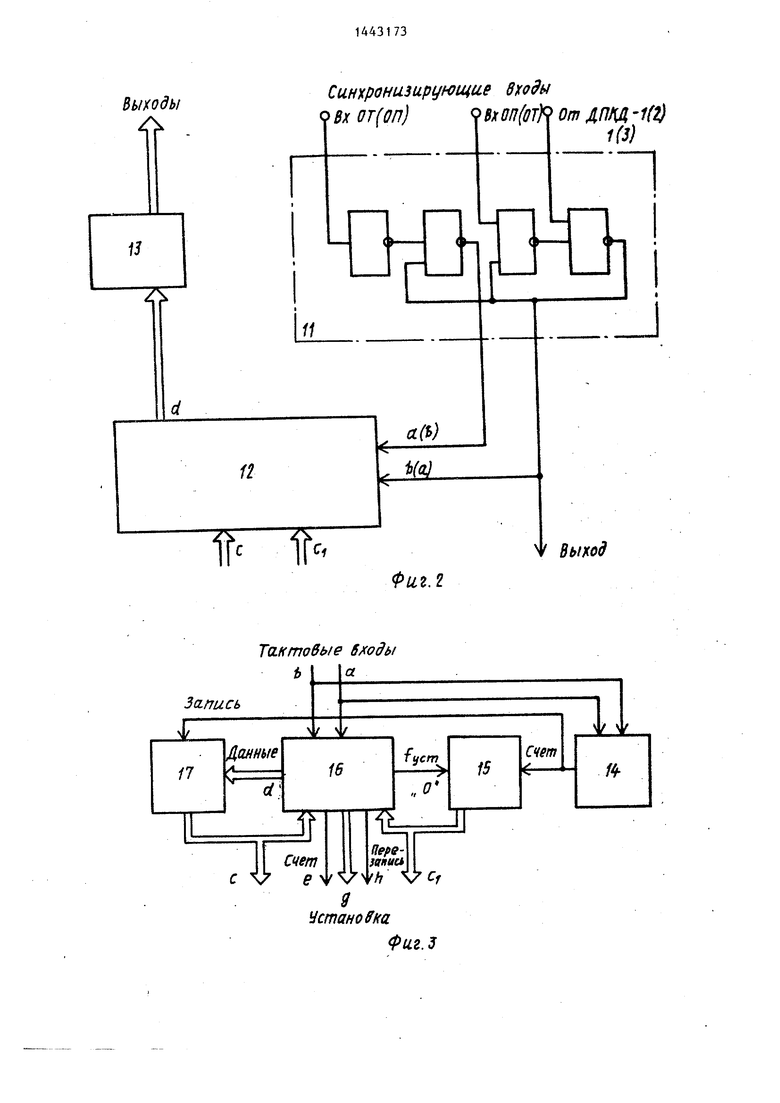

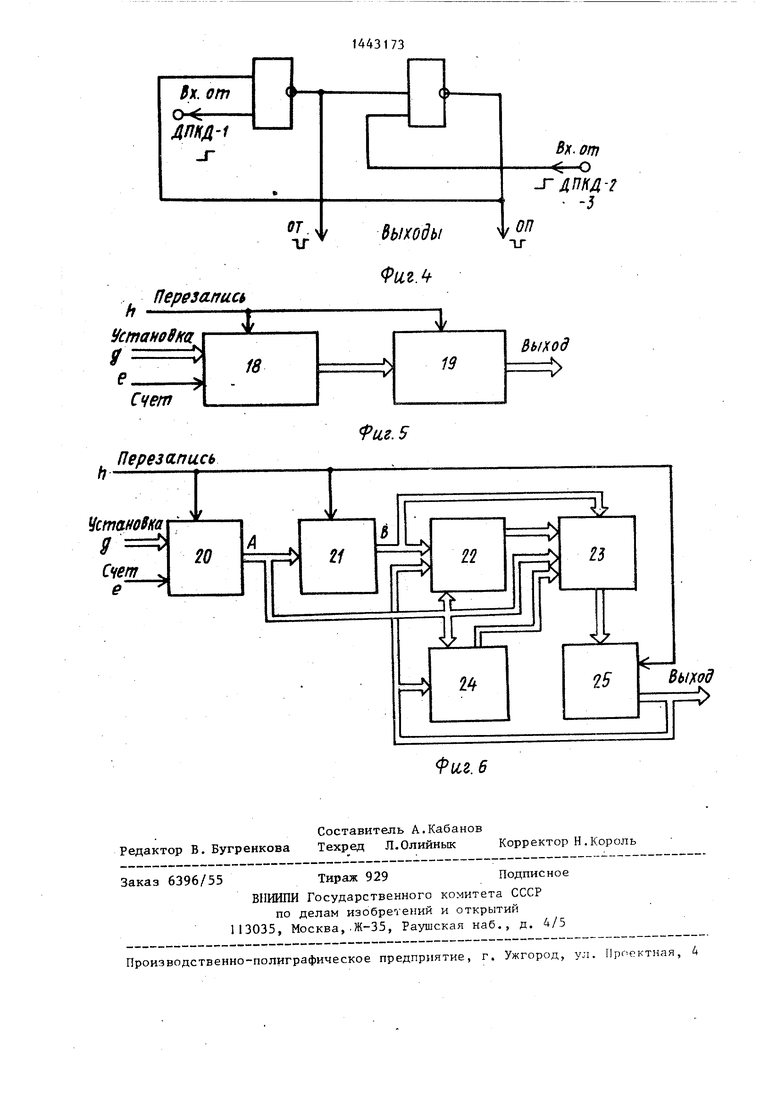

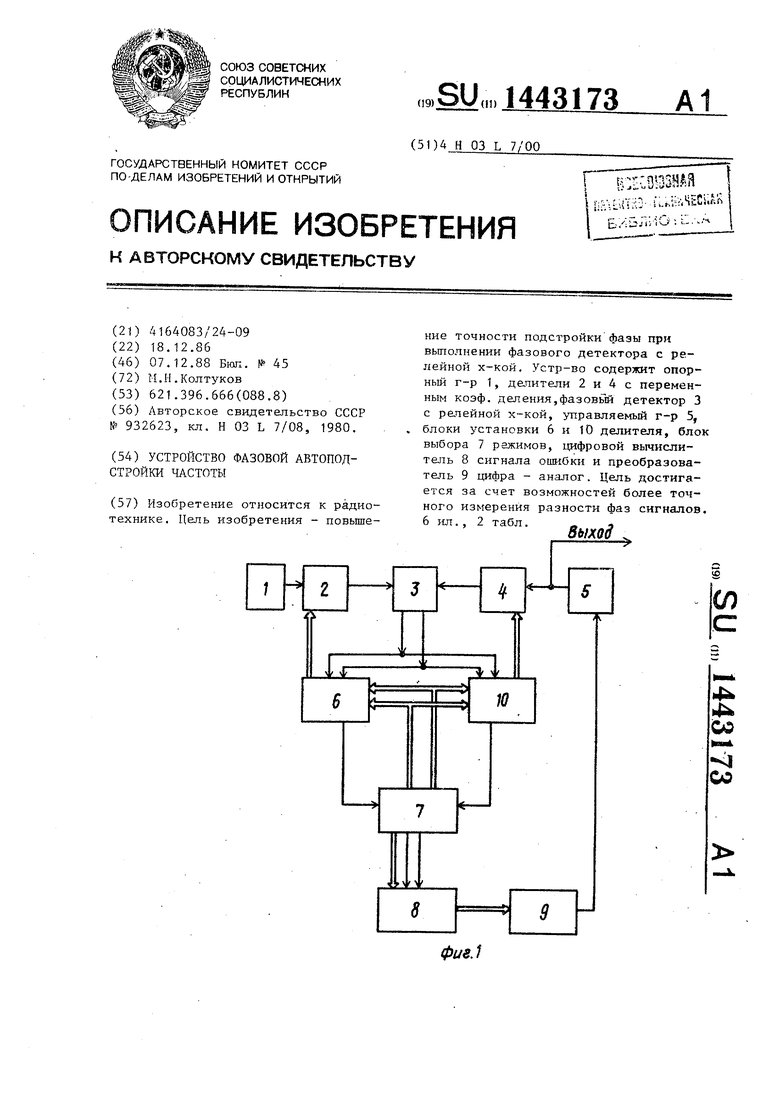

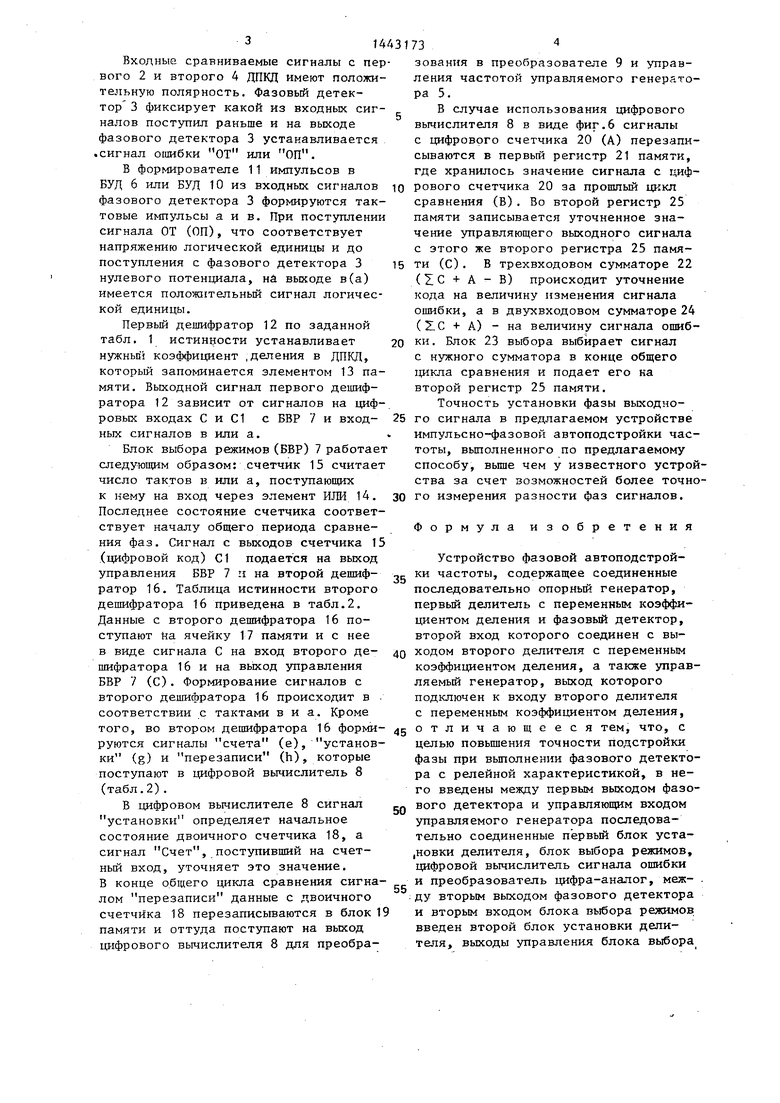

На фиг,1 представлена структурная электрическая схема устройства фазовой автоподстройки частоты; на , - структурная электрическая схема первого и второго блоков установ- ки делителя; на фиг. 3 - структурная электрическая схема.блока выбора режимов; на фиг.4 - пример вьшолне- ния фазового детектора с релейной характеристикой; на фиг,5 и 6 - при- меры вьшолнения цифрового вычислителя сигнала ошибки.

Устройство фазовой автоподстройки частоты содержит опорный генератор 1j первьм делитель 2 с переменным козф- фициентом депения (ДПКД)$ фазовый детектор 3 с релейной характеристикой, второй ДПК,П 4;, управляемьш генератор 55 первый блок 6 установки делителя (БУД), блок 7 выбора режимов, цифровой вычислитель 8 сигнала ошиб7 ки, преобразователь 9 цифра-аналог, второй БУД Юз при этом первый и второй БУД содержат фop iИpoвaтeль 11 И1--т:ульсов5 первый дешифратор 12 и элемент 13 памяти,, блок 7 выбора режимов содержит элемент ИЛИ 14, счетчик 15, второй дешифратор 16 и ячейку 17 памяти, цифровой вычислитель 8 сигнала ошибки, реализующий статические свойства устройства, как системы автоподстройки фазы, содержит дво- ичньй счетчик 18 и блок 19 памяти, а цифровой вычислитель 8 сигнала опиб ки, реализующий статические свойства устройства, как системы автоподстрой- ки фазы, содержит цифровой счетчик 20 первьш регистр 21 памяти, трехвходо- вьй сумматор 22, блок 23 выбора,двух- входовьш сумматор 24 и второй регистр 25 памяти.

1 стройство фазовой автоподстройки частоты работает следующим обра3 OiM .

Первый 2 и второй 4 ДПКД формируют сигналы с различными периодами соот ветственно из сигнала опорного генераторе. 1 и выходного сигнала, получаемого от управляемого генератора 5.0т

.

JQ

20 25 30дд - ,

35

50

55

личие в длине периодов всегда имеет заданную определенную величину при каждой паре коэффициентов деления первого 2 и второго 4 ДПКД.Фазовый детектор 3 сравнивает во времени моменты поступления сигналов с первого 2 и второго 4 ДПКД и фиксирует полярность сигнала ошибки. Если сигнал с второго ДПКД 4 поступил раньше, то фазовый детектор 3 выдает сигнал ошибки опережения (ОП), а если отстает, то отставания (ОТ). Первый и второй БУД по полярности сигнала ошибки устанавливают коэффициенты деления первого 2 и второго 4 ДПКД таким образом, чтобы эту ошибку уменьшить, а затем изменить ее полярность.В конце общего периода сравнения, который определяется счетчиком 15 в блоке 7 выбора режима, коэффициенты деления первого 2 и второго 4 ДПКД устанавливаются такими, чтобы общий период сравнения фаз поделенных сигналов (N сигналов с первого 2 и второго 4 ДПК/1)бьт одинаков для эталонного сигнала и сигнала управляемого генератора. Порядок изменения коэффициентов деления первого 2 и второго 4 ДПКД устанавливается сигналами управления с блока 7 выбора режимов. Один из этих сигналов указывает на порядок сближения фаз поделенных сигналов, а другой на число этапов сравнения, по которым формируется общий период сравнения. Результаты грубого сравнения фаз, когда периоды сигналов с первого 2 и второго 4 ДПКД сильно отличаются друг от друга, формируют сигнал установки в блоке 7 выбора режимов, который поступает на цифровой вычислитель 8-, а результаты точного сближения фаз сигналов с первого 2 и второго 4 ДПКД, когда их периоды отличаются незначительно (вплоть до тысячных долей такта управляемого генератора 5) подаются на цифровой вычислитель 8 с блока 7 выбора режимов в виде импульсов счета числа сравнений. Начало нового общего периода сравнения соответствует формированию сигнала перезаписи,который также подается с блока 7 выбора режимов на цифровой вычислитель 8.Выходной сигнал, сформированный в цифровом вьиислителе 8, преобразуется с помощью преобразователя 9 в управляющий сигнал, который поступает на управляемый генератор 5.

314

Входные сравниваемые сигналы с первого 2 и второго 4 ДПКД имеют положительную полярность. Фазовый детектор 3 фиксирует какой из входных сигналов поступил раньше и на выходе фазового детектора 3 устанавливается .сигнал ошибки ОТ или ОП.

В формирователе 11 импульсов в БУД 6 или БУД 10 из входных сигналов фазового детектора 3 формируются тактовые импульсы айв. При поступлении сигнала ОТ (ОП), что соответствует напряжению логической единицы и до поступления с фазового детектора 3 нулевого потенциала, н& выходе в(а) имеется положительный сигнал логической единицы.

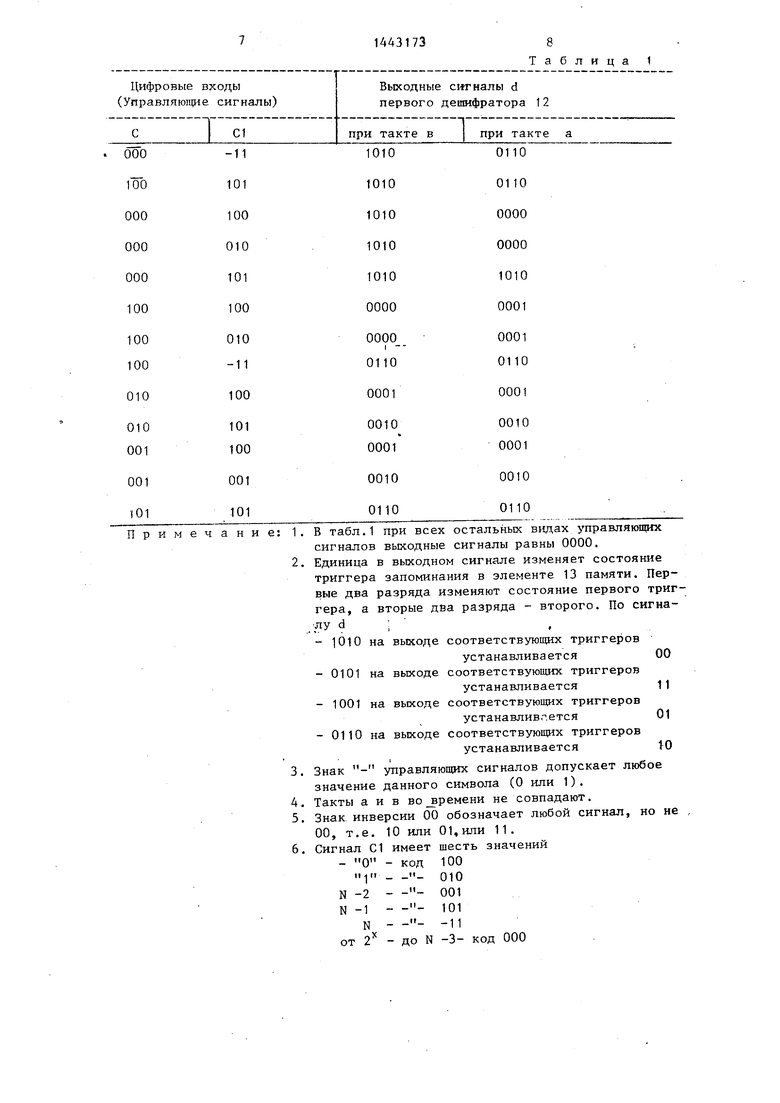

Первый дешифратор 12 по заданной табл. 1 истинности устанавливает нужньй коэффициент .деления в ДПКД, который запоминается элементом 13 памяти. Выходной сигнал первого дешифратора 12 зависит от сигналов на цифровых входах С и С1 с ВЕР 7 и вход- ных сигналов в или а.

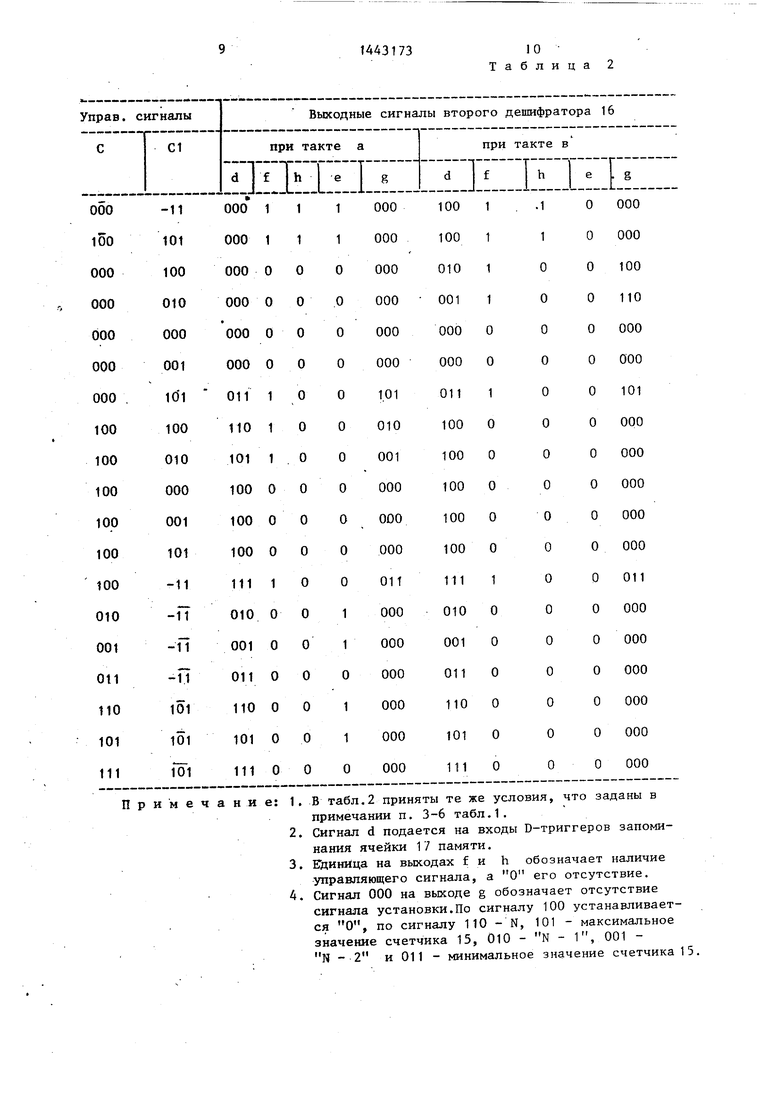

Блок выбора режимов (БВР) 7 работает следующим образом: счетчик 15 считает число тактов в или а, поступающих к нему на вход через элемент ИЛИ 14. Последнее состояние счетчика соответствует началу общего периода сравнения фаз. Сигнал с выходов счетчика 15 (цифровой код) С1 подается на выход управления БВР 7 и на второй дешиф- ратор 16. Таблица истинности второго дешифратора 16 приведена в табл.2. Данные с второго дешифратора 16 поступают йа ячейку 17 памяти и с нее в виде сигнала С на вход второго де- шифратора 16 и на выход управления БВР 7 (С). Формирование сигналов с второго дешифратора 16 происходит в . соответствии с тактами в и а. Кроме того, во втором дешифратора 16 форми- руются сигналы счета (е), установки (g) и перезаписи (h), которые поступают в цифровой вычислитель 8 (табл.2).

В цифровом вычислителе 8 сигнал установки определяет начальное состояние двоичного счетчика 18, а сигнал Счет, поступивший на счетный вход, уточняет это значение.

В конце общего цикла сравнения сигна.,.,

лом перезаписи данные с двоичного

счетчика 18 перезаписываются в блок 1 памяти и оттуда поступают на выход 1ЩФРОВОГО вычислителя 8 для преобра734

зования в преобразователе 9 и управления частотой управляемого генератора 5.

В случае использования цифрового вычислителя 8 в виде фиг.6 сигналы с цифрового счетчика 20 (А) перезаписываются в первый регистр 21 памяти, где хранилось значение сигнала с цифрового счетчика 20 за прошпый цикл сравнения (В). Во второй регистр 25 памяти записывается уточненное значение управляющего выходного сигнала с этого же второго регистра 25 памяти (С). В трехвходовом сумматоре 22 (ZC + А - В) происходит уточнение кода на величину изменения сигнала ошибки, а в двухвходовом сумматоре 24 (21С + А) - на величину сигнала ошибки. Блок 23 выбора выбирает сигнал с нужного сумматора в конце общего цикла сравнения и подает его на второй регистр 25 памяти.

Точность установки фазы выходного сигнала в предлагаемом устройстве импульсно-фазовой автоподстройки частоты, вьшолненного по предлагаемому способу, вьш1е чем у известного устройства за счет возможностей более точного измерения разности фаз сигналов.

Формула изобретения

Устройство фазовой автоподстройки частоты, содержащее соединенные последовательно опорный генератор, первьш делитель с переменным коэффициентом деления и фазовый детектор, второй вход которого соединен с выходом второго делителя с переменным коэффициентом деления, а также управляемый генератор, выход которого подключен к входу второго делителя с переменным коэффициентом деления, отличающееся тем, что, с целью повьш1ения точности подстройки фазы при выполнении фазового детектора с релейной характеристикой, в него введены между первым выходом фазового детектора и управляющим входом управляемого генератора последовательно соединенные первый блок уста- ,новки делителя, блок выбора режимов, цифровой вычислитель сигнала ошибки и преобразователь цифра-аналог, меж- ду вторым выходом фазового детектора и вторым входом блока выбора режимов введен второй блок установки делителя, выходы управления блока выбора

5 14

режимов соединены с управляющими входами первого и второго блоков установки делителяJ управляющие выходы которых соединены с установочными входами соответственно первого и второго делителей с переменным коэффициентом деления, а первый и второй выходы фазового детектора дополнительно соединены соо тветственно с торыми входа- ми второго и первого блоков установки делителя, причем каждьй блок установки делителя вьтолнен в виде последовательно соединенньк формирователя импульсов, входы которого явля- ются входами блока установки делителя, а один из выходов является выходом блока установки делителя,первого дешифратора и элемента памяти, выходы которого являются управляющими выходами блока установки делителя, при этом управляющими входами блока установки делителя являются первьш

736

и второй цифровые входы первого дешифратора, а блок выбора режимов выполнен в виде последовательно соединенных элементов ИЛИ, входы которого являются первым и вторым входами блока выбора режимов, счетчика, второго дешифратора и ячейки памяти, причем входы элемента ШЖ соединены также с тактовыми входами второго дешифратора, а выход элемента ИЛИ - с входом записи ячейки памяти, выходы ячейки памяти и счетчика являются управляющими выходами блока выбора режимов и соединены с управляющими входами второго дешифратора, установочный выход второго дешифратора подключен к входу сброса счетчика в ноль при этом выходы второго дешифратора Счетный, Установка и Перезапись являются выходами блока выбора режимов.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЧАСТОТНО-ВРЕМЕННОЙ СИНХРОНИЗАЦИИ | 2006 |

|

RU2341892C2 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

| Синтезатор частот | 1989 |

|

SU1730720A1 |

| Цифровой синтезатор частот с частотной модуляцией | 1985 |

|

SU1293840A1 |

| Способ определения отклонения частоты от номинального значения | 1989 |

|

SU1707561A1 |

| Устройство синхронизации с фазовой автоподстройкой частоты | 1988 |

|

SU1700751A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

Изобретение относится к радиотехнике. Цель изобретения - повьшение точности подстройки фазы при выполнении фазового детектора с релейной х-кой. Устр-во содержит опорный г-р 1, дапители 2 и 4 с переменным коэф. деления,фазовый детектор 3 с релейной х-кой, управляемый г-р 5, . блоки установки 6 и 10 делителя, блок выбора 7 режимов, цифровой вычислитель 8 сигнала ошибки и преобразователь 9 цифра - аналог. Цель достигается за счет возможностей более точного измерения разности фаз сигналов. 6 ил., 2 табл. Вымд (Л ф 4i С Ч СО

000

100

000

010

000

101

100

100

001

001

jOI

101

Примечание: 1

В табл.1 при всех остальных видах управляющих сигналов выходные сигналы равны 0000.

-1010 на выходе соответствующих триггеров

устанавливается

-0101 на выходе соответствующих триггеров

устанавливается

-1001 на выходе соответствующих триггеров

устанавливается

-0110 на выходе соответствующих триггеров

устанавливается

00 11 01

to

- до N

- код

-

0000 0000

1010 0001

0001 0110

0001

0010 0001

0010 0110

00 11 01

to

100 010 001 101 -11 - до N -3- код 000

- код

- - примечании п. 3-6 табл.1.

Вы)(оды Л

Синхронизирующие биоды

9Вх ОТ(ОП)98)(Ofj(OT)9 От (2)

1(3)

Тактовые

п

Фиг.2

Фиг.З

Перезапись

.S

| Цифровой синтезатор частоты | 1980 |

|

SU932623A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-07—Публикация

1986-12-18—Подача