вторым входом четвертого элемента И, единичный выход второго триггера подключен к второму входу элемента ИЛИ, причем второй вход третьего элемента И и 1&ервый вход четвертого элемента И являются входами блока определения интервала выравнивания, первым, вторым и третьим выходами которого являются единичные выходы соответственно первого, второго и пятого триггеров, четвертым выходом

блока определения интервала выравнивания является выход дешифратора

интервала выравнивания.

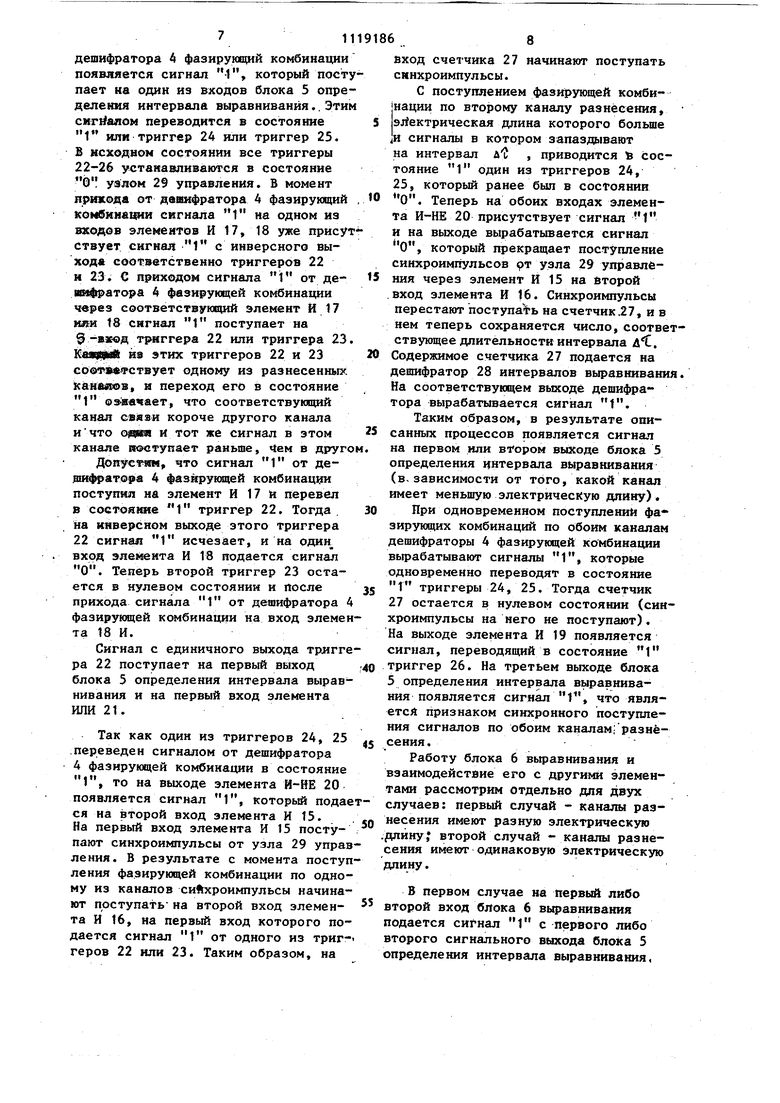

3. Устройство по п, 1, о т л ич а ю щ е 6 с я тем, что блок выравнивания содержит основные элемен- ты И, дополнительные элементы И, элементы ИЛИ, элементы НЕ и два ре гистра сдвига, выходы соответствующих разрядов которых подключены к первым входам соответствуницих основных элементов И, выходы которых соединены с соответствующими входами первого и второго элементов ИЛИ, выходы которых подключены к первым входам соответственно первого и вто- рого дополнительных элементов И, выходы которых соединены с пepвы я входами соответственно третьего и четвертого элементов ШШ, вторые входы которых подключены к выходам

соответственно третьего и четверто го дополнительных элементов И, перв1нё

входы которых соединены с первыми входами соответственно пятого, шестого, седьмого и восьмого дополнитель ных элементов И, выходы шестого и восьмого дополнительных элементов Или соединены с первыми входами соответственно пятого и шестого элемен- ; тов ИЛИ, вторые которых подключены к выходам соответственно девятого и десятого дополнительных элементов И, первые входы которых объединены и подключены к выходу первого элемента НЕ, вход которого соединен с первыми входами одиннадцатого и двенадцатого дополнительных элемен1 тов И, выходы которых сдединеш с первыми входами соответственно седьмого и восьмого элементов ИЛИ, вторые входы которых подключены к выходам соответственно пятого и седьмого дополнительных элементов И, вторые входы которых объединены и подключены к входу второго элемента НЕ, выход которого соединен с вторыми входами шестого и восьмого дополнительных элементов И, выходы пятого и шестого элементов ИЛИ подключены к первым входам соответственно тринадцатого и четырнадцатого дополнительных элементов И, выходы которых coefs,KHeHbi с первыми входшш соответственно девятого и десятого элементов ШШ, вторые входы которых подключены к выходам соответственно пятнадцатого и шестнадцатого допол{нителЬных элементов И, первые входы которых соединены с вторыми входами соответственно девятого и одиннадцатого и десятого и двенадцатого Дополнительных элементов И,Вторые входы первого, второго, тринадцатого и четырнадцатого дополнительных элементов И подключены к выходу третьего элемента НЕ, вход которого соединен с вторыми вводами третьего, четвертого, пятнадцатого и шестнадцатого дополнительных элементов И, устано1вочные входа первого и второго регистров сдвига подключены к выходам соответственно седьмого и восьмого элементов ИЛИ, вторые входы основных элементов И, относящихся к одноименным разрядам первого и второго регистров сдвига, попарно объединены и совместно с синхронизирующими входами первого и второго регистров сдвига являются четвертым входом блока выравнивания, первым, вторым, третьим пятым,шecтым, и восьмым входами которого являются соответственно первый вход пятого дополнительного элемента И, первый вход : одиннадцатого дополнительного элемента И, вход третьего элемента HEt первый 1вход четвертого дополнйтельного элемента И, второй вход десятого дополнительного элемента И, первый вход третьего дополнительного элементам ивторой вход девятого допап нительного элемента И,первым, вторын, тр ет ьим и чет вертым выходами блок а выравнивания являются соответственно вы ходы четвертого,десятого,третьего и девятого элементов Н)Ш,

1 1

Изобретение относится к технике связи и может быть использовано в системах передачи дискретной информа1ЦШ.

По основному авт.св. № 919109 известно двухканальное устройство ретрансляции дискретных сигналов, содержащее первьй блок приема, выход которого подключен к объединенным первому входу первйго блока оценки и входу первого решающего блока, второй блок приема, выход которого подключен к объединенным первому входу второго блока оценки и входу второго решакщего блока, блок сравнения .и первый и второй блоки передачи, первые выходы первого и второго решающих блоков подключены ко вторым входам соответсгвенно первого и второго блоков оценки, выходы которых соответственно через первый и второй элементы И подключены к управлякщим входам Соответственно первого и второго элементов запрета, выходы которых подклйчены ко йходам соответственно первого и второго блоков передачи,- а вторые выходы первого И второго решающих блоков подключеньг соответственно к cиfнaльнoмy входу первого элемента зап|рета, объединенному с первым входом блока сравнения, к к сигнальному входу втЪрого элемента запрета, объединенному со вторым входом блоКа сравнения, выход которого подключен к объединенным вторым входам первого и второго элементов И, выхода KoTopbix через соответствующие последовательно соединеннью элемент НЕ, элемент И-НЕ и дополнительньй элемент запрета соединены с .первыми входами соответствующих элементов ИЛИ, выхода которых соединены с входами блоков передачи, решающих блоков, соединены с другими входами соответствующих дополнительных элементов, запрета, вторые входа элементов ИЛИ соединены с выходами элемента, запрета Щ.

Однако это устрбйство обладает недостаточной точностью при работе с каналами связи, имеющими различное время распространения электрических сигналов.

Цель изобретения - повышение точности при работе с каналами связи, имеющими различное время распространения электрических сигналов.

191862

Указанная цель достигается тем, что в двухканальное устройство ретрансляции дискретньк сигналов, содержащее первый блок приема, выход 5 которого подключен к объединенным первому входу первого блока оценки и входу первого решающего блока, второй блок приема, выход которого подключен к объединенным первому вхоtO ду второго блока оценки и входу второго решающего блока, блок-сравнения ,и первый и второй блоки передачи, первые выходы Первого и второго решаклцих блоков подключены ко вторым

15 входам соответственно первого и

второго блоков оценки, выходы котоpbix соответственно через первый и второй элементы И подключены к управ ляющим входам соответственно первого

20 и второго элементов запрета, выходы которых подключе ны ко входам соответственно первого и второго блоков i передачи, а вторые выходы первого и второго решающих блоков подключены

25 соответственно к сигнальному входу первого элемента запрета, объединенному с первым входом блока сравнения и к сигнальному входу второго элемента запрета, объединенному со вторым

0 входом блока сравнения, выход которого подключен к объединенным вторым входам первого и второго элементов И, выхода которых через соответствукщие последовательно соединенные

- элемент НЕ, элемент И-НЕ и дополнительный элемент запрета соединены с первыми входами соответствующих элементов.ИЛИ, выходы которых соединены с входами блоков передачи, вы Q ходы решаквцих блоков соединены с

другими входами соответствующих дополнительных элементов запрета, вто;рые входа элементов ИЛИ соединены с выходами Элемента запрета, введены

5 блок выравнивания, блок определения интервала выравнивания и два дешифратора фазирующей комбинации, ды которых соединены с соответствую-,

:щими входами блока определения ии0 тервала выравнивания, первый, вто|рой, третий и четверть й вьпсоды которого подключены соответственно к первому, второму, третьему и четвёртому входам блока выравнивания, при 5 чем выходы блоков оценки подключены

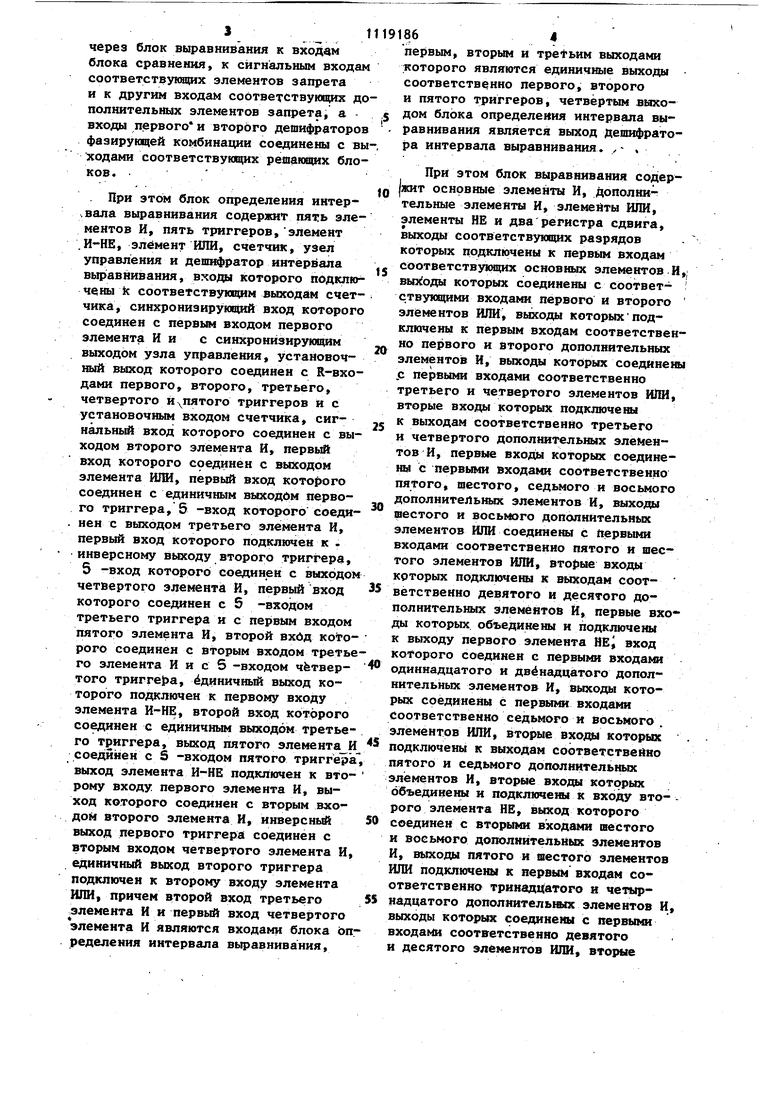

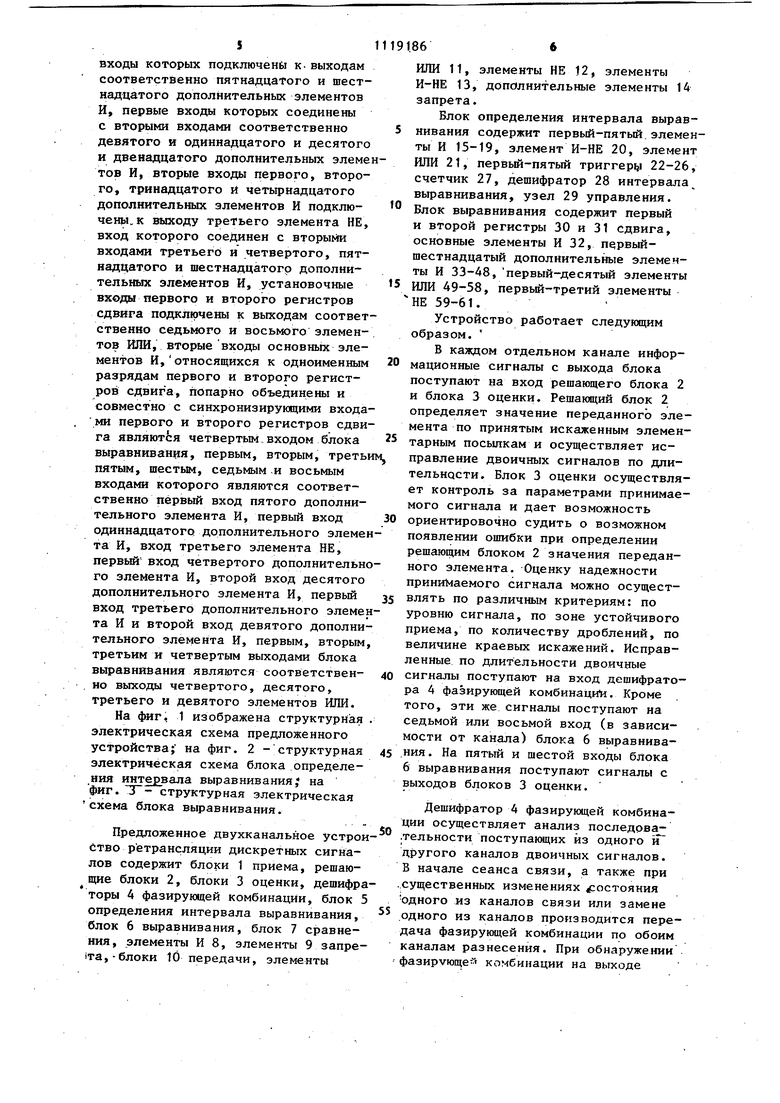

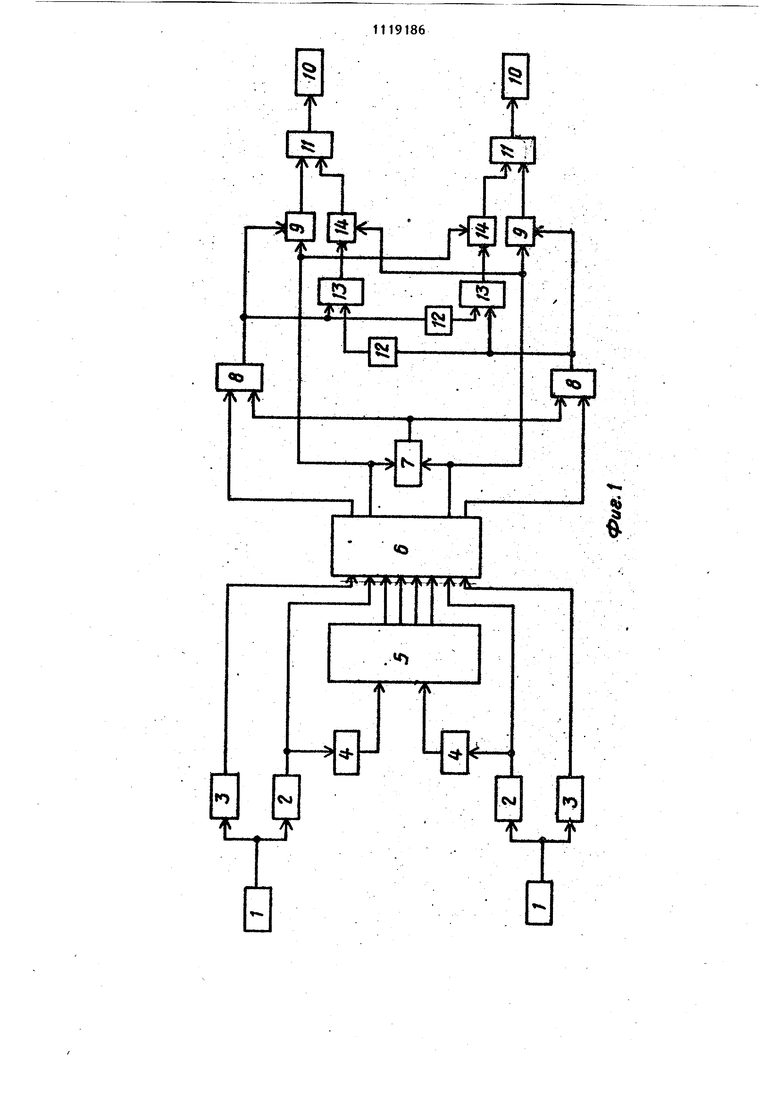

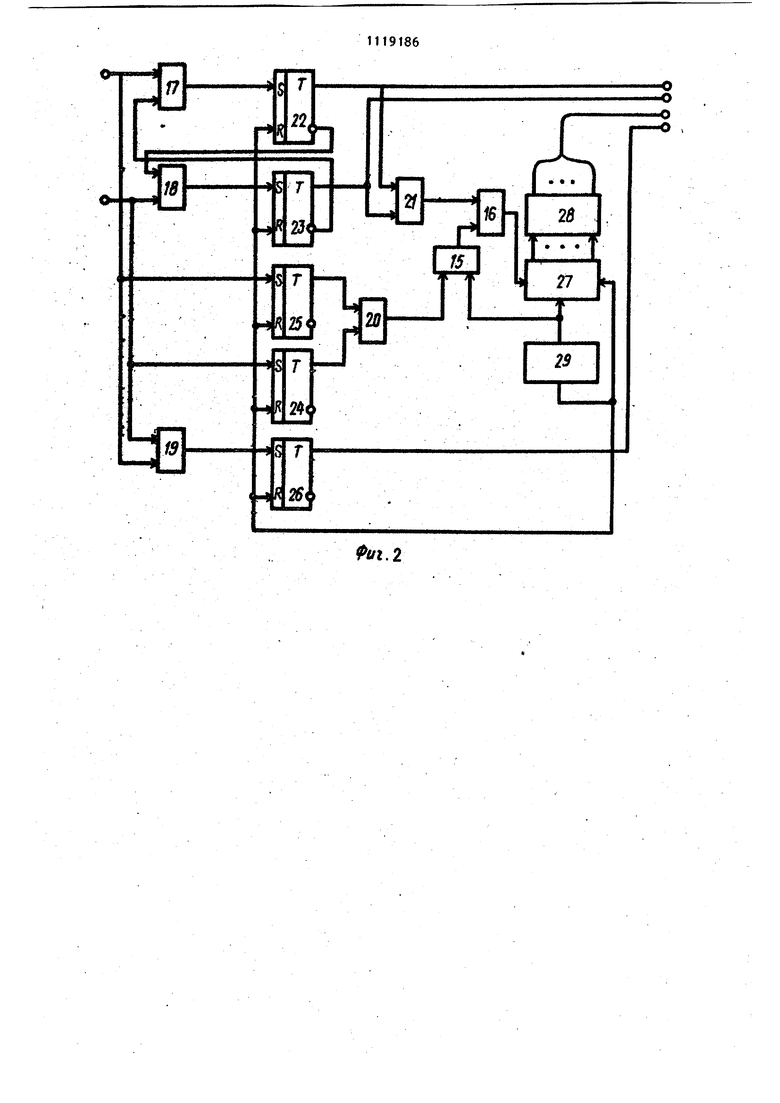

через блок-вьфавнивания к первым -входам соответствующих элементов И, , выходы решающих блоков подк.пючены через блок выравнивания к входам блока сравнения, к сигнальным входам соответстэуклцих элементов запрета и к другим входам соответствуючих до полнительных элементов запрета, а входы первого и второго дешифраторов фазирующей комбинации соединены с вы ходами соответствующих решающих блоков. . При этом блок определения интер.вала выравнивания содержит пя1гь элементов И, пять триггеров,элемент .И-НЕ, элемент ИЛИ, счетчик, узел управления и дешифратор интервала выравнивания, входы которого подклк чены k соответствующим выходам счетчика, синхронизирующий вход которого соединен с первым входом первого элемента Ни с синхронизирующим выходом узла управления, установочный выход которого соединен с R-BXOдами первого, второго, третьего, четвертого и пятoгo триггеров и с установочным входом счетчика, сигнальный вход которого соединен с выходом второго элемента И, первый вход которого соединен с выходом элемента ШШ, первый вход которого соединен с единичным выходом первого триггера, 5 -вход которого соединен с выходом третьего элемента И, первый вход которого подключен к . инверсному выходу второго триггера, 5 -вход которргЬ соединен с выходом четвертого элемента И, первый вход которого соединен с 5 -входом третьего триггера и с первым входом пятого элемента И, второй вхОд которого соединен с вторым входом третье го элемента И и с 5 -входом четвертого триггера, единичный выход которого подключен к первому входу элемента И-НЕ, второй вход которого соединен с единичным выходом третьего триггера, выход пятог о элемента И соединен с S -входом пятого триггера выход элемента И-НЕ подключен к второму входу первого элемента И, выход которого соединен с вторым входом второго элемента И, инверсный выход первого триггера соединен с вторым входом четвертого элемента И, единичный выход второго триггера подключен к второму входу элемента ИЛИ, причем второй вход третьего элемента И и первый вход четвертого элемента И являются входами блока Оп ределения интервала выравнивания. первым, вторым и трефьим выходами которого являются единичные выходы соответственно первого, второго и пятого триггеров, четвертым выходом блока определения интервала выравнивания является выход дешифратора интервала выравнивания. , , При этом блок выравнивания содер жит основные элементы И, дополни тельные элементы И, элементы ИЛИ, элементы НЕ к дварегистра сдвига, выходы соответствующих разрядов которых подключены к первым входам соответствующих основных элементов И,, выводы которых соединены с соответ- ; ствующими входами первого и второго элёьюнтов ИЛИ, вюсоды которыхподключены к первым входам соответственно первого и второго дополнительных элементов И, выходы которых соединены .с первыми входами соответственно третьего и четвертого элементов ШШ, вторые входы которых подключены к выходам соответственно третьего и четвертого дополнительных элементов И, первые входы которых соединены с первыми входами соответственно пятого, шестого, седьмого и восьмого дополнительных элементов И, выходы шестого и восьмого дополнительных элементов ИЛИ соединены с тервыми входами соответственно пятого И шестого элементов ИЛИ, вторые входы которых подключены к выходам соотвётственно девятого и десятого дополнительных элементов И, первые входы которых объединены и подключены к выходу первого элемента HEi вход которого соединен с первыми входами одиннадцатого и двенадцатого дополнительных элементов И, выходы которых соединены с первыми входами соответственно седьмого и восьмого . элементов ИЛИ, вторые входы которых подключены к выходам соответствеЯно пятого и седьмого дополнительных элементов И, вторые входа которых 6бъединеш 1 и подключены к входу вто-. рого элемента НЕ, выход которого соединен с вторы а1 выходами шестого и восьмого дополнительных элементов И, выходы пятого и шестого элементов ИЛИ подключены к первым входам соответственно тринадцатого и четырнадцатого дополнительных элементов И, выходы которых соединены с первыьш входами соответственно девятого и десятого элементов ИЛИ, вторые входы которых подключены к-выходам соответственно пятнадцатого и шестнадцатого дополнительных элементов И, первые входы которых соединены с вторыми входами соответственно девятого и одиннадцатого и десятого и двенадцатого дополнительных элеме тов И, вторые входы первого, второго, тринадцатого и четьфнадцатого дополнительных элементов И подключены, к выходу третьего элемента НЕ, вход которого соединен с вторыми входами третьего и четвертого, пятнадцатого и шестнадцатого дополнительных элементов И, установочные входы первого и второго регистров сдвига подкл1очены к выходам соответ ственно седьмого и восьмого элементов PfflH, вторые входы основных элементов И,относящихся к одноименным разрядам первого и второго регистров сдвига, попарно объединены и совместно с синхронизирующими входа ми первого и второго регистров сдви га являются четвертым-ВХОДОМ блока выравнивания, первым, вторым, треть пятым, шестым, седьмым и восьмым входами которого являются соответственно первый вход пятого дополнительного элемента И, первый вход одиннадцатого дополнительного элеме та И, вход третьего элемента НЕ, первый вход четвертого дополнительн го элемента И, второй вход десятого дополнительного элемента И, первый вход третьего дополнительного элеме та И и второй вход девятого дополни тельного элемента И, первым, вторым третьим и четвертым выходами блока выравнивания являются соответственно выходы четвертого, десятого, третьего и девятого элементов ИЛИ. На фиг, 1 иэображена структурная электрическая схема предложенного устройства; на фиг. 2 - структурная электрическая схема блока .определения выравнивания, на фиг. ЭГ- структурная электрическая схема блока выравнивания. Предложенное двухканальное устро ство ретрансляции дискретных сигналов содержит блоки 1 приема, решающие блоки 2, блоки 3 оценки, дешифр торы 4 фазирующей комбинации, блок определения интервала выравнивания, блок 6 выравнивания, блок 7 сравнения, элементы И 8, элементы 9 запре 1та,-блоки 10 передачи, элементы ИЖ 11, элементы НЕ 12, элементы И-НЕ 13, дополнительные элементы 14 запрета. Блок определения интервала выравнивания содержит первый-пятый. элементы И 15-19, элемент И-НЕ 20, элемент ИЛИ 21, первый-пятый триггеру 22-26, счетчик 27, дешифратор 28 интервала выравнивания, уэел 29 управления. Блок выравнивания содержит первый и второй регистры 30 и 31 сдвига, основные элементы И 32, первыйшестнадцатый дополнительные элементы И 33-48, первый-десятый элементы ИЛИ 49-58, первый-третий элементы НЕ 59-61. Устройство работает следующим образом. В каждом отдельном канале информационные сигналы с выхода блока поступают на вход решающего блока 2 и блока 3 оценки. Решающий блок 2 определяет значение переданного элемента по принятым искаженным элементарным посылкам и осуществляет исправление двоичных сигналов по длительности. Блок 3 оценки осуществляет контроль за параметрами принимаемого сигнала и дает возможность ориентировочно судить о возможном появлении ошибки при определении решающим блоком 2 значения переданного элемента. Оценку надежности принижаемого сигнала можно осуществлять по различным критериям: по уровню сигнала, по зоне устойчивого приема, по количеству дроблений, по величине краевых искажений. Исправленные по длительности двоичные сигналы поступают на вход дешифратора 4 фазирующей комбинаций. Кроме того, эти же сигналы поступают на седьмой или восьмой вход (в зависимости от канала) блока 6 выравнива.ния. На пятый и шестой входы блока 6 выравнивания поступают сигналы с выходов блоков 3 оценки. Дешифратор 4 фазирующей комбинации осуществляет анализ последова.тельности поступающих из одного iT другого каналов двоичных сигналов. В начале сеанса связи, а также при .существенных изменениях ростояния одного из каналов связи или замене .одного из каналов производится передача фазирующей комбинации по обоим каналам разнесения. При обнаружении фазирующей комбинации на выходе дешифратора 4 фазирующий комбинации появляется сигнал 1, который посту пает на один из входов блока 5 определения интервала выравнивания.. Этим переводится в состояние Г или триггер 2А или триггер 25. В исходном состоянии все триггеры 22-26 устанавливаются в состояние О узлом 29 управления. В момент прихода от дешифратора 4 фазирующий )сомбина1 и сигнала 1 на одном из входов элементов И 17, 18 уже присут ствует сигнал 1 с инверсного выхода соответственно триггеров 22 и 23. G приходом сигнала 1 от дешифратора 4 фазирующей комбинации через соответствующий элемент И 17 или 18 сигнал 1 поступает на @ -вход триггера 22 или триггера 23 Каац/аЦМ из этих триггеров 22 и 23 совтввфствует одному из разнесенных КанвоЕов, и переход его в состояние 1 вэиачает, что соответствукшщй канал связи короче другого канала ичто одия и тот же сигнал в этом канале иэступает раньше, Чем в друго Допус чда, что сигнал 1 от дершфратора 4 фазирующей комбинации поступил на элемент И 17 И перевел в состоя1ше 1 триггер 22. Тогда на инверсном выходе этого триггера 22 сигнал 1 исчезает, и на один вход элемента И 18 подается сигнал О. Теперь второй триггер 23 остается в нулевом состоянии и после прихода сигнала 1 от дешифратора фазирующей комбинации на вход элеме та 18 И. Сигнал с единичного выхода трягг ра 22 поступает на первый выход блока 5 определения интервала выравнивания и на первый вход элемента ИЛИ 21. Так как один из триггеров 24, 25 .переведен сигналом от дешифратора 4 фазирующей комбинации в состояние 1, то на выходе элемента Н-ЙЕ 20 появляется сигнал 1, который пода ся на второй вход элемента И 15. На первый вход элемента И 15 поступают синхроимпульсы от узла 29 упра ления. В результате с момента посту ления фазирующей комбинации по одно му из каналов синхроимпульсы начина ют поступать на второй вход элемента И 16, на первый вход которого по дается сигнал 1 от одного иэ триг геров 22 или 23. Таким образом, на вход счетчика 27 начинают поступать синхроимпульсы. С поступлением фазирующей комбинации по второму каналу разнесения, электрическая длина которого больше ,и сигналы в котором запаэдашают на интервал д , приводится fe состояние 1 один иэ триггеров 24, 25, который ранее был в состоянии 0. Теперь на обоих входах элемента И-НЕ 20 присутствует сигнал -Ч и на выходе вырабатывается сигнал О, который прекращает поступление синхроимпульсов рт УЭла 29 управления через элемент И 15 на второй вход элемента И 16. Синхроимпульсы перестают поступать на счетчик .27, и в нем теперь сохраняется число, соответствующее длительности интервала йС, Содержимое счетчика 27 подается на дещифратор 28 интервалов выравнивания. На соответствующем выходе дещифратора вырабатывается сигнал 1. Таким образом, в результате описанных процессов появляется сигнал на первом или втором выходе блока 5 определения интервала выравнивания (в.зависимости от того, какой канал имеет меньшую электрическую длину). При одновременном поступлений фазирующих комбинаций по обоим каналам дешифраторы 4 фазирующей комбинации вьфабатывают сигналы 1, которые одновременно переводят в состояние Т триггеры 24, 25. Тогда счетчик 27 остается в нулевом состоянии (синхроимпульсы на него не поступают). На выходе элемента И 19 появляется сигнал, переводящий в состояние 1 триггер 26. На третьем выходе блока 5 определения интервала выравнивания появляется сигнал 1, что является признаком синхронного поступления сигналов по обоим каналам разнесения. Работу блока 6 выравнивания и взаимодействие его с другими элементами рассмотрим отдельно для двух случаев: первый случай - каналы разнесения имеют разную электрическую длйну второй случай - каналы разнесения имеют одинаковую электрическую дпину. В первом случае на первый либо второй вход блока 6 выравнивания подается сигнал 1 с первого либо второго сигнального выхода блока 5 определения интервала выравнивания, 9 Пусть более короткую электрическую длину имеет первьА канал разнесения Тогда сигнал 1 появляется на первом выходе блока 5 определения интервала выравнивания и поступает на первый вход блока 6 выравнивания Этот сигнал поступает на второй вхо элемента И 37 и на второй вход элемента И 39. На первый вход элемента И 37 подается с седьмого входа блока 6 выравнивания исправленный по длительности двоичный сигнал от решающего блока 2 первого канала. Этот сигнал .через элемент И 37 пост пает на второй вход элемента ШШ 55 На первый вход элемента И 39 под ется сигнал от блока 3 оценки перво го канала. Этот сигнал через элемен И 39 поступает на второй вход эле-, мента ИЛИ- 56. На первый вход элемента И 43 с второго входа блока 6 выравнивания подается сигнал О, поступающий со второго выхода блока 5 определения интервала выравнивания. Поэтому поступаюпщй на второй вход элемента И 43 и восьмого входа блока 6 выравнивания сигнал от решающего блока 2 второго канала через элемен И 43 не проходит. Поэтому на выходе элемента ИЛИ 55 появляется исправленный по длительности двоичный сигнал от решающего блока 2 первого канала. На первый вход элемента И 44 .подается нулевой сигнал с второго входа блока 6 выравнивания. На втор вход элемента И 44 с шестого входа блока б выравнивания подается сигна от блока 3 оценки второго канала. Поэтому на первый вход элемента ИЛИ 56 поступает сигнал только от блока оценки первого канала. Если же первой принимается фазирующая, комбинация по второму каналу разнесения, то сигналы от решающего блока 2 и блока 3 оценки этого канала через элементы И 43 и 44 поступают на первые входы элементов ИЛИ 55 и 56 соответственно. Таким образом, на выходе элементов ШШ 55 и 56 появляются сигналы соответственно от решающего блока 2 и блока 3 оценки канала, электричес кая длина которого короче. Двоичные сигналы с выходов элеме тов ШШ 55 и 56 и подаются на установочные входы соответственно регис 8610 ра jjO сдвига и регистра 31 сдвига; Регистр 30 сдвига используется для задержки на интервал вьфавнивания 42 двоичных сигналов. от решающего блока 2 канала с меньшей электрической длиной, а регистр сдвига 31 для задержки на двоичных сигналов от блока 3 оценки этого же канала. -На запараллельные синхронизирующие входы регистров сдвига подаются синхроимпульсы по многоканальной соединительной линии между коммути1рующим четвертым выходом блока 5 определения интервала выравнивания и i четвертым входом блока 6 выравнивания. В такт с этими синхроимпульсами происходит сдвиг сигналов в регистрах 30 и 31 сдвига. В соответствии с il по одному .из каналов выхода блока 5 определения интервала вьфавнивания в блок 6 поступает сигнал 1 от дешифратора 28 интервала вьфавнивания, который поступает на вторые входы двзпс элементов И 32, у одного из которых первый вход соединен с выходом f -го разряда регистра 30 сдвига, а у другого первый вход соединен с выходом 1 -го разряда регистра 31 сдвига. Тогда на одном входе элемента ШШ 49 появляется двоичный сигнал с выхода решающего блока 2, задержанный на интервал выравнивания , а на одном входе элемента ИЛИ 50 - двоичный сигнал с выхода блока 3 оценки, задержанный на такой же интервал. Если электрическая длина первого .канала разнесения меньше, то сигнал от решающего блока 2 этого канала не про}содит через элемент И 38, поскольку на второй вход этого же элемента подается от элемента НЕ 60 сигнал О, Этот же сигнал О подается и на второй вход элемента И 40, что дает возможности пройти через этот элемент сигналу с выхода блока 3 оценки этого же канала. В то же время на первых входах элементов 41 и 42 находится сигнал 1 (с второго входа блока 6 вьфавнивания, соединенного со вторым выходом блока 5 определения интервала вьфавнивания, подается О), который инвертируется элементом НЕ 59. Поэтому через элемент И 4t проходит сигнал of реша1(хцего блока 2 {(анала большей . электрической длины, а через элемент И 42 - сигнал от блока 3 оценки этого же канала. Эти сигналы поступают на входы и появляются на выход элементов ИЛИ 53 и 54. Таким образом, на выходах элементов ИЛИ 4.9 и 50 блока 6 выравниванияпоявляютс задержанные на интервал выравнивани сигналы одного канала, а на выходах элементов ИЛИ 53 и 54 - незадержанные сигналы второго канала, т.е. электрические длины обоих каналов искусственно выравниваются и одновр менно появляющиеся .на выходах этих Элементов сигналы соответствуют одному и тому же переданному и принятому двоичному элементу. Сигнал с выхода элемента ИЛИ 49 подается на первый вход элемента И 33. Сигнал с выхода элемента ИЛИ подается на первый вход элемента И 34. На вторые входы элементов И 33 и 34 подается инвертированный элементом НЕ 61 сигнал с третьего выхода блока 5 определения интервала выравнивания, т.е. с третьего входа блока 6 выравнивания. При раз ной электрической длине каналов раз . несения на третьем выходе блока 5 оп1зеделения интервала выравнивания вырабатывается сигнал О, на выходе элемента .НЕ 61 будет сигнал 1 и сигналы с выходов элементов ИЛИ 49 и 50 проходят череэ элементы И 33 и 34 на выходы элементов ИЛИ 51 h 52 соответственно. Аналогичным образом сигналы с вьлходов элементов ИЛИ 53 и 54 прохо дят на выходы элементов ИЛИ 57 и 58 Во втором с-пучае, т.е. при син.хронном поступлении фазирующей комбинации по обоим каналам, на третье выходе блока 5 определения интервала вьфавнивания пбявляетея сигнал 1. Этот же сигнал на третьем вход блока 6 выравнивания, инвертированный элементом НЕ 61, запрещает про, ход сигналов от элементов ИЛИ 49, 5 53 и 54 соответственно через элементы И 33, 34, 45, 46. Одновременно этот сигнал с третьего входа блока 6 выравнивания позволяет прой через элементы И 35, 36, 47 и 48 соответственно сигналам от решающего блока 2 первого канала, от блока 3 оценки первого канала, от решающего блока 2второго канала и от блока 3 оценки второго канала, мину элементы блока 6 выравнивания, обес печивающие задержку сигналов. Таким образомi как при разной, так и лри одинаковой электрической длине Каналов разнесения на выходах элементов ИЛИ 51, 52, 57 и 58, одно-г временно являющихся соответственно третьим, первым, четвертым и вторым .выходами блока 6 выравнивания, появ ляются сигналы, соответствующие одному и тому же переданному по каналам разнесения сигналу. Дальнейшая обработка принятьк по каналам разнесения информационных сигналов происходит так же, как в известном устройстве fij . Исправленные решающим блоком 2 по длительности двоичные сигналы одного канала третьего выхода, блока 6 поступают на одий из входов блока 7 сравнения, на другой вход которого поступают исправленные решающим блоком 2 другого канала по Длительности двоичные Сигналы с чётвepтo o выхода блока 6 вьфавнивания. Принятые на йходы блока 7 сравнения сигнал ошибки отсутствует (0), в противном случае на вход элемента И 8 вьщается с блока 7 сравнения сигнал ошибки (1). Одновременно управляющий сигнал с выхода блока 3 оценки, который осуществляет оценку надежности принятого сигнала в соответствии р принятым критерием (по Зфовню принятого сигнала, по зоне устойчивого приема, по количеству дроблений и т.д.), через блок 6 выравнивания и его первый выход поступает на другой вход элемента И 8, выход которого соединен с управляющим входом элемента 9 запрета подключения выхода блока 1 приема на вход блока 10 передачи через элемент ИЛИ 11. С выхода элемента, И 8 другого канала инвертированный с помощью элемента НЕ 12 сигнал подается на один из входов элемента ИгНЕ 13, на другой вход которого подается сигнал с выхода элемента И 8 данного канала. С элемента И-НЕ 13 сигнал подается на управЛЯ10ЩИЙ вход элемента 14 запрета, на информационнь1й вход которого подаются исправленные по длительности двоичные сигналы с выхода решающего блока 2 другого канала. Выход элемента 14 запрета через элемент ИЛИ 11 соединен со входом блока 10 передачи.

Если сигнал, переданный на разнесенных частотах, принят в каждом канале правильно, то на выходе блока 7 сравнения и блока 3 оценки ошиб ки отсутствует и не вьщается на вход элемента 9 запрета сигнал блокировки информационного выхода блока 1 приема на вход элемента ИЛИ 11. На входе элемента И-НЕ 13 каждого канала, соединенного с выходом элемента И 8 данного канала, будет сигнал О, а на другом входе элемента И-НЕ 13, соединенного через элемент И-НЕ 13 с выходом элемента И 8 другого канала, будет сигнал 1 На выходе элемента И-НЕ 13 в этом случае появляется запрещенный сигнал 1, поступающий на вход элемента 14 запрета, и выход блока 1 приема другого канала на вход блока 10 передачи данного канала блокируется.

Если в одном из каналов разнесения СНГНШ1 принят неправильно, то на выходе блока 7 сравнения и блока 3 оценки данного канала появляется сигнал ошибки. С выхода элемента И 8 данного канала на вход его элемета 9 запрета поступает сигнал блокировки выхода блока 1 приема данного канала на вход его блока 10 передачи, Этот же сигнал подается на один вход элемента И-НЕ 13 данного канала; В это же время на выходе элемен та И 8 другогб канала будет сигнал , О, в результате инвертирования которого на второй вход элемента И-НЕ 13 поступает сигнал 1. На выходе элемента И-ЯЕ 13 вырабатьшается сигнал О, поступающий на управляющий вход элемента 14 запрета. В результате через элемент 14 запрета и элемент ИЛИ 11 на вход блока 10 передачи канала, в котором сигнал

принят неправильно, подается сигнал принятый во втором канале.

В случае, когда в обоих каналах блоки 3 оценки вырабатывают сигнал ошибки, но значения принятого в обоих каналах сигнала совпадают, на вы:ходе блока 7 сравнения сигнал ошибки не появляется. На входах элемента И-НЕ 13 в каждом канале сигналы противоположны, на выходе элемента И-НЕ 13 появляется сигнал 1, который поступает на управляющий вход элемента 14 запрета данного канала, и на вход-блока каждого канала подключается выход блока 1 приема этого же канала.

Наконец, если в одном из каналов блок 3 о11енки вырабатывает сигнал ошибки, а значения сигналов в обоих каналах совпадают, на выходе блока 7 сравнения сигнал ошибки не появляется. На входах- элемента И-НЕ 13. в каждом канале сигналы противоположны и в каждом канале на вход блока 10 передачи переключается выхо блока 1 приема этого же канала.

Введение в двухканальное устройство ретрансляции новых блоков позволяет обеспечить ретрансляцию дискретной информации при разной электрической длине каналов разнесения за счет синхронизации обработки сигналов, поступающих по двум каналам разнесения. В результате при сохранении уровня достоверности инфомации, обеспечиваемого известным устройством, расширяется область применения двухканального устройства и оно может использоваться с каналами связи разной электрической длины, в том числе и с проводящей средой разной физической природы например, один канал разнесения Может быть каналом ТЧ, а другой .радиоканалом KB диапазона.

t/i.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронного радиоприема частотноманипулированных сигналов | 1985 |

|

SU1275787A1 |

| Способ формирования частотно-импульсных сигналов датчика перемещения и устройство для его осуществления | 1976 |

|

SU905993A1 |

| Устройство контроля состоянияКАНАлА СВязи | 1979 |

|

SU809594A1 |

| Импульсный преобразователь перемещения | 1981 |

|

SU985808A1 |

| Устройство для измерения расстояния между центрами интерференционных полос интерферограмм | 1988 |

|

SU1677877A1 |

| Система выравнивания сигналов | 1977 |

|

SU699327A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ КОММУТАЦИИ КАНАЛОВ | 2007 |

|

RU2341046C1 |

| Двухканальное устройство ретрансляции дискретных сигналов | 1981 |

|

SU987831A1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| Устройство для моделирования систем "человек-машина | 1982 |

|

SU1038948A1 |

1. ДВУХКАНАЛЬНОЕ УСТРОЙСТВО РЕТРАНСЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ по авт.св. № 919109, отличающееся тем, что, с целью повьше- . ния точности при работе с каналами связи, имеющими различное время распространения электрических сигналов, в него введены блок выравнивания, блок определения интервала выравнивания и два дешифратора фазирующей комбинации, выходы которых соединены с соответствукмцими входами блока определения интервала выравнивания, первый, второй, третий н четвертый выходы которого подключены соответственно к первому, второму, третьему и четвертому входам блока вьфавнивания, причем выходы блоков оценки подключены через блок выравнивания к первым входам соответствующих элементов И, выходы решающих блоков подключены через блок выравнивания к входам блока сравнения, к сигнальным входам соответствующих элементов запрета и к другим входам соответствующих дополнительных элементов запрета, а входы первого и второго дешифраторов фазирующей комбинации соединены с выходами соот- . ветствующих решающих блоков. 2. Устройство по п. 1, отличающееся тем, что блок определения интервала выравнивания содержит пять элементов И, пять триггеров, элемент И-НЕ, элемент ИЛИ, счетчик, узел управления и дешифратор интервала выравнивания, входы которого подключены к соответствующим выходам счетчика, синхронизирующий вход которого соединен с первым входом первого элемента И и с синхронизирующим выходом узла управления, установочный выход которого соединен с К-Входами первого, второго, третьего, четвертого и пятого триггеров и с установочным входом счетчика, сигнальный вход которого, соединен с выходом второго ;элемента И, первый вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с единичным выходом первого триггера, 5 -вход которого соединен с выходом третьего элемента И, первый вход которого подключен к инверсному выходу второго Триггера, 5 -вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с 5 -входом третье го триггера и с первым входом пятоСО го элемента И, второй вход которого соединен с вторым входом третьего СХ) элемента И и с 5 -входом четвертов го триггера, единичный выход которого подключен к первому входу элемента И-НЕ, второй вход которого соединен с единичным выходом третьего триггера, выход пятого элемента И соединен с 5 -входом пятого триггера, выход элемента И-НЕ подключен к второму входу первого элемента И, выход которого соединен с вторым входом второго элемента И, инверсный . |выход первого триггера соединен с

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Двухканальное устройство ретрансляции дискретных сигналов | 1980 |

|

SU919109A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-10-15—Публикация

1983-07-18—Подача