сигналов в квадратурных каналах при сохранении разности фаз сигналов 90 . Со смесителей 4, 5 сигналы через соотв. фильтры 6, 7 нижних частот и усилители-ограничители 8, 9 поступают на блок 21 регистрации непосредственно и через соотв. элементы НЕ 12, 13 - на выделитель 14 тактовых импульсов и на соотв. элементы дифференцирования 10, 11. Выделитель 14 тактовых импульсов выделяет тактовые импульсы только при смене знака информационного сигнала Вьщеленные тактовые импульсы усредняются в блоке 15 тактовой .синхронизации. С его выхода последовательность тактовых импульсов, а также удвоенная и учетверенная последовательности поступают на формирователь 16 импульсов запрета, считывания и сброса. Формирователь 16 совместно с элементами И 17-20 формирует соотв. сигналы для блока 21 регистрации и формирователя 23 выходного сигнала. В результате анализа сигналов , поступающих в одном тактовом интервале, в блоке 21 регистрации производится регистрация трех решений о знаке принимаемого сигнала. Решающий блок 22 принимает окончателное решение о знаке информационного сигнала. 5 з.п. ф-лы, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Устройство синхронного радиоприема частотно-манипулированных сигналов | 1986 |

|

SU1327316A1 |

| Цифровой синтезатор частот | 1991 |

|

SU1803977A1 |

| Устройство для контроля работы оператора | 1989 |

|

SU1709370A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

| Устройство автоматической стабилизации амплитуды видеосигнала | 1990 |

|

SU1757124A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИНФОРМАЦИИ С ФОТОНОСИТЕЛЯ | 1991 |

|

RU2024941C1 |

| УСТРОЙСТВО ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2217791C1 |

| Устройство для вычисления временных интервалов микропроцессорных систем | 1980 |

|

SU960781A1 |

Изобретение может использоваться в цифровой радиорелейной связи и обеспечивает повышение помехоустойчивости . Частотно-манипулированный сигнал через усилитель 1 поступает на смесители 4, 5, на другие входы которых подаются сигналы гетеродина 2 в квадратуре (сдвинутые на 90 по фазе квадратурным направленным ответвителем 3). При изменении знака передаваемой цифровой информации происходит взаимное инвертирование (Л

Изобретение относится к радиосвязи и может быть использовано в цифровой радиорелейной связи.

Целью изобретения является повышение помехоустойчивости.

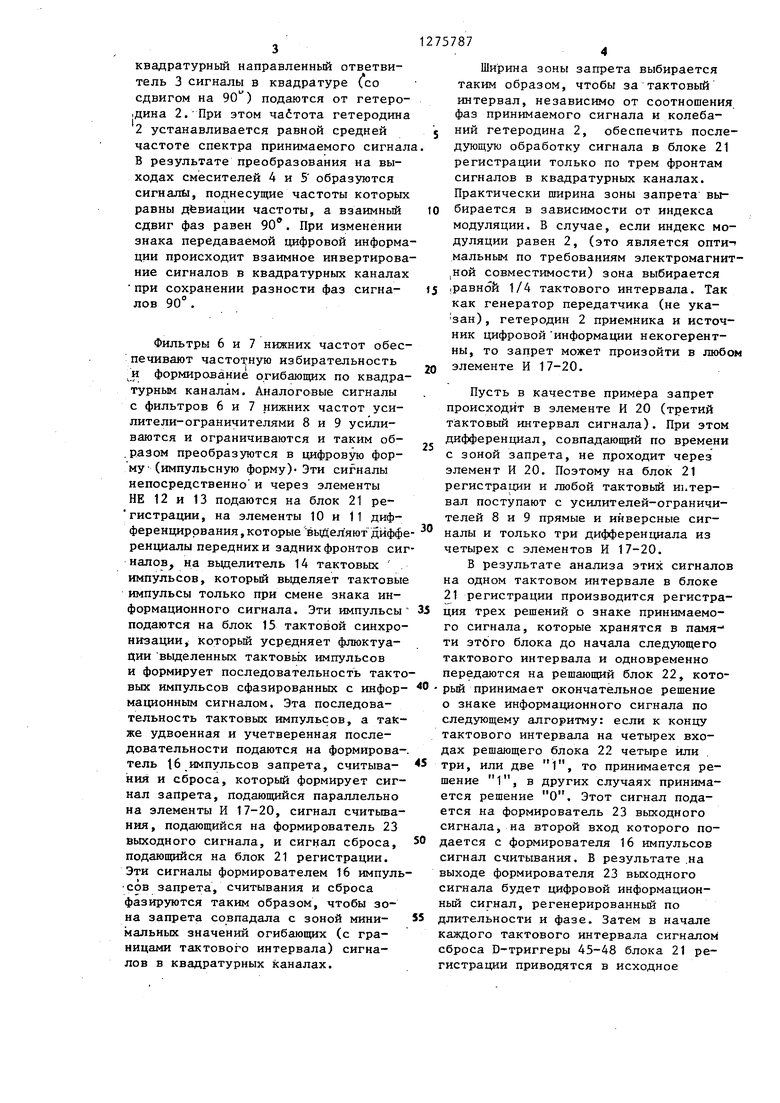

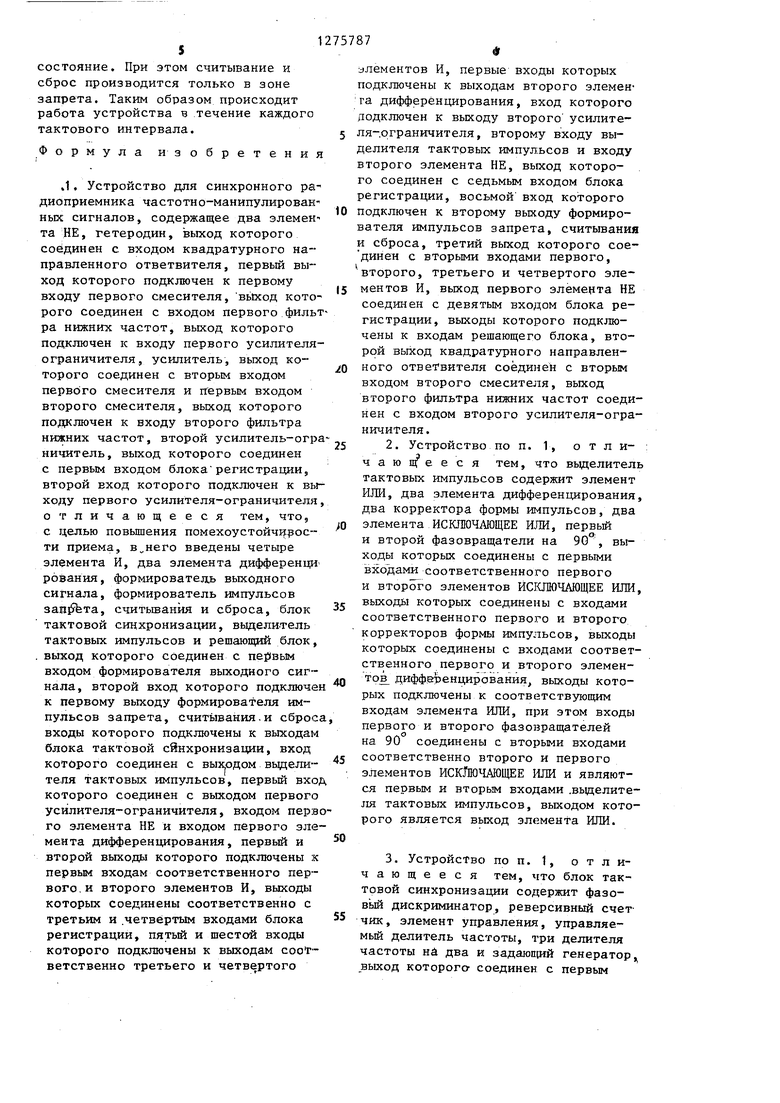

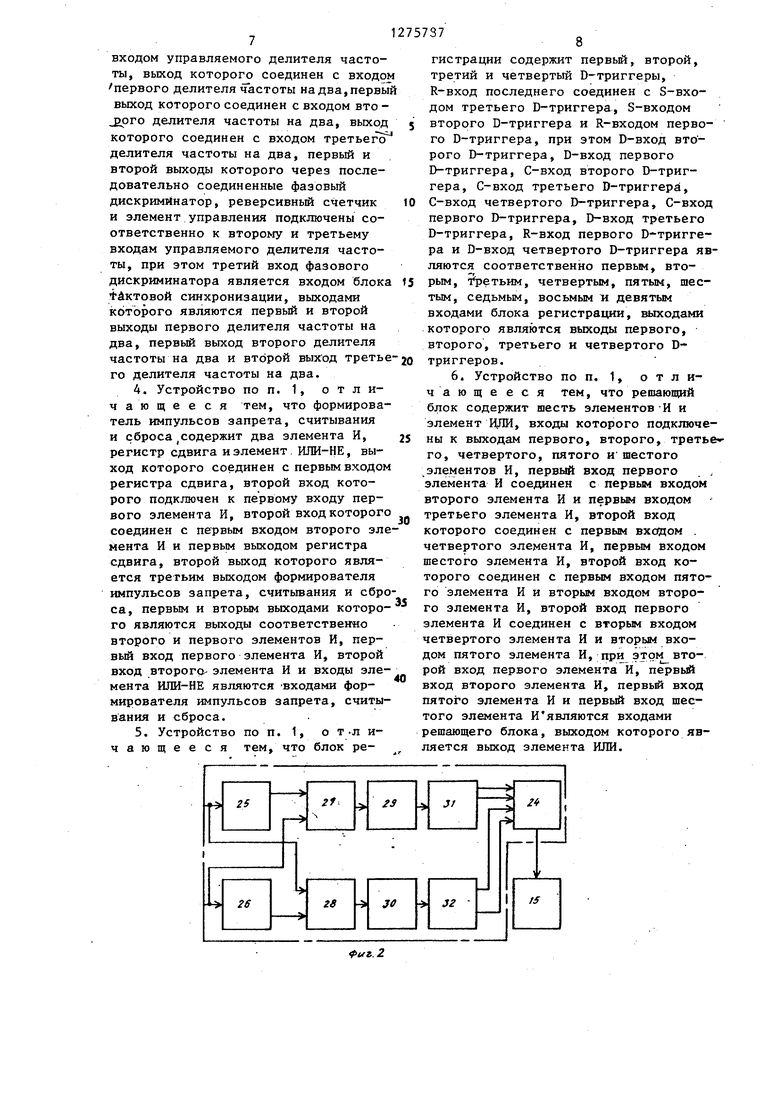

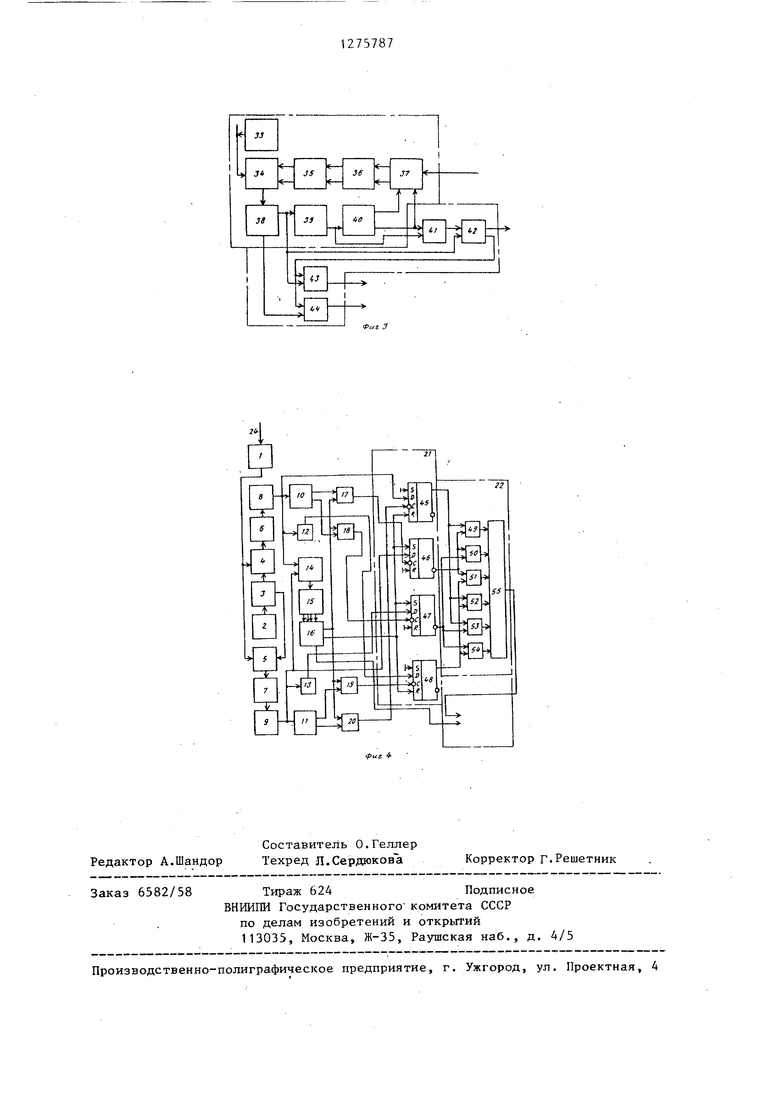

На фиг. 1 изображена структурная электрическая схема предложенного устройстваi на фиг. 2 - структурная электрическая схема выделителя тактовых импульсов, на фиг. 3 - структурная электрическая схема блока тактовой синхронизации и формирователя импульсов запрета, считывания и сброса/ на фиг. 4 - структурная электрическая схема блока регистрации и решающего блока.

Устройство для синхронного радио.цриемачастотно-манипулированных сигналов содержит усилитель 1, гетеродин 2 квадратурный направленньш ответвитель 3, первьш и второй смесители 4 и 5, первый и второй фильтры 6 и 7 нижних частот, первый и второй усилители-ограничители В и 9, первьй и второй элементы 11 и 12 дифференцирования, первьй и второй элементы НЕ 12 и 13, выделитель 14 тактовых импульсов, блок 15 тактовой синхронизации, формирователь 16 импульсов запрета, считывания и сброса первьй, второй, третий и четвертьй элементы И 17-20, блок 21 регистрации, решающий блок 22, формирователь 23 выходного сигнала.

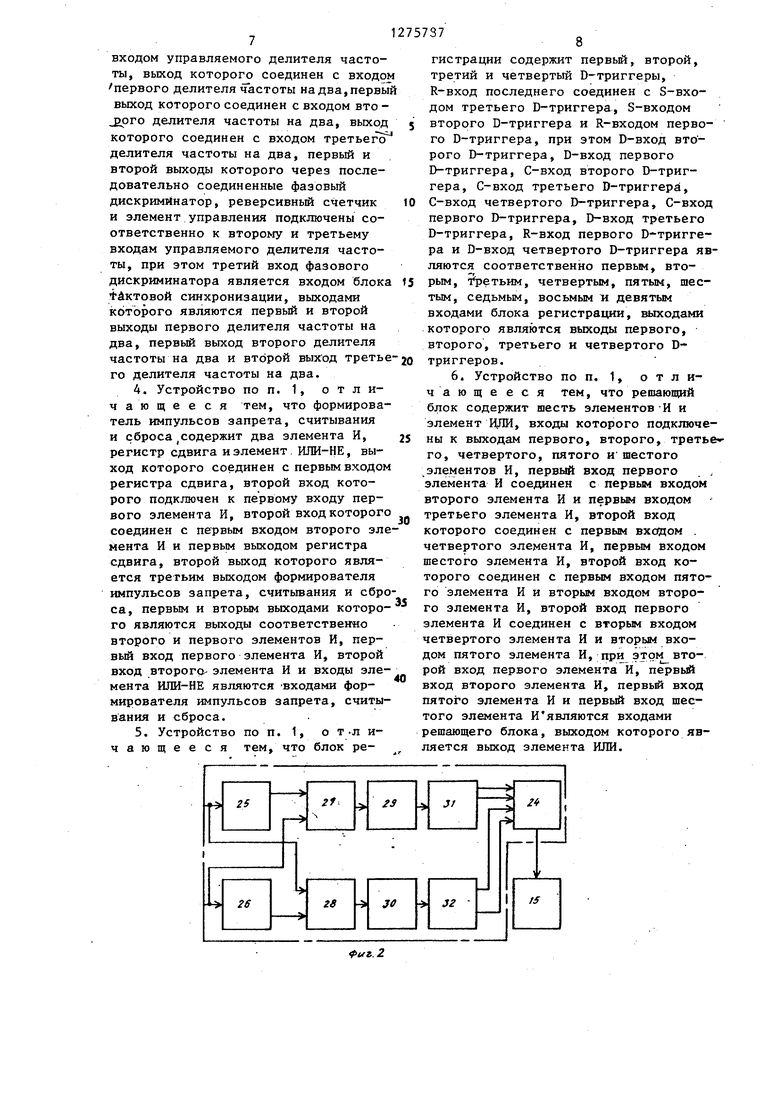

Вьщелитель тактовых импульсов содержит элемент ИЛИ 24, первьй и второй фазовращатели на 90° 25 и 26, первьй и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 27 и 28, первьй и второй корректоры 29 и 30 формы импульсов, первьй и второй элементы 31 и 32 дифференцирования.

Блок тактовой синхронизации содержит задающий генератор 33, управляемьй делитель 34 частоты, элемент

35 управления, реверсивньй счетчик 36, фазовьй дискриминатор 37, первьй, второй и третий делители 38-40 частоты на два.

Формирователь импульсов запрета,

0 считывания и сброса содержит элемент ИЛИ-НЕ 41, регистр 42 сдвига, первьй и второй элементы И 43 и 44. Блок регистрации содержит первый, второй, третий и четвертьй D-триггеры 45-48.

5 Решающий блок содержит первьй, второй, третий, четвертый, пятьй и шестой элементы И 49-54, и элемент ИЛИ 55.

Устройство работает следующим

Q образом.

Частотно-манипулированньй сигнал с входа устройства через усилитель 1 одНовременно подается на смесители 4 и 5. На эти же смесители через квадратурный направленный ответвите ль 3 сигналы в квадратуре (со сдвигом на 90) подаются от гетеро1дина 2.При этом чабтота гетеродина 2 устанавливается равной средней частоте спектра принимаемого сигнал В результате преобразования на выходах смесителей 4 и 5 образуются сигналы, поднесущие частоты которых равны девиации частоты, а взаимньй сдвиг фаз равен 90. При изменении знака передаваемой цифровой информа ции происходит взаимное инвертирова ние сигналов в квадратурных каналах при сохранении разности фаз сигналов 90°. Фильтры 6 и 7 нижних частот обес печивают частотную избирательность и формирование огибающих по квадра турным каналам. Аналоговые сигналы с фильтров 6 и 7 нижних частот усилители- ограничителями 8 и 9 усиливаются и ограничиваются и таким об.разом преобразуются в цифровзпо форму (импульсную форму)Эти сигналы непосредственно и через элементы НЕ 12 и 13 подаются на блок 21 регистрации, на элементы 10 и 11 дифференциррвания,которыевыйеляют дйфф ренциалы передних и задних фронтов сиг налов, на вьщелитель 14 тактовых . импульсов, который выделяет тактовые импульсы только при смене знака информационного сигнала. Эти импульсы подаются на блок 15 тактовой синхронизации, который усредняет флюктуации выделенных тактовьЬс импульсов и формирует последовательность такто вых импульсов сфазированных с информационным сигналом. Эта последовательность тактовых импульсов, а также удвоенная и учетверенная последовательности подаются на формирователь 16 импульсов запрета, считывания и сброса, который формирует сигнал запрета, подающийся параллельно на элементы И 17-20, сигнал считьшания, подающийся на формирователь 23 выходного сигнала, и сигнал сброса, подающийся на блок 21 регистрации. Эти сигналы формирователем 16 импуль сов запрета, считывания и сброса фазируются таким образом, чтобы зона запрета совпадала с зоной минимальных значений огибающих (с границами тактового интервала) сигналов в квадратурных каналах. Ширина зоны запрета выбирается таким образом, чтобы за тактовый интервал, независимо от соотношения фаз принимаемого сигнала и колебаний гетеродина 2, обеспечить последующую обработку сигнала в блоке 21 регистрации только по трем фронтам сигналов в квадратурных каналах. Практически ширина зоны запрета выбирается в зависимости от индекса модуляции. В случае, если индекс модуляции равен 2, (это является опти- мальным по требованиям электромагнит,ной совместимости) зона выбирается .равней 1/4 тактового интервала. Так как генератор передатчика (не указан), гетеродин 2 приемника и источник цифровой информации некогерентны, то запрет может произойти в любом элементе И 17-20. Пусть в качестве примера запрет происходит в элементе И 20 (третий тактовый интервал сигнала). При этом ифференциал, совпадающий по времени с зоной запрета, не проходит через элемент И 20. Поэтому на блок 21 регистрации и любой тактовый иктервал поступают с усилителей-ограничителей 8 и 9 прямые и инверсные сигалы и только три дифференциала из четырех с элементов И 17-20. В результате анализа этих сигналов на одном тактовом интервале в блоке 21 регистрации производится регистрация трех решений о знаке принимаемого сигнала, которые хранятся в памяти этого блока до начала следующего тактового интервала и одновременно передаются на решающий блок 22, который принимает окончательное решение о знаке информационного сигнала по следующему алгоритму: если к концу тактового интервала на четырех входах решающего блока 22 четыре или три, или две 1, то принимается решение 1, в других случаях принимается решение О. Этот сигнал подается на формирователь 23 вьпсодного сигнала, на второй вход которого подается с формирователя 16 импульсов сигнал считывания. В результате .на выходе формирователя 23 выходного сигнала будет цифровой информационный сигнал, регенерированный по длительности и фазе. Затем в начале каждого тактового интервала сигналом сброса D-триггеры 45-48 блока 21 регистрации приводятся в исходное 1 состояние. При этом считывание и сброс производится только в зоне запрета. Таким образом происходит работа устройства в течение каждого тактового интервала. Формула изобретения .1, Устройство для синхронного ра диоприемника частотно-манипулирован ных сигналов, содержащее два элемента НЕ, гетеродин, выход которого соединен с входом квадратурного направленного ответвителя, первый выход которого подключен к первому входу первого смесителя, вь1ход которого соединен с входом первого фильт ра нижних частот, выход которого подключен к входу первого усилителя ограничителя, усилитель, выход которого соединен с вторым входом первЬго смесителя и ггервым входом второго смесителя, выход которого подключен к входу второго фильтра нижних частот, второй усилитель-огр ничитель, выход которого соединен с первым входом блокарегистрации, второй вход которого подключен к вы ходу первого усилителя-ограничителя отличающееся тем, что, с целью повьшения помехоустойчг рости приема, в„него введены четыре элемента И, два элемента дифференци рования, формирователь выходного сигнала, формирователь импульсов запета, считьшанйя и сброса, блок тактовой синхронизации, вьщелитель тактовых импульсов и решающий блок, . выход которого соединен с первым входом формирователя выходного сигнала, второй вход которого подключе к первому выходу формирователя импульсов запрета, считывания.и сброс входы которого подключены к выходам блока тактовой синхронизации, вход которого соединен с выходом выдели теля тактовых импульсов, первый вхо которого соединен с выходом первого усилителя-ограничителя, входом перв го элемента НЕ и входом первого эле мента дифференцирования, первый и второй выходы которого подключены :к первым входам соответственного первого, и второго элементов И, выходы которых Соединены соответственно с третьим и .четвёртым входами блока регистрации, пятьй и шестой входы которого подключены к выходам соответственно третьего и четвертого 7 лементов И, первые входы которых одключены к выходам второго элемена дифференцирования, вход которого одключен к выходу второго усилитея-,рграничителя, второму входу выелителя тактовых импульсов и входу торого элемента НЕ, выход котороо соединен с седьмым входом блока егистрации, восьмой вход которого одключен к второму выходу формироателя импульсов запрета, считывания сброса, третий вьгход которого соединен с вторыми входами первого, второго, третьего и четвертого элементов И, выход первого элемента НЕ соединен с девятым входом блока регистрации, выходы которого подключены к входам решающего блока, второй выход квадратурного направленного ответвителя соединен с вторым входом второго смесителя, вьгход второго фильтра нижних частот соединен с входом второго усилителя-ограничителя. 2.Устройство по п. 1, о т л и- ; тем, что вьщелитель тактовых импульсов содержит элемент ИЖ, два элемента дифференцирования, два корректора формы импульсов, два элемента ИСКЛЮЧАЮЩЕЕ И.ПИ, первый и второй фазовращатели на 90°, выходы которых соединены с первыми входами соответственного первого и вторсГго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых соединены с входами соответственного первого и второго корректоров формы импульсов, выходы которых соединены с входами соответственного первого и второго элементов дифференцирования, выходы которых подключены к соответствующим входам элемента ИЛИ, при этом входы первого и второго фазовращателей на 90 соединены с вторыми входами соответственно второго и первого элементов ИСКЙОЧАЮЩЕЕ ИЛИ и являются первым и вторым входами .вьщелителя тактовых импульсов, выходом которого является выход элемента ИЛИ. 3.Устройство по п. 1, отличающееся тем, что блок тактовой синхронизации содержит фазовый дискриминатор, реверсивный счетчик, элемент управления, управляемьй делитель частоты, три делителя частоты НА два и задаюп ий генератор , выход которого- соединен с первым входом управляемого делителя частоты, выход которого соединен с входо первого делителя частоты на два,первы выход которого соединен с входом вто делителя частоты на два, выход которого соединен с входом третьего делителя частоты на два, первый и второй выходы которого через последовательно соединенные фазовый дискриминатор, реверсивньй счетчик и элемент управления подключены соответственно к второ гу и третьему входам управляемого делителя частоты, при этом третий вход фазового дискриминатора является входом блок tАктовой синхронизации, выходами которого являются первый и второй выходы первого делителя частоты на два, первый выход второго делителя частоты на два и второй выход треть го делителя частоты на два. 4. Устройство по п. 1, отличающееся тем, что формирова тель импульсов запрета, считывания и сбросаJсодержит два элемента И, регистр сдвига и элемент. ИЛИ-НЕ, выход которого соединен с первым входо регистра сдвига, второй вход которого подключен к первому входу первого элемента И, второй вход которого соединен с первым входом второго эле мента И и первьм выходом регистра сдвига, второй выход которого является третьим выходом формирователя импульсов запрета, считывания и сбро са, первым и вторым выходами которого являются выходы соответственно второго и первого элементов И, первый вход первого элемента И, второй вход второго- элемента И и входы элемента ШШ-НЕ являются Входами формирователя импульсов запрета, считывания и сброса. 5. Устройство по п. 1, о тЛ ичающееся тем, что блок регистрации содержит первый, второй, третий и четвертый D-триггеры, R-вход последнего соединен с S-BXOдом третьего D-триггера, S-входом второго D-триггера и R-входом первого D-триггера, при этом D-вход второго D-триггера, D-вход первого D-триггера, С-вход второго D-триггера, С-вход третьего D-триггера, С-вход четвертого D-триггера, С-вход первого D-триггера, D-вход третьего D-триггера, R-вход первого D-триггера и D-вход четвертого D-триггера являются соответственно первым, вторым, Третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым входами блока регистрации, выходами которого являются выходы первого, второго, третьего и четвертого Dтриггеров. 6. Устройство по п. 1, о т л ичающе еся тем, что решающий блок содержит шесть элементов-И и элемент ИДИ, входы которого подключены к выходам первого, второго, третье го, четвертого, пятого и шестого элементов И, первый вход первого элемента И соединен с первым входом второго элемента И и первым входом третьего элемента И, второй вход которого соединен с первым входом . четвертого элемента И, первым входом шестого элемента И, второй вход которого соединен с первым входом пятого элемента И и вторым входом второго элемента И, второй вход первого элемента И соединен с вторым входом четвертого элемента И и вторым входом пятого элемента И, при этом второй вход первого элемента И, первый вход второго элемента И, первьй вход пятого элемента И и первьй вход шестого элемента Иявляются входами решающего блока, выходом которого является выход элемента ИЛИ.

| Способ получения мыла | 1946 |

|

SU70695A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-12-07—Публикация

1985-06-11—Подача