Настоящее техническое решение относится к системам автоматического управления движением широкого класса подвижных объектов, как наземных, так и авиационных, а также изделий ракетно-космической техники, робототехнических комплексов, к которым предъявляются повышенные требования по точности управления и надежности работы в экстремальных условиях и в полях ионизирующего излучения. Экстремальность обусловлена широким диапазоном изменения температуры окружающей среды от - 60 до +125°С, механическими воздействиями в виде ударов и широкополосной вибрации.

Известна система автоматического управления судном (См. патент RU №2248914, (B63Н 25/04) от 01.03.2004), содержащая датчик и задатчик курса, датчик угловой скорости, датчик кормовых рулей, выходы которых подключены к входам первого сумматора-усилителя, выход которого соединен с входом рулевого привода кормовых рулей, датчик угла дрейфа и датчик носовых рулей, выход которого подключен к первому входу второго сумматора-усилителя. Кроме того, в составе системы имеются датчик и задатчик бокового смещения судна, задатчик допустимого угла дрейфа и блок логики, содержащий алгебраический сумматор, сумматор модулей двух сигналов, диод и электромагнитное реле с нормально-разомкнутой и нормально-замкнутой контактными группами. Недостатками данного технического решения являются:

1. Нестабильность характеристик. В связи с применением аналоговых узлов, параметры которых существенно зависят от условий эксплуатации (в первую очередь от температуры окружающей среды), будет наблюдаться дрейф параметров системы в целом, что усугубляется действием ионизирующего излучения.

2. Недостаточная отказоустойчивость. В системе не предусмотрено каких-либо средств нейтрализации отказов отдельных узлов, поэтому выход из строя любого узла приведет к отказу системы в целом.

3. Ограниченные функциональные возможности. Введение дополнительных управляющих звеньев или расширение набора датчиков требует существенной переработки аппаратуры системы управления.

4. Фиксированный алгоритм управления. Как в случае расширения, а также реализации другого алгоритма управления требуется переработка аппаратуры.

Задачи расширения функциональных возможностей, применения различных алгоритмов управления и повышения стабильности благодаря наличию цифрового вычислителя частично решаются в изобретении АППАРАТУРА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ДВИЖЕНИЕМ СУДНА (См. патент RU №2221728, (B63H 25/04) от 13.05.2002), содержащая кроме вычислителя, задатчик путевого угла, датчик угла перекладки руля, рулевой привод, опорную и вспомогательную антенну, приемник системы спутниковой навигации (ССН), сумматор, два интегратора и дифференциатор. Однако недостаток - низкая отказоустойчивость - в данной аппаратуре по-прежнему присутствует, так как любой отказ вычислительного устройства влечет за собой отказ всей системы.

В то же время катастрофический отказ может быть нейтрализован за счет использования введенных в состав системы резервных компонентов, а параметрический дрейф параметров отдельных узлов, обусловленный изменением температуры и ионизирующим излучением, может быть нейтрализован перестройкой режимов работы схем электрических, например изменением быстродействия цифровых блоков обработки и учетом изменения параметров, например текущих значений токов и напряжений аналоговых узлов их измерениями в процессе работы и последующим учетом этих отклонений при обработке данных в вычислительных устройствах. Наиболее полно задача нейтрализации одиночных отказов в вычислительном устройстве, являющемся основным звеном системы, решена в изобретении СИСТЕМА УПРАВЛЕНИЯ СУДНОМ (См. патент RU №242944), данное решение может быть принято за ПРОТОТИП.

Для нейтрализации последствий одиночных отказов вычислительного устройства и сохранения работоспособности системы управления в целом в составе известной системы имеются три управляющих вычислительных устройства (УВУ) с общим устройством синхронизации, обеспечивающим синхронную и синфазную работу вычислителей, выходные сигналы которых, прежде чем поступить на исполнительные органы(ИО) объекта управления, проходят через узел мажоритации. Данное решение обеспечивает нейтрализацию первого отказа в любом из вычислителей. Однако после возникновения первого отказа надежность дальнейшей работы системы резко снижается, так как возникновение любого второго отказа в одном из двух оставшихся исправными вычислителей приводит к отказу системы в целом, а интенсивность отказа двух вычислителей, приводящая к потере управления при таком варианте резервирования, в два раза больше, чем при работе с одним оставшимся исправным вычислителем.

Целесообразно после возникновения первого отказа перейти от структуры с мажоритацией к структуре, в которой к выходу подключен один из исправных вычислителей, что требует введения дополнительных средств контроля работы вычислителей и переключения их выходных сигналов.

Кроме того, надежность снижает наличие общего устройства синхронизации, отказ в котором приводит к неработоспособности УВУ и системы в целом. Устройство синхронизации, кроме того, реализовано с жесткой тактовой сеткой, а при переключении каналов УВУ изменяется длина цепей прохождения информации, и при жесткой сетке синхроимпульсов данные могут исказиться. Необходимо менять частоту синхронизации при перестройке структуры, вызывающей изменение задержек в цепях прохождения информации с учетом фактического быстродействия цепей передачи информации, которая может изменяться со временем, под действием ионизирующего излучения и изменения температуры. В большинстве вычислительных устройств, работающих длительное время в неблагоприятных внешних условиях и полях ионизирующего излучения, происходит дрейф параметров элементов, приводящий в цифровых устройствах, как правило, к изменению быстродействия, а в аналоговых узлах - к изменению стабильности и точности их работы. В то же время, подстраивая частоту обработки информации в цифровых узлах под фактическое быстродействие и фактические времена передачи информации их блоков и узлов, а также учитывая дрейф параметров в аналоговых узлах (например, в аналого-цифровых преобразователях) можно сохранить работоспособность и точностные характеристики системы управления.

Кроме того, при создании радиационно стойких БИС для таких систем их разработчики технологическими мерами (например, перелегированием) производят сдвиг параметров этих БИС в сторону, противоположную изменению их параметров при наборе дозы от ионизирующего излучения. Поэтому при начальном наборе дозы быстродействие элементов БИС может возрастать. Представляется целесообразным использовать повышение быстродействия БИС для увеличения производительности УВУ и эффективности системы в целом за счет расширения состава задач и точности вычислений.

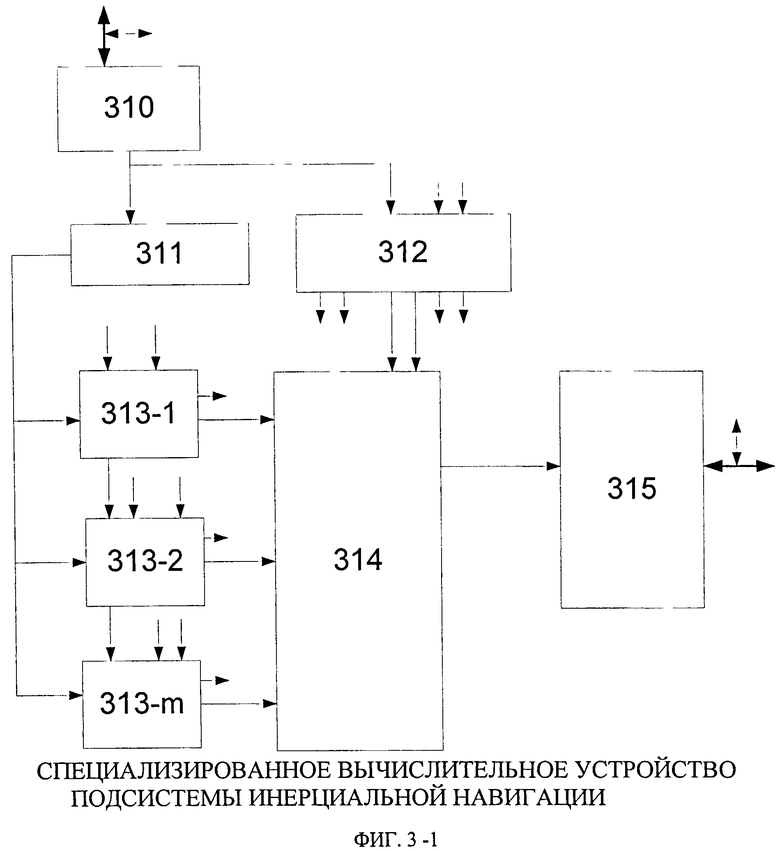

Решение этих задач требует существенной переработки известных решений.

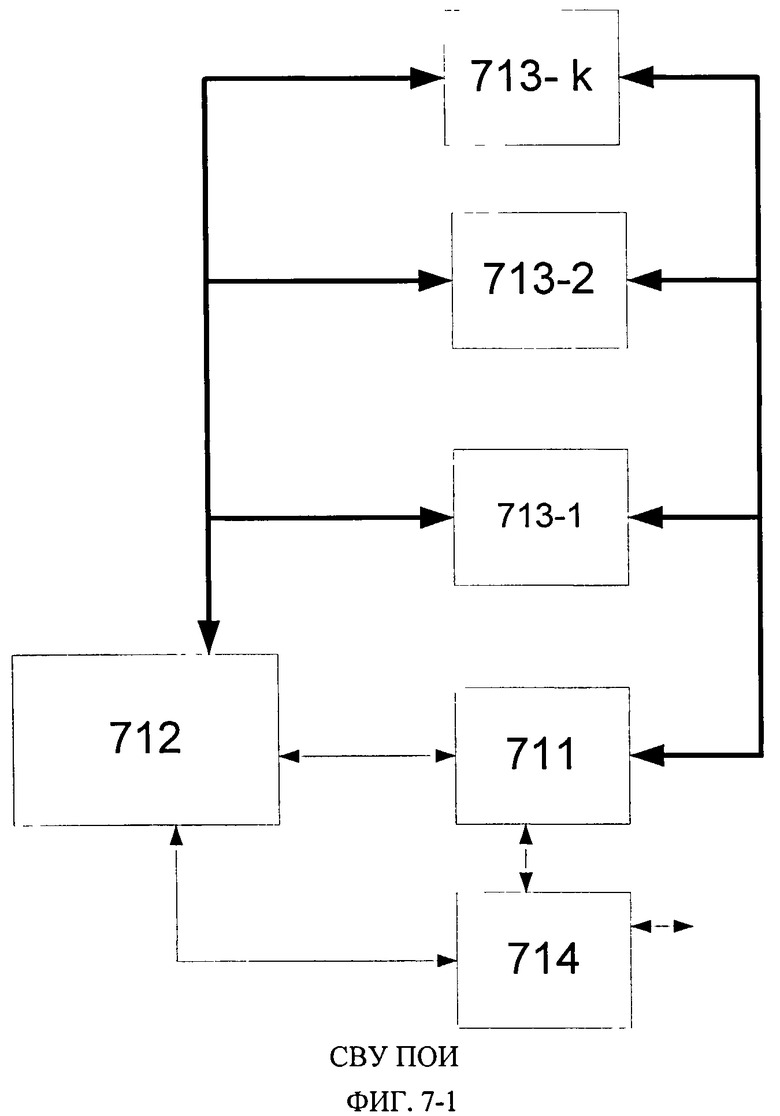

С целью повышения эффективности работы системы управления и расширения состава объектов для ее применения предлагается

СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ.

Заявляемое устройство содержит различные датчики (угловой скорости, ускорения и т.д.), аппаратуру спутниковой навигации (АСН), блок сбора информации (БСИ), три управляющих вычислительных устройства (УВУ), исполнительные органы (ИО) объекта управления и подсистему инерциальной навигации (ПИН).

Кроме того, в состав заявляемого устройства дополнительно введены переключатель каналов (ПК) УВУ, блок контроля (БК), подсистема оптической коррекции (ПОК), подсистема электропитания (ПЭП), датчик внешнего воздействия (ДВВ), формирователь сигнала (ФС) блокировки и энергонезависимое запоминающее устройство с санкционированным доступом (ЗУ СД).

ПИН содержит датчик ускорения и три датчика угловой скорости (соответственно рысканья, вращения (крена) и тангажа). Выходы датчиков подключены к входам первого специализированного вычислительного устройства подсистемы инерциальной навигации (СВУ ПИН), вход-выход которого является входом-выходом подсистемы, подключенным через двунаправленную навигационную связь к БСИ.

СВУ ПИН содержит процессор, к которому через двунаправленную связь подключено первое специализированное запоминающее устройство. Вход-выход процессора объединен с входом-выходом блока связи и является входом-выходом СВУ. Выход процессора подключен к входу первого блока микропрограммного управления (БМУ), входу блока синхронизации и входу буферного регистра. Выходы этого регистра подключены к входам n умножителей, соединенных последовательно шинами переноса. Выходы умножителей подключены к входам сумматора, выход которого подключен к входу блока связи, вход-выход которого является входом-выходом СВУ и подсистемы, подключенным к БСИ.

Подсистема оптической коррекции содержит n датчиков инфракрасного, светового и ультрафиолетового диапазонов, подключенных выходами к входам второго СВУ подсистемы оптической коррекции (СВУ ПОИ), подключенного входом-выходом через двунаправленную обрабатывающую связь к БСИ.

СВУ ПОИ содержит управляющий микропроцессор с подключенным к нему через первую двунаправленную связь вторым специализированным запоминающим устройством, к которому через вторую двунаправленную связь подключено устройство связи, вход-выход которого является входом-выходом СВУ и ПОИ, подключенным к БСИ. Кроме того, к управляющему микропроцессору через первую магистраль подключено m вычислительных микропроцессоров, подключенных через вторую магистраль ко второму запоминающему устройству. При этом установочный выход управляющего микропроцессора подключен к установочным входам второго БМУ и устройства синхронизации, выходы которых подключены к микропрограммным входам и входам синхронизации всех микропроцессоров и устройства связи, выходы признаков которых подключены к входам признаков второго БМУ.

Устройство синхронизации и блок синхронизации реализованы идентично и каждый из них содержит перестраиваемый генератор импульсов, установочный вход которого является одноименным входом устройства (блока), а выход подключен к запускающему входу сдвигающего регистра, выход последнего разряда которого подключен к его запускающему входу, а выходы этого регистра являются синхронизирующими выходами устройства (блока).

Блок сбора информации содержит последовательно соединенные регистры, входы и выходы которых являются входами и выходами, схемы развязки и схемы связи, вход-выход которых является входом-выходом блока, подключенного к УВУ.

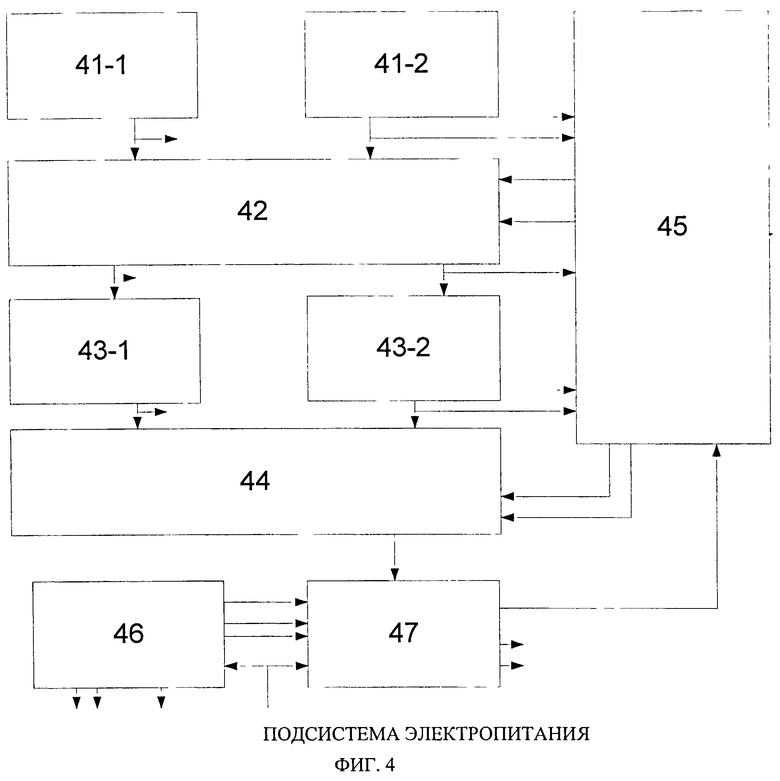

Подсистема электропитания содержит первый и второй первичные источники энергии, подключенные выходами к первой группе входов блока контроля и управления (БКУ) и соответственно к первому и второму входам первого коммутатора. Выходы этого коммутатора подключены к входам первого и второго аккумуляторов, подключенных выходами ко второй группе входов БКУ и соответственно к первому и второму входам второго коммутатора, выходы которого подключены к входу источника вторичного электропитания (ИВЭП), установочный вход которого является установочным входом подсистемы, подключенным в выходу ПК, и объединен с установочным входом формирователя синхроимпульсов (ФСИ), три управляющих выхода которого подключены к управляющим входам ИВЭП. Выходы постоянного и импульсного питания ИВЭП, синхронизирующие выходы и выходы метки времени ФСИ, являются одноименными выходами подсистемы, подключенными к соответствующим входам АСН, ПИН, ПОИ и ЗУСД.

Датчик внешнего воздействия выполнен как блокинг-генератор, к базе транзистора которого подключен обратно-смещенный диод.

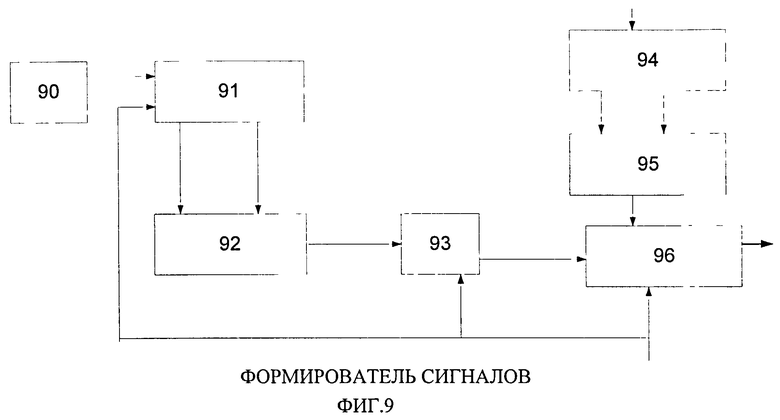

Формирователь сигнала содержит стабильный задающий генератор, подключенный выходом к интервальному счетчику, выход которого через интервальный дешифратор подключен к сбрасывающему входу триггера запрета, запускающий вход которого объединен с запускающим входом интервального счетчика и первым входом логического элемента, выход которого является выходом формирователя, установочный вход которого является входом регистра санкционированного кода. Выходы этого регистра через санкционированный дешифратор подключены к запрещающему входу логического элемента.

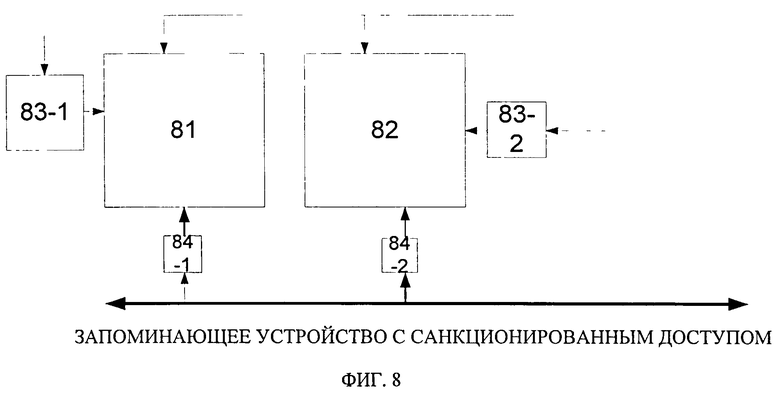

Запоминающее устройство с санкционированным допуском содержит первый и второй накопители, блокирующие входы которых являются блокирующим входом устройства, подключенным к выходу формирователя сигналов. Кроме того, к каждому из накопителей, первому и второму, через собственную первую временную двунаправленную связь подключен свой сумматор времени, соответственно первый и второй, входы которых являются входом метки времени устройства, у которого, кроме того, к каждому из накопителей, первому и второму, через свою вторую массивную двунаправленную связь подключен свой сумматор массивов, соответственно первый и второй, вход-выход каждого из которых к двунаправленной шине связи ЗУСД с блоком сбора информации.

Накопитель содержит энергонезависимый элемент памяти, параллельно которому к шинам записи подключен полевой транзистор со встроенным каналом, к затвору которого подключен сигнал блокировки.

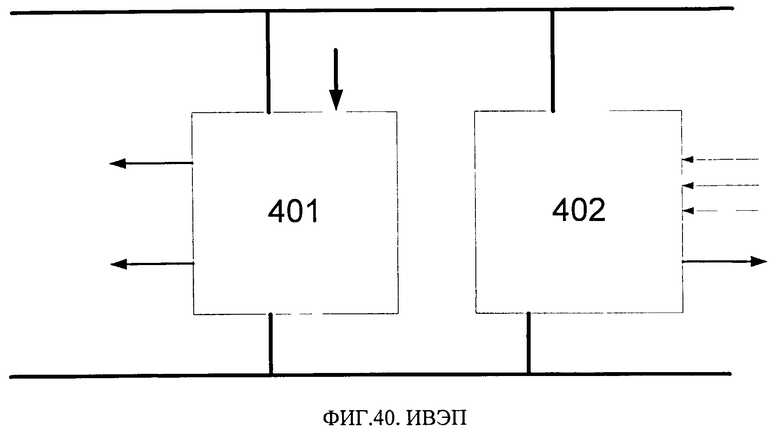

ИВЭП содержит модуль постоянного питания (МПП) и модуль импульсного питания (МИП), силовой, установочный вход и три управляющих входа которых являются одноименными входами ИВЭП.

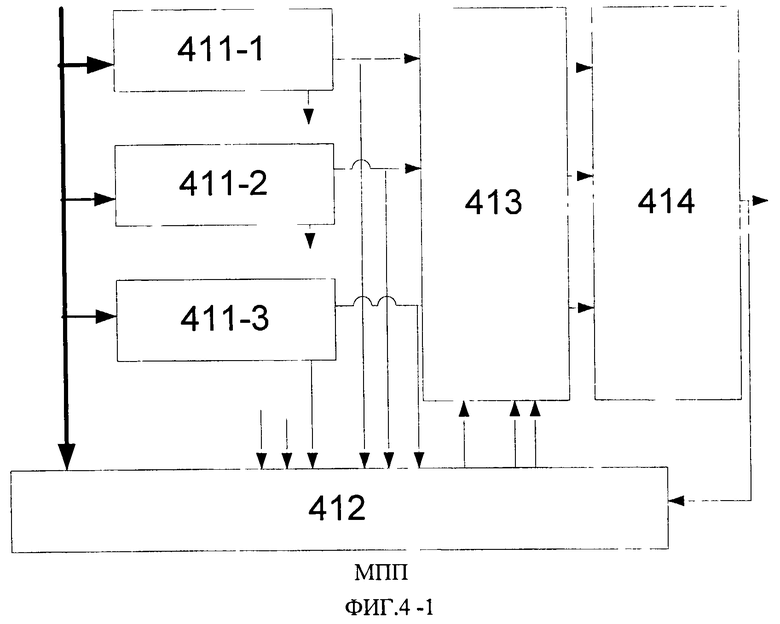

МПП содержит три конвертора, силовые и установочные входы которых являются одноименными входами ИВЭП, а частотный выход каждого из конверторов подключен к частотным входам блока управления и контроля (БУК), к контрольным входам которого подключены выходы конверторов, которые кроме того через блок отключения (БО) подключены к входам блока выравнивания (БВ), выход которого является выходом модуля и подключен к дополнительному контрольному входу БУК.

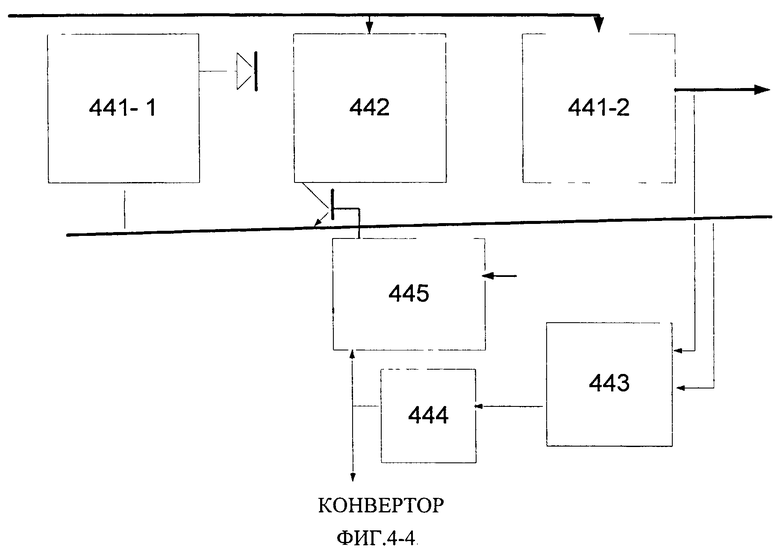

Конвертор содержит последовательно включенные фильтр, вход которого является силовым входом конвертора, защитный диод, трансформатор с включенным в первичную обмотку транзистором - прерывателем, выпрямляющий диод и выходной фильтр, выход которого является выходом конвертора. К этому выходу подключен преобразователь напряжения в частоту, выход которого подключен к элементу развязки, выход которого является частотным выходом конвертора и подключен к входу частотно-импульсного модулятора, установочный вход которого является установочным входом конвертора, а выход подключен к базе транзистора - прерывателя.

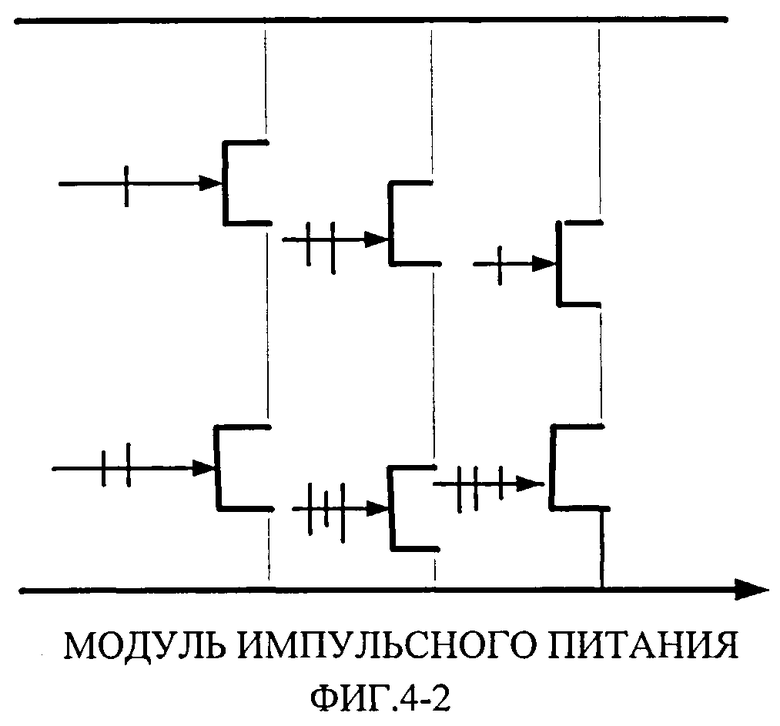

МИП содержит три ветви, объединенные с каждой из сторон, одна из которых является силовым входом, вторая - выходом. В каждой ветви последовательно включены два полевых транзистора, а три управляющих сигнала разведены таким образом, что каждый из них подключен к затворам двух транзисторов, установленных в разных ветвях, образуя выборку «2 из 3».

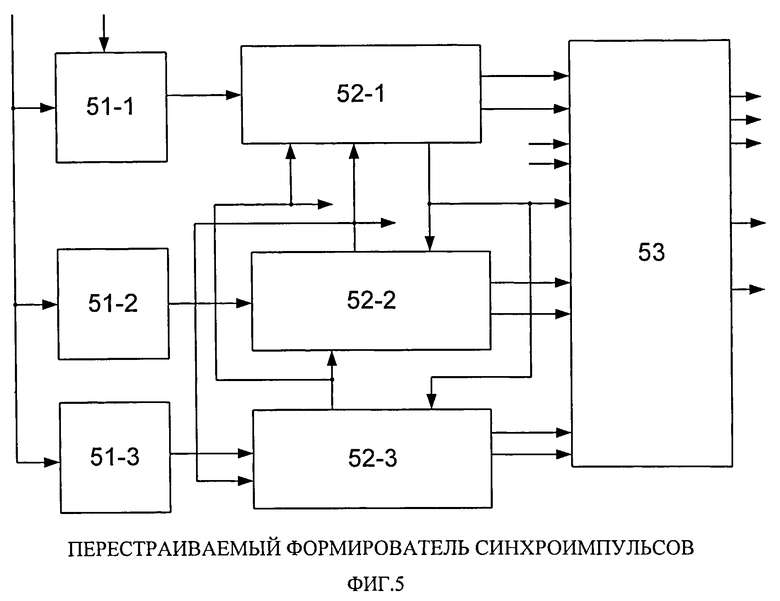

ФСИ содержит первый, второй и третий перестраиваемые генераторы импульсов, установочные входы которых являются установочным входом формирователя. Выходы каждого из генераторов подключены к входам своего блока фазирования, соответственно первого, второго и третьего, фазирующий выход каждого из которых подключен к фазирующим входам двух других блоков и к фазирующим входам блока мажоритации, к синхронизирующим входам которого подключены синхронизирующие выходы блоков фазирования, а выходы этого блока являются выходами метки времени, трех управляющих сигналов и синхроимпульсов блока и формирователя.

Перестраиваемый генератор импульсов содержит первую группу последовательно соединенных инверторов, подключенных выходами к входам первого мультиплексора, выход которого является выходом генератора и подключен к входу первого инвертора группы и входу счетчика частоты. Выходы этого счетчика подключены к первым входам первой схемы сравнения, ко вторым входам которой подключены выходы регистра кода частоты, а инкрементный и декрементный выходы схемы сравнения подключены к одноименным входам первого счетчика кода частоты, выходы которого подключены к управляющим входам мультиплексора. При этом установочный вход первого счетчика кода частоты и установочный вход первого регистра кода частоты являются установочным входом генератора.

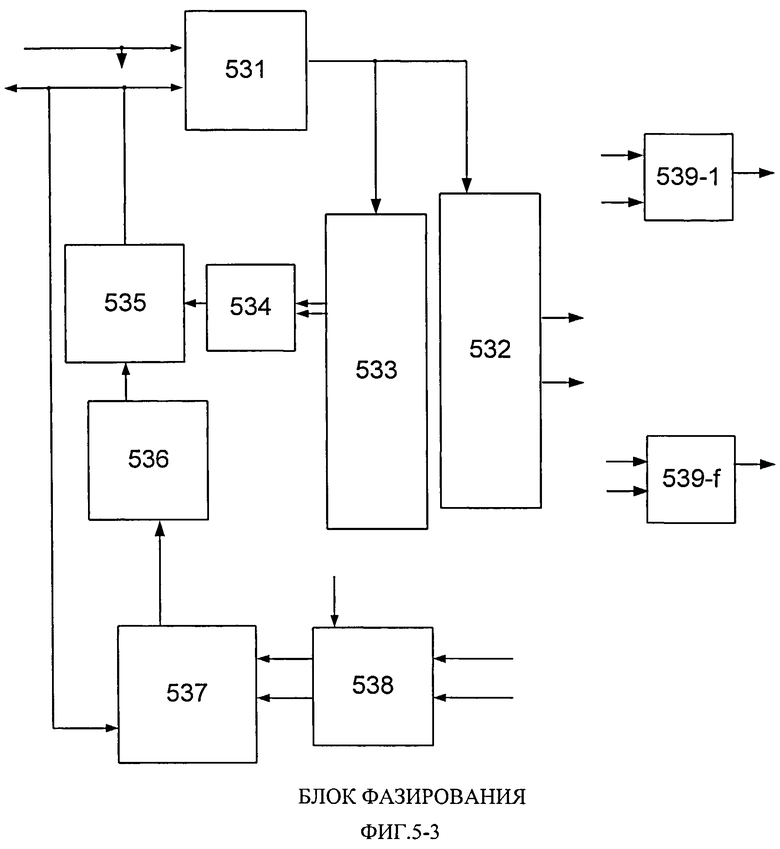

Блок фазирования содержит элемент И, первый вход которого является входом блока, подключенным к выходу генератора импульсов, а выход элемента подключен к входу сдвигающего регистра и входу выполненного на динамических триггерах динамического счетчика, выходы которого подключены через дешифратор к запускающему входу триггера останова, выход которого является фазирующим выходом блока и подключен ко второму входу элемента И и первому входу мажоритарного элемента, к двум другим входам которого подключены выходы триггеров привязки, стробирующий вход которых объединен с первым входом элемента И, а входы являются фазирующими входами блока. При этом выходы четных и нечетных разрядов сдвигающего регистра подключены соответственно к запускающим и сбрасывающим входам f выходных триггеров, выходы которых являются синхронизирующими выходами блока.

Частотно-импульсный модулятор реализован аналогично перестраиваемому генератору импульсов с тем отличием, что вход счетчика частоты не подключен к выходу мультиплексора, а является входом модулятора, подключенного к выходу элемента развязки, и, кроме того, основные узлы: группа инверторов, мультиплексор, счетчик частоты, регистр кода частоты и счетчик кода частоты являются вторыми, а не первыми, как в перестраиваемом генераторе импульсов.

Состав системы приведен на фигуре 1, где цифрой 1 обозначены датчики, цифрой 1.1 - аппаратура спутниковой навигации, цифрой 1.2 - подсистема инерциальной навигации и цифрой 1.3 обозначена подсистема оптической коррекции. Цифрой 2 обозначен БСИ. Цифрами 3-1, 3-2 и 3-3 обозначены УВУ. Цифрой 4 - ПЭП, цифрой 5 обозначен переключатель каналов, цифрой 6 - блок контроля, цифрой 7 - ЗУ СД. Цифрой 8 обозначены исполнительные органы. Цифрой 9 обозначен формирователь сигнала и цифрой 10 обозначен датчик внешнего воздействия.

На фигуре 2 приведен состав блока сбора информации. Блок содержит приемные регистры 21, схемы развязки 22 и схемы связи 23.

На фигуре 3 приведен состав подсистемы инерциальной навигации. Цифрой 31 обозначен датчик ускорения, цифрами 32-1, 32-2 и 32-3 обозначены три датчика угловой скорости (соответственно рысканья, вращения (крена) и тангажа), цифрой 33 обозначено специализированное вычислительное устройство подсистемы инерциальной навигации (СВУ ПИН).

На фигуре 3-1 приведен СВУ ПИН. Цифрой 310 обозначен процессор, цифрой 311 обозначен буферный регистр, цифрой 312 обозначен блок микропрограммного управления, цифрами от 313-1 до 313-m обозначены умножители, цифрой 314 обозначен сумматор и цифрой 315 обозначен блок связи.

Подсистема электропитания приведена на фигуре 4. Здесь цифрами 41-1 и 41-2 обозначены первый и второй первичные источники энергии, цифрой 42 обозначен первый коммутатор, цифрами 43-1 и 43-2 обозначены первый и второй аккумуляторы, цифрой 44 обозначен второй коммутатор, цифрой 45 - блок контроля и управления и цифрами 46 и 47 обозначены ФСИ и ИВЭП.

ИВЭП приведен на фигуре 40, где цифрами 401 и 402 обозначены модуль постоянного и модуль импульсного питания.

МПП приведен на фигуре 4-1. На фигуре цифрами 411-1, 411-2 и 411-.3 обозначены первый, второй и третий конверторы, цифрой 412 обозначен БУК, цифрой 413 - блок отключения и 414 обозначен блок выравнивания.

Модуль импульсного питания приведен на фигуре 4-2.

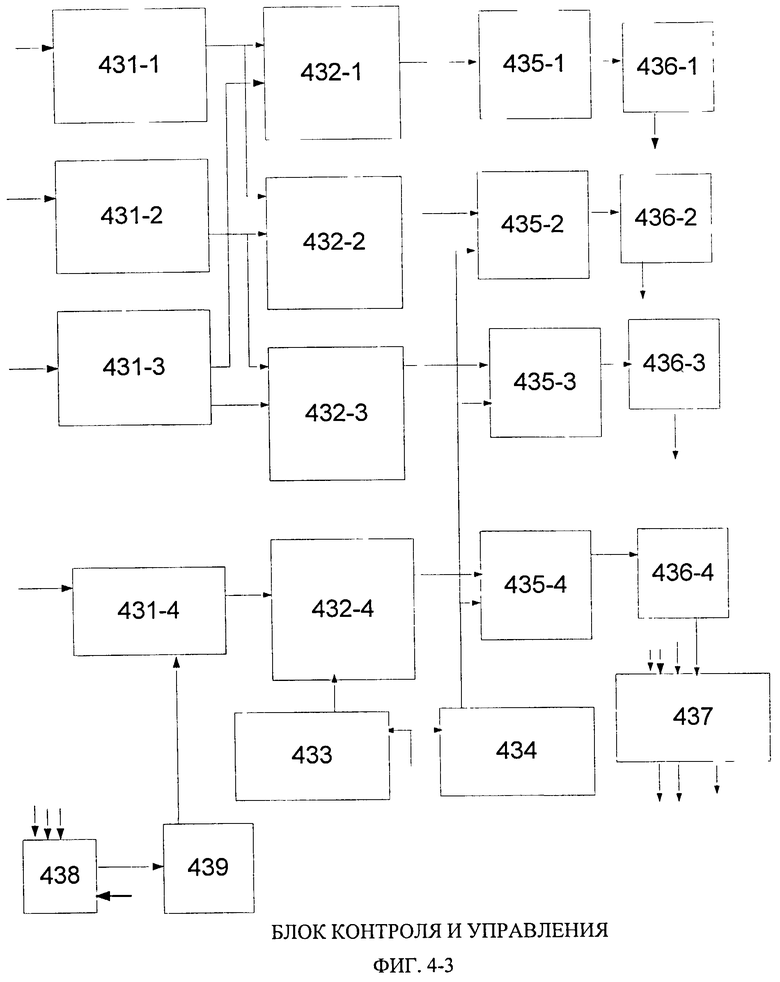

Блок управления и контроля приведен на фигуре 4-3. Здесь цифрами 431-1, 431-2, 431-3 и 431-4 обозначены первый, второй, третий и четвертый счетчики частоты. Цифрами 432-1, 432-2, 432-3 и 432-4 обозначены первый, второй, третий и четвертый сумматоры. Цифрами 433 и 434 обозначены регистр кода и регистр допуска. Цифрами 435-1, 435-2, 435-3 и 435-4 обозначены первая, вторая, третья и четвертая схемы совпадения. Цифрами 436-1, 436-2, 436-3 и 436-4 обозначены первый, второй, третий и четвертый триггеры неисправности, цифрой 437 обозначена группа логических элементов, цифрой 438 обозначен аналоговый мультиплексор и цифрой 439 обозначено устройство преобразования напряжения в частоту.

Конвертор приведен на фигуре 4-4, где цифрами 441-1 и 441-2 обозначены фильтр и выходной фильтр, цифрой 442 - трансформатор, цифрой 443 обозначен преобразователь напряжения в частоту, цифрой 444 обозначен элемент развязки и цифрой 445 обозначен частотно-импульсный модулятор.

Перестраиваемый формирователь синхроимпульсов приведен на фигуре 5, содержит три генератора импульсов первый 51-1, второй 51-2 и третий 51-3, три блока фазирования - первый 52-1, второй 52-2, третий 52-3 и блок мажоритации 53.

Перестраиваемый генератор импульсов приведен на фигуре 5-1, где цифрой 510 обозначена первая группа инверторов, цифрой 511 - первый мультиплексор, цифрой 512 обозначен первый счетчик кода частоты. Цифрами 513 и 514 обозначены первая схема сравнения и первый счетчик частоты и цифрой 515 обозначен первый регистр кода частоты.

Блок синхронизации приведен на фигуре 5-2, где цифрами 520 и 521 обозначены соответственно перестраиваемый генератор импульсов и сдвиговый регистр.

Блок фазирования приведен на фигуре 5-3, где цифрой 531 обозначен элемент И, цифрами 532 и 533 обозначены сдвиговый регистр и динамический счетчик. Цифрой 534 обозначен дешифратор, цифрами 535 и 536 обозначены соответственно триггер останова и триггер пуска, цифрой 537 - мажоритарный элемент. Цифрой 538 обозначены триггеры привязки и цифрами от 539-.1 до 539-.f обозначены триггеры-формирователи.

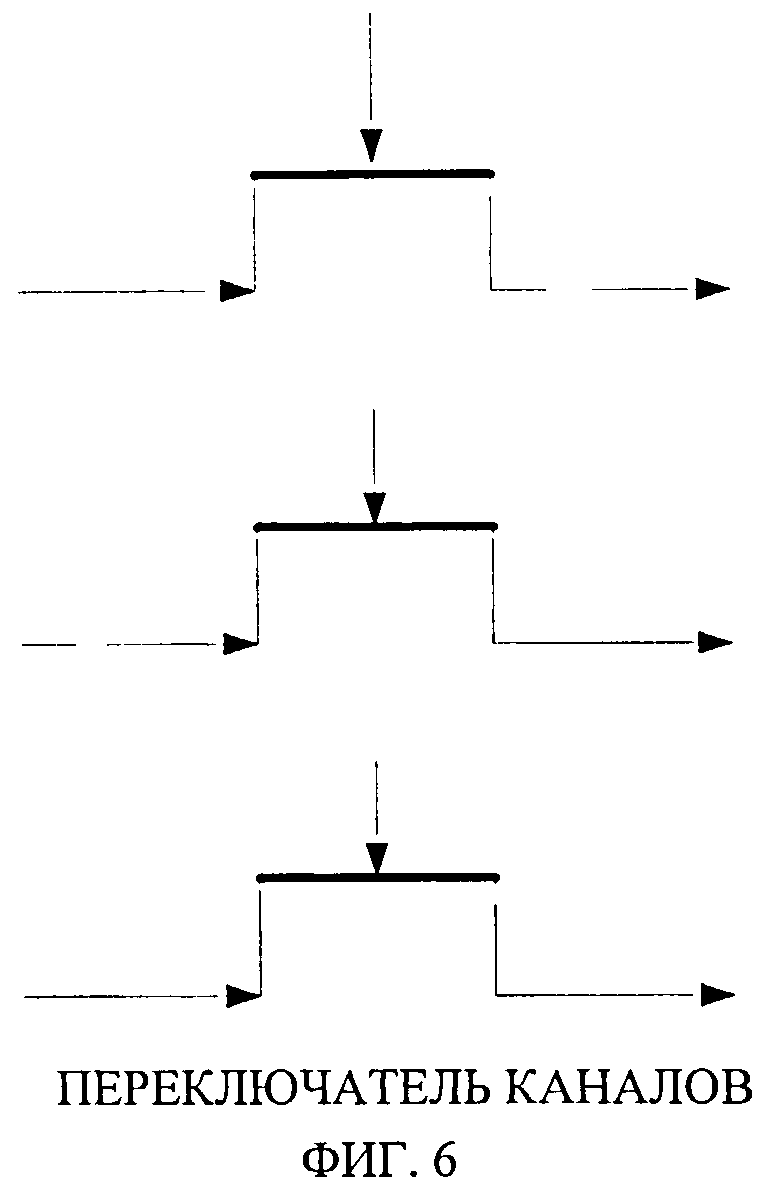

На фигуре 6 показан переключатель каналов.

Подсистема обработки изображений приведена на фигуре 7, где цифрами от 71-1 до 71-n обозначены оптические датчики. Цифрой 72 обозначено специализированное вычислительное устройство подсистемы обработки изображений (СВУ ПОИ).

На фигуре 7-1 представлено специализированное вычислительное устройство подсистемы обработки изображений (СВУ ПОИ). Цифрой 711 обозначено второе специализированное запоминающее устройство, цифрой 712 обозначен управляющий микропроцессор, цифрами от 713-1 до 713-k обозначены вычислительные микропроцессоры, цифрой 714 обозначено устройство связи.

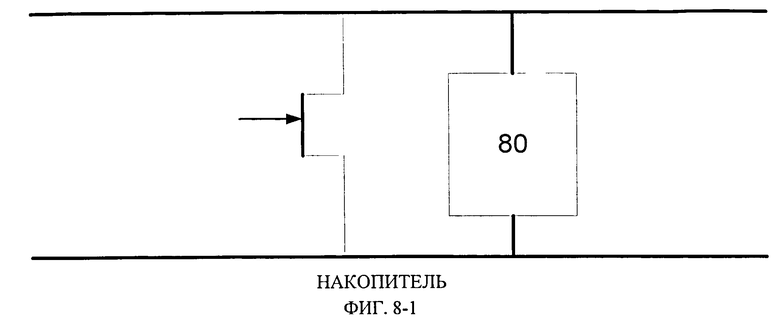

Запоминающее устройство с санкционированным доступом (ЗУ СД) приведено на фигуре 8, где цифрами 81 и 82 обозначены первый и второй накопители, 83-1 и 83-2 обозначены первый и второй сумматоры меток времени и цифрами 84-1 и 84-2 обозначены первый и второй сумматоры массивов.

Накопитель приведен на фигуре 8-1, где цифрой 80 обозначен энергонезависимый элемент памяти.

Формирователь сигналов приведен на фигуре 9. В формирователе цифрой 90 обозначен стабильный задающий генератор, цифрой 91 - интервальный счетчик, цифрой 92 - интервальный дешифратор, цифрой 93 обозначен триггер запрета, цифрой 94 - регистр санкционированного кода, цифрой 95 обозначен кодовый дешифратор и цифрой 96 обозначен логический элемент.

Частотно-импульсный модулятор приведен на фигуре 10, где цифрой 101 обозначена вторая группа инверторов, цифрой 102 - второй мультиплексор, цифрой 103 обозначен второй счетчик кода частоты, цифрой 104 обозначен второй счетчик частоты, цифрой 105 обозначен второй регистр кода частоты и цифрой 106 обозначена вторая схема сравнения.

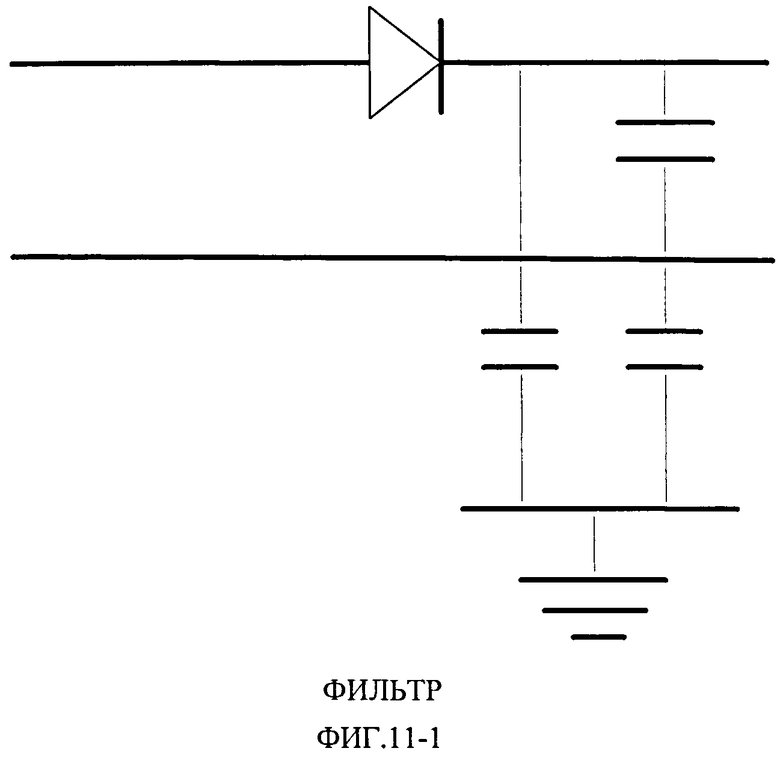

На фигуре 11 показан датчик внешнего воздействия (ДВВ), на фигуре 11-1 приведен фильтр.

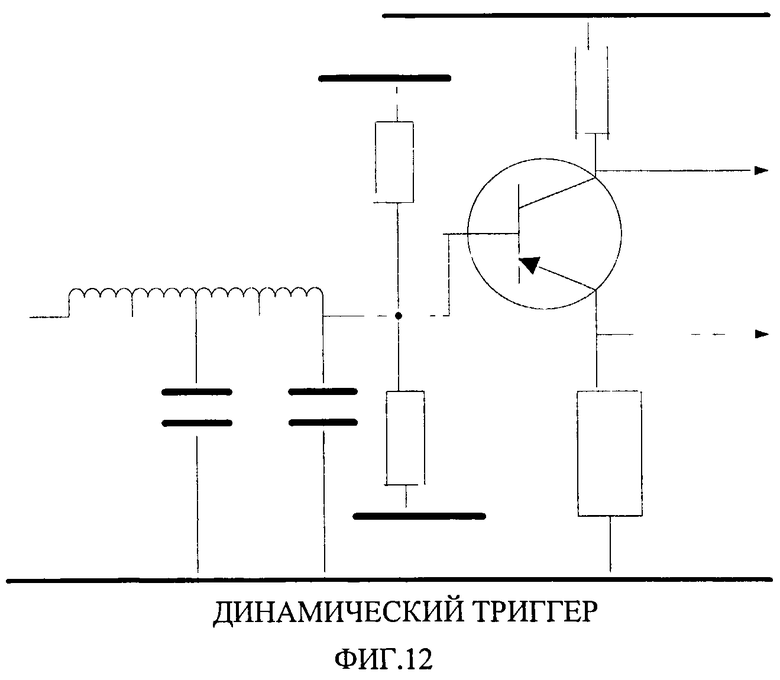

На фигуре 12 приведен динамический триггер.

Заявляемое устройство может быть реализовано следующим образом.

Процессор СВУ ПИН реализуется на БИС 1867 ВМ2, первый блок микропрограммного управления реализуется на БИС памяти серии 1620РЕ и БИС на основе БМК серий 1556 и 1557.

Все микропроцессоры СВУ ПОИ являются БИС 1825 ВС3, а блок микропрограммного управления реализуется аналогично блоку микропрограммного управления СВУ ПИН.

Блок формирователь синхроимпульсов реализуется на БИС 1825 ВБ 1 и БИС на основе БМК серий 1556 и 1567, а динамический счетчик реализуется на основе динамических триггеров. Преобразователи и схемы преобразования напряжения в частоту реализуются на основе БИС ADFC32 фирмы Analog Devices или ее аналога, например КР 1801. Элемент развязки и схема развязки реализуется на оптроне 249 ЛП5 или планарном трансформаторе, изготавливаемом в производстве НПОА.

Блок сбора информации, блок контроля, блок контроля и управления, блок управления и контроля реализуются на БИС на основе БМК сер. 1556 и 1557.

Источник вторичного электропитания, датчик внешнего воздействия и динамический триггер реализуются на дискретных элементах и моточных изделиях завода-изготовителя.

Система работает следующим образом.

После включения питания начинают работать генераторы импульсов ФСИ, блока синхронизации и устройства синхронизации, через несколько периодов высокой частоты с выхода ФСИ в УВУ и ЗУ СД начинают поступать синхронно и синфазно метки времени на входы сумматоров ЗУСД и входы прерывания УВУ, а также импульсы синхронизации на синхровходы УВУ и остальных модулей системы. УВУ приступают к выполнению программ управления, опрашивая через блок сбора информации внешние датчики, ПИН и корректирующие подсистемы (АСН и ПОК).

Результаты вычислений сохраняются в виде рестартовых массивов в ЗУСД и выдаются через переключатель каналов на исполнительные органы объекта управления, выходная информация всех каналов УВУ поступает одновременно в блок контроля, управляющего переключателем, в который кроме того поступают сигналы неисправности, вырабатываемые встроенными в каждое УВУ аппаратурными средствами контроля, например, по mod3. Можно обозначить сигналы от этих средств через Hi, где i - номер УВУ (1, 2 или 3). Для логики работы переключателя каналы УВУ расположены по кольцу: (1, 2, 3, 1). Таким образом для УВУ3 (i) УВУ2 будет иметь индекс i-1, а УВУ1 будет иметь индекс i+1 и т.д. При обнаружении неисправности i-го УВУ переключатель подключает к выходу сигналы предыдущего по номеру, т.е. (i-1)-го вычислителя. В случае неисправности двух вычислителей к выходу подключены сигналы третьего исправного. Таким образом, после возникновения первого отказа к выходу подключены сигналы всегда одного вычислителя, что существенно снижает вероятность отказа системы при возникновении второй неисправности. В случае формирования сигналов неисправности трех вычислителей, что может быть следствием ограниченной надежности и достоверности работы встроенных средств контроля или схем сравнения, к выходу остается подключенным последний признанный исправным вычислитель, что исключает неопределенность в логике работы переключателя. Логику выработки сигналов неисправности УВУ, вырабатываемых БКУ, по которым происходит переключение каналов, можно представить в виде логической формулы

Обозначим:

Hi - неисправность i-го УВУ,

Нi - неисправность этого же вычислителя, сформированную внутренними средствами контроля,

сi - неисправность этого же вычислителя, сформированную схемами сравнения.

Тогда Нi=Сi \/ Hi

Логику выработки сигнала неисправности, формируемого схемами сравнения, можно записать следующим образом:

сi=(Иi /\ Иi+1 /\ JИi-1 \/ Иi /\ Иi-1 /\ Иi+1) \/ (JИi /\ JИi+1 /\ Иi-1 \/ Иi /\ JИi+1 /\ Иi-1 \/ JИi /\ JИi-1 /\ Иi+1).

Таким образом, введение переключателя с блоком контроля позволяет нейтрализовать до двух неисправностей в вычислительных устройствах и сохраняет вероятность работоспособности системы при трех неисправностях УВУ. Наличие в ФСИ трех генераторов импульсов и трех взаимно фазируемых блоков фазирования обеспечивает нейтрализацию как одной постоянной неисправности в ФСИ, так и нейтрализацию кратковременных отказов (сбоев) в формирователе, в которых реализована функция взаимного фазирования за 2-3 периода высокой частоты. После чего начинается формирование синхронных и синфазных меток реального времени, управляющих сигналов и синхроимпульсов, обеспечивающих работу ЗУСД, ИВЭП, УВУ и системы в целом,

Введение перестройки частоты генераторов импульсов, входящих в состав ФСИ, блока и устройства синхронизации позволяет на каждый интервал времени установить частоту синхронизации, соответствующую текущему быстродействию цифровых узлов, соответствующего вычислительного устройства, что позволяет не только повысить надежность работы системы при снижении быстродействия элементов, но и использовать возникающие запасы по быстродействию, для чего предусмотрено периодическое выполнение программ тестовых проверок УВУ, и СВУ подсистем, позволяющее оценить работоспособность при текущей или устанавливаемой частоте синхронизации.

Для нейтрализации параметрических уходов аналоговых узлов в конверторе и БУК в качестве основного выбран преобразователь напряжения в частоту, обладающий тем несомненным преимуществом, что зависимость точности и стабильности его работы определяется всего двумя элементами - резистором и конденсатором, выбором типов которых и предварительной их радиационной и термотренировкой можно обеспечить требуемую стабильность на продолжительном интервале времени в полях ионизирующего излучения. Нестабильность работы источника питания, необходимого для запитки подсистем и УВУ в предложенной системе, нейтрализуется установкой в выходную цепь высокостабильного эталонного резистора, замером выходного напряжения и в котором определяют текущее значение выходного напряжения, и после проведения необходимого пересчета результатов замеров и формируют новую уставку конверторам в их частотно-импульсные модуляторы.

Совокупность предложенных решений в виде дополнительных резервных устройств и блоков, организации перестройки структуры при возникновении отказов, а также нейтрализация параметрических уходов элементов как цифровых узлов, так и аналоговых позволяет повысить надежность и точность работы системы управления, работающей длительное время в условиях воздействия внешних дестабилизирующих факторов, что существенно расширяет по сравнению с известными решениями диапазон применения системы для объектов различного назначения.

Таким образом, в заявляемом устройстве обеспечена нейтрализация любого одиночного отказа за счет резервирования на различных уровнях. Обеспечена нейтрализация параметрических изменений в элементах из-за изменения температуры и дозовых эффектов от действия ионизирующего излучения и заявляемое устройство может успешно использоваться для управления авиационными объектами, изделиями ракетно-космической техники и робототехническими комплексами, работающими в экстремальных условиях и полях ионизирующего излучения.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЕСПЛАТФОРМЕННАЯ ИНЕРЦИАЛЬНАЯ НАВИГАЦИОННАЯ СИСТЕМА | 2013 |

|

RU2563333C2 |

| СИСТЕМА АСТРОНАВИГАЦИИ | 2013 |

|

RU2548927C1 |

| СИСТЕМА УПРАВЛЕНИЯ КОСМИЧЕСКОГО АППАРАТА | 2013 |

|

RU2560204C2 |

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| ТЕХНОЛОГИЧЕСКАЯ УВМ | 2013 |

|

RU2563139C2 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2011 |

|

RU2494006C2 |

Изобретение относится к автоматике и может быть использовано при создании систем управления авиационными объектами, изделиями ракетно-космической техники и робототехническими комплексами, работающими в экстремальных условиях (широкий диапазон изменения температур от -60 до +125°C, механические воздействия в виде ударов и широкополосной вибрации) в полях ионизирующего излучения. Технический результат - повышение эффективности работы системы управления, а именно сохранение работоспособности при возникновении любого одиночного отказа в аппаратуре системы, а также сохранение функционирования и точности управления при возникновении параметрических изменений в комплектующих элементах, вызванных старением, изменением температуры окружающей среды и дозовыми факторами ионизирующего излучения. Предлагаемая система содержит исполнительные органы объекта управления, датчик угловой скорости, датчик ускорения, блок сбора информации, аппаратуру спутниковой навигации, подсистему инерциальной навигации, управляющие вычислительные устройства, датчик внешнего воздействия, формирователь сигнала блокировки, запоминающее устройство с санкционированным доступом и исполнительным органам, подсистему электропитания, подсистему обработки изображений, блок контроля и подсистему оптической коррекции. 23 з.п. ф-лы, 24 ил.

1. Система автоматического управления, содержащая исполнительные органы объекта управления, датчики, подключенные выходами к входам блока сбора информации, аппаратуру спутниковой навигации и подсистему инерциальной навигации, подключенные через подсистемные, соответственно спутниковую и навигационную двунаправленные связи к блоку сбора информации, подключенному выходом к трем управляющим вычислительным устройствам, отличающаяся тем, что в ее состав дополнительно введены датчик внешнего воздействия, подключенный выходом к формирователю сигнала блокировки, выход которого подключен к блокирующим входам запоминающего устройства с санкционированным доступом и исполнительным органам, подсистема электропитания, подсистема обработки изображений, подключенная через свою обрабатывающую двунаправленную связь к блоку сбора информации, при этом выходы каждого управляющего вычислительного устройства подключены к входам блока контроля и входам переключателя каналов, выходы которого подключены к исполнительным органам, установочным входам подсистемы инерциальной навигации, подсистемы оптической коррекции и подсистемы электропитания, выходы постоянного и импульсного питания, синхронизирующие выходы и выходы метки времени которой подключены к соответствующим входам управляющих вычислительных устройств, подсистемы инерциальной навигации, подсистемы обработки изображений и запоминающего устройства с санкционированным доступом.

2. Система по п.1, отличающаяся тем, что блок сбора информации содержит последовательно включенные входные регистры, входы и входы-выходы которых являются входами и входами-выходами блока, схемы развязки и схемы связи, группа входов-выходов которых является подсистемными входами-выходами блока, а основной вход является основным выходом блока.

3. Система по п.1, отличающаяся тем, что запоминающее устройство с санкционированным доступом содержит первый и второй энергонезависимые накопители, блокирующий вход которых является блокирующим входом устройства, а вход метки времени устройства подключен к входам первого и второго сумматоров меток времени, а каждый из сумматоров через свою, соответственно первую и вторую, временную двунаправленную связь подключен к своему, соответственно первому и второму, накопителю, к каждому из которых через свою, соответственно первую и вторую, массивную двунаправленную связь подключен первый и второй сумматор массивов, подключенные входом-выходом к двунаправленной шине, являющейся санкционированной шиной связи запоминающего устройства.

4. Система по п.1, отличающаяся тем, что подсистема электропитания содержит первый и второй источники энергии, выходы которых подключены соответственно к первому и второму входам первого коммутатора и к первой группе входов блока контроля и управления, подключенного первыми управляющими выходами к управляющим входам первого коммутатора, выход которого подключен к входам первого и второго аккумуляторов, выходы которых подключены соответственно к первому и второму входам второго коммутатора и ко второй группе входов блока контроля и управления, вторые управляющие выходы которого подключены к управляющим входам второго коммутатора, выход которого подключен к силовому входу источника вторичного электропитания, выходы которого являются выходами синхронизации, метки времени, постоянного и импульсного питания подсистемы, а установочный вход источника объединен с установочным входом формирователя синхроимпульсов, три управляющих выхода которого подключены к трем управляющим входам источника вторичного электропитания, а выходы синхроимпульсов и метки времени формирователя синхроимпульсов являются выходами подсистемы.

5. Система по п.1, отличающаяся тем, что формирователь сигнала содержит стабильный генератор частоты, подключенный выходом к входу счетчика интервала, запускающий вход которого является входом формирователя и объединен с входом триггера запрета и входом логического элемента, а выход счетчика интервала подключен к входам интервального дешифратора, подключенного к сбрасывающему входу триггера запрета, выход которого подключен к первому входу логического элемента, к запрещающему входу которого подключен выход дешифратора санкционированного кода, подключенного входами к выходу регистра санкционированного кода, вход которого является санкционированным входом формирователя, выходом которого является выход логического элемента.

6. Система по п.1, отличающаяся тем, что подсистема инерциальной навигации содержит первый, второй, третий датчики угловых скоростей и датчик ускорений, подключенные выходами к входам первого специализированного вычислительного устройства подсистемы, вход-выход которого является входом-выходом подсистемы.

7. Система по п.1, отличающаяся тем, что подсистема обработки изображений содержит n датчиков изображений, подключенных выходами к входам второго специализированного вычислительного устройства подсистемы, вход-выход которого является входом-выходом подсистемы.

8. Система по п.1, отличающаяся тем, что датчик внешнего воздействия реализован как блокинг-генератор, к базе транзистора которого подключен обратносмещенный диод.

9. Система по п.4, отличающаяся тем, что формирователь синхроимпульсов содержит первый, второй и третий перестраиваемые генераторы импульсов, установочный вход которых является одноименным входом формирователя, а выход каждого из генераторов подключен к входу своего, соответственно первого, второго и третьего, блоков фазирования, фазирующий выход каждого из которых подключен к фазирующим входам двух других блоков фазирования и фазирующим входам блока мажоритации, к синхронизирующим входам которого подключены синхронизирующие выходы блоков фазирования, а выходы блока мажоритации являются выходами метки времени, трех управляющих сигналов и синхроимпульсов.

10. Система по п.3, отличающаяся тем, что энергонезависимый накопитель содержит блок памяти, параллельно шинам записи которого включен полевой транзистор со встроенным каналом, к затвору которого подключен вход блокировки, являющийся входом накопителя.

11. Система по п.4, отличающаяся тем, что источник вторичного электропитания содержит модуль постоянного и модуль импульсного питания, силовой вход каждого из которых является силовым входом источника, а установочный вход модуля постоянного питания и три управляющих входа модуля импульсного питания являются одноименными входами источника, выходы постоянного и импульсного питания которого являются выходами соответствующих модулей.

12. Система по п.6, отличающаяся тем, что специализированное вычислительное устройство подсистемы инерциальной навигации содержит процессор, входы угловых скоростей и линейных ускорений которого являются одноименными входами устройства, вход-выход является входом-выходом устройства, объединенным с входом-выходом блока связи, а выход процессора подключен к входу первого блока микропрограммного управления и входу регистра, подключенного выходом к входам n последовательно соединенных шинами переноса умножителей, подключенных выходами к входам сумматора, подключенного выходом к блоку связи, подключенного первой двунаправленной шиной к первому специализированному запоминающему устройству, подключенного, кроме того, второй двунаправленной шиной к процессору, а вход-выход блока связи является входом-выходом специализированного вычислительного устройства.

13. Система по п.7, отличающаяся тем, что специализированное вычислительное устройство подсистемы обработки изображений содержит управляющий микропроцессор, входы и вход-выход которого являются соответственно датчиковыми входами и входом-выходом устройства, а через двунаправленную связь к нему подключено второе специализированное запоминающее устройство, через первую магистраль к нему подключено k вычислительных микропроцессоров, подключенных через вторую магистраль ко второму специализированному запоминающему устройству, причем установочный выход управляющего микропроцессора подключен к входу второго блока микропрограммного управления, выходы которого подключены к микропрограммным входам всех микропроцессоров.

14. Система по п.9, отличающаяся тем, что перестраиваемый генератор импульсов содержит первую группу последовательно включенных инверторов, выходы которых подключены к входам первого мультиплексора, выход которого является выходом генератора и подключен к входу первого инвертора и входу первого счетчика частоты, подключенного выходами к первым входам первой схемы сравнения, ко вторым входам которой подключены выходы первого регистра кода частоты, а инкрементный и декрементный выходы этой схемы подключены к одноименным входам первого счетчика кода частоты, выходы которого подключены к управляющим входам первого мультиплексора, причем входы первого регистра кода частоты и первого счетчика кода частоты являются установочным входом генератора.

15. Система по п.9, отличающаяся тем, что блок фазирования содержит элемент И, первый вход которого является входом блока, а выход подключен к входу сдвигового регистра и входу динамического счетчика, подключенного выходами через дешифратор к запускающему входу триггера останова, выход которого является фазирующим выходом блока и подключен ко второму входу элемента И и первому входу мажоритарного элемента, подключенного выходом к входу триггера пуска, подключенного выходом к сбрасывающему входу триггера останова, при этом ко второму и третьему входам мажоритарного элемента подключены выходы триггеров привязки, входы которых являются фазирующими входами блока, у которого выходы четных и нечетных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам триггеров-формирователей, выходы которых являются синхронизирующими выходами блока.

16. Система по п.11, отличающаяся тем, что модуль постоянного питания содержит первый, второй и третий конверторы, частотные выходы которых подключены к блоку управления и контроля, а входы через блок отключения подключены к входам блока выравнивания, выход которого является выходом модуля, при этом установочные входы конверторов и блока управления и контроля являются установочным входом модуля.

17. Система по п.11, отличающаяся тем, что модуль импульсного питания содержит три параллельных ветви, концы которых объединены и один из них является входом силового питания модуля, второй - выходом модуля, при этом в каждой ветви последовательно включены два полевых транзистора, а три входных управляющих сигнала разведены таким образом, что каждый из них подключен к затворам двух транзисторов, установленных в разных ветвях, образуя выборку «2 из 3».

18. Система по п.16, отличающаяся тем, что конвертор содержит последовательно включенные фильтр, трансформатор с включенным в первичную обмотку транзистором-прерывателем, выпрямляющий диод, выходной фильтр, выход которого подключен к входу преобразователя напряжения в частоту, подключенного выходом к входу элемента развязки, выход которого является частотным выходом конвертора и подключен к входу частотно-импульсного модулятора, установочный вход которого является установочным входом конвертора, а выход подключен к базе транзистора прерывателя.

19. Система по п.16, отличающаяся тем, что блок отключения содержит три полевых транзистора, истоки которых являются входами, стоки - выходами, а управляющие сигналы подключены к затворам транзисторов.

20. Система по п.16, отличающаяся тем, что блок выравнивания содержит три идентичные ветви, в каждой из которых установлены последовательно включенные резистор и диод, причем первый вывод каждого резистора является входом блока, второй подключен к аноду диода этой ветви, а катоды диодов объединены и являются выходом блока.

21. Система по п.16, отличающаяся тем, что блок управления и контроля содержит первый, второй, третий и четвертый счетчики, входы первых трех из которых являются частотными входами блока, а вход четвертого подключен к выходу устройства преобразования напряжения в частоту, подключенного входом к выходу аналогового мультиплексора, входы которого являются контрольными и дополнительным входами блока, при этом выход первого счетчика частоты подключен к первым входам первого и второго сумматоров, выход второго счетчика подключен ко второму входу первого сумматора и к первым входам второго и третьего сумматоров, выход третьего счетчика подключен ко вторым входам первого и третьего сумматоров, а выход четвертого счетчика частоты подключен к первому входу четвертого сумматора, ко второму входу которого подключен выход регистра контрольного кода, вход которого является установочным входом блока и объединен с установочным входом регистра допуска, выход которого подключен к первым входам первой, второй, третьей и четвертой схем совпадения, ко вторым входам которых подключены выходы первого, второго, третьего и четвертого сумматоров, причем выход каждой схемы совпадения подключен к входу своего, соответственно первого, второго, третьего и четвертого триггеров неисправностей, выходы которых подключены к группе логических схем, выходы которой являются выходами блока.

22. Система по п.18, отличающаяся тем, что частотно-импульсный модулятор содержит вторую группу последовательно включенных инверторов, подключенных выходами к входам второго мультиплексора, выход которого является выходом формирователя, вход которого является входом второго счетчика кода частоты, подключенного выходами к первым входам второй схемы сравнения, ко вторым входам которой подключены выходы второго регистра кода частоты, а инкрементный и декрементный выходы второй схемы сравнения подключены к одноименным входам второго счетчика кода частоты, подключенного выходами к управляющим входам второго мультиплексора, причем входы второго регистра кода частоты и второго счетчика кода частоты являются установочным входом формирователя.

23. Система по п.15, отличающаяся тем, что динамический триггер выполнен как транзисторный усилитель, к базе транзистора которого кроме резисторного делителя в качестве элемента памяти подключена LC цепь, индуктивность которой имеет рабочую обмотку и намотанную поверх нее встречно компенсационную, концы которой закорочены.

24. Система по п.18, отличающаяся тем, что фильтр содержит включенный в плюсовую шину диод, анод которого является входом, катод - выходом фильтра, между плюсовой и минусовой шинами установлен низкочастотный конденсатор, а каждая из шин через свой высокочастотный конденсатор подключена к шине земли.

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ДВИЖЕНИЕМ СУДНА | 2011 |

|

RU2463205C2 |

| ИНЕРЦИАЛЬНО-СПУТНИКОВАЯ СИСТЕМА НАВИГАЦИИ, ОРИЕНТАЦИИ И СТАБИЛИЗАЦИИ | 2008 |

|

RU2375679C2 |

| СИСТЕМА УПРАВЛЕНИЯ СУДНОМ | 2010 |

|

RU2424944C1 |

| US 8215252 B1, 10.07.2012 | |||

| US 7496434 B2, 24.02.2009 | |||

Авторы

Даты

2014-12-10—Публикация

2013-04-09—Подача