вателей сигналов, выходы которых являют.ся выходами дешифратора адреса, входы

фильтров объединены и являются входом дешифратора адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2001 |

|

RU2195774C2 |

| Устройство для передачи цифровой информации | 1987 |

|

SU1418792A1 |

| СИСТЕМА РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2003 |

|

RU2263401C2 |

| СПОСОБ МНОГОКАНАЛЬНОЙ ПЕРЕДАЧИ ПАКЕТОВ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043658C1 |

| Адаптивная телеизмерительная система | 1987 |

|

SU1494023A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| Адаптивный коммутатор телеизмерительной системы | 1980 |

|

SU877597A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Система радиосвязи с подвижными объектами | 1986 |

|

SU1401626A1 |

| Устройство для обмена информацией | 1974 |

|

SU732848A1 |

. 1. УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ЦИФРОВОЙ ИHФOP 1AЦИИ, содержащее источники информации, первые выходы которых подключены к соответствующим информационным входам коммутатора, блоки буферной памяти и генератор тактовых импульсов, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены программно-временной блок, ключи, триггер, дешифратор адреса, элемент задержки, блок сравнения, генераторы адреса и счетчики , выходы источников информации через соответствующие генераторы адреса подключены к информационному входу первого ключа, выход которого соединен с входом дешифратора адреса и через элемент задержки с информационным входом второго ключа, выход второго ключа соединен с пходами источников информации и первым управляющим входом коммутатора, выходы которого соединены с входами соответствующих блоков буферной памяти, первые выходы которых являются выходами устройства, вторые выходы блоков буферной памяти соединены с первыми входами соответствующих счетчиков, выходы которых соединены ч: первым входом блока. сравнения, выход которого соединен с вторым управляющим входом коммутатора, выход генератора тактовых импульсов соединен с вторым входом блока сравнения и первым входом программно-временного блока, информационный и управляющий выходы которого соединены соответственно с вторыми входами счетчиков и объединены с третьим входом блока сравнения и первым входом триггера, выходы дешифратора адреса соединены с вторыми входами прог(Л раммно-временного блока и триггера, выходы которого соединены с управляющими входами ключей. 2.Устройство по п. 1, о т л и ч а ющ е е с я тем, что программно-временной блок содержит коммутатор, генератор . адресов и регистры сдвига, первые выходы которых соединены с соответствующими входами коммутатора, выходы которого динены с соответствующими входами генератора адресов, объединенные первые вхо00 а ды и вторые входы регистров сдвига являются соответственно первым и вторыми входами программно-временного блока, выход генератора адресов и объединенные вторые выходы регистров сдвига являются соответственно информационными и управляющим входами программно-временного блока. 3.Устройство по п. 1, о т л и ч а ющ е е с я тем, что дешифратор адреса выполнен на формирователях сигнала, ограничителях и фильтрах, выходы фильтров че рез соответствующие ограничители соединены с входами соответствующих формирь

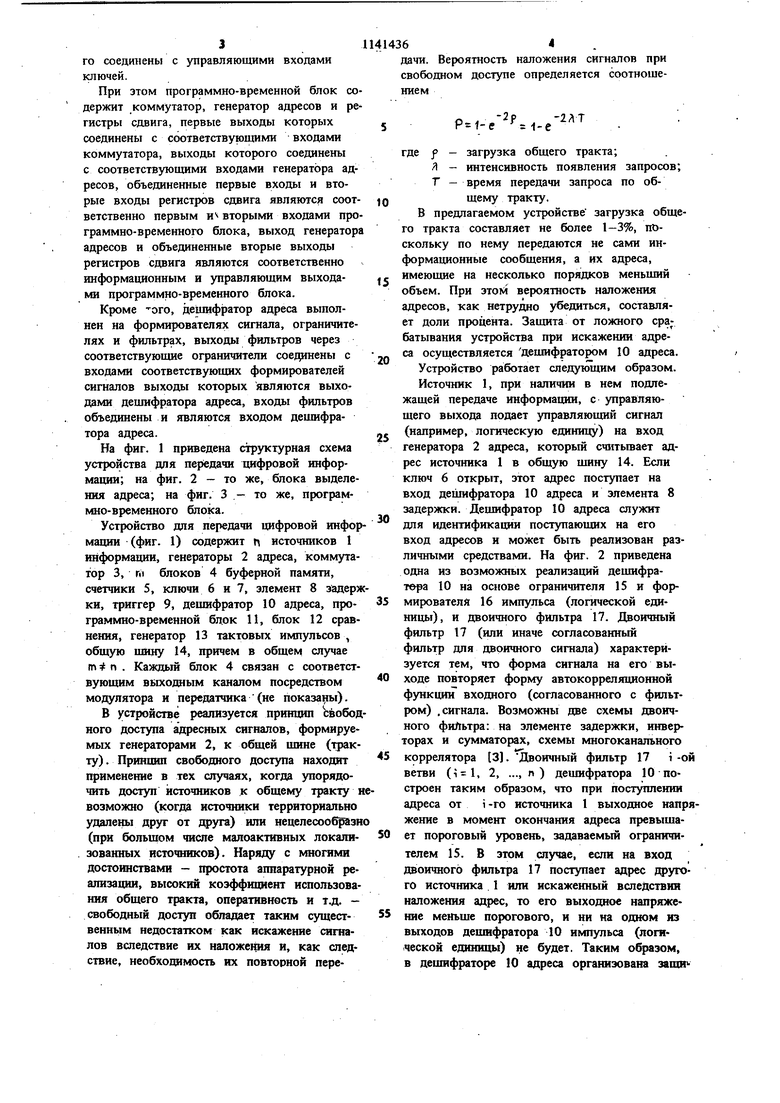

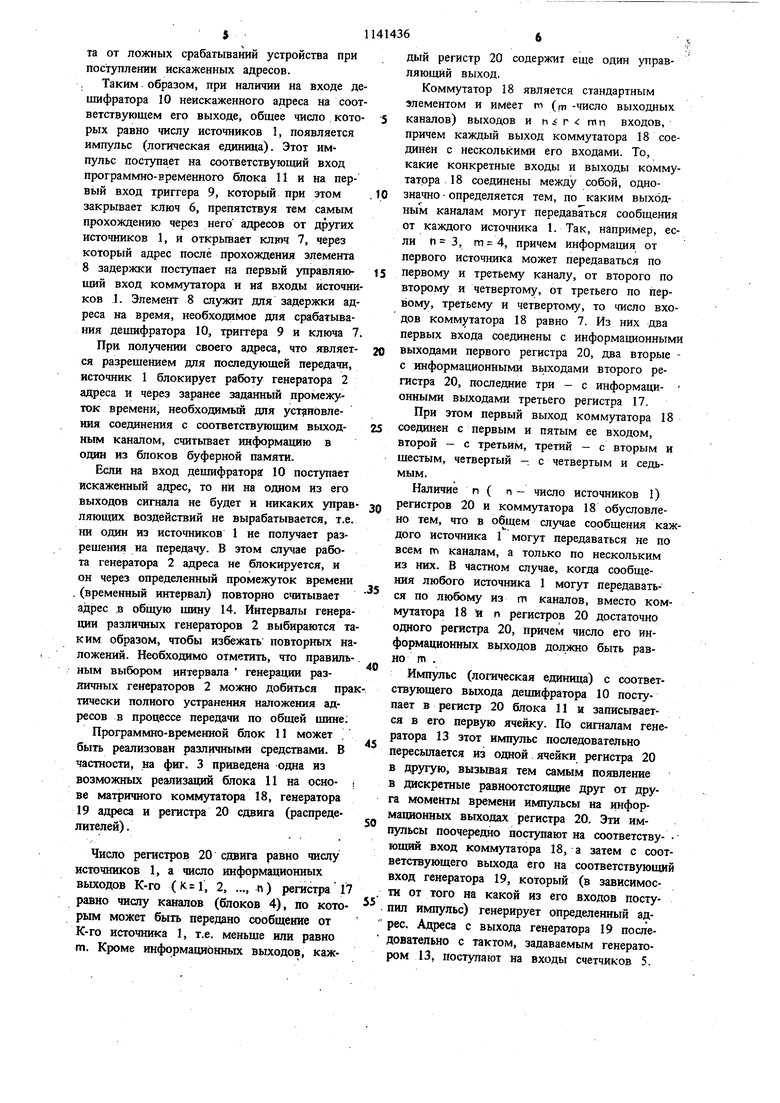

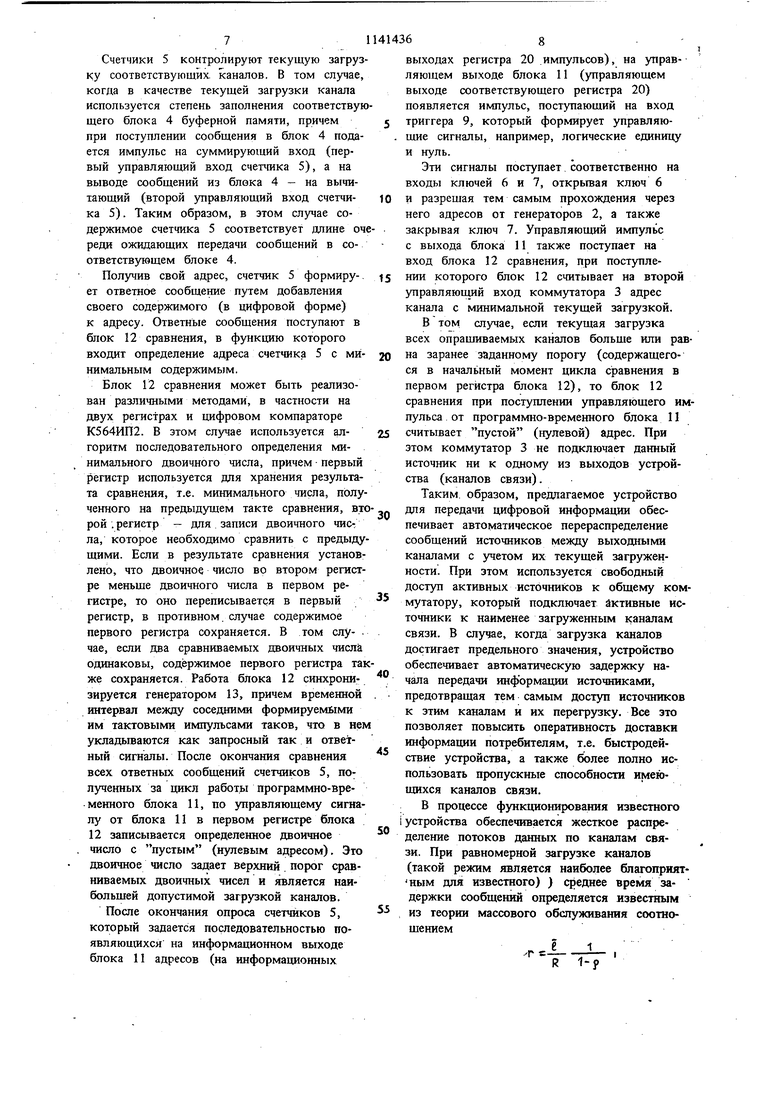

Изобретение относится к автоматике, в частности к передаче информации и может бьпъ использовано для передачи цифровых сообщений от территориально удаленных или большого числа малоактивных локализо ванных источников, информация,. от которых может передаваться по любому из заданного множества выходных каналов. Известно устройство для передачи цифровой информации, содержащее два блока обработки данных, к информационным шинам которых подключены блок системной памят для программ и данных, блоки ввода-вывода, которые управляются посредством адресов, передаваемых по адресной шине, и спе циальиых управляющих сигналов, блок памя ти состояний, подключенный к информационной шине, логические схемы, два блока буферной памяти, выход каждого из которых соединен с информационной шиной относящегося к нему блока обработки данных, вход - с информационной шиной дру го блока обработки данных, адресный деши фратор, rpjoiny переключателей 1. Однако устройство характеризуется высокой сложностью управления и невозможностью его использования в структурах, содержащих более двух блков обработки данных (процессоров, передающих блоков и т.д.)Наиболее близким техническим решением к предлагаемому изобретению является устройство для передачи цифровой информации содержащее источники информации, первые выходы которых соединены с -соответствующим информационным входом коммутатора, блоки буферной памяти, генератор тактовых импульсов, выход которого подключен к управляющему входу коммутатора, блоки ввода-вьюода информации, подключенные через соответствующие периферийные процессоры с входами блока основной памяти, подключенного к центральному процессору 2. Недостатком устройства является низкое быстродействие, обусловленное жестким закреплением за каждым источником соответствующего канала. Позтому при наличии в одном шш нескольких блоках буферной памяти очереди сообщений, ожидающих передачи по соответствующим каналам, и одного или нескольких свободных (или менее загруженных) каналов, использовать последние для передачи находящихся в других выходных блоках сообщений нельзя. Целью изобретения является повышение быстродействия устройства за счет гибкого перераспределения сообщений источников между каналами с учетом их текущей загруженности. Поставленная цель достигается тем, что в устройство для передачи цифровой информации, содержащее источники информации, первые выходы которых подключены к соответствующим информационным входам коммутатора, блоки буферной памяти и генератор тактовых импульсов, введены программно-временной блок, ключи, триггер, дешифратор адреса, элемент задержки, блоксравнения, генераторы адреса и счетчики, выходы источников информации через соответствзтощие генераторы адреса подключены к информационному входу первого ключа,, выход которого соединен с входом дешифратора адреса и через элемент задержки с информационным входом второго ключа, выход второго ключа соединен с входами источников информации и первым управляющим входом коммутатора, выходы которого соединены с входами соответствующих блоков буферной памяти, первые выходы которых являются выходами устройства, вторые выходы блоков буферной памяти соединены с первыми входами соответствующих счетчиков, выходы которых соединены с первым входом блока сравнения, выход которого соединен с вторым управляющим входом коммутатора, выход генератора тактовых импульсов соединен с вторым входом блока сравнения И первым входом программно-временно го блока, информационный и управляющий выходы которого соединены соответственно с вторыми входами счетчиков я объединены с третьим входом блока сравнения и первьгм входом триггера, выходы дешифратора адреса соединены с вторыми входами программно-временного блока и триггера, выходы которого соединены с управляющими входами ключей. При этом программно-временной блок со держит коммутатор, генератор адресов и регистры сдвига, первые выходы которых соединены с соответствующими входами коммутатора, выходы которого соединены с соответствующими входами генератора адресов, объединенные первые входы и вторые входы регистров сдвига являются соответственно первым и вторыми входами про граммно-временного блока, выход генератора адресов и объединенные вторые выходы регистров сдвига являются соответственно информационным и управляющим выходами программно-временного блока. Кроме ого, дешифратор адреса выполнен на формирователях сигнала, ограничителях и фильтрах, выходы фильтров через соответствующие ограничители соединены с входами соответствующих формирователей сигналов выходы которых являются выходами дешифратора адреса, входы фильтров объединены и являются входом дешифратора адреса. На фиг. 1 приведена стрзтстурная схема устройства для передачи цифровой информации; на фиг. 2 - то же, блока выделения адреса; на фиг. 3 - то же, программно-временного блока. Устройство для передачи цифровой инфор мации (фиг. 1) содержит п источников 1 информации, генераторы 2 адреса, коммутатор 3, Г(1 блоков 4 буферной памяти, счетчики 5, ключи 6 и 7, элемент 8 эйдерж ки, триггер 9, дешифратор 10 адреса, программно-временной бл.ок 11, блок 12 сравнения, генератор 13 тактовых импульсов , общую пшну 14, причем в общем случае m 4t п . Каждый блок 4 свяэан с соответствующим выходаым каналом посредством модулятора и передатчика (не показаны). В устройстве реализуется принцип Ьвобод ного доступа адресных сигналов, формируемых генераторами 2, к общей шине (тракту) . Принцип свободного доступа находит применение в тех случаях, когда упорядочить доступ источников к общему тракту н возможно (когда источники территориально удалены друг от друга) или нецелесообразн (при большом числе малоактивных локализованных источников). Наряду с многими достоинствами - простота аппаратурной реализации, высокий коэффициент использования общего тракта, оперативность и т.д. свободный доступ обладает таким существенным недостатком как искажение сишалов вследствие их наложения и, как следствие, необходимость их повторной передачи. Вероятность наложения сигналов при свободном доступе определяется соотношениемPM-e- 1., где f - загрузка общего тракта; Я - интенсивность появления запросов; Т - время передачи запроса по общему тракту. В предлагаемом устройстве загрузка общего тракта составляет не более 1-3%, поскольку по нему передаются не сами информационные сообщения, а их адреса, имеющие на несколько порядков меньщий объем. При этом вероятность наложения адресов, как нетрудно убедиться, составляет доли процента. Защита от ложного срабатывания устройства при искажении адреса осуществляется дешифратором 10 адреса. Устройство работает следующим образом. Источник 1, при наличии в нем подлежащей передаче информации, с- управляющего выхода подает зтравляющин сигнал (например, логическую единицу) на вход генератора 2 адреса, который считьгеает адрес источника 1 в общую шину 14. Если ключ 6 открыт, этот адрес поступает на вход дешифратора 10 адреса и элемента 8 задержки. Дешифратор 10 адреса служит для идентификации поступающих на его вход адресов и может быть реализован различными средствами. На фиг. 2 приведена одна из возможных реализаций дешнфратера 10 на основе ограничителя 15 и формирователя 16 импульса (логической единицы), и двоичного фильтра 17. Двоичный фильтр 17 (или иначе согласованный фильтр для двоичного сигнала) характеризуется тем, что форма сигнала на его выходе повторяет форму автокорреляционной функции входного (согласованного с фильтром) .сигнала. Возможны две схемы двоичного фийьтра: на элементе задержки, инверторах и сумматорах, схемы многоканального коррелятора 3. Двоичный фильтр 17 i -ой ветви (, 2, ..., п) дешифратора 10 построен таким образом, что при поступлении адреса от i -го источника 1 выходное напряжение в момент окончания адреса превышает пороговый уровень, задаваемый ограничителем 15. В этом случае, если на вход двоичного фильтра 17 поступает адрес другого источника 1 или искаженный вследствия наложения адрес, то его выходное напряжение меньше порогового, и ни на одном из выходов дешифратора 10 импульса (логи ческой едниицы) не будет. Таким образом, в дешифраторе 10 адреса организована от ложных срабатываний устройства при поступлении искаженных адресов. Таким образом, при наличии на входе де шифратора 10 неискаженного адреса на соот ветствующем его выходе, общее число которых равно числу источников 1, появляется импульс (логическая единица). Этот импульс поступает на соответствующий вход программно-временного блока 11 и на первый вход триггера 9, который при этом закрывает ключ 6, препятствуя тем самым прюхождению через него адресов от других источников 1, и открывает ключ 7, через который адрес после прохождения элемента 8 задержки поступает на первый управляющий вход коммутатора и на входы источни ков 1. Элемент 8 служит для задержки адреса на время, необходимое для срабатывания дешифратора 10, триггера 9 и ключа 7 При получении своего адреса, что является разрешением для последующей передачи, источник 1 блокирует работу генератора 2 адреса и через заранее заданный промежуток времени, необходимый для устрновления соединения с соответствующим выходным каналом, считывает информацию в один из блоков буферной памяти. Если на вход дешифратора 10 поступает искаженный адрес, то нИ на одном из его выходов сигнала не будет и никаких управ ляющих воздействий не вырабатывается, т.е. ни один из источников 1 не получает разрешения на передачу. В этом случае работа генератора 2 адреса не блокируется, и он через определенный промежуток времени . (временный интервал) повторно считывает адрес в общую шину 14. Интервалы генерации различных генераторов 2 выбираются та ким образом, чтобы избежать повторных на ложений. Необходимо отметить, что правильным выбором интервала генерации различных генераторов 2 можно добиться пра тически полного устранения наложения адресов в процессе передачи по общей шине: Программно-временной блок 11 может . быть реализован различными средствами. В частности, на фиг. 3 приведена одна из возможных реализаций блока 11 на осиове матричного коммутатора 18, генератора 19 адреса и регистра 20 сдвига (распределителей) . Число регистров 20 сдвига равно числу источников 1, а число информационных выходов К-го (, 2, ..., h) регистра17 равно числу каналов (блоков 4), по которым может быть передано сообщение от К-го источника 1, т.е. меньще или равно т. Кроме информационньи выходов, каждый регистр 20 содержит еще один управляющий выход. Коммутатор 18 является стандартным элементом н имеет п (т -число выходных каналов) выходов и п г m п входов, причем каждый выход коммутатора 18 соединен с несколькими его входами. То, какие конкретные входы и выходы коммутатора 18 соединены между собой, однозначно определяется тем, по каким выходным каналам могут передаваться сообщения от каждого источника 1. Так, например, если п 3, , причем информация от первого источника может передаваться по первому и третьему каналу, от второго по второму и четвертому, от третьего по первому, третьему и четвертому, то число входов коммутатора 18 равно 7. Из них два первых входа соединены с информационными выходами первого регистра 20, два вторые с информационными выходами второго регистра 20, последние три - с информационными выходами третьего регистра 17. При этом первый выход коммутатора 18 соединен с первым и пятым ее входом, второй - с третьим, третий - с вторым и шестым, четвертый - с четвертым и седьмым. Наличие п ( п - число источников 1) регистров 20 и коммутатора 18 обусловлено тем, что в общем случае сообщения каждого источника 1 могут передаваться не по всем m каналам, а только по нескольким из них. В частном случае, когда сообщения любого источника 1 могут передаваться по любому из m каналов, вместо коммутатора 18 и п регистров 20 достаточно одного регистра 20, причем число его информационных вькодов должно быть равно гт . Импульс (логическая единица) с соответствующето выхода дешифратора 10 поступает в регистр 20 блока 11 и записьгеается в его первую ячейку. По сигналам генератора 13 этот импульс последовательно пересылается из одной ячейки регистра 20 в другую, вызывая тем самым появление в дискретные равноотстоящие друг от друга моменты времени импульсы на информационных выходах регистра 20. Эти импульсы поочередао поступают на соответству- . ющий вход коммутатора 18, а затем с соответствующего выхода его на соответствующий вход генератора 19, который (в зависимости от того на какой из его входов поступил импульс) генерирует определенный адрес. Адреса с выхода генератора 19 последовательно с тактом, задаваемым генератором 13, поступают на входы счетчиков 5. Счетчики 5 контролируют текущую загруз ку соответствующих, каналов. В том случае, когда в качестве текущей загрузки канала используется степень заполнения соответствую щего блока 4 буферной памяти, причем при поступлении сообщения в блок 4 подается импульс на суммирующий вход (первый управляющий вход счетчика 5), а на выводе сообщений из блока 4 - на вычитающий (второй управляющий вход счетчика 5). Таким образом, в этом случае содержимое счетчика 5 соответствует длине оч реди ожидающих передачи сообщений в соответствующем блоке 4. Получив свой адрес, счетчик 5 формиру-. ет ответное сообщение путем добавления своего содержимого (в цифровой форме) к адресу. Ответные сообщения поступают в блок 12 сравнения, в функцию которого входит определение адреса счетчика 5 с минимальным содержимым. Блок 12 сравнения может быть реализован различными методами, в частности на двух perHctpax и цифровом компараторе К564И112. В этом случае используется алгоритм последовательного определения минимального двоичного числа, причем первый регистр используется для хранения результата сравнения, т.е. минимального числа, полу ченного на предыдущем такте сравнения, вт рой .регистр - для записи двоичного числа, которое необходимо сравнить с предыду щими. Если в результате сравнения установлено, что двоичное число во втором регистре меньще двоичного числа в первом регистре, то оно переписывается в первьш регистр, в противном, случае содержимое первого регистра сохраняется. В том слу- . чае, если два сравниваемых двоичных числа одинаковы, содержимое первого регистра так же сохраняется. Работа блока 12 синхронизируется генератором 13, причем временной интервал между соседними формируемыми им тактовыми импульсами таков, что в нем укладьгеаются как запросный так и ответный сигналы. После окончания сравнения всех ответных сообщений счетчиков 5, полученных за цикл работы программно-временного блока И, по управляющему сигналу от блока 11 в первом регистре блока 12 записывается определенное двоичное . число с пустым (нулевым адресом). Это двоичное число задает верхний порог q)aBниваемых двоичных чисел и является наибольшей допустимой загрузкой каналов. После окончания опроса счетчиков 5, который задается последовательностью появляющихся на информационном выходе блока 11 адресов (на информационных 68 выходах регистра 20 .импульсов), на jTtpaBляющем выходе блока 11 (управляющем выходе соответствующего регистра 20) появляется импульс, поступающий на вход триггера 9, который формирует управляющие сигналы, например, логические единицу и нуль. Эти сигналы поступает. соответственно на входы ключей 6 и 7, открывая ключ 6 и разрещая тем самым прохождения через него адресов от генераторов 2, а также закрывая ключ 7. Управляющий импульс с выхода блока 11 также поступает на вход блока 12 сравнения, при поступлении которого блок 12 считывает на второй управляюпшй вход коммутатора 3 адрес канала с минимальной текущей загрузкой. В том случае, если текущая загрузка всех опрашиваемых каналов больще или равна заранее заданному порогу (содержащегося в начальный момент цикла сравнения в первом регистра блока 12), то блок 12 сравнения при поступлении управляющего импульса от программно-временного блока 11 считывает пустой (нулевой) адрес. При зтом коммутатор 3 не подключает данный источник ни к одному из выходов устройства (каналов связи). Таким, образом, предлагаемое устройство для передачи цифровой информации обеспечивает автоматическое перераспределение сообщений источников между выходными каналами с учетом их текущей загруженности. При зтом используется свободный доступ активных источников к общему коммутатору, который подключает Активные источники к наименее загруженным каналам связи. В случае, когда загрузка каналов достигает предельного значения, устройство обеспечивает автоматическую задержку начала передачи информации источниками, предотвращая тем самым доступ источников к зтим каналам и их перегрузку. Все это позволяет повысить оперативность доставки информации потребителям, т.е. быстродействие устройства, а также более полно использовать пропускные способности имеющихся каналов связи. В процессе функционирования известного устройства обеспечивается жесткое распределение потоков данных по каналам связи. При равномерной загрузке каналов (такой режим является наиболее благоприятным для известного) ) среднее время задержки сообщений определяется известным из теории массового обслуживания соотношением

где р - коэффициент загрузки Каналов

связи; f - срепяяя длина информационных

сообщений; R - пропускная способность каналов

связи.

В предлагаемом техническом решении перераспределение потоков информации бсуществляется па основе текущей информации о степени загруженности выходных каналов связи. Для зтого получена следующая формула 4 для расчета среднего времени задержки я ггаллскявальной системе: г - ч

, . .

Из приведенных соотношений видно, в этом случае предлагаемое техническое решение позволяет в.

1+р

уменьшить среднее время задержки сообщений, то есть в ( ) раз повысить

onepaijiBHocTb (быстродействие) по сравнению с известным. Поскольку в нормальном ре- жиме козффициент загрузки канала связи составляет 0,8-0,9, то при равных техничесйих характеристиках каналов предлагае-.

мое устройство обеспечивает почти двухкратное повышение оперативности по сравнению с известным.

Если число каналов , то, как показьгеают результаты имитационного моделирования на ЭВМ, потенциальный выигрьпп предлагаемого устройства по сравнению с известным ; пропорционален числу fn , т.е. увеличивается с ростом числа каналов.

i

i

Фиг.

Авторы

Даты

1985-02-23—Публикация

1983-10-21—Подача