{Компаратора являются входами устав;ки, выходы первого и второго цифро 8ых KotoiapaTopoB связаны соответ

ственно с первым и вторым входами элемента 2И, выход которого являетс|1 выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения фаз | 1987 |

|

SU1494102A1 |

| Устройство фазового пуска | 1984 |

|

SU1225035A1 |

| Формирователь последовательности импульсов | 1982 |

|

SU1094137A1 |

| УСТРОЙСТВО КОНТРОЛЯ РАЗНОСТИ ФАЗ ДЛЯ РЕЛЕЙНОЙ ЗАЩИТЫ | 1999 |

|

RU2153681C1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Устройство сжатия цифрового телевизионного сигнала | 1985 |

|

SU1334397A1 |

| Устройство синхронизации с м-последовательностью | 1984 |

|

SU1218484A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| Устройство для определения содержания связующего в стеклопластиках | 1984 |

|

SU1265538A1 |

УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ФАЗ. содержащее формирователи электрических величин, на входа которых подают сравнигд.емые величины, два.инвер-, тора, три R-5-триггера и два элемента 2И-НЕ, причем выход первого формирователя . с первым входом первого RS -триггера и через первый инвертор - с первым входом второго R-5-триггера, выход второго формирователя связан с вторым входбм первого R-S-триггера и через второй инверг тор - с вторым входом второго К-5триггера, первые Выходы первого второго R-S -триггеров связаны с входами первого элемента 21J-HE, вторые выходы первого и второго S-5 -тригге- . ров связаны с входами второго элемента 2И-НЕ, выходы Первого и второго элементов 2И-НЕ связаны соответ- У первым и вторым входами третьего R-6-триггера, о т л и ч а ю ц е е с я тем, что, с целью :: , : V- N/ расширения функциональных возможностей путем обеспечения регулировки границ зоны срабатывания, в него дополнительно введены третий инвертор, мультиплексор, генератор импульсов стабильной Частоты, элемент задерж«сй, двоичный счетчик, параллельный регистр памяти, первый и второй цифровые компараторы и элемент 2И, причем выход первого элемента 2И-НЕ дополнительно связан с первым информационным входом мультиплексора, выход второго элемента 2И-НЕ дополнительно связан через третий инвертор с вторым информационным входом § мультиплексора, первый выход третьего 1 -5 -триггера связан с третьим (Л упра.вляющим входом мультиплексора и с h -м информационным входом регистра памяти, а второй выход третьего Ц-5-триггера - с четвертым управляющим входом мультиплексора, который свежи выходом связа:Н с запускающим входом генератора импульсов стабильной частоты, вторым входом сброса двоичного :л счетчика через элемент задержки и (ll+i)-M тактовым входом регистра э& памяти, выход генератора связан с со первым тактовым входом двоичного 9) С ч;етчикА, который своими первым, вто рым, .. ,(h-l)-M выходами связан соответственно с первым, вторым, .. , (й О м инфЬрмационньм входаtiK регистра памяти, который своим П-разрядным выходом связан с вторым П -разрядным входом первого цифрового компаратора и первым } разрядным входом второго цифрового компаратора, причем первый tt -разрядный вход кокшаратора и второй И разрядньй вход второго ;

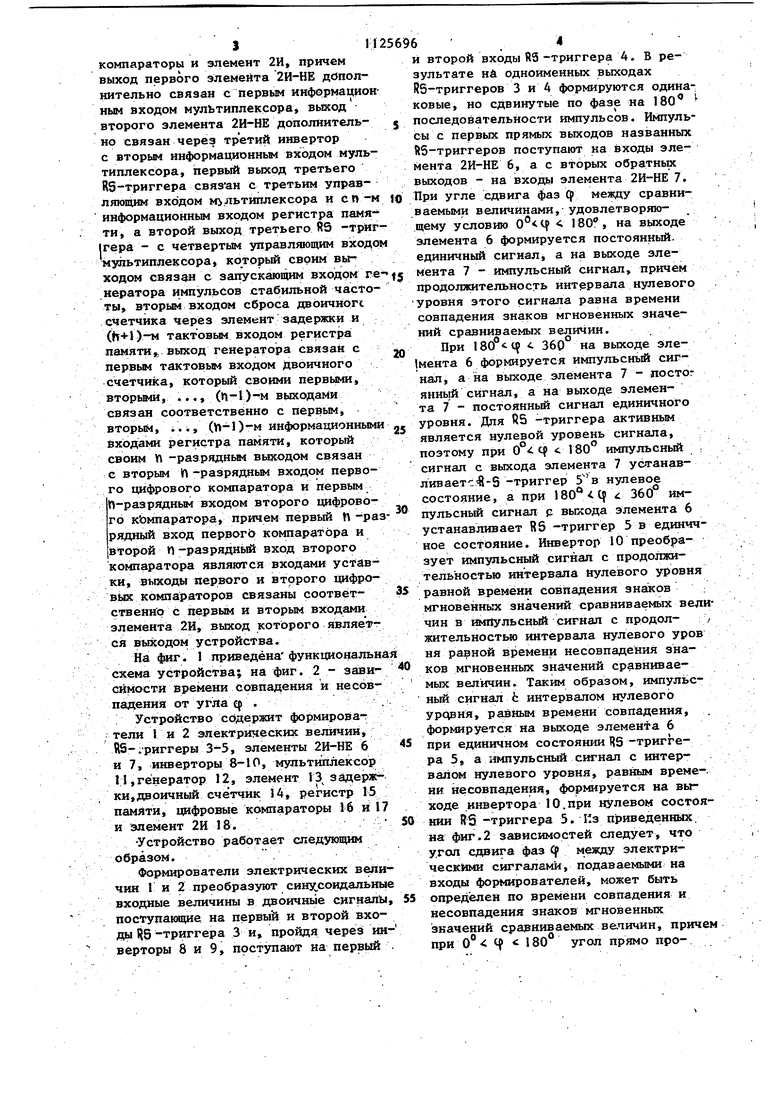

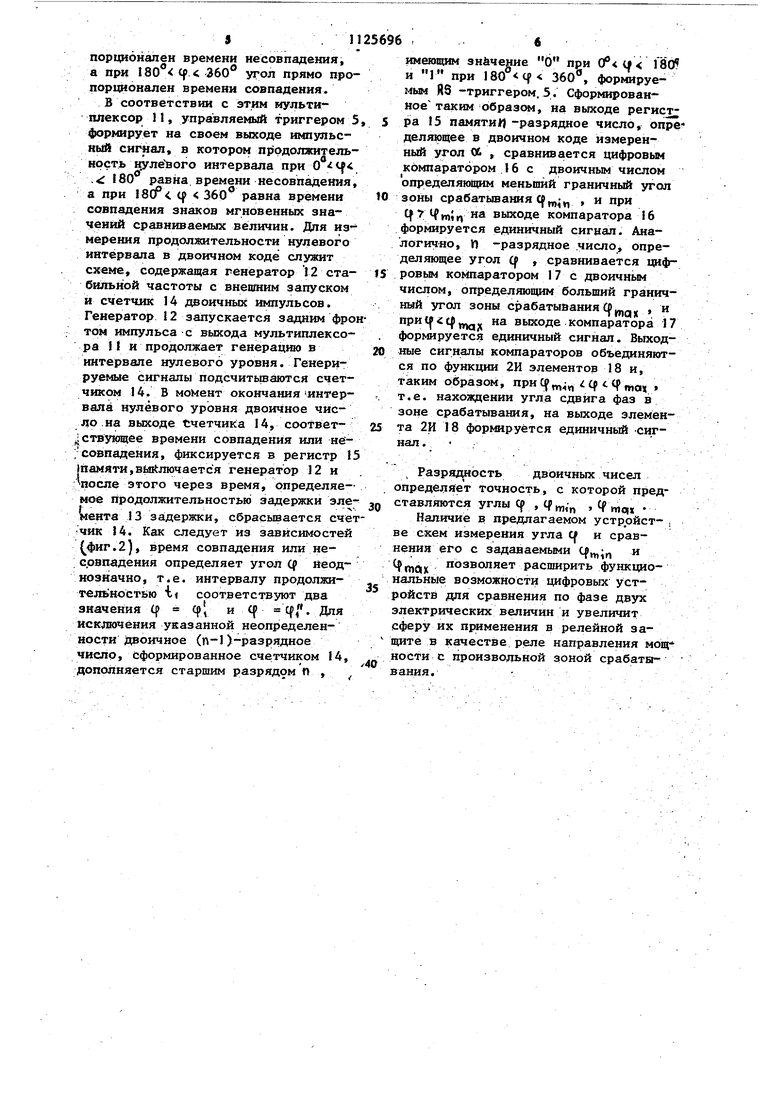

Изобретение относится к области релейной защиты и может применяться в цифровых комплексах релейной защи TU и автоматики энергосистем, вклю- чающих в себя микропроцессоры или шкро-ЭВМ, в которых уставки измерительных органов автоматически изменяются при изменении режима работы энергосистемы. Известно рел1енаправления мощности« позволяющее осуществлять электрическую регулировку зоны срабаты вания, на основе использования п&роговых эле&ентов с зоной нечувствительности, выполненных на операционных усилителях llj . Недостатком указанного анагюгово го реле в цифровьп: комплексах, включающих микропроцессы и микро-ЭВМ, является усложнение последних, вы званное необходимостью применения согласующих щ фроаналоговых и аналого-цифровых преобразователей и допол нительных источников питания для операционных усилителей. Известны также устройства дпЯ сравнения по фазе двух электрических величин, реализованные на цифровой элементной базе fzl и |з . .Недостаткам данных устройств явля ется невозможность изменения границ зоны срабатывания. Нш1более близким по технической сущности к изобретению является уст;ройство для сравнения фаз, содержащее формирователи электрическшс величин, на входы которых подаются/ сравниваемые величины, два инвертора, три R5 -триггер1а и два элемента 2Й-НЕ, причем выход первого формирователй соединен с первым входом рервого R9 -триггера и через первый инвертор т с первым входо второго 95-триггера, выход второго формирова теля с:Ёязан с вторым входом первого вЗ-триггера и через второй инвертор - с вторым входом второго RS Tpifi repa, первые выходы первого и второго RS -триггеров связаны с первого элемента 2И-НЕ, в торые выходы первого и второго RS -триггеров связаны с входами второго элемента 2И-НЕ, выходы первого и второго, элементов 2И-НЁ связаны соответ твённо г первым и вторым входами третьего R6 -триггера 4j. Недостатком известного устройства является то, что оно по принципу своего действия имеет фиксироваиные границы зоны срабатывания, что ограничивает его применение в цифровых устройствах релейной за1циты. Целью изобретения является расщи рение функциональных возможностей устройства путем обеспечения регулИ ровки границ зоны срабатывания, Поставленная цель достигается тем, что в устройство дпя срг нения фаз, содержащее формирователи электри ческих величин, на входы которых подшот сравниваете величины, два инвертора, три R5-триггера, .и два элемента 2H-HEi причем выход первого, формирователя соединен с первым входом первого R5 -триггера и через первый инвертор - с первым входом второго Н5 -триггера, выход второго формирователя связан с вторым входом, первого RS -триггера и через второй инвертор - с вторым входом второго . R5-триггера, первые выходы первого и второго RS-триггеров связаны с рхог. дами первого элемента 2И-НЕ, вторые выходы первого и второго RS -триггеров связаны с входами второго элемента 2И-НЕ, выходы первого и второго элементов 2И-НЕ связаны соответственно с первым и вторым входами третьего 85 -триггера, дополнительно введены инвертор, мультиплексор генератор импульсов стабильной частоты, элемент задержки, двоичный счетчик, параллельный регистр ПШ4ЯТИ, первьй и второй цифровые компараторы и элемент 2И, причем выход первого элемейта 2И-НЕ дополнительно связан с первым информацион ным входом мультиплексора, выход второго элемента 2И-НЕ дополнительно связан через третий инвертор с вторым информационным входом мультиплексора, первый выход третьего RS-триггера с третьим управляющим входом мультиплексора и сп -м информационным входом регистра памяти, а второй выход третьего RS -трй jrepa - с четвертым управляющим вход мультиплексора, который своим выходом связ с запускающим входом r нератора импульсов стабильной часто ты, вторым входом сброса двоичногс счетчика через элемент задержки и (h+l)-M тактовым входом регистра памяти выход генератора связан с первым тактовым входом двоичного счетчика, который своими первыми, вторыми, ..., (Г|-1)-м выходами связан соответственно с первым, вторым, i.i, (h-l)-M информационным входами регистра памяти, который своим -разрядным выходом связан с вторым tt-разрядньм входом первого цифрового компаратора и первым П-разрядным входом второго цифрового компаратора, причем первый ft -ра рядный вход первогЬ компаратора и второй П-разрядный вход второго компаратора являются входами уст авки, выходы первого и второго цифровых компараторов связаны соответственнъ с и вторым входами элемента 2И, выход которого является выходом устройства. На фиг. 1 Приведенафункциональн схема устройства; на фиг. 2 - зависймости времени совпадения и несовпадения от угла Cf . ; Устройство содержит формироваг тели 1 и 2 электрических величин, RS-триггеры 3-5, элементы 2И-НЕ 6 и 7, инверторы 8-10, мультиплексор 1:1 jгенератор 12, элемент 13 задерж ки,двоичный счетчик 14, регистр 15 памяти, цифровые компараторы 16 и 1 и элемент 2И 18. Устройство работает следующим образом.. Формирователи электрических вели чин 1 и 2 преобразуют сину соидальны входные величины в двоичные сигналы поступающие на первый и второй входы R5 -триггера 3 и, пройдя через ин верторы 8 и 9, поступшот на первый и второй входы R3-триггера 4. В результате на одноименных выходах Н5-триггеров 3 и А формируются одинаковые, но сдвинутые по фазе на 180 последовательности импульсов. Импульсы с первых прямых выходов названных Я5-триггерОв поступают на входы элемента 2И-НЕ 6, а с вторых обратньк выходов - на входа, элемента 2И-НЕ 7. При угле сдвига фаз (р между сравниваемыми величинами,-удовлетворяющему условию 180, на выходе элемента 6 формируется постоянный, единичный сигнал, а на выходе элемента 7 - импульсный сигнал, причем продолжительность интервала нулевого уровня этого сигнала равна времени совпадения знаков мгновенных значений сравниваемых величин. При 180 t i. Збр на выходе элемента 6 формируется импульсный сигнал, а на выходе элемента 7 - постог яиный сигнал, а на выходе элемента 7 - постоянный сигнал единичного уровня. Для R5 -триггера активным является нулевой уровень сигнала, поэтому при 0° cjp 180 импульсный сигнал с выхода элемента 7 устанавливаетс/в-З -триггер 5в нулевое состояние, а при 180( 360 импульсный сигнал р выхода элемента 6 устанавливает R6 -триггер 5 в единичное состояние. Инвертор 10 преобразует импульсный сигнал с продолжительностью интервала нулевого уровня равной времени совпадения знаков : мгновенных значений сравниваемых величин в и4Пульснь)й сигнал с продол- / жительностыо интервала нулевого уров ня равной времени несовпадения знаков мгновенных значений сравниваемых величин. Таким образом, импульсный сигнал t интервалом нулевого УРЧВНЯ, равным времени совпадения, . формируется на выходе элемента 6 при единичном состоянии 43 -триггера 5, а нмпульсньй сигнал с интервале нулевого уровня, равным време-. ни несовпадения, формируется на выходе инвертора 10.при чУлевом состоянии RS -триггера 5. Из приведенных, на фиг.2 зависимостей следует, что угол сдвига фаз Ср между электрическими сиггалами, подаваемыми на входы формирователей, может быть определен по времени совпадения и несовпадения знаков мгновенных значений сравниваемых величин, причем при О 180 угол прямо пропорционален времени несовпадения, а ПРИ 180 if Збо УГОЛ прямо пропорционален времени совпадения. В соответствии с этим мультиплексор II, управляемый триггером 5 формирует на своем выходе импульсный сигнал, в KOTopobf продолжительность нулевого интервала при О .i 180 равна, времени несовпадения. а при 18СР ц 360 равна времени совпадения знаков мгновенных значений сравниваемых величин. Дпя измерения продолжительности нулевого интервала в двоичном коде служит схеме, содержащая генератор 12 стабильной частоты с внешним запуском и счетчик 14 двоичных импульсов. Генератор 12 запускается задним фро том импульса с выхода мультиплексора II и продолжает генерацию в интервале нулевого уровня. Генерируемые сигналы подсчитьшаются счетчиком 14. В момент окончания-интервала нулевого уровня двоичное число . на вюсоде счетчика 14, соответ.ствующее времени совпадения или не;совпадения, фиксируется в регистр 1 (памяти,выйлючается генератор 12 и после Этого через время, определяемое продолжительностью задержки эле «вита 13 за:держки, с&расывается сче чик 14. Как следует из зависимостей {фиг.2), время совпадения или несовпадения определяет угол Ср неоднозначно , т.е. интервалу продолжительностью ii соответствуют два 1 и (f . Для значения 4f vf, исключения указанной неопределенности двоичное (п-1)-разрядное число, сформированное счетчиком 14, дополняется старшим разрядом п , имеющим знёчение 6 при (f | l80 и 1 при 180 Ч 360, формируемым R6 -триггером. 5. Сформированноетаким образсш, на выходе регистра 15 памятиИ -разрядное число, опре деляющее в двоичном коде измеренный угол tt , сравнивается цифровым компаратором 16 с двоичным числом определякздим меньший граничный угол зоны срабатывания , и при Cf7if ; на выходе компаратора 16 формируется единичный сигнал. Аналогично, И -разрядное .число, определяющее угол ср сравнивается цифровым компаратором 17 с двоичным числом, оттределяющим больший граничный угол зоны срабатывания ttjjj-. , и npHty tf на выходе компаратора 17 формируется единичный сигнал. Выходные сигналы компараторов объединяются по функции 2И элементов 18 и, таким образом, прн Cf „ Cf Я mat . т.е. нахождении угла сдвига фаз в зоне срабатывания, на выходе элемента 2И 18 формируется единичный -сигнал . . Разрядаость двоичных чисел определяет точность, с которой представляются углы ср , q fn , ,, . Наличие в предлагаемом устррйст- , ве схем измерения угла С и сравнения его с задаваемыми и f тох позволяет расширить функциоальные возможности цифровых устойств для сравнения по фазе двух лектрических величин и увеличит феру их применения в релейной заите в качестве реле направления мощ ости с произвольной зоной срабатыания.

п

п п

а) у 1,5

; 0:

1Д|1|ШПППГ

m ff

n n n n

/7f-n

d)

y 27ff

Авторы

Даты

1984-11-23—Публикация

1983-11-09—Подача