ледовательности. Сегменты принимав-, мой и местной МП соответственно, с PC 3 и PC 4 сравниваются в цифровом компараторе 15.. Если на протяжении if тактов происходит неискаженный .прием МП, то сигнал лог. 1 с прямого выхода счетчика 9 блокирует его. Этот сигнал м. использоваться как сигнал.установления синхронизации. При нарушении синхронизма сигнаш лог. 1 с цифрового компаратора разрешает счетчику 8 счет импульсов генератора 7 тактовых импульсов. ЕсГ

Изобретение относится к радио связи и может использоваться в системах связи с шумоподобными сигналами.

Цель изобретения - сокращение вре мени вхождения в синхронизм при одновременном повышении достоверности установления наличия синхронизма

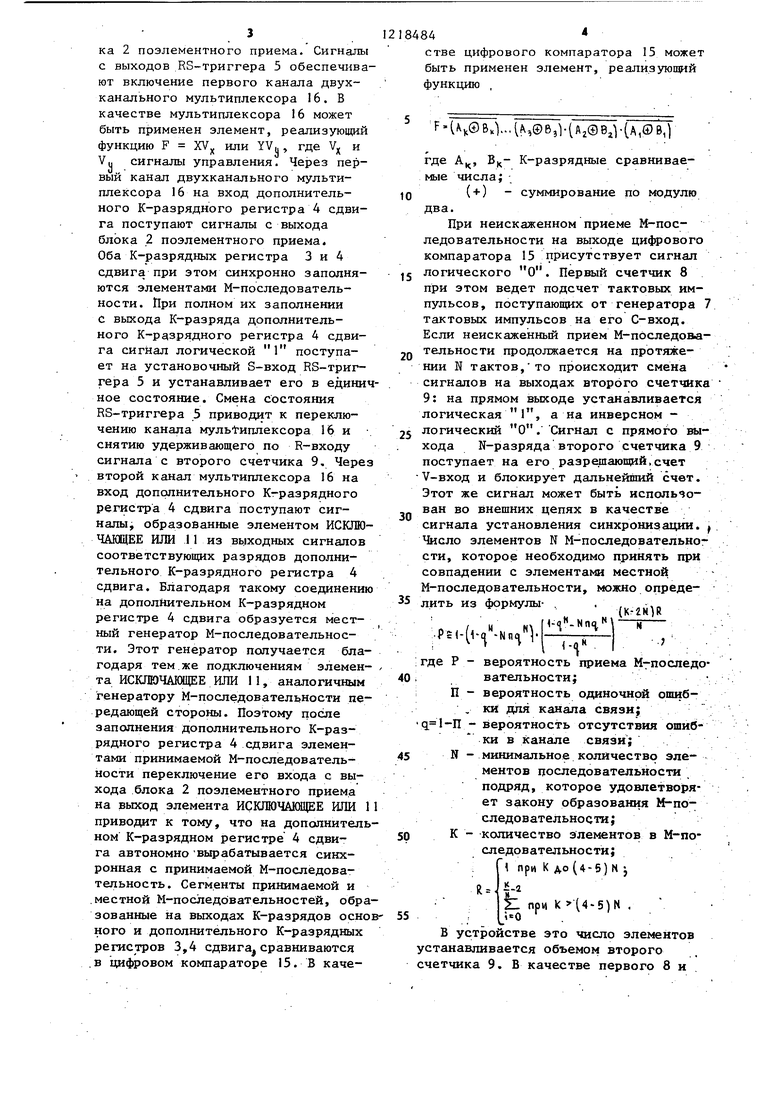

На чертеже представлена структурная электрическая схема устройст- ва синхронизации с М-последователь- ностью.

Устройство синхронизации с М-пос ледовательиостью содержит фильтр 1, блок 2 поэлементного приема, основ- ной К-разрядный регистр 3 сдвига, дополнительный К-разрядный регистр 4 сдвига, RS-триггер 5 делитель 6 частоты, генератор 7 тактовых импульсов, первьШ 8 и второй 9 счетчики, детектор 10 уровня, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11, формирова-. тель 12 импульсов установки начального состояния, первый 13 и второй 14 элементы ИЛИ, цифровой компара- тор 15, двухканальный мультиплексор 16. Формирователь 12 импульсов установки начального состояния содержит D-триггер 17, интегратор 18.

.Устройство синхронизации с М-по- следовательностью работает следующим образом.

В исходном состоянии (при отсутствии на входе устройства сигнала и включенном питании) на выходе детектора 10 уровня формируется сигли нарушение синхронизма более, чем задано, то сигнал лог. 1 со счетчика 8 поступает на формирователь 12 импульсов установки начального состояния. Импульс с зтого блока через элемент ИДИ 13 устанавливает PC 3,4 и RS-триггер 5 в начальное состояние. ДеЛитель 6 частоты и элемент ИЛИ 14 задают длительность отрезка МП, на котором определяется несинхронность , путем обнуления счетчика 8 . 1 з.п.ф-лы 1 ил.

нал, соответствующий логической 1 Этот сигнал через первый элемент ИЛИ 13 устанавливает в исходное (нулевое) состояние основной 3 и дополнительный 4 К-разрядные регистры сдвига и RS-триггер 5. С инверсного выхода RS-триггера 5 сигнал, соответствующий логической 1., поступает на R-вход Второго счетчика 9, который под действием этого сигнала устанавливается и удерживается в нулевом состоянии. В результате этого устанавливается и удерживается в нулевом состоянии и первый счетчик 8 по R-входу через второй элемент ШШ 14 сигналом с инверсного выхода второго счетчика 9. Сигнал принимаемой М-последова- тельности фильтруется в фильтре 1 и поступает на блок 2 поэлементного приема и детектор 10 уровня. В качестве детектора 10 уровня может быть применен, например, амплитудный детектор с инвертором на выходе В блоке 2 поэлементного приема по мере поступления символов М-последо вательности производится их оценка и запись в основной К-разрядный регистр 3 сдвига. Блок 2 поэлементного приема может быть выполнен, например, на D-триггере, информационный D-вход которого соединяется с основньм входом блока 2 поэлементного приема, дополнительный вход которого соединяется с тактовым С-в дом D-триггера, прямой выход которого соединяется с выходом бло3

ка 2 поэлементного приема. Сигналы с выходов RS-триггера 5 обеспечивают включение первого канала двух- канального мультиплексора 16. В качестве мультиплексора 16 может быть применен элемент, реализующий функцию F XVj( или YVa, где V, и У и сигналы управления. Через первый канал двухканального мультиплексора 16 на вход дополнительного К-разрядного регистра 4 сдвига поступают сигналы с выхода блока 2 поэлементного приема. Оба К-разрядных регистра 3 и 4 сдвига при этом синхронно заполняются элементами М-последователь- нос ти. При полном их заполнении с выхода К-разряда дополнительного К-разрядного регистра 4 сдвига сигнал логической 1 поступает на установочный S-вход RS-триггера 5 и устанавливает его в единичное состояние. Смена состояния RS-триггера 5 приводит к переключению канала мyльtишleкcopa 16 и снятию удерживающего по R-входу сигнала с второго счетчика 9, Через второй канал мультиплексора 16 на вход дополнительного К-разрядного регистра 4 сдвига поступают сигналы, образованные элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 11 из вь1ходных сигналов соответствующих разрядов дополнительного К-разрядного регистра 4 сдвига. Благодаря такому соединению на дополнительном К-разрядном регистре 4 сдвига образуется местный генератор М-последовательнос- ти. Этот генератор получается благодаря тем.же подключениям элемен- та ИСКПЮЧАЩЕЕ ИЛИ П, аналогичным генератору М-последовательности передающей стороны. Поэтому после заполнения дополнительного К-разрядного регистра 4 сдвига элементами принимаемой М-последовательности переключение его входа с выхода блока 2 поэлементного приема на выход элемента ИСКЛЮЧАИЩЕЕ ИЛИ приводит к тому, что на дополнительном К-разрядном регистре 4 сдвига автономно вырабатывается синхронная с принимаемой М-последова- тельность. Сегменты принимаемой и .местной М-последовательностей, образованные на выходах К-разрядов осноного и дополнительного К-разрядных регистров 3,4 сдвига сравниваются в цифровом компараторе 15. В каче18484

стве цифрового компаратора 15 может быть применен элемент, реализуюпяй функцию

р.(,у.,(А,®В,1-(А2®8,1-(А,0В,

где А, Вц- К-разрядные сравниваемые числа;

(+) - суммирование по модулю два.

При неискаженном приеме М-последовательности на выходе цифрового компаратора 15 присутствует сигнал логического О. Первый счетчик 8

0

5

при этом ведет подсчет тактовых импульсов, поступающих от генератора 7 тактовых импульсов на его С-вход. Если неискаженный прием М-последоаа- тельности продолжается на протяжении N тактов, то происходит смена сигналов на выходах второго счетчика 9: на прямом выходе устанавливается логическая 1, а на инверсном - логический О. Сигнал с прямого и.1- хода N-разряда второго счетчика 9 поступает на его разрешающий,счет - V-вход и блокирует дальнейгиий счет. Этот же сигнал может быть использован во Внешних цепях в качестве сигнала установления синхронизации. : элементов N М-последовательности, которое необходимо принять при совпадении с элементами местной М-последовательности, можно опреде- лить из формулы- ,

0

:.p(-(

-(|

{K-lNlR

.

0

5

0

;где Р - вероятность приема М последо- . вательиости;

П - вероятность одиночной ощиб, кк для канала связи; - вероятность отсутствия ошиб ки в канале связи; N - минимальное количество элементов последовательности подряд, которое удовлетворяет закону образования М-последовательности;К - количество элементов в М-по- следовательиости; при К до(4-6)N J

ii .

11

il при (4-5)N .

UO

В устройстве это число элементов устанавливается объемом второго счетчика 9. В качестве первого 8 и

второго 9 счетчиков в устройстве могут быть применены счетчики в виде интегральных микросхем. После подсчета N элементов вторым счет.чи- , ком 9 устройство переходит в режим слежения за сохранением синхронизма. Если синхронизм сохраняется, то иа выходах цифрового компаратора 15 присутствует сигнал логического JQ Р, который запрещает счет тактовых импульсов первым счетчиком 8. При нарушений синхронизации на выходе цифрового компаратора 15 устанавливается сигнал логической 1, кото- J5 рый поступает на разрешающий счет (У-вход с инверсией первого счетчика 8 и разрешает ему счет тактовых импульсов, поступающих на тактовый С-вход с инверсией. Тактовый С-вход 20 с инверсией у первого счетчика 8 использован с целью разнесения процессов счета первого 8 и второго 9 счетчиков, что исключает сбои в формировании импульсов начальной уста- 25 новки по их сигналам. Если нарушение синхронизации проявляется на числе элементов более, чем задано для установленного отрезка М-пос- ледовательности, то происходит ЗО переполнение первого счетчика В. Сигналом логической 1 с выхода первого счетчика 8 D-триггер 17 формирователя 12 импульсов установки начального состояния переводится в единичное состояние по S-входу. Сигнал логической 1 с прямого выхода D-триггера 17 длится до тех пор, пока на выходе интегратора 18 не установится сигнал логической 1 JQ Выбором постоянной времени этой цепи и задается длительность импульса начальной установки, достаточной для перевода в начальное состо- : яние основного и дополнительного К-разрядных регистров 3,4 сдвига: и RS-триггера 5 через первый элемент ИЛИ 13. Импульс начальной установки в этом случае переводит устройство в режим установления синхронизации .Длительность отрезка М-после- довательности, за который определяется число элементов, принимаемых не синхронно с элементами местной последовательности, задается делителем 6 частоты за счет деления час- тоты тактовой последовательности в требуемое число раз и периодиче- ским обнулением первого счетчика 8

35

45

50

, JQ J5 20 25 ЗО Q

5

5

0

через второй элемент ИЛИ 14 импуль-- сами делителя 6 частоты. При поступлении на вход устройства только помех, уровень которых достигает уровня сигнала, на выходе цифрового компаратора 15 сигналы логической 1 йоявляются прежде, чем произойдет, переполнение второго счетчика 9. В результате в D-триггер 17 записывается сигнал логической 1, подаваемый на его й нфо.р- мационный D-Bxofltc инверсного выхЪ- да второго счетчика 9 каждым сигналом цифрового компаратора 15 за счет воздействия этого сигнала на тактовый С-вход D-триггера 17. Сформированный при этом импульс начальной установки возвращает уст- ройство в исходное состояние.

При уровне сигнала на входе устройства ниже установленного рабочим на выходе детектора 10 уровня присутствует сигнал логической J, который удерживает устройство в исходном состоянии. Величину рабочего уровня сигнала можно задавать путем изменения характеристики детектора 10 уровня.

Формула изобретения

1.Устройство синхронизации с М-последовательностью, содержащее на входе последовательно соединенные фильтр и блок поэлементного приема, выход которого подключен к информационному D-входу основного К-разрядного регистра сдвига, а также RS-триггер, дополнительный К-раз- рядный регистр сдвига и генератор тактовых импульсов, выход которого подключен к входу делителя частоты, о тли чающееся тем, что, с целью сокращения времени.вхождения в синхронизм при одновременном повьшении достоверности установле- ,ния наличия синхронизма, в него вве- день: цифровой компаратор, двухка- нальный мультиплексор, первый и второй счетчики, первый и второй элементы ИЛИ, детектор уровня, элемент ИСКПЮЧАЩЕЕ ИЛИ и формирователь импульсов установки начального состояния, к первому входу которого и разрешающему счет V-входу первого счётчика подключен выход цифрового компаратора, а вьйсод формирователя импульсов установки начального соетояния подключен к первому входу первого элемента ИЛИ, к второму вхду которого через детектор уровня подключен выход фильтра, при этом прямой выход первого счетчика подключен к второму входу формирователя импульсов установки начального состояния, к третьему входу которого и первому входу второго элемента ИЛИ подключен инверсный выход второго счетчика, прямой выход которого подключен к разрешающему счет V-входу, к тактовому С-входу второго сче.тчика, а также к тактовым С-входам первого счетчика, основного и дополнительного К-раз- рядных регистров сдвига, к дополнительному входу блока поэлементного приема подключен выход генератора тактовых импульсов, причем к установочному R-входу первого счетчика подключен выход второго элемента ИЩ., к второму входу, которого подключен выход делителя чатоты, а к установочному R-входу второго счетчика и первому управляющему входу двухканального мультиплексора - инверсный выход RS- триггера, прямой выход которого под ключе; к второму управляющему вход двухканального мультиплексора к входам первого и второго каналов которого подключены соответственно выходы блока поэлементного приема и элемента ИСКЛЮЧАКЩЕЕ ИЛИ, а выРедактор Н.Швыдкая

Заказ 1139/61Тираж 624

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35,Раушская наб., д. 4/5

Филиал ШШ П,тент, г. Ужгород, ул. Проектная, 4

ход двухканального мультиплексора подключен к информационному D-BXO- , ду дополнительного К-разрядного реги- 5 стра сдвига, к установочному R-входу которого, а также к установочным R-входам основного К-разрядного регистра сдвига и RS-триггера подключен выход первого элемента ИЛИ, а

10 к установочному S-входу RS-триггера - выход последнего К-разряда дополнительного К-разрядного регистра сдвига, выходы всех разрядов которого подключены к входам эле5 мента ИСКПЮЧАНЯЦЕЕ ИЛИ и соответствующим входам разрядов первого сравниваемого числа цифрового компаратора, к входам разрядов второго сравниваемого числа которого под0 ключены выходы разрядов основного К-разрядного р егистра сдвига.

2. Устройство ПОП.1, отли- ч а ю щ е е с я тем, что формирователь импульсов установки начального

5 состояния содерясит D-триггер и интегратор, выход которого подключен к установочному R-входу D-триггера, выход которого подключен к входу - интегратора и является выходом

0 формирователя импульсов установки начального состояния вым , вторьи и третьим дами которого являются ветственно тактовый установочный S - вход

5

, первхо-соот- С - вход , и информационный D -вход Л -триггера.

Составитель Г.ЛерантовиЧ

Техред 3.Палий Корректор С.Шекмар

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации с М-последовательностью | 1987 |

|

SU1522420A1 |

| Система передачи и приема информации рекуррентными последовательностями | 1985 |

|

SU1338101A1 |

| Устройство для передачи и приема сигналов начальной синхронизации | 1987 |

|

SU1543559A1 |

| Устройство фазового пуска | 1984 |

|

SU1225035A1 |

| Система передачи дискретной информации | 1986 |

|

SU1406806A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНЫХ СРЕДСТВ | 1992 |

|

RU2054198C1 |

| Устройство для передачи сигналов начальной синхронизации | 1985 |

|

SU1338100A1 |

| Устройство для регистрации аналогового процесса | 1986 |

|

SU1429171A1 |

| Устройство для регистрации аналогового процесса | 1989 |

|

SU1774379A1 |

Изобретение может использоваться в системах связи с шумоподобными сигналами. Сокращается время вхождения в синхронизм при одновременном повьшении достоверности установления наличия синхронизма. Сигнал принимаемой М-последовательности (мл) через фильтр 1 проходит на детектор 10 уровня: и на блок 2 поэлементного приема. С этого блока символы МП записываются в регистр 3 сдвига (РС) непосредственно, а в PC 4 - через первый канал двухканального мультиплексора 16. При полном заполнении PC 3 и 4, сигнал лог. 1 с К-го разряда PC 4 устанавливает RS-триггер 5 в состояние 1. В результате на основе PC 4 при помощи элемента ИСКЛЮЧАЮЩЕЕ ИЛИ .1 1 и переключения двухканального мультиплексора 16 на второй канал образуется местный генератор М-пос(Л 00 41 QO

| Устройство синхронизации с -последовательностью | 1976 |

|

SU585619A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Авторское свидетельство СССР | |||

| Устройство синхронизации с М-последовательностью | 1981 |

|

SU1003371A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-03-15—Публикация

1984-10-08—Подача