чений блок 9 формирования кода сигнала, коммутатор 10, выходной БП М и блок 12 управления. Кадр телевизионного изображения эаписьшается во входной БП 1 и хранится в нем в течение времени сжатия телевизионного сигнала. Он разбивается на кодируемые блоки (КБ) размером га к п точек изображения. В КБ выбирают пороговую точку (ЛТ), например первую точку. При сжатии вначале последовательно считьшаются и сравниваг ются между собой значения ПТ кодируе1 .

Изобретение относится к технике цифрового телевидения и может быть использовано для сжатия отдельных кадров телевизионных изображений.

Цель изобретения - увеличение степени сжатия и повьшение скорости кодирования.

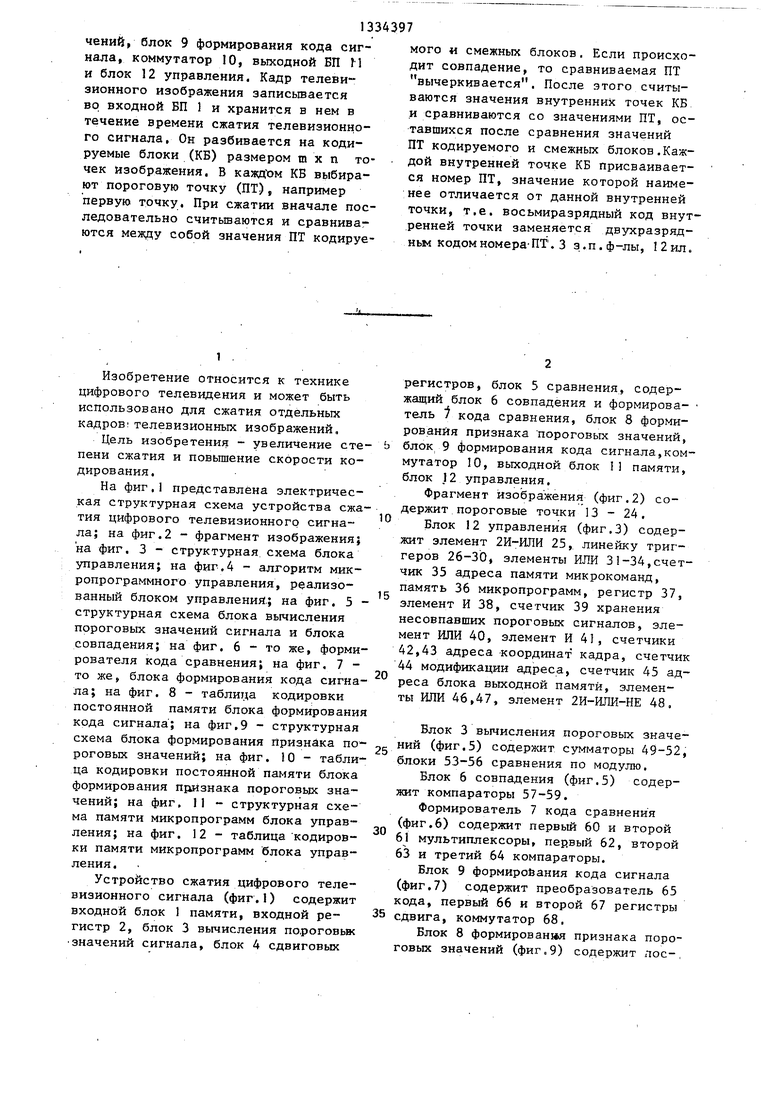

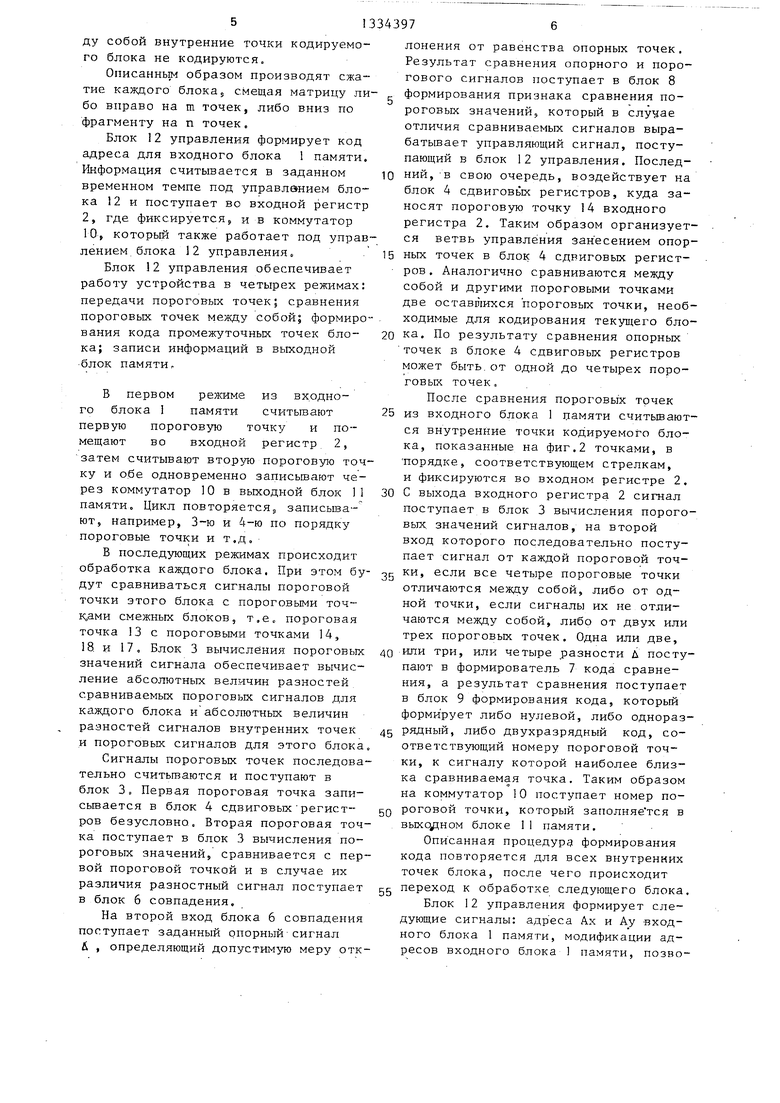

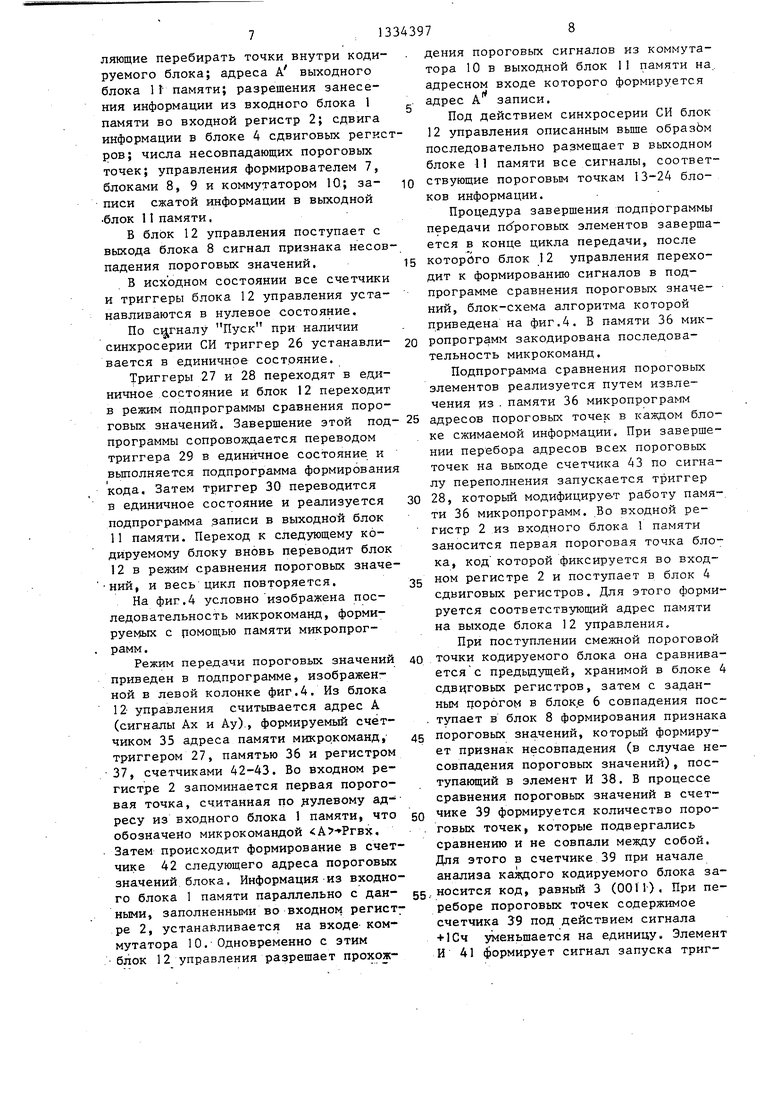

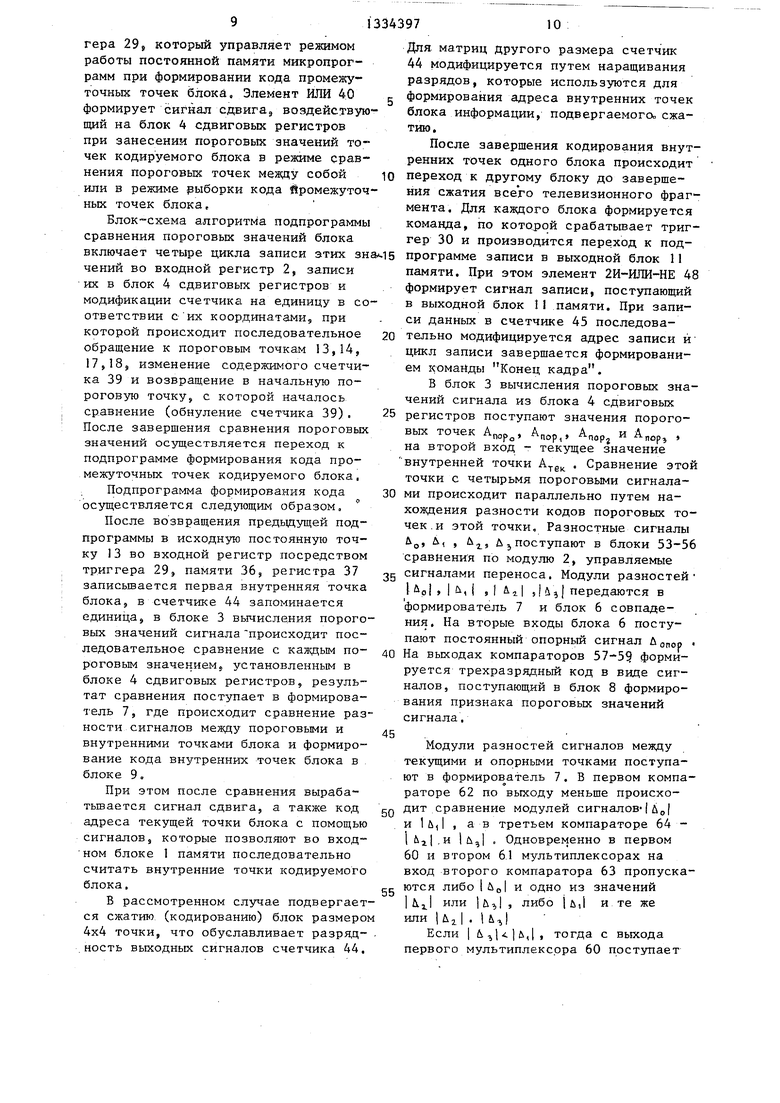

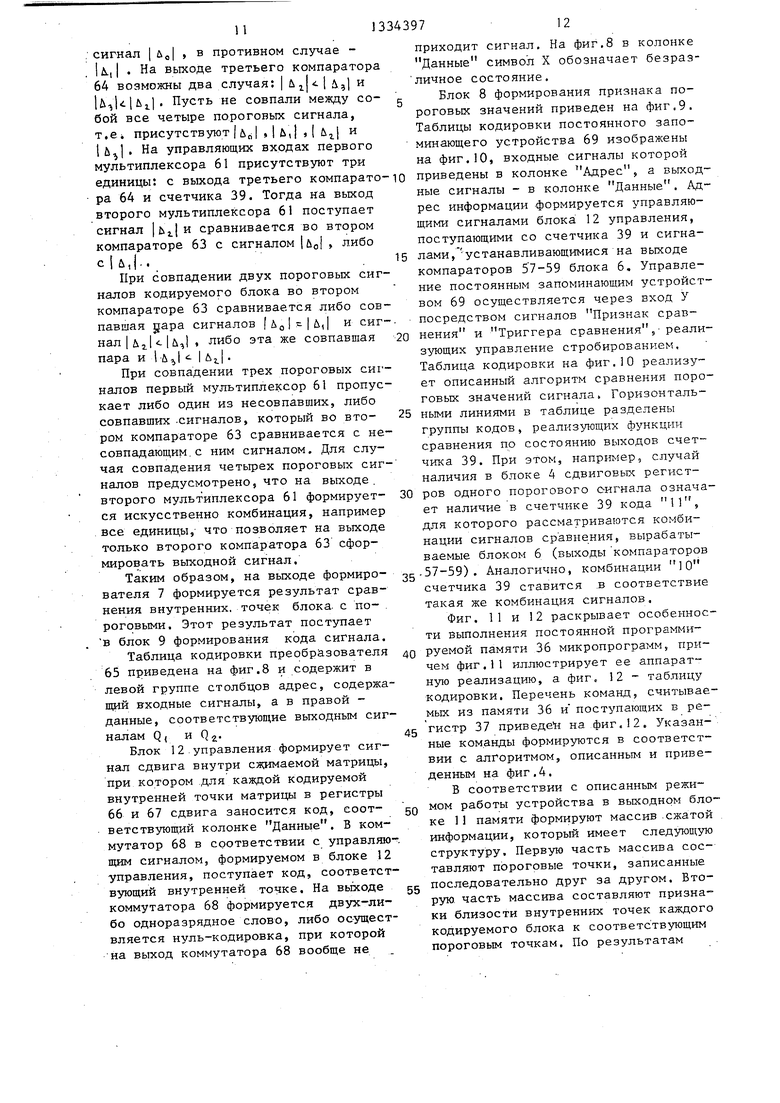

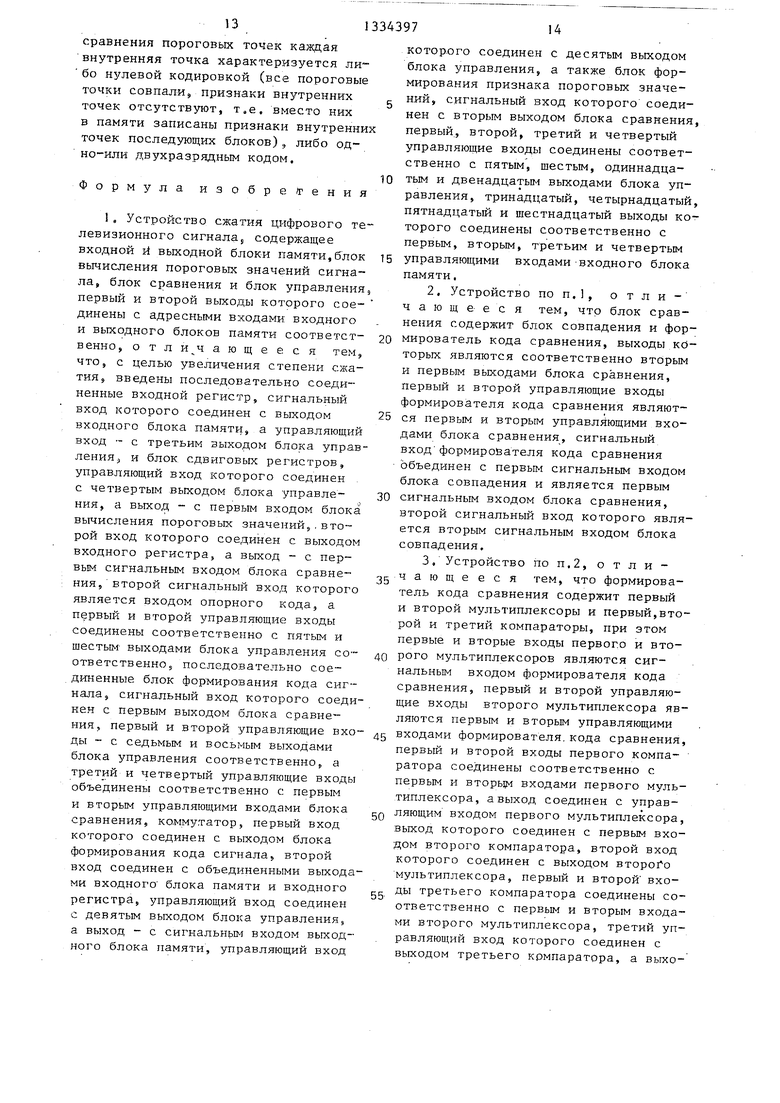

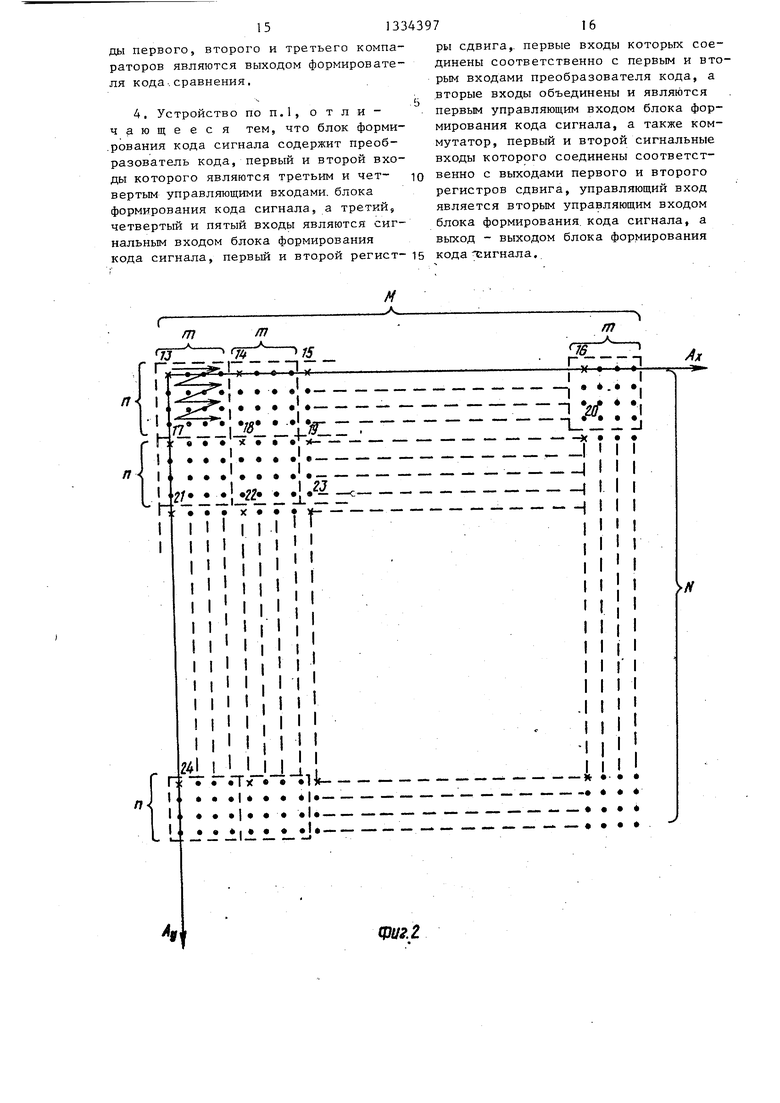

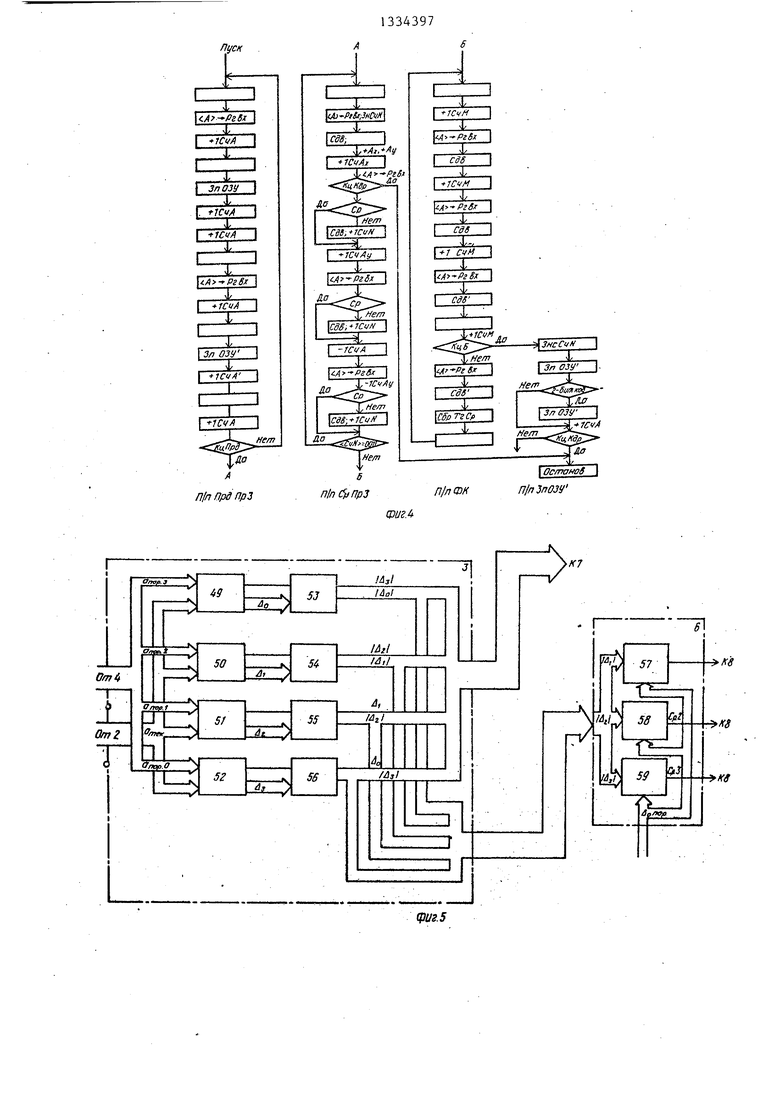

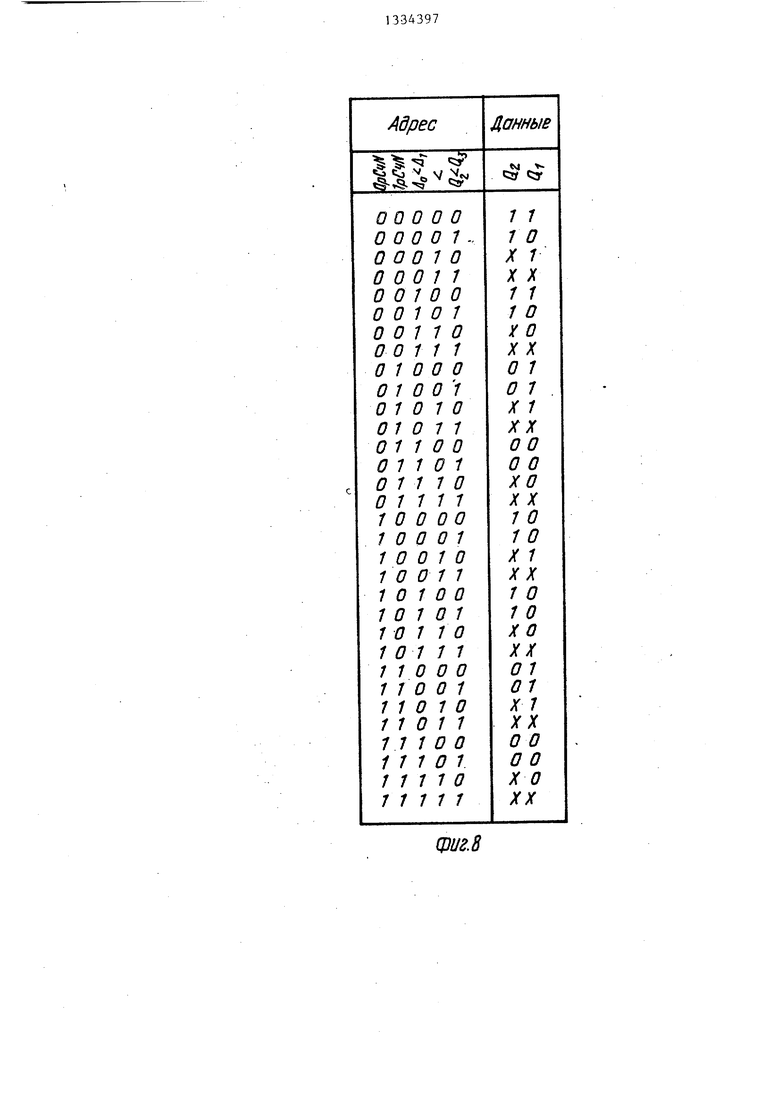

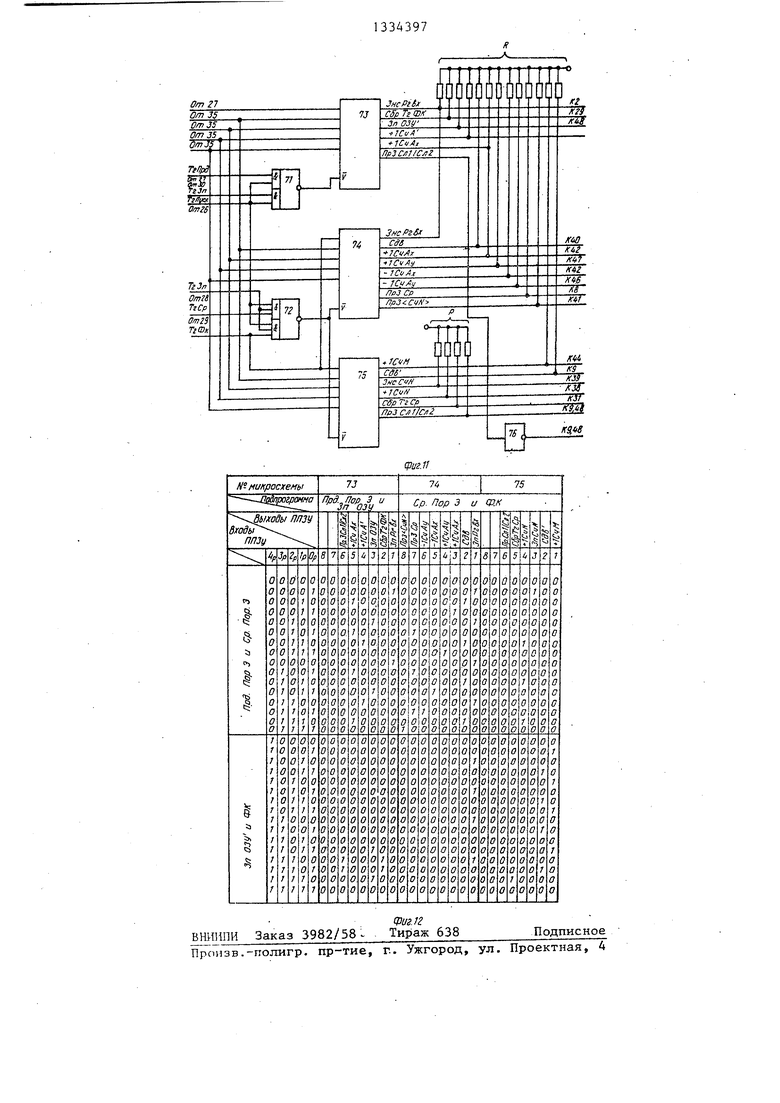

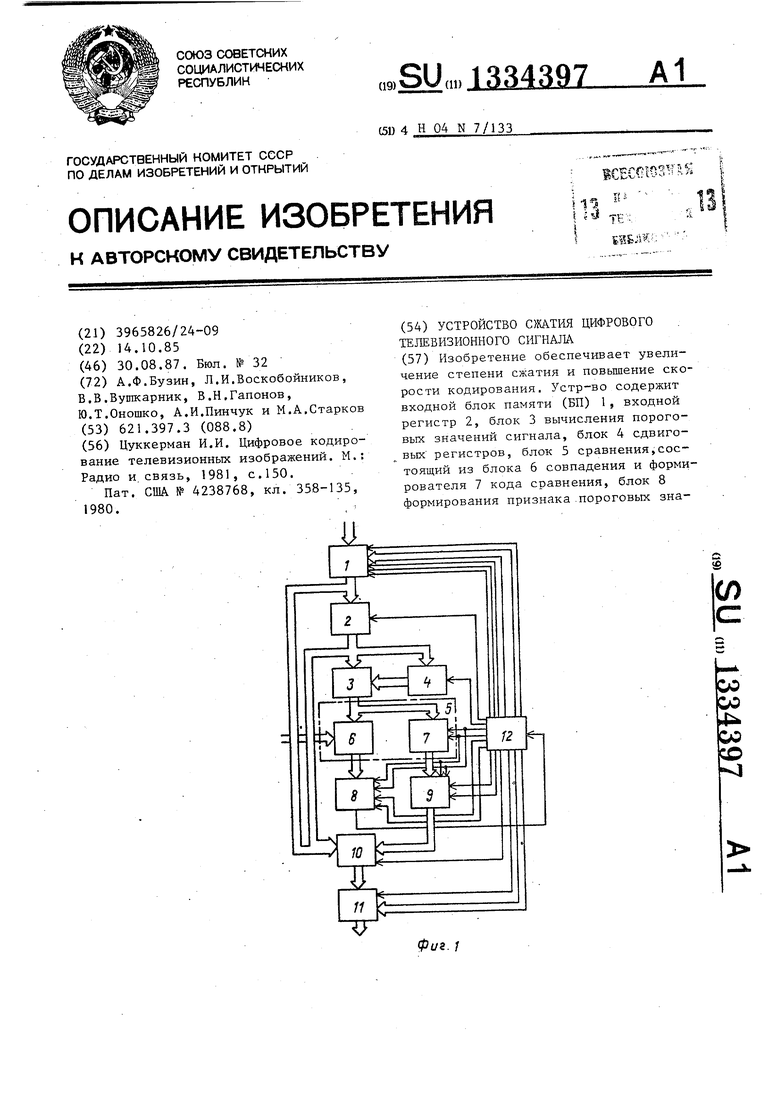

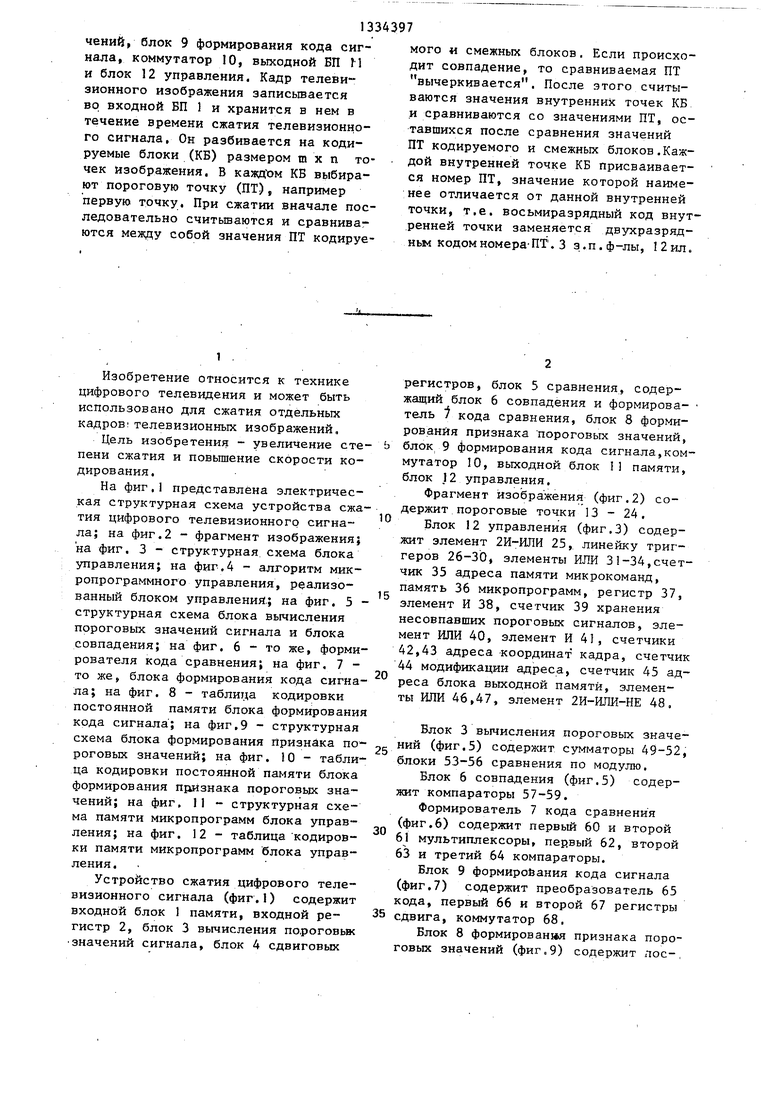

На фиг.1 представлена электрическая структурная схема устройства сжатия цифрового телевизионного сигнала; на фиг.2 - фрагмент изображения; на фиг. 3 - структурная схема блока управления; на фиг.4 - алгоритм микропрограммного управления, реализованный блоком управления.; на фиг. 5 - структурная схема блока вычисления пороговых значений сигнала и блока совпадения; на фиг. 6 - то же, формирователя кода сравнения; на фиг. 7 - то же, блока формирования кода сигнала; на фиг. 8 - таблица кодировки постоянной памяти блока формирования кода сигнала; на фиг.9 - структурная схема блока формирования признака пороговых значений; на фиг. О - таблица кодировки постоянной памяти блока формирования П1шзнака пороговых значений; на фиг. 11 - структурная схема памяти микропрограмм блока управления; на фиг. 12 - таблица кодировки памяти микропрограмм блока управления.

Устройство сжатия цифрового телевизионного сигнала (фиг.1) содержит входной блок 1 памяти, входной регистр 2, блок 3 вычисления пороговьж значений сигнала, блок 4 сдвиговых

мого и смежных блоков, Если происходит совпадение, то сравниваемая ПТ вычеркивается. После этого считываются значения внутренних точек КБ и сравниваются со значениями ПТ, оставшихся после сравнения значений ПТ кодируемого и смежных блоков.Каждой внутренней точке КБ присваивается номер ПТ, значение которой наименее отличается от данной внутренней точки, т.е. восьмиразрядный код внутренней точки заменяется двухразрядным кодом номера- ПТ .3 з. п. ф-лы, 1 2 ил.

регистров, блок 5 сравнения, содержащий блок 6 совпадения и формирова- тель / кода сравнения, блок 8 формирования признака пороговых значений, блок 9 формирования кода сигнала,коммутатор 10, выходной блок I памяти, блок 12 управления.

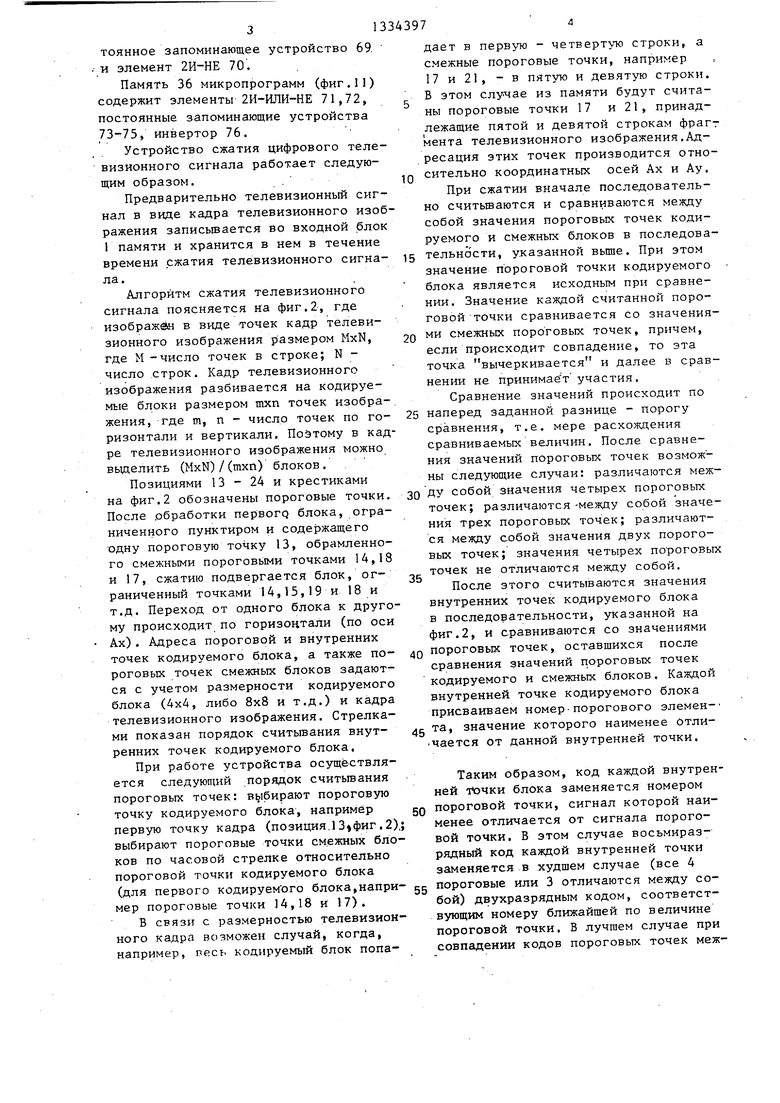

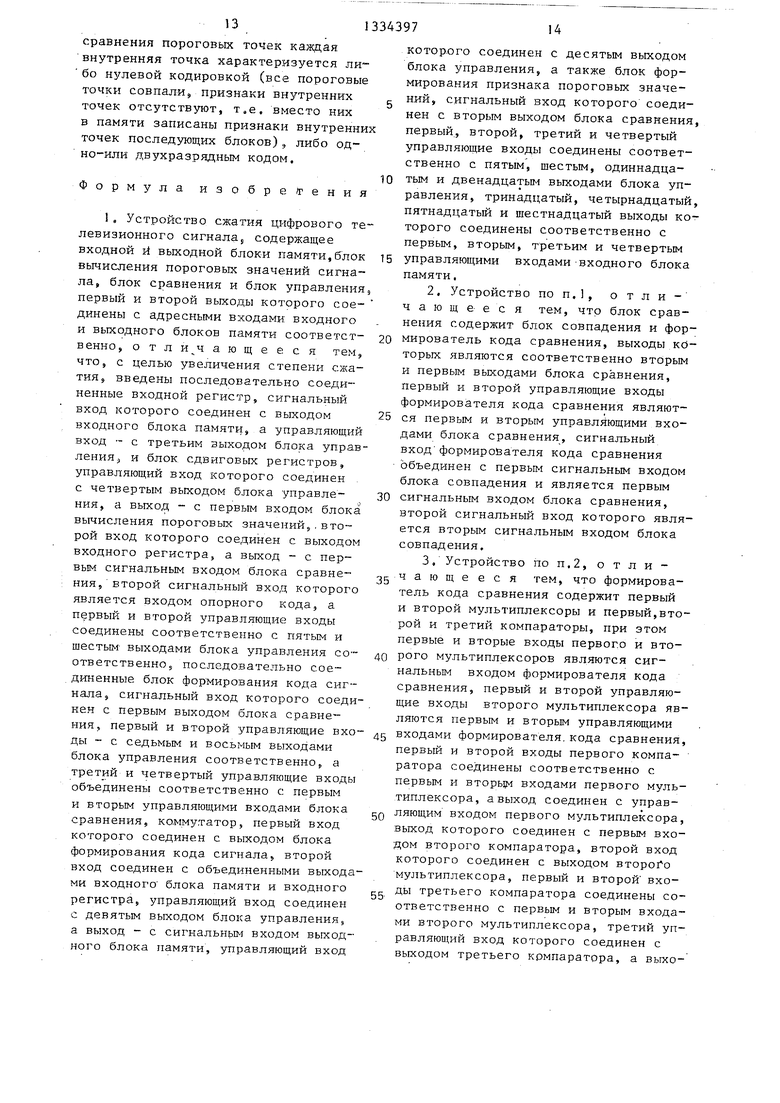

Фрагмент изображения (фиг.2) содержит пороговые точки 13 - 24.

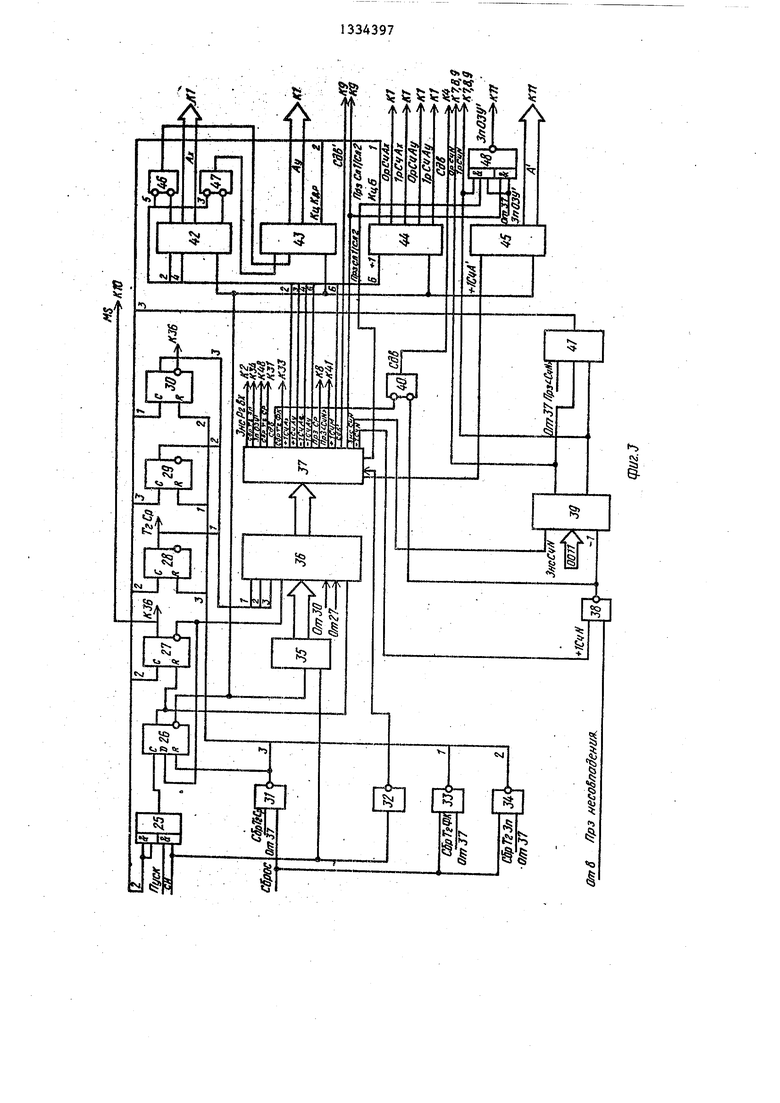

БЛОК 12 управления (фиг.З) содержит элемент 2И-ИЛИ 25, линейку триггеров 26-30, элементы ИЛИ 31-34,счетчик 35 адреса памяти микрокоманд, память 36 микропрограмм, регистр 37, элемент И 38, счетчик 39 хранения несовпавших пороговых сигналов, элемент ИЛИ 40, элемент И 41, счетчики 42,43 адреса координат кадра, счетчик 44 модификации адреса, счетчик 45 адреса блока выходной памяти, элементы ИЛИ 46,47, элемент 2И-ИЛИ-НЕ 48.

Блок 3 вычисления пороговых значе- с НИИ (фиг.З) содержит сумматоры 49-52, блоки 53-56 сравнения по модулю.

Блок 6 совпадения (фиг.5) содержит компараторы 57-59.

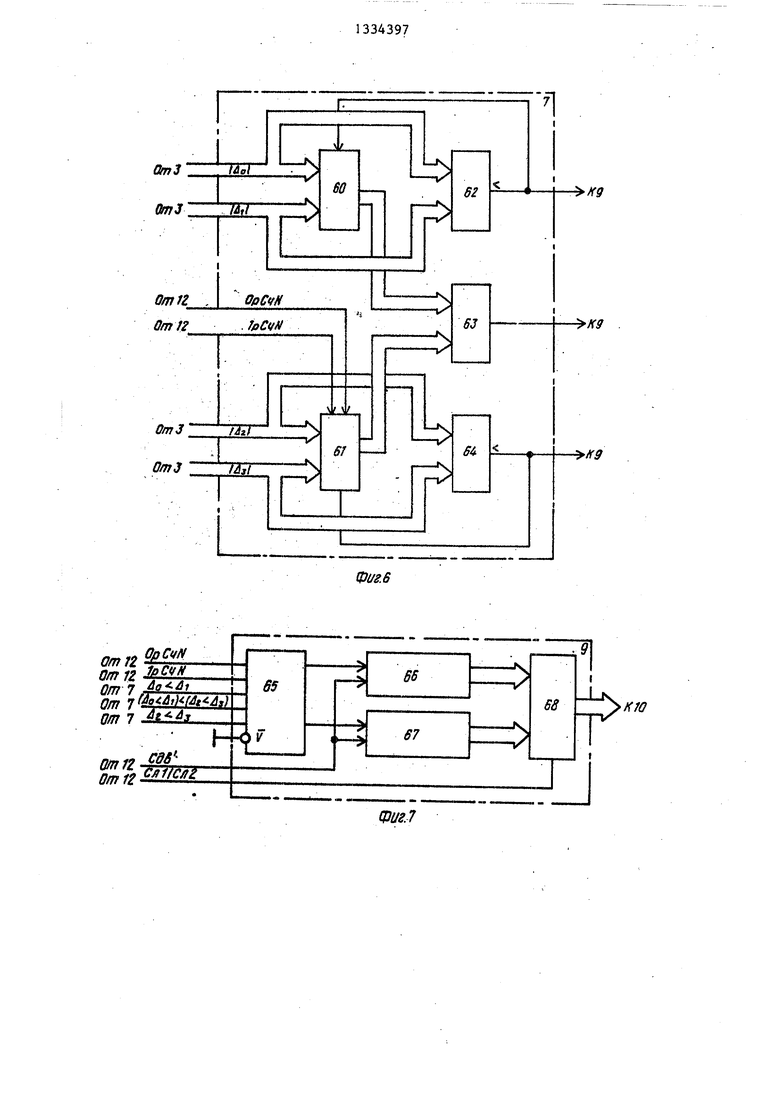

Формирователь 7 кода сравнения (фиг.6) содержит первый 60 и второй 61 мультиплексоры, первый 62, второй 63 и третий 64 компараторы.

Блок 9 формиройания кода сигнала (фиг.7) содержит преобразователь 65 кода, первый 66 и второй 67 регистры 5 сдвига, коммутатор 68.

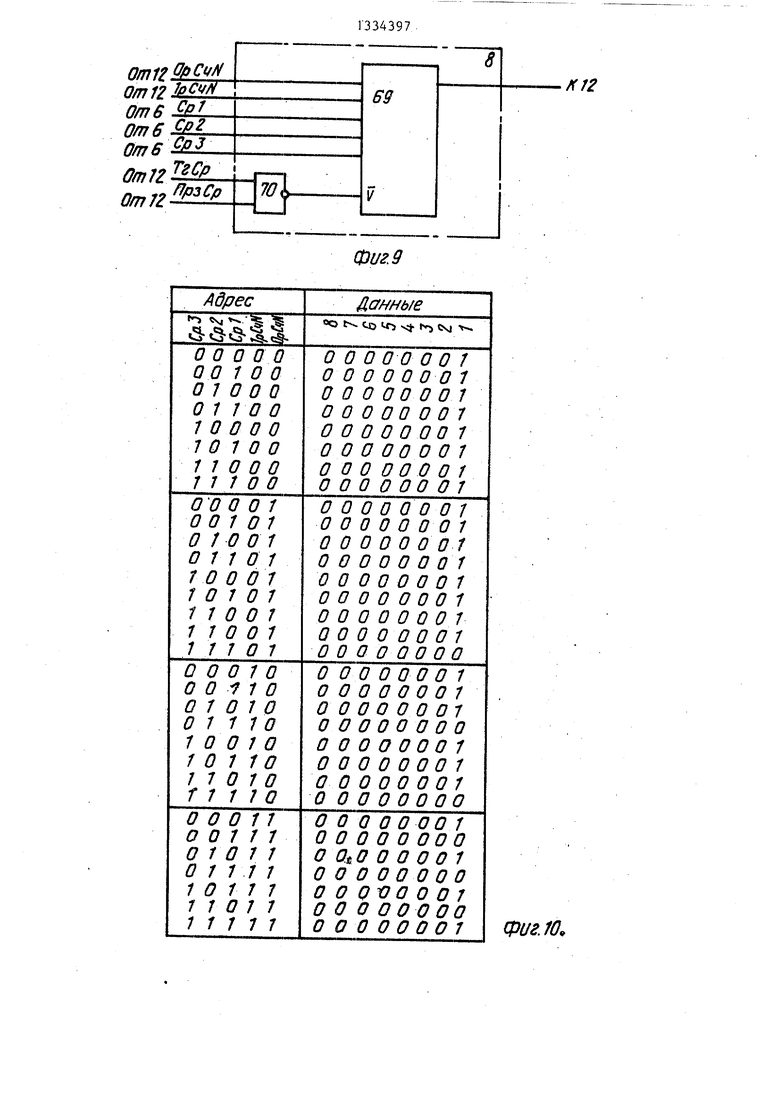

Блок 8 формирования признака пороговых значений (фиг,9) содержит лос-,

тоянное запоминающее устройство 69. и элемент 2И-НЕ 70.

Память 36 микропрограмм (фиг.11) одержит элементы 2И-ИЛИ-НЕ 71,72, остоянные запоминающие устройства 3-75, инвертор 76.

Устройство сжатия цифрового телевизионного сигнала работает следующим образом.

Предварительно телевизионный сигнал в виде кадра телевизионного изображения записывается во входной блок Г памяти и хранится в нем в течение времени сжатия телевизионного сигнала.

Алгоритм сжатия телевизионного сигнала поясняется на фиг.2, где изображен в виде точек кадр телевизионного изображения размером MxN, где М -число точек в строке; N - число строк. Кадр телевизионного изображения разбивается на кодируемые блоки размером mxn точек изображения, где т, п - число точек по го

ризонтали и вертикали. Поэтому в кадре телевизионного изображения можно выделить (MxN)/(mxn) блоков.

Позициями 13 - 24 и крестиками на фиг.2 обозначены пороговые точки. После обработки первогд блока, ограниченного пунктиром и содержащего одну пороговую точку 13, обрамленного смежными пороговыми точками 14,18 и 17, сжатию подвергается блок, ограниченный точками 14,15,19 и 18 и т.д. Переход от одного блока к другому происходит по горизонтали (по оси Ах). Адреса пороговой и внутренних точек кодируемого блока, а также пороговых точек смежных блоков задаются с учетом размерности кодируемого блока (4x4, либо 8x8 и т.д.) и кадра телевизионного изображения. Стрелками показан порядок считывания внутренних точек кодируемого блока.

При работе устройства осуществляется следующий порядок считьшания пороговых точек: выбирают пороговую точку кодируемого блока, например первую точку кадра (позиция.13$фиг .2), выбирают пороговые точки смежных блоков по часовой стрелке относительно пороговой точки кодируемого блока (для первого кодируем ого блока,напри- мер пороговые точки 14,18 и 17).

В связи с размерностью телевизионного кадра возможен случай, когда, например, весь кодируемый блок попа

0

5

дает в первую - четвертую строки, а смежные пороговые точки, например 17 и 21, - в пятую и девятую строки. Б этом случае из памяти будут считаны пороговые точки 17 и 21, принадлежащие пятой и девятой строкам фрагт мента телевизионного изображения.Адресация зтих точек производится относительно координатных осей Ах и Ау. При сжатии вначале последовательно считьшаются и сравниваются между собой значения пороговых точек кодируемого и смежных блоков в последова5 тельности, указанной вьш1е. При этом значение пороговой точки кодируемого блока является исходным при сравнении. Значение каждой считанной пороговой ТОЧКИ сравнивается со значения0 ми смежных пороговых точек, причем, если происходит совпадение, то эта точка вычеркивается и далее в сравнении не принимае т участия.

Сравнение значений происходит по

5 наперед заданной разнице - порогу сравнения, т.е. мере расхождения сравниваемых величин. После сравнения значений пороговых точек возможны следующие случаи: различаются меж0 ДУ собой значения четырех пороговых точек; различаются-между собой значения трех пороговых точек; различаются между собой значения двух пороговых точек; значения четырех пороговых точек не отличаются между собой.

После этого считываются значения внутренних точек кодируемого блока в последовательности, указанной на фиг.2, и сравниваются со значениями

п пороговых точек, оставщихся после сравнения значений цороговых точек кодируемого и смежных блоков. Каждой внутренней точке кодируемого блока присваиваем номер-порогового элемен- та, значение которого наименее Отли5

чается от данной внутренней точки.

Таким образом, код каждой внутренней блока заменяется номером пороговой точки, сигнал которой наименее отличается от сигнала пороговой точки. В этом случае восьмиразрядный код каждой внутренней точки заменяется в худщем случае (все 4 пороговые или 3 отличаются между собой) двухразрядным кодом, соответствующим номеру ближайщей по величине ороговой точки. В лучщем случае при совпадении кодов пороговых точек между собой внутренние точки кодируемого блока не кодируются.

Описаннь1м образом производят сжатие каждого блокаS смещая матрицу либо вправо на m точек, либо вниз по фрагменту на п точек.

Блок 12 управления формирует код адреса для входного блока 1 памяти. Информация считывается в заданном временном темпе под управлением блока 12 и поступает во входной регистр 2, где фиксируетсяJ ив коммутатор 10, который также работает под управлением, блока 12 управления.

Блок 12 управления обеспечивает работу устройства в четырех режимах: передачи пороговых точек; сравнения пороговых точек между собой; формирования кода промежуточных точек блока; записи информации в выходной блок памяти.

из вXодно- считьгаают

В первом релшме го блока 1 памяти первую пороговую точку и помещают во входной регистр 2, затем считывают вторую пороговую точку и о.бе одновременно записьшают через коммутатор 10 в выходной блок 11 памяти. Цикл повторяется записьшают, например, 3-ю и -1--ю по порядку пороговые точки и т.д.

В последующих режимах происходит обработка каждого блока. При этом будут сравниваться сигналы пороговой точки этого блока с пороговыми точ- ками смежных блоков, т.е. пороговая точка 13 с пороговыми точками 14, 18 и 17, Блок 3 вычисления пороговых значений сигнала обеспечивает вычисление абсолютных величин разностей сравниваемых пороговых сигналов для каждого блока и абсолютных величин разностей сигналов внутренних точек и пороговых сигналов для этого блока

Сигналы пороговых точек последовательно считываются и поступают в блок 3, Первая пороговая точка запи- сьшается в блок 4 сдвиговых регистров безусловно. Вторая пороговая точка поступает в блок 3 вычисления пороговых значений, сравнивается с первой пороговой точкой и в случае их различия разностный сигнал поступает в блок 6 совпадения.

На второй вход блока 6 совпадения поступает заданный опорный сигнал Л , определяющий допустимую меру отклонения от равенства опорных точек. Результат сравнения опорного и порогового сигналов поступает в блок 8 формирования признака сравнения пороговых значений, который в случае отличия сравниваемых сигналов вырабатывает управляющий сигнал, поступающий в блок 12 управления. Послед- НИИ, В свою очередь, воздействует на блок 4 сдвиговьк регистров, куда заносят пороговую точку 14 входного регистра 2. Таким образом организуется ветвь управления зан есением опор- 5 ньк точек в блок 4 сдвиговьк регистров . Аналогично сравниваются между собой и другими пороговыми точками две остав111ихся пороговых точки, необходимые для кодирования текущего бло- 0 ка. По результату сравнения опорных точек в блоке 4 сдвиговых регистров может быть, от одной до четырех пороговых точек.

После сравнения пороговьгх точек 5 из входного блока 1 памяти считьюают- ся внутренние точки кодируемого блока, показанные на фиг.2 точками, в порядке, соответствующем стрелкам, и фиксируются во входном регистре 2. 0 С выхода входного регистра 2 сигнал поступает в блок 3 вычисления пороговых, значений сигналов, на второй вход которого последовательно поступает сигнал от каждой пороговой точки, если все четыре пороговые точки отличаются между собой, либо от одной точки, если сигналы их не отличаются между собой, либо от двух или трех пороговых точек. Одна или две, или три, или четыре разности Д поступают в формирователь 7 кода сравнения, а результат сравнения поступает в блок 9 формирования кода, который формирует либо нулевой, либо однораз- 5 рядный, либо двухразрядный код, соответствующий номеру пороговой точки, к сигналу которой наиболее близка сравниваемая точка. Таким образом на коммутатор 10 поступает номер по- Q роговой точки, который заполняе тся в выхоудном блоке 1 1 памяти.

Описанная процедура формирования кода повторяется для всех внутренних точек блока, после чего происходит gc переход к обработке следующего блока. Блок 12 управления формирует следующие сигналы: адр еса Ах и Ау входного блока 1 памяти, модификации адресов входного блока 1 памяти, позво5

0

ляющие перебирать точки внутри кодируемого блока; адреса А выходного блока И памяти; разрешения занесения информации из входного блока 1 памяти во входной регистр 2; сдвига информации в блоке 4 сдвиговых регисров; числа несовпадающих пороговых точек; управления формирователем 7, блоками 8, 9 и коммутатором 10; за- писи сжатой информации в выходной блок 11 памяти,

В блок 12 управления поступает с вькода блока 8 сигнал признака несовпадения пороговых значений.

В исходном состоянии все счетчики и триггеры блока 12 управления устанавливаются в нулевое состояние.

По С1 гналу Пуск при наличии синхросерии СИ триггер 26 устанавли- вается в единичное состояние.

Триггеры 27 и 28 переходят в единичное состояние и блок 12 переходит в режим подпрограммы сравнения пороговых значений. Завершение этой под программы сопровождается переводом триггера 29 в единичное состояние и выполняется подпрограмма формировани кода. Затем триггер 30 переводится в единичное состояние и реализуется подпрограмма записи в выходной блок

11памяти. Переход к следующему кодируемому блоку вновь переводит блок

12в режим сравнения пороговых значе ний, и весь цикл повторяется.

На фиг.4 условно изображена последовательность микрокоманд, формируемых с ромощью памяти микропрограмм.

Режим передачи пороговых значений приведен в подпрограмме, изображенной в левой колонке фиг.4. Из блока 12 управления считьшается адрес А (сигналы Ах и Ау)., формируемый счётчиком 35 адреса памяти микрокоманд,- триггером 27, памятью 36 и регистром 37, счетчиками 42-43. Во входном регистре 2 запоминается первая пороговая точка, считанная по рулевому адресу из входного блока 1 памяти, что обозначено микрокомандой . Затем происходит формирование в счетчике 42 следующего адреса пороговых значений блока, Информация из входного блока 1 памяти параллельно с дан- ными, заполненными во входном регистр ре 2, устанавливается на входе- коммутатора 10. Одновременно с этим блок 12 управления разрешает прохождения пороговых сигналов из коммутатора 10 в выходной блок И памяти на адресном входе которого формируется адрес А записи.

Под действием синхросерии СИ блок 12 управления описанным вьше образбм последовательно размещает в выходном блоке 11 памяти все сигналы, соответствующие пороговым точкам 13-24 блоков информации.

Процедура завершения подпрограммы передачи псэ роговых элементов завершается в конце цикла передачи, после которого блок I2 управления переходит к формированию сигналов в подпрограмме сравнения пороговых значений, блок-схема алгоритма которой приведена на фиг.4. В памяти 36 микропрограмм закодирована последовательность микрокоманд.

Подпрограмма сравнения пороговых элементов реализуется путем извлечения из . памяти 36 микропрограмм адресов пороговых точек в каждом блоке сжимаемой информации. При завершении перебора адресов всех пороговых точек на выходе счетчика 43 по сигналу переполнения запускается триггер 28, который модифицирует работу памяти 36 микропрограмм. Во входной регистр 2 из входного блока 1 памяти заносится первая пороговая точка блока, код которой фиксируется во входном регистре 2 и поступает в блок 4 сдвиговых регистров. Для этого формируется соответствующий адрес памяти на выходе блока 12 управления.

При поступлении смежной пороговой точки кодируемого блока она сравнивается с предьщущей, хранимой в блоке 4 сдвиговых регистров, затем с заданным цорогом в блоке 6 совпадения поступает в блок 8 формирования признака пороговых зна.чений, который формирует признак несовпадения (в случае несовпадения пороговых значений), поступающий в элемент И 38. В процессе сравнения пороговых значений в счетчике 39 формируется количество пороговых точек, которые подвергались сравнению и не совпали между собой. Для этого в счетчике 39 при начале анализа каждого кодируемого блока заносится код, равный 3 (ООП), При переборе пороговых точек содержимое счетчика 39 под действием сигнала +1Сч уменьшается на единицу. Элемент И 41 формирует сигнал запуска триггера 29, который управляет режимом работы постоянной памяти микропрограмм при формировании кода промежуточных точек блоки. Элемент ИЛИ 40

формирует сигнал сдвига, воздействующий на блок 4 сдвиговых регистров при занесении пороговых значений точек кодируемого блока в режиме сравнения пороговых точек мевду собой или в режиме рыборки кода Промежуточных точек блока,

Блок-схема алгоритма подпрограммы сравнения пороговых значений блока включает четыре цикла записи этих зн чений во входной регистр 2, записи их в блок 4 сдвиговых регистров и модификации счетчика на единицу в соответствии с их координатами, при которой происходит последовательное обращение к пороговым точкам 13,14, 17,18, изменение содержимого счетчика 39 и возвращение в начальную пороговую точку, с которой началось сравнение (обнуление счетчика 39). После завершения сравнения пороговых значений осуществляется переход к подпрограмме формирования кода промежуточных точек кодируемого блока, . Подпрограмма формирования кода осуществляется следующим образом.

После возвращения предыдущей подпрограммы в исходную постоянную точку 13 во входной регистр посредством триггера 29, памяти 36, регистра 37 записьшается первая внутренняя точка блока, в счетчике 44 запоминается единица, в блоке 3 вычисления пороговых значений сигнала происходит последовательное сравнение с каждым по- роговым значением, установленным в блоке 4 сдвиговых регистров, результат сравнения поступает в формирователь 7, где происходит сравнение разности сигналов между пороговыми и внутренними точками блока и формирование кода внутренних точек блока в блоке 9.

При этом после сравнения выраба- тьшается сигнал сдвига, а также код адреса текущей точки блока с помощью сигналов, которые позволяют во вход- ном блоке 1 памяти последовательно считать внутренние точки кодируемого блока,

В рассмотренном случае подвергается сжатию (кодированию) блок размеро 4x4 точки, что обуславливает разряд- .ность выходных сигналов счетчика 44,

Для матриц другого размера счетчик 44 модифицируется путем наращивания разрядов, которые используются для формирования адреса внутренних точек блока информации, подвергаемого сжатию.

После завершения кодирования внутренних точек одного блока происходит переход к другому блоку до завершения сжатия всего телевизионного фрагмента. Для каждого блока формируется команда, по срабатывает триггер 30 и производится переход к подпрограмме записи в выходной блок 11 памяти. При этом элемент 2И-ИЛИ-НЕ 48 формирует сигнал записи, поступающий в выходной блок 11 памяти. При записи данных в счетчике 45 последовательно модифицируется адрес записи и цикл записи завершается формированием команды Конеп; кадра.

В блок 3 вычисления пороговых значений сигнала из блока 4 сдвиговых регистров поступают значения пороговых точек АП,Р, А„ор,, А„,р и А„ор, , на второй вход - текущее значение внутренней точки , , Сравнение этой точки с четырьмя пороговыми сигналами происходит параллельно путем нахождения разности кодов пороговых точек, и этой точки. Разностные сигналы &о, U., , Л 2 5 д,, поступают в блоки 53-56 сравнения по модулю 2, управляемые сигналами переноса, Модули разностей I up , I U, I , &i| Ji, передаются в формирователь 7 и блок 6 совпадения. На вторые входы блока 6 поступают постоянный опорный сигнал Допор На выходах компараторов 57-59 формируется трехразрядный код в виде сигналов, поступающий в блок 8 формирования признака пороговых значений сигнала.

Модули разностей сигналов между текущими и опорными точками поступают в формирователь 7. В первом компараторе 62 по выходу меньше происходит сравнение модулей сигналов-1 йо( и 1й,| , а в третьем компараторе 64 - 1 г1-И Одновременно в первом 60 и втором 61 мультиплексорах на вход второго компаратора 63 пропускаются либо I До1 и одно из значений I или 1й,,|, либо iu,| и те же или I Д i I , U,, I

Если I Д,,,1, тогда с выхода первого мультиплексора 60 поступает

, в противном случае 133439712

приходит сигнал. На фиг,8 в колонке Данные символ X обозначает безразличное состояние.

Блок 8 формирования признака по;сигнал |

. |, I . На выходе третьего компаратора 64 возможны два случая: | и U Ulbil- Пусть не совпали между со- g бой все четыре пороговых сигнала, роговых значений приведен на фиг.9. T.Ci присутствуют I ,|л, ,| & I и Таблицы кодировки постоянного запо- 1U I. На управляющих входах первого минающего устройства 69 изображены мультиплексора 61 присутствуют три на фиг.10, входные сигналы которой единицы: с выхода третьего компарато-ю приведены в колонке Адрес, а выход ра 64 и счетчика 39. Тогда на выход второго мультиплексора 61 поступает сигнал IbiJH сравнивается во втором компараторе 63 с сигналом |Ьо1 либо cU,|..

При совпадении двух пороговых сигналов кодируемого блока во втором компараторе 63 сравнивается либо совные сигналы - в колонке Данные. Адрес информации -формируется управляющими сигналами блока 12 управления, поступающими со счетчика 39 и сигна- 15 лами, устанавливающимися на выходе компараторов 57-59 блока 6, Управление постоянным запоминающим устройством 69 осуществляется через вход У

павшая gapa сигналов |До1)|Л,| и сиг-. посредством сигналов Признак срав- нал I t lu, , либо эта же совпавшая 20 нения и Триггера сравнения , реали- пара и .l зующих управление стробированием.

При совпадении трех пороговых си:- Таблица кодировки на фиг.10 реализу- налов первый мультиплексор 61 пропус- ет описанный алгоритм сравнения порскает либо один из несовпавших, либо говых значений сигнала. Горизонталь- совпавших .сигналов, который во вто- 25 ными линиями в таблице разделены ром компараторе 63 сравнивается с не- группы кодов, реализующих функции совпадающим.с ним сигналом. Для слу- сравнения по состоянию выходов счет- чая совпадения четырех пороговых сиг- чика 39. При этом, например, случай налов предусмотрено, что на выходе. наличия в блоке 4 сдвиговых регист- второго мультиплексора 61 формирует- 30 ров одного порогового сигнала означает наличие в счетчике 39 кода 11, для которого рассматриваются комбинации сигналов сравнения, вырабатываемые блоком 6 (выходы компараторов Таким образом, на выходе формиро- gg-57-59). Аналогично, комбинации 10 вателя 7 формируется результат срав- счетчика 39 ставится в соответствие нения внутренних, точек блока, с по- . такая же комбинация сигналов, роговыми. Этот результат поступает Фиг. 11 и 12 раскрывает особеннос- в блок 9 формирования кода сигнала. ти выполнения постоянной программи- Таблица кодировки преобразователя 40 РУемой памяти 36 микропрограмм, при65приведена на фиг.8 и содержит в чем фиг.11 иллюстрирует ее аппарат- левой группе столбцов адрес, содержа- ную реализацию, а фиг. 12 - таблицу щий входные сигналы, а в правой - кодировки. Перечень команд, считывае- данные, соответствующие выходным сиг- мых из памяти 36 и поступающих в ре- налам Q, и Q.45 37 приведе-н на фиг, 12. УказанБлок 12 управления формирует сигнал сдвига внутри сжимаемой матрицы, при котором для каждой кодируемой внутренней точки матрицы в регистры

66и 67 сдвига заносится код, соот- gQ ветствующий колонке Данные. В комся искусственно комбинация, например все единицы, что позволяет на выходе только второго компаратора 63 сформировать выходной сигнал.

ные ком.анды формируются в соответствии с алгоритмом, описанным и приведенным на фиг.4,

В соответствии с описанным режимом работы устройства в выходном блоке П памяти формируют массив .сжатой информации, который имеет следующую структуру. Первую часть массива составляют пороговые точки, записанные последовательно друг за другом. Вторую часть массива составляют признаки близости внутренних точек каждого кодируемого блока к соответствующим пороговым точкам. По результатам

мутатор 68 в соответствии с управляю-, щим сигналом, формируемом в блоке 12 управления, поступает код, соответствующий внутренней точке. На вькоде коммутатора 68 формируется двух-ли- бо одноразрядное слово, либо осуществляется нуль-кодировка, при которой на выход коммутатора 68 вообще не

9712

приходит сигнал. На фиг,8 в колонке Данные символ X обозначает безразличное состояние.

Блок 8 формирования признака пороговых значений приведен на фиг.9. Таблицы кодировки постоянного запо- минающего устройства 69 изображены на фиг.10, входные сигналы которой приведены в колонке Адрес, а выходные сигналы - в колонке Данные. Адрес информации -формируется управляющими сигналами блока 12 управления, поступающими со счетчика 39 и сигна- лами, устанавливающимися на выходе компараторов 57-59 блока 6, Управление постоянным запоминающим устройстные ком.анды формируются в соответствии с алгоритмом, описанным и приведенным на фиг.4,

В соответствии с описанным режимом работы устройства в выходном блоке П памяти формируют массив .сжатой информации, который имеет следующую структуру. Первую часть массива составляют пороговые точки, записанные последовательно друг за другом. Вторую часть массива составляют признаки близости внутренних точек каждого кодируемого блока к соответствующим пороговым точкам. По результатам

сравнения пороговых точек каждая внутренняя точка характеризуется либо нулевой кодировкой (все пороговые точки совпали9 признаки внутренних точек отсутствуют, т.е. вместо них в памяти записаны признаки внутренни точек последующих блоков) ,, либо од- но-или двухразрядным кодом.

Формула изобретения

, Устройство сжатия цифрового телевизионного сигнала, содержащее входной и выходной блоки памяти,блок вычисления пороговых значений сигнала, блок сравнения и блок управления первый и второй выходы которого соединены с адресными входами входного и выходного блоков памяти соответственно, о т л а ю щ е е с я тем, что, с целью увеличения степени сжатия введены последовательно соединенные входной регистр, сигнальный вход которого соединен с выходом входного блока памяти, а управляющий вход - с третьим зь ходом блока управ лениЯз и блок сдвиговых регистров, управляющий вход которого соединен . с четвертым выходом блока управления, а выход - с первым входом блока вычисления пороговых значений,.второй вход которого соединен с выходом входного регистра, а выход - с первым сигнальным входом блока сравнения, второй сигнальный вход которого является входом опорного кода, а первый и второй управляющие входы соединены соответственно с пятым и шестым выходами блока управления соответственно, последовательно сое- диненные блок формирования кода сигнала, сигнальный вход которого соединен с первым выходом блока сравнения, первый и второй управляющие входы - с седьмым и восьмым выходами блока управления соответственно а третий и четвертый управляющие входы объединены соответственно с первым и вторым управляющими входами блока сравнения, коммутатор, первый вход которого соединен с выходом блока формирования кода сигнала,, второй вход соединен с объединенными выходами ВХОДНОГО блока памяти и входного регистра, управляющий вход соединен с девятым выходом блока управления, а выход - с сигнальньгм входом выходного блока памяти, управляющий вход

которого соединен с десятым выходом блока управления, а также блок формирования признака пороговых значеНИИ, сигнальный вход которого соединен с вторым выходом блока сравнения, первый, второй, третий и четвертый управляющие входы соединены соответственно с пятым, шестым, одиннадца- тым и двенадцатым выходами блока управления, тринадцатый, четырнадцатый, пятнадцатый и шестнадцатый выходы которого соединены соответственно с первым, вторым, третьим и четвертым

управляющими входами-входного блока памяти,

2.Устройство по п.1, о т л и - чающееся тем, что блок сравнения содержит блок совпадения и формирователь кода сравнения, выходы которых являются соответственно вторым и первым выходами блока сравнения. Первый и второй управляющие входы формирователя кода сравнения являются первым и вторым управляющими входами блока сравнения, сигнальный вход формирователя кода сравнения объединен с первым сигнальным входом блока совпадения и является первым

сигнальным входом блока сравнения, второй сигнальный вход которого является вторым сигнальным входом блока совпадения.

3,Устройство по п.2, о т л и - чающе е с я тем, что формирователь кода сравнения содержит первый

и второй мультиплексоры и первый,второй и третий компараторы, при этом первые и вторые входы первого и второго мультиплексоров являются сигнальным входом формирователя кода сравнения, первый и второй управляющие входы второго мультиплексора являются первым и вторым управляющими

входами формирователя, кода сравнения, первый и второй входы первого компаратора соединены соответственно с первым и вторь5м входами первого мультиплексора, а выход соединен с управляющим входом первого мультиплексора, выход которого соединен с первым входом второго компаратора, второй вход которого соединен с выходом второго мультиплексора, первый и второй входы третьего компаратора соединены соответственно с первым и вторым входами второго мультиплексора, третий управляющий вход которого соединен с выходом третьего крмпаратора, а выходы первого, второго и третьего компараторов являются выходом формирователя кода., сравнения.

4, Устройство по п.1, о т л и чающееся тем, что блок форми- .рования кода сигнала содержит преобразователь кода, первый и второй входы которого являются третьим и чет- вертым управляющими входами, блока формирования кода сигнала, а третий, четвертый и пятый входы являются сигнальным входом блока формирования

кода сигнала, первый и второй регист- 15 кода сигнала.

/77

/П

ры сдвига,- первые входы которых соединены соответственно с первым и вторым входами преобразователя кода, а вторые входы объединены и являются первым управляющим входом блока формирования кода сигнала, а также коммутатор, первый и второй сигнальные входы которого соединены соответственно с выходами первого и второго регистров сдвига, управляющий вход является вторым управляющим входом блока формирования, кода сигнала, а выход - выходом блока формирования

ГЛ

Фиг.1

Г

ОтЗ

jooL

0

Дту JW

J ggfy/y

.fpCvN

ААГГ

i

-N

S

-N

-N

J

-Ж9

Lb

54

rV

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1285532A1 |

| Устройство памяти на кадр цифрового теливизионного изображения | 1988 |

|

SU1600002A1 |

| УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ ИЗОБРАЖЕНИЙ И ИЗМЕРЕНИЯ РАЗМЕРОВ ОБЪЕКТОВ | 1998 |

|

RU2163395C2 |

| Устройство интерполирования сигналов телевизионного изображения | 1989 |

|

SU1690213A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2051416C1 |

| Телевизионный имитатор | 1981 |

|

SU965020A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СПЛОШНЫХ ОБРАЗОВ | 1991 |

|

RU2042204C1 |

| Телевизионный пеленгатор | 1989 |

|

SU1670805A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

Изобретение обеспечивает увеличение степени сжатия и повьшение скорости кодирования. Устр-во содержит входной блок памяти (БП) 1, входной регистр 2, блок 3 вычисления пороговых значений сигнала, блок 4 сдвиго- вых регистров, блок 5 сравнения,состоящий из блока 6 совпадения и формирователя 7 кода сравнения, блок 8 формирования признака .пороговых знаИ и (Л i со 00 4 со :о vl фиг. /

-,, фЛ

От 12 ..

Й77 Гг . 1/77 7

0m , от 7 .ЖЕЖИЩ

-йб ,.

Д7У/г д

кю

Фиг.7

фиг.8

Фиг. 9

фиг.Ю

| Цуккерман И.И | |||

| Цифровое кодирование телевизионных изображений | |||

| М.: Радио и, связь, 1981, с.150 | |||

| Пат | |||

| США № 4238768, кл | |||

| Зажим для канатной тяги | 1919 |

|

SU358A1 |

Авторы

Даты

1987-08-30—Публикация

1985-10-14—Подача