Изобретение относится к автоматике, а именно к устройствам преобразования информации, и может быть использовано в преобразователях пере- мещений в код.

Цель изобретения - расширение области применения шифратора путем обеспечения его реверсивной работы.

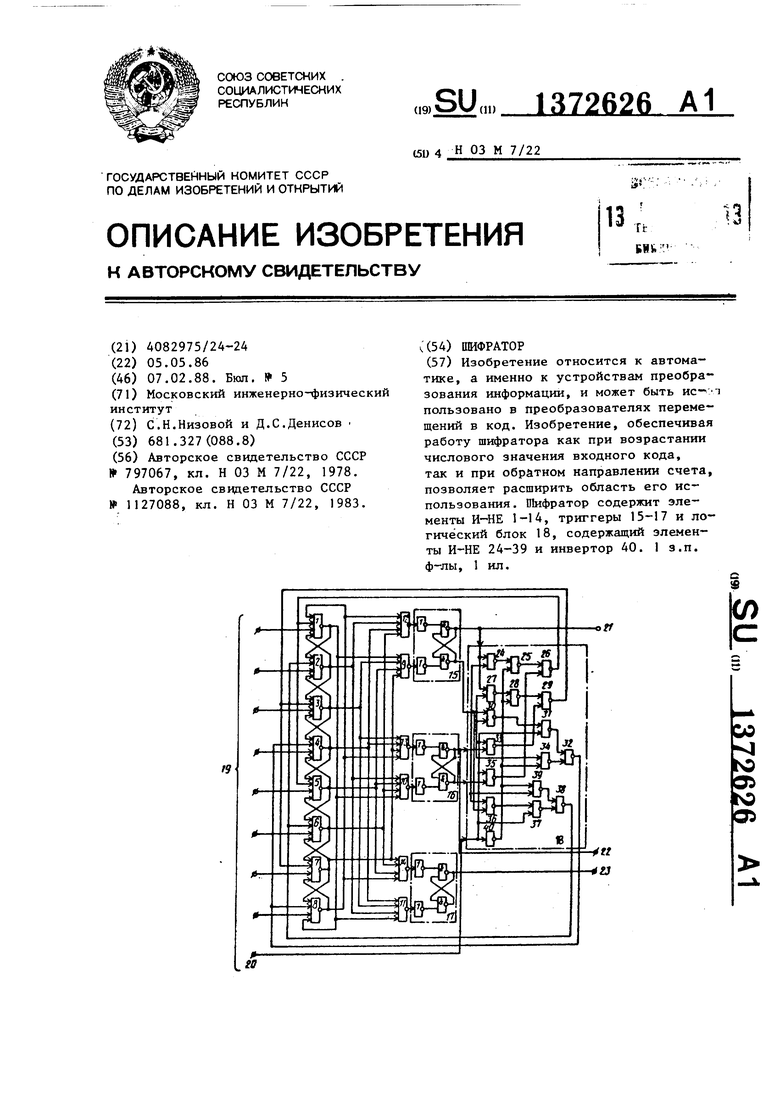

На чертеже представлена структур- ная схема шифратора.

Шифратор содерткит элементы И-НЕ 1 14, первый 15, второй 16, третий 17 триггеры, вьтолненные на элементах И-НЕ и инверторах, логический блок 18, информационные 19 и управляющий 20 входы шифратора и первый 21, второй 22 и третий 23 выходы шифратора.

Логический блок 18 содержит первый - шестнадцатый элементы И-НЕ 24- 39 и инвертор 40.

Шифратор работает следующим образом.

Пусть на управляющем входе 20 реверса шифратора присутствует уровень логического О, а на первый вход элемента И-НЕ 1 поступает потенциал логической 1, на остальных входах шифратора - логический О. На выходе элемента И-НЕ 1 формирует- ся сигнал логического О, а на выходах элементов И-НЕ 2-8 - сигнал логической 1. Триггеры 15-17 устанавливаются в нулевое состояние.

При возникновении импульсных по- мех, приводящих к пропаданию входного сигнала на первом входе элемента И-НЕ 1, на выходах элементов И-НЕ 9-14 устанавливается нулевой сигнал, однако, на выходах 21-23 шифратора сохраняется информация, записанная в триггерах 15-17.

Входные сигналы шифратора поступают с перекрытием при переходе между соседними положениями. Поэтому при поступлении уровня логической 1 на второй вход шифратора на выходе элемента И-НЕ 2 сохранится уровень логической 1, так как на второй вход этого элемента поступает уровен логического О с выхода элемента И-НЕ 1. При перепаде потенциала на первом входе шифратора до уровня логического О на выходе элемента IИ-НЕ 1 возникает уровень логической 1, который деблокирует по второму входу элемент И-НЕ 2. Поскольку на втором входе шифратора сохраняется уровень логической 1, на выходе

элемента И-НЕ появится уровень логического О. Код на выходах элементов И-НЕ 9-14 устанавливает триггеры 15-17 в состояние 100.

При переключении триггеров 15-17 в состояние 100 на первом-выходе логического блока 18 появляется уровень логического О, который блокирует по третьему входу элемент И-НЕ I, предотвращая обратное пере-: ключение шифратора в предыдущее состояние после прохождения помехи, есл срабатьшание произошло от таковой.

Аналогичным образом переключение шифратора в остальные состояния, при этом элементы И-НЕ 2 и 6 блокируются по третьим входам потенциалом с третьего выхода логического блока 18, элементы И-НЕ 3 и 7 - потенциалом с второго, элементы И-НЕ 4 и 8 - четвертого и элемент И-НЕ 5 - потенциалом с первого,выхода логического блока 18.

В результате описанного процесса на прямых выходах триггеров 15-17 формируется двоичный код (соответственно первый, второй и третий разряды) состояния шифратора, причем переключение шифратора из предьодутцего состояния в последующее происходит однократно за время перекрытия вход- ных сигналов. При этом связь между выходом каждого из элементов И-НЕ 1-8 и четвертым входом предыдущего элемента не оказывает влияния на работу шифратора.

Если на управляющем входе 20 реверса присутствует сигнал логической 1, логический блок 18 вьфабатьтает сигналы, обеспечивающие работу шифратора в обратном направлении. Это происходит так.

Пусть на первый вход элемента И-НЕ 1 поступает потенциал логической 1, на его выходе формируется уровень логического О, который устанавливает через элементы И-НЕ 9-14 триггеры 15-17 в нулевое состояние. Логический блок 18 при этом вырабатывает сигнал логического О на трет- тьем выходе, блокирующий прямое переключение.

При поступлении уровня логической 1 на восьмой вход шифратора на выходе элемента И-НЕ 8 сохраняется уровень логической 1, так как на четвертый вход этого элемента посту-

пает уровень логического О с выхода элемента И-НЕ 1 . При перепаде по тенциала на первом входе до уровня логического О на выходе элемента И-НЕ 1 возникает уровень логической 1, которьй деблокирует по четвертому входу элемент И-НЕ 8. Поскольку на восьмом входе шифратора сохраняется уровень логической 1, на выходе элемента И-НЕ 8 появится уровень логического О. Код на выходах элементов И-НЕ 9-14 установит триггеры 15-17 в состояние 1 И,

При переключении триггеров в состояние 111 на первом выходе логического блока 18 появляется уровень логического О, который блокирует по третьему входу элемент И-НЕ 1, предотвращая прямое переключение шифратора.

Аналогичным образом происходит переключение шифратора в остальные состояния.

Логический блок 18, выполненный на элементах И-НЕ 24-40, должен обеспечивать формирование сигналов на выходах в соответствии со следующим алгоритмом. Если на управляющем входе 20 реверса присутствует сигнал логического О, элементы И-НЕ 33, 35, 31 и 37 заперты этим сигналом, на первом выходе логического блока 18 (выход элемента И-НЕ 26) сигнал логического О появляется только тогда, когда триггер 15 находится в единичном состоянии, а триггер 16 - в нулевом, на третьем выходе блока 18 (выход элемента И-НЕ 38) сигнал логического О появляется, когда триггер 16 находится в единичном состоянии, на втором выходе (элемент И-НЕ 29) - когда триггеры 15 и 16 находятся в единичном состоянии, на четвертом (элемент И-НЕ 32) - когда триггер 16 находится в нулевом состоянии. При единичном сигнале на управляющем входе 20.реверса заперты элементы И-НЕ 34, 39, 25 и 28, нулевой сигнал на первом выходе блока 18 (элемент И-НЕ 26) появляется в единичном состоянии триггера 16; на третьем . (элемент И-НЕ 38) - в нуле- вых состояниях обоих триггеров 15 и 16, на втором (элемент И-НЕ 29) - пр нулевом состоянии триггера 16 и на четвертом выходе (выход элемента И-НЕ 32) нулевой сигнал появляется

при нулевом состоянии триггера 15 и единичном триггера 16.

Логический блок 18 может быть выполнен в виде постоянного запоминающего устройства (ПЗУ) например на микросхеме 155РЕЗ, при этом в ПЗУ должна быть записана информация, обеспечивающая вьтолнение приведенного алгоритма работы логического блока 18.

Формул

изобретения

5

0

5

0

5

0

5

0

5

1.Шифратор, содержащий элементы И-НЕ, первые входы первого - восьмого элементов И-НЕ являются информационными входами шифратора, выход первого элемента И-НЕ соединен с вторым входом второго элемента И-НЕ и с первыми входами девятого, десятого и одиннадцатого элементов И-НЕ, выходы которых соединены с первыми входами соответственно первого, второго и третьего триггеров, первые выходы первого и второго триггеров и выход третьего триггера являются соответственно первым, вторым и третьим выходами шифратора, выход второго элемента И-НЕ соединен с вторыми входами третьего, десятого и одиннадцатого элементов И-НЕ и с первым входом двенадцатого элемента И-НЕ, выход которого соединен с вторым входом первого триггера, выход третьего элемента И-НЕ соединен с вторыми входами четвертого и девятого элементов И-НЕ, третьим входом одиннадцатого элемента И-НЕ и первым входом тринадцатого элемента И-НЕ, выход которого соединен с вторым входом второго триггера, выход четвертого элемента И-НЕ соединен с вторыми входами пятого, двенадцатого и тринадцатого элементов И-НЕ и четвертым входом одиннадцатого элемента И-НЕ, выход пятого элемента И-НЕ соединен с вторым входом шестого, с третьими входами девятого и десятого и с лервым входом четырнадцатого элементов И-НЕ, выход четырнадцатого элемента И-НЕ соединен с вторым входом третьего триггера, выход шестого элемента И-НЕ соединен с вторыми входами седьмого и четырнадцатого, с третьим входом двенадцатого и с четвертым входом десятого элементов И-НЕ, выход седьмого элемента И-НЕ соединен с вторым входом восьмого, с четвертым

входом девятого и с третьими входа- ,toi тринадцатого и четырнадцатого элементов И-НЕ, выход восьмого элемента И-НЕ соединен с вторым входом первого и с четвертыми входами двенадцатого, тринадцатого и четырнадцатого элементов И-НЕ, третьи входы первого, второго, третьего и четвертого элементов И-НЕ объединены с третьими ю входами соответственно пятого, шестого, седьмого и восьмого элементов И-НЕ, отличающийся тем, что, с целью расширения области применения шифратора путем обеспечения jj его реверсивной работы, в него введен логический блок, первый, второй, третий и четвертый выходы которого подклзбчены к третьим входам соответст- венно первого, третьего, шестого и 20 восьмого элементов И-НЕ, первый, второй, третий и четвертый входы логического блока подключены соответст-; венно к первому и второму выходам

выход седьмого элемента И-НЕ соединен с первым входом восьмого элемента И-НЕ, выход которого соединен с первым входом девятого элемента И-НЕ, выходы десятого и одиннадцатого элементов И-НЕ соединены с вторыми входами соответственно шестого и девятого элементов И-НЕ, выход двенадцатого элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ, выход тринадцатого элемента И-НЕ соединен с первьм входом четырнадцатого элемента И-НЕ, выход которого соединен с первым входом пятнадцатого элемента И-НЕ, второй вход которого подключен к выходу шестнадцатого элемента И-НЕ, выход инвертора соединен с вторыми входами второго и пятого элементов И-НЕ и первыми входами одиннадцатого и шестнадцатого элементов И-НЕ, первые входы первого и четвертого элементов И-НЕ объединены и являются первым входом логипервого триггера и к первому и второ-25 ческого блока, первые входы седьмого

му выходам второго триггера, пятый вход логического блока является управляющим входом шифратора, четвертые входы первого, второго, третьего, четвертого, пятого, шестого, седьмо- зо го и восьмого элементов И-НЕ подключены соответственно к выходам второг го, третьего, четвертого, пятого, шестого, седьмого, восьмого и первого элементов И-НЕ.

2.Шифратор поп.1,отличаю- щ и и с я тем, что логический блок содержит инвертор и элементы И-НЕ, выход первого элемента И-НЕ соединен

35

и тринадцатого элементов И-НЕ объед нены и являются вторым входом логич кого блока, первый вход десятого эл мента И-НЕ объединен с вторыми вход ми четвертого, седьмого и одиннадца го элементов И-НЕ и является треть входом логиче-ского блока, первый вход двенадцатого элемента И-НЕ объ динен с вторыми входами первого, тр .надцатого и шестнадцатого элементов И-НЕ и является четвертым входом ло гического блока, вход инвертора объ динен с вторыми входами восьмого, д сятого, двенадцатого и четырнадцато

с первым входом второго элемента г о элементов И-НЕ и является пятым

входом логдгческого блока, выходы третьего, шестого, пятнадцатого и девятого элементов И-НЕ являются со ответственно первым, вторым, третьи и четвертьп выходами логического бл ка.

И-НЕ, выход которого соединен с первым входом третьего элемента И-НЕ, выход четвертого элемента И-НЕ соединен с первым входом пятого элемент та И-НЕ, выход которого соединен с nepBbw входом шестого элемента И-НЕ,

выход седьмого элемента И-НЕ соединен с первым входом восьмого элемента И-НЕ, выход которого соединен с первым входом девятого элемента И-НЕ, выходы десятого и одиннадцатого элементов И-НЕ соединены с вторыми входами соответственно шестого и девятого элементов И-НЕ, выход двенадцатого элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ выход тринадцатого элемента И-НЕ соединен с первьм входом четырнадцатого элемента И-НЕ, выход которого соединен с первым входом пятнадцатого элемента И-НЕ, второй вход которого подключен к выходу шестнадцатого элемента И-НЕ, выход инвертора соединен с вторыми входами второго и пятого элементов И-НЕ и первыми входами одиннадцатого и шестнадцатого элементов И-НЕ, первые входы первого и четвертого элементов И-НЕ объединены и являются первым входом логи

и тринадцатого элементов И-НЕ объединены и являются вторым входом логического блока, первый вход десятого элемента И-НЕ объединен с вторыми входами четвертого, седьмого и одиннадцатого элементов И-НЕ и является третьим входом логиче-ского блока, первый вход двенадцатого элемента И-НЕ объединен с вторыми входами первого, три- .надцатого и шестнадцатого элементов И-НЕ и является четвертым входом логического блока, вход инвертора объединен с вторыми входами восьмого, десятого, двенадцатого и четырнадцатог о элементов И-НЕ и является пятым

входом логдгческого блока, выходы третьего, шестого, пятнадцатого и девятого элементов И-НЕ являются соответственно первым, вторым, третьим и четвертьп выходами логического блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| Устройство для определения направления и угла поворота вращающегося объекта | 1991 |

|

SU1786441A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2017 |

|

RU2667798C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| Гомодинный лазерный интерферометрический измеритель параметров вибраций объектов | 1984 |

|

SU1188541A1 |

| Устройство для контроля и диагностики цифровых устройств | 1986 |

|

SU1499286A1 |

| Ассоциативный запоминающий элемент | 1982 |

|

SU1057988A1 |

| Система динамической синхронизации и корректировки рангов объектов в АСУ | 1985 |

|

SU1305630A1 |

Изобретение относится к автоматике, а именно к устройствам преобра зования информации, и может быть пользовано в преобразователях перемещений в код. Изобретение, обеспечивая работу шифратора как при возрастании числового значения входного кода, так и при обратном направлении счета, позволяет расширить область его использования. Шифратор содержит элементы И-НЕ 1-14, триггеры 15-17 и логический блок 18, содержащий элементы И-НЕ 24-39 и инвертор 40. 1 з.п. ф-лы, 1 ил. с СЛ

| Шифратор | 1978 |

|

SU797067A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шифратор | 1983 |

|

SU1127088A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1988-02-07—Публикация

1986-05-05—Подача