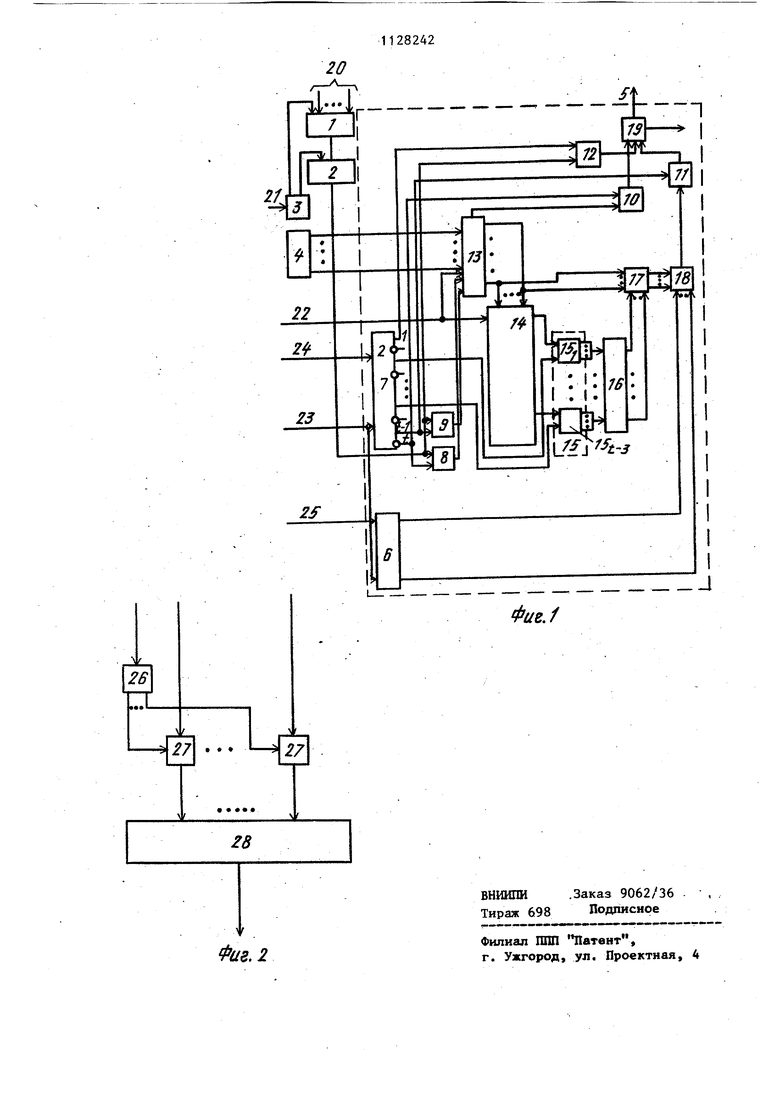

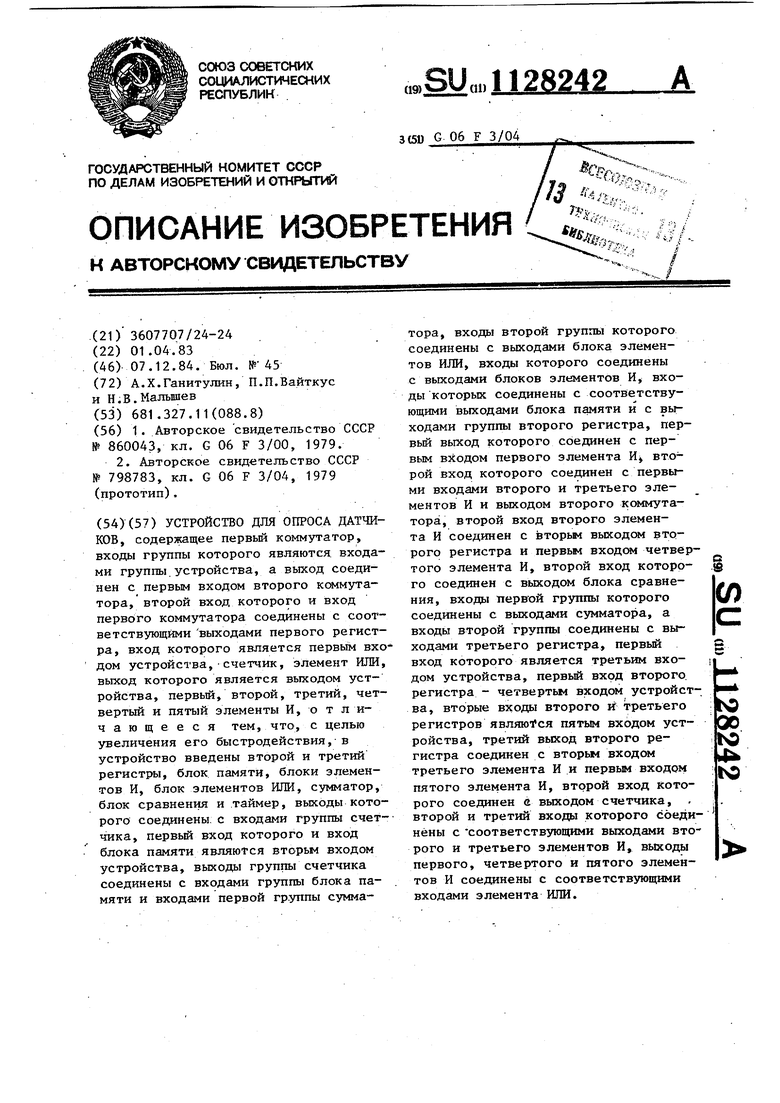

Изобретение относится к вычислительной технике, в частности к системам сбора данных, и может быть широко использовано в системах управления реконфигурацией многомодульных вычислительных систем, например, для определения модулей, подлежащих выводу в ремонтную конфигурацию, а также для сбора статистических данных о работе модулей в различных режимах. Известно устройство для выбора информации, содержащее блоки памяти, блок сравнения, блок счетчиков, регистры, распределитель импульсов, шифратор, блок синхронизации, элементы И, элементы ИЛИ и элементы НЕ. В устройство поступает поток измеритель ной информации, из которого производится выбор и переиндексация данньсх;, соответствующих адресам измерения Cl Недостатками устройства являются его сложность и невозможность выбора фиксированного количества измеренных данных, соответствующих заданному порогу и происшедших в течение определенного времени. Наиболее близким по технической сущности к изобретению является устройство для сбора информации, содержащее коммутаторы несовместимых и совместимых параметров, регистр, дешифратор, группу счетчиков, элемент ИЛИ и элементы И. I Коммутаторы несовместимых и совмес тимых параметров (на один вход) содержат дешифратор, элементы И и ИЛИ. Информационные входы коммутатора нecoв ecтимыx параметров являются информационными входами устройства, управляющий вход подключен к первому выходу регистра выбора группы, а выход соединен с информационны входом коммутатора совместимых параметров, управляющий вход которого подключен к второму вькоду регистра выбора группы. Выход элемента ИЖ является выходом запросов прерывания устройства, а входы соединены соответственно с выходами переполнения счетчиков группы, информационные выходы которых являются информационньми выходами устройства. Управляющие входы счетчиков группы подключены к соответствующим выходам дешифратора, соединенного входом с управляющим входом устройства, а счетные входы - к выходу коммутатора совместимых параметров Cz. Недостатком известного устройства является невозможность сбора данных о наступлении определенного количества событий за конкретное время, что не позволяет своевременно принять решение на изменение.структурной конфигурации многомодульных ЭВМ. Цель изобретения - увеличение быстродействия устройства. .Поставленная цель достигается тем, что в устройство для опроса датчиков, содержащее первый коммутатор, входы группы которого являются входами группы устройства, а выход соединен с первым входом второго коммутатора, второй вход которого и вход первого коммутатора соединены с соответствующими выходами первого регистра, вход которого является первым входом устройства, счетчик, элемент ИЛИ, выход которого является выходом устройства, первьй, второй, третий, четвертьй и пятый элементы И, введены второй и третий регистры, блок памяти, блоки элементов И,, блок элементов ИЛИ, сумматор, блок сравнения и таймер, выходы которого соединены с входами . группы счетчика, первьш вход которого и вход блока памяти являются вторым входом устройства, выходы группы счетчика соединены с входами группы блока памяти и входами первой группы сумматора, входы второй группы которого соединены с выходами блока элементов ИЛИ, входы которого соединены с выходами блоков элементов И, входы которых соединены с соответствзтощими вькодами .блока памяти и с выходами группы второго регистра,первый выход которого соединен с первым входом первого элемента И, второй вход которого соединен с первыми входами второго и третьего элементов И и выходом второго коммутатора, второй вход второго элемента И соединен с вторым выходом второго регистра и первым входом четвертого элемента И, второй вход которого соединен с выходом блока сравнения, входы первой группы которого соединены с выходами сумматора, а входы второй группы соединены с выходами третьего регистра, первый вход которого является третьим входом устройства, первьй вход второго регистра - четвертым входом устройства, вторые входы второго и третьего регистров являются пятым входом устройства, третий выход второго регистра соединен с вторым входом третьего , элемента И и первым входом пятого элемента И, второй вход которого сое динен с выходом счетчика, второй и третий входы которого соединены с соответствующими выходами второго и третьего элементов И,- выходы первого четвертого и пятого элементов И соединены с соответствующими входами элемента ИЛИ. На фиг. 1 представлена функционал ная схема устройства для опроса датчиков; на фиг. 2 - схема первого (вт рого) коммутатора. Устройство содержит первый коммутатор 1 , второй коммутатор 2, первый регистр 3, таймер 4, выход 5, третий регистр 6, второй регистр 7, третий элемент И 8, второй элемент И 9, пятьй элемент И 10, чеТвер тый элемент И 11, первый элемент И 12 счетчик 13, блок 14 памяти, блоки элементов И 15, блок элементов ИЛИ 16 сумматор 17, блок 18 сравнения, элемент ИЛИ 19, входы 20 группы, первый вход 21, второй вход 22, пятый вход 23, четвертый вход 24, третий вход 25. . Первый (второй) коммутатор 1 (2) (фиг. 2) содержит дешифратор 26, элементы И 27 w элемент ИЛИ 28. Устройство работает следующим образом. По сигналу, поступающему на вход 2 устройства, осуществляется обнуление блока 14 памяти (магазинного запоминающего устройства) и всех разрядов счетчика 13 за исключением самого старшего, в которьш записывается 1 Под действием сигнала, поступающего на вход 23 устройства, в регистры 6 и 7 заносится соответственно код временного интервала и код однопозиционньй порога. Порог определяет koлйчecтвo событий (сбоев, отказов и т.д.) происходящих за фиксированный интервал вре мени, код которого хранится в регист ре 6. Одновременно с записью кодов поро га и временного интервала в регистры 7 и 6 на регистр 3 через управляющие входы 21 устройства записывается код адресов коммутации. Устройство далее может работать в двух режимах: определения количест ва совершившихся событий без учета времени, в течение которого они произошли., определения количества совершившихся событий за строго фиксированный промежуток времени. Для задания режимов работы устройства в регистре 7 отведен- один из разрядов (самьш младший), в который одновременно с записью в старшие разряды кода порогов заносится код режима работы (1 или О). Код О соответствует первому, а код 1 второму режимам работы. В первом режиме работы с 2 го и z-1-го выходов регистра 7 (с прямат го и инверсного выходов разряда режима) на вторые э|1ементов И 8 и 9, действуют соответственно нулевой и единичньй сигналы. Регистр 3 через коммутаторы 1 и 2 коммутирует К-й информационный вход из входов 20 устройства (, ..., N , где N количество информационных входов устройства) , к которому подключена опрашиваемая контрольная точка, на первые входы элементов И 8 и 9 и на второй вход элемента И 12. Под действием единичного сигнала с z-ro выхода (Z - количество выходов регистра 7) регистра открывается третий 8 и пятьй 10 элементы И. Поступивший при этом с контрольной точки сигнал проходит через открытый элемент И 8, действуя на второй (счетный) вход счетчика 13, которьй осуществляет их суммирование. При переполнении счетчика 13 сигнал через открытьй элемент И 10, элемент ИЛИ 19 и выход 5 устройства поступает в блок прерываний управляющего процессора, по которому осуществляется прерывание и передача управления программе учета статистической информации. При поступлении очередного сигнала на |второй (счетньй) вход счетчика 13 работа устройства аналогична рассмотренной. Во втором режиме работы в разряде режима находится код 1. Поэтому на выходе регистра 7 действует нулевой, а на 2-1-м выходе - единичньй сигналы. Регистр 3 через комутаторы 1 и 2, как и в первом режие, коммутирует k-й информационный вход из входов 20 устройства, к котоому подключена опрашиваемая контольная точка, на входы элементов И 810. Во втором режиме работы устройст- ва возможны три случая: однопозицион5 .11 ный код порога Ъ; хранящийся в регистре 7, не равен единице и с контррльной точки поступил j-й сигнал, номер которого меньше порога ( j Ь ) однопозиционный код порога Ъ не равен единице ( Ъ 2, ..., i- 2), и с контрольной точки поступил сигнал, номер которого больше или равен порогу (j Ь ), однопозиционный код порога, храняющийся в регистре 7, равен единице (Ь 1). В первом случае второго режима единицы находятся в двух разрядах регистра 7; в разряде режима и в разряде, номер которого определяется заданньм однопозиционным кодом порога (Ъ 2, ..., t - 2) . Поэтому единичным сигналом,, действующим с t -1го выхода регистра 7, открывается второй 9 и четвертый 11 элементы И. К0оме того, единичным сигналом, действующим с -го (Р Ъ) выхода того же регистра открываются элементы И I-го ( Ъ- 1) блока 15. Элементы И остальных блоков 15 оста.ются закрытыми, так как на вторых их входах нулевые сигнал1 1 с соответствующих выходов регистра 7. Поступивший сигнал с контрольной точки.проходит открытый элемент И 9 и действует на третий (стробирующий) вход счетчика 13, котррьй в этом режиме работает как регистр. При наличи сигнала на третьем входе код текущего времени с таймера 4 записьшается в счетчик 13. Таким образом в счет,чике 13 будет зафиксирован момент прихода j-ro (j b ) сигнала с контрольной точки. Кроме того, j-й Jtlt.:lJ4 ХЛ, jT.-fc«ieJ.i. сигнал с контрольной точки осуществляет перепись кода времени поступления j-1-го сигнала со счетчика 13 в первую ячейку блока 14 памяти. Но до поступления j-ro ( j b) сигнала с контрольной точки в г-й (г Ь-1) ячейке блока 14 памяти информации. нет (хранится код О), поэтому и на выходах элементов И i-го блока 15 действуют нулевые сигналы, несмотря на то, что на их вторых входах деист1-го выховуют единичные сигналы с да регистра 7. На сумматоре 17 осуществляется определение разности между находящимся в счётчике 13 кодом времени поступпения j-ro сигнала с контрольной точки и кодом времени, хранящимся в одной из ячеек блока. 14 памяти (ЭТУ - .. 2 . 6 разность в дальнейшем будем называть разностным временем), Следовательно, в сумматоре 17 при поступлении j-ro ( j Ь ) сигнала с контрольной точки определяется разность между кодом времени, находящимся в счетчике 13, и кодом времени, равным нулю (так как на выходах элементов ИЛИ блока 16 нулевые сигналы) , С сумматора 17 код разностного времени (при У Ь - это собственно код времени поступления j-ro сигнала с контрольной точки) поступает на первую группу входов блока 18 сравнения. Последний, в общем случае, осуществ- ляет сравнение кода заданного интервала времени, поступающего с регистpa 6 на входы второй его группы, с разностным кодом времени поступления j-ro сигнала .с контрольной точки. Если код разностного времени j-ro сигнала равен или меньше кода заданного юттервала времени, то на выходе блока 18 сравнения будет деиствовать единичньй сигнал. Б первом случае второго режима единичный сигнал на выходе блока 18 сравнения может возникнуть и при поступлении j-ro (j Ь) сигнала с контрольной точки. Это происходит когда разность между кодом времени поступления j-ro (J : b ) сигнала с контрольной точки времени, хранящимся в - ячейке блока 14 памяти г-и ячейке которого до поступле « J сигнала -хранятся нули), меньше или равна коду заданного интерВала времени. Но этот сигнал будет ложньм, поскольку в действительности «1J/, 14 поступил только . j-и ( j Ь ) сигнал с контрольной точки, т.е. условие, что поступил j-й сигнал с номером, Равным Ь , еще не вьшолнилось. искл-.очения этой ситуации в дополнительный разряд счетчика 13 записывается 1..В этом случае код разностного времени всегда будет больше кода заданного интервала времени (так как в старшем разряде регистра 6 всегда находится О) и на выходе блока 18 сравнения, а следовательно, и на выходе 5 устройствавложного единичного сигнала не будет. Во втором случае второго режима при поступлении j-ro ( j : Ь ) сигнала с контрольной точки в г-й ( ) ячейки блока 14 памяти окажется код времени поступления i-t + 1-го J ; сигнала. Этот код времени через Ьткрытые элементы И |--го блока 15 (так как на вторых входах этих элементов действует единичный сигнал с Р-го выхода регистра 7) и элементы ИЛИ блока 16 поступает нА входы второй группы входов сумматора 17. В послед нем определяется разностное время j-ro ( j/b ) сигнала с контрольной точки, код времени поступления котор го хранится в счетчике 13 и j-b+1го сигнала, код времени поступления которого хранится в --й() ячейке блока 14 памяти. При определении разностного времени j-ro (j Ъ ) и j 1-го сигналов с контрольных точек единицы,добавлен ные к коду времени их поступления, за счет записи единицы в старший . разряд счётчика 13 вычитаются. Таким образом, на выходе сумматора 17 в этом случае будет получено действительное разностное время j-ro (j7,ь) и j-b+ 1-го сигналов с контрольной точки. Блок 18 сравнения, как и в предьщущем слзгчае, осуществляет срав нение разностного кода времени j-ro (/Ъ)и j-b + 1-го сигналовс кодом заданного интервала времени. Если разностный код времени j-ro ( j Ь ) и j - 1-го сигналов равен или меньше кода заданного интервала времени, то на выходе блока 18 сравнения, а следовательно, и на выходе 5 устройства будет действовать единичный сигнал, свчцетедьствующий о поступлении j -го ( j - Ь ) сигнала в заданном интервале времени В третьем случае второго режима единичный сигнал на выходе 5 устройства должен появиться каждый раз, как только пришел сигнал с контрольной точки (без учета временного интервала) . . Поэтому в регистр 6 одновременно с записью в регистр 7 порога, равного 1 (b - 1), заносится код временного интервала, равньй О. При. коде порога, равном 1 (-Ь 1), единичный сигнал действует только на первом выходе регистра 7, а соответственно, и на первом входе элемента И 12. Поступивший при этом сигнал с контрольной точки действует на второй вход элемента И 12, что приводит к появлению на выходе устройства единичного сигнала. Таким образом, предлагаемое устройство позволяет по количеству событий, поступивших в заданном интервале времени, определить начало воздействия на вычислительную систему внешних интенсивных мешающих факторов (например, помех), наиболее подверженные этим мешающим факторам модули ЭВМ, и осуществить их своевременньй вывод в ремонтную конфигурацию, а также на основе определения и анализа различных групп событий оценить эффективность использования оборудования, причина его простоя и перегрузок с целью рационального распределения ресурсов в вычислительной системе., Использование предлагаемого устройства в системах управления реконфигурацией в многомодульных вычислительных системах позволяет значительно аденьшить количество ложных выводов в ремонтную конфигурацию.

Фue.f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для опроса датчиков | 1984 |

|

SU1238089A2 |

| Устройство для выделения области во внешней памяти | 1985 |

|

SU1254497A1 |

| Устройство для сбора данных о работе операционной системы | 1981 |

|

SU1024934A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Устройство для управления блоками памяти | 1982 |

|

SU1111203A1 |

| Устройство для сдвига информации | 1983 |

|

SU1109807A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1160414A1 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1126963A1 |

УСТРОЙСТВО ДЛЯ ОПРОСА ДАТЧИКОВ, содержащее первьш коммутатор, входы группы которого являются, входами группы.устройства, а выход соединен с первым входом второго коммутатора, второй вход которого и вход первого коммутатора соединены с соответствующими выходами первого регистра, вход которого является первым вхо дом устройства,счетчик, элемент ИЛИ, выход которого является выходом устройства, первый, второй, третий, четвертый и пятый элементы И, о т л ичающееся тем, что, с целью увеличения его быстродействия, в устройство введены второй и третий регистры, блок памяти, блоки элементов И, блок элементов ИЛИ, сумматор, блок сравнения и таймер, выходы которого соединены, с входами группы счетчика, первый вход которого и вход блока памяти являются вторьм входом устройства, выходы группы счетчика соединены с входами группы блока памяти и входами первой группы сумматора, входы второй группы которого соединены с выходами блока элементов ИЛИ, входы которого соединены с выходами блоков элементов И, входы которых соединены с соответствующими выходами блока памяти и с вьгходами группы второго регистра, первьм выход которого соединен с первым входом первого элемента И второй вход которого соединен с первыми входами второго и третьего элементов И и выходом второго коммутатора, второй вход второго элемента И соединен с ззторьм выходом второго регистра и первым входом четвертого элемента И, второй вход которого соединен с выходом блока сравнеСП ния, входы первой группы которого соединены с выходами сумматора, а входы второй группы соединены с выходами третьего регистра, первьй вход которого является третьим входом устройства, первьй вход второго, регистра - четвертые входом устройства, вторые входы второго и третьего регистров являются пятым входом устройства, третий выход второго регистра соединен с вторьм входом третьего элемента И и первым входом пятого элемента И, второй вход которого соединен ё выходом счетчика, второй и третий входы которого соединены с соответствзгющими выходами второго и третьего элементов И, выходы первого, четвертого и пятого элементов И соединены с соответствующими входами элемента ИЛИ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для выбора информации | 1979 |

|

SU860043A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сбора информации | 1979 |

|

SU798783A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-07—Публикация

1983-04-01—Подача