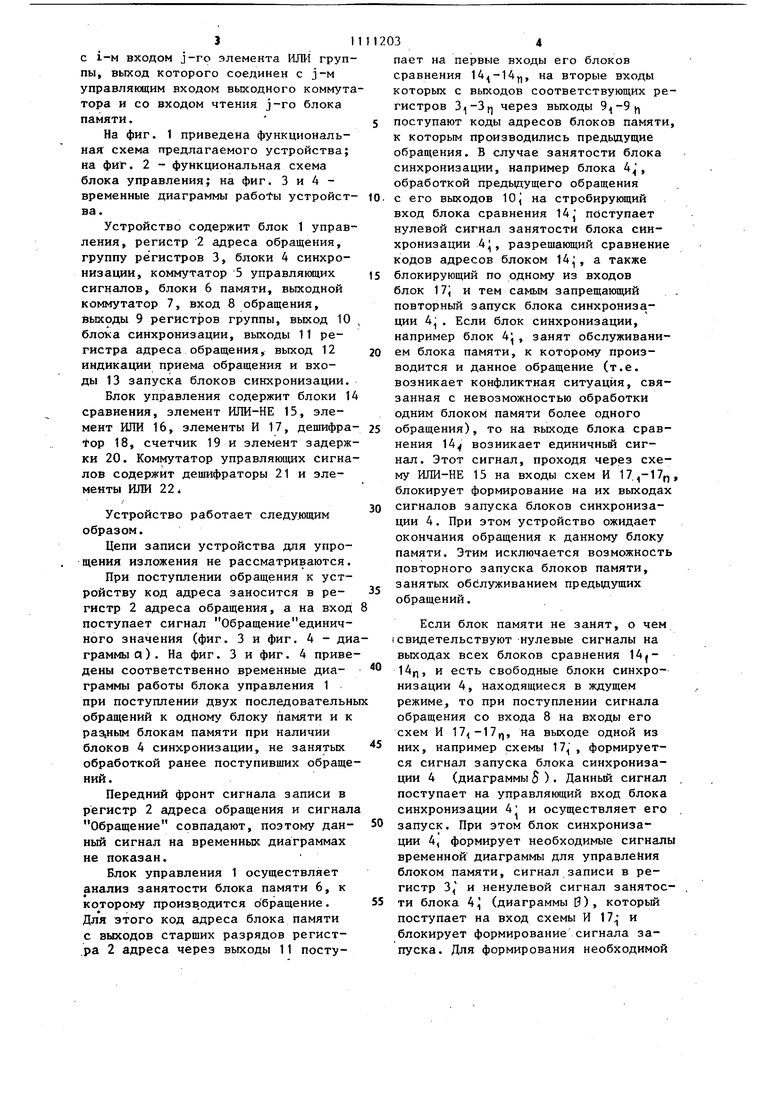

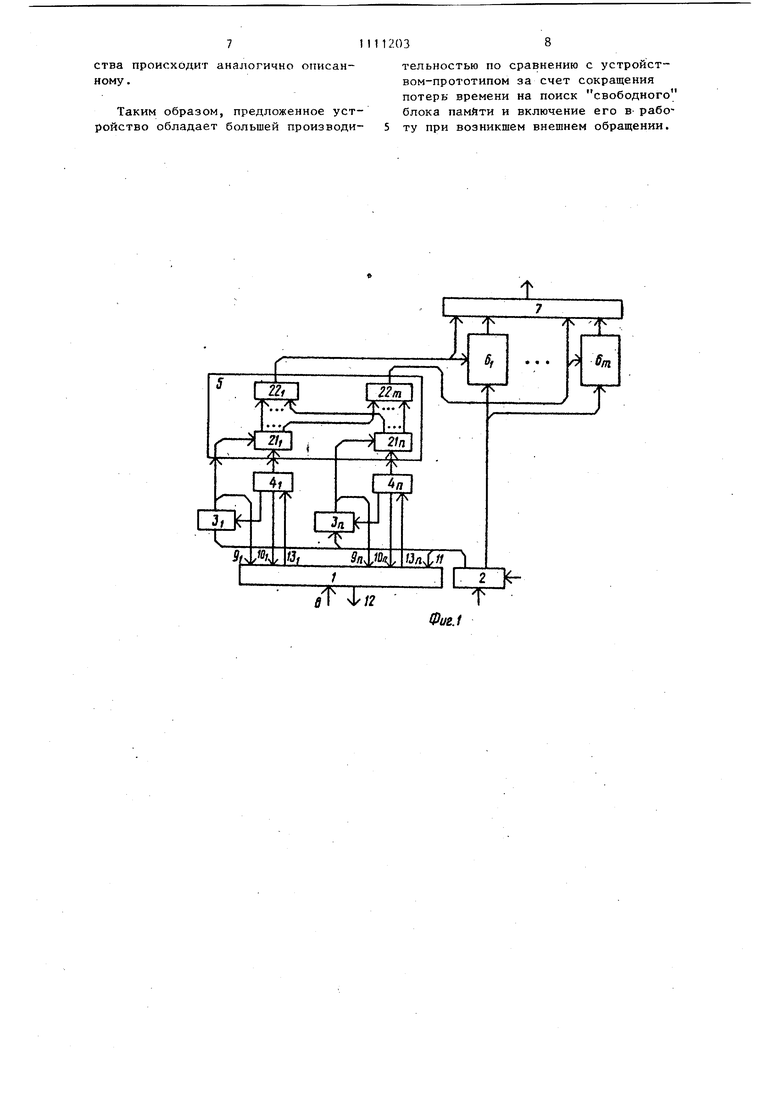

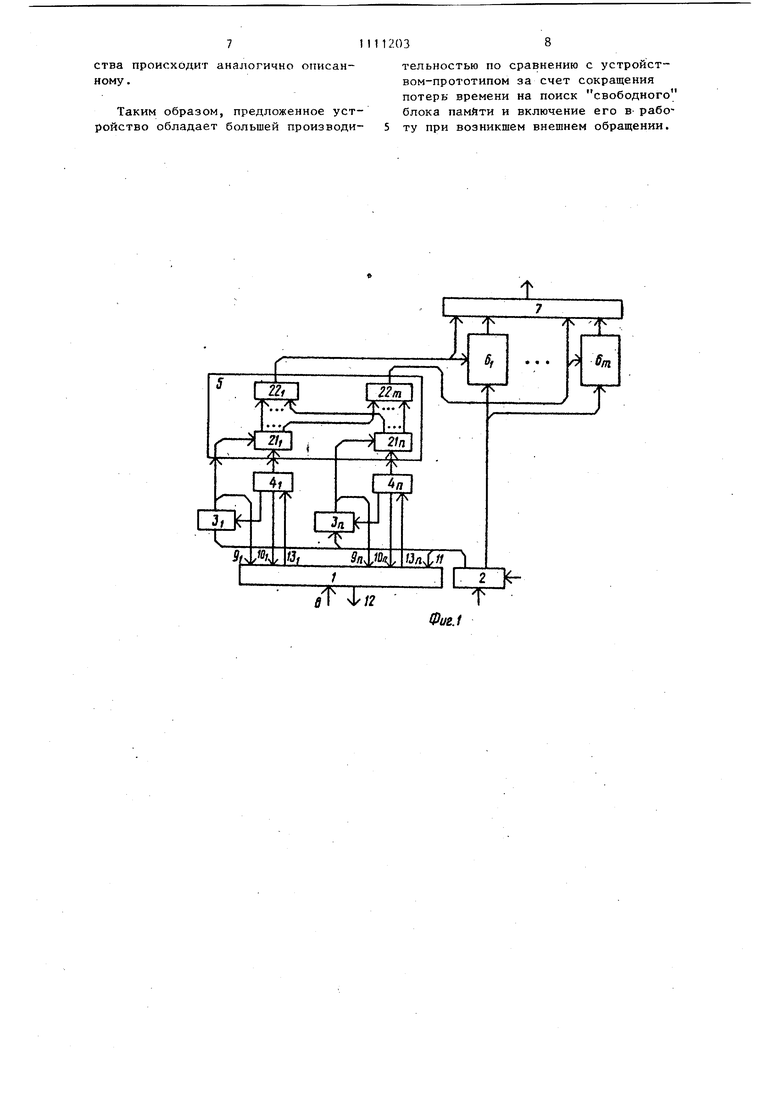

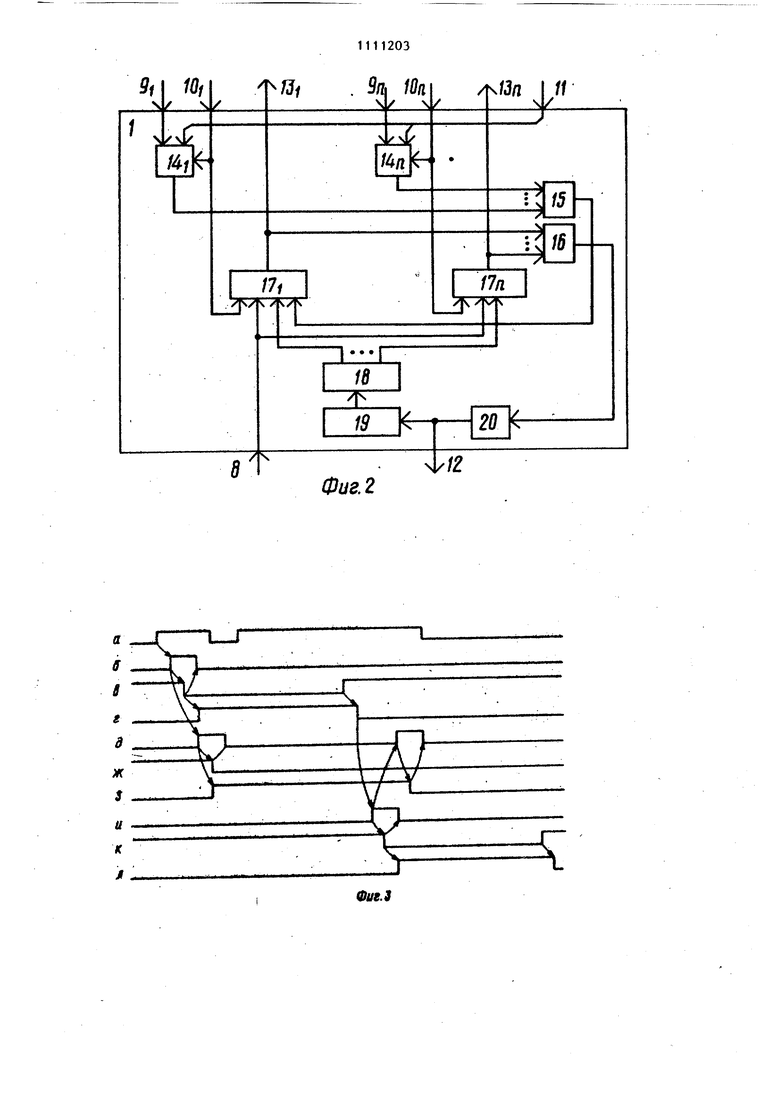

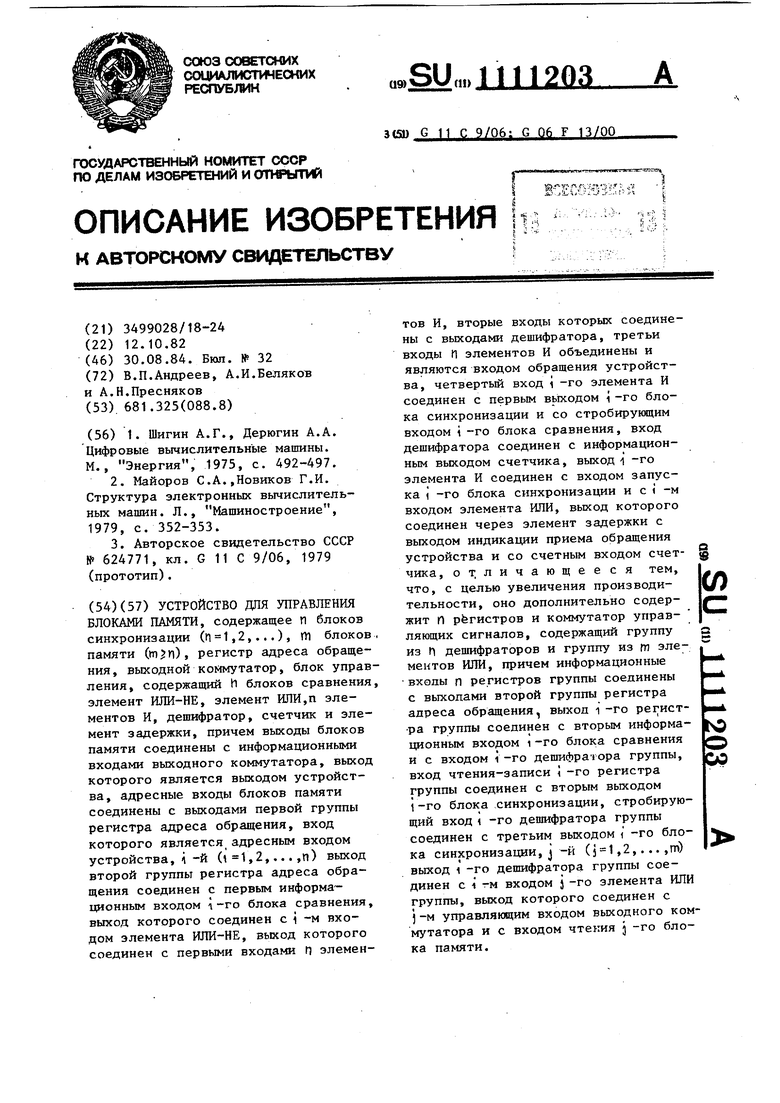

Изобретение относится к вычислительной технике и может быть использ вано в качестве устройства для управ ления блоками памяти с повышенным быстродействием. Известны устройства для управлени блоками памяти, содержащие блоки синхронизации, входящие ь состав каж дого блока памяти регистр адреса, вы ходной коммутатор, устройство управления l и 2. К недостаткам этих устройств отно сится большое количество оборудовани наряду с его непроизводительными про стоями. Наиболее близким к предлагаемому является устройство для управления блоками памяти, содержащее п блоков синхронизации (,2,...). группу бл ков памяти, регистр адреса обращения выходной коммутатор и блок управления, содержащий п блоков сравнения, элемент ИЛИ-НЕ, элемент ИЛИ, п элеме тов И, дешифратор, счетчик и элемент задержки, причем выходы блоков памяти соединены с информационными входа ми выходного коммутатора, выход кото рого является выходом устройства, адресные входы блоков памяти соедине ны с выходами первой группы регистра адреса обращения, вход которого явля ется адресным входом устройства, i-й (,2...,n) выход второй группы регистра адреса обращения соединен с первым информационным входом 1-го блока сравнения, выход которого соединен с i-M входом элемента ИЛИ-НЕ, выход которого соединен с первыми входами п элементов И, вторые входы которых соединены с выходами дешифратора, третьи входы п элементов И объединены и являются входом обращения устройства, четвертый вход i-ro элемента И соединен с первым выходом i-ro блока синхронизации и со стробирукяцим входом i-ro блока сравнения, вход дешифратора соединен с информационным выходом счетчика, выход i-ro элемента И соединен со входом запуска i-ro блока синхронизации и с i-м входом элемента ИЛИ, выход которого через элемент задержки соединен с выходом индикации приема обращения устройства j со счет ным входом счетчика З . Недостатком данного устройства является низкая производительность памяти. Целью изобретения является повыше-, ние производительности. Указанная цель достигается тем, что в устройство для управления блоками памяти, содержащее п блоков синхронизации (,2...), m блоков памяти (), регистр адреса обращения, выходной коммутатор и блок управления, содержащий п блоков сравнения, элемент КПИ-НЕ, элемент ИЛИ, п элементов И, дешифратор, счетчик и элемент задержкиj причем выходы блоков памяти соединены с информационными входами выходного коммутатора, выход которого является выходом устройства, адресные входы блоков памяти соединены с выходами первой группы регистра адреса обращения, вход которого явля я адресным входом устройства, d-l ,2,...,п) выход второй группы регистра адреса обращения соединен с первым информационным входом 1-го блока сравнения, выход которого соединен с i-M входом элемента ИЛИ-НЕ, вьгход которого соединен с первыми вхо дами п элементов И, вторые входы которых соединены с выходами дешифратора, третьи входы п элементов И объединены и являются входом обращения устройства, четвертый вход i-ro элемента И соединен с первым выходом i-ro блока синхронизации и со стробирующим входом i-ro блока сравнения, вход дешифратора соединен с информационным выходом счетчика, выход i-ro элемента И соединен со входом запуска i-ro блока синхронизации и с i-м входом элемента ИЛИ, выход которого соединен через элемент задержки с выходом индикации приема обращения устройства и со счетным входом счетчика, введены п регистров и коммутатор управляющих сигналов, содержащий группу из п дешифраторов и группу из m элементов ИЛИ, причем информационные входы п регистров группы соединены с выходами второй группы регистра адреса обращения, выход i-ro регистра группы соединен со вторым информационным входом i-ro блока сравнения и со входом i-ro дешифратора группы, вход чтения-записи i-ro регистра группы соединен со вторым выходом i-ro блока синхронизации, стробирующий вход i-ro дешифратора группы соединен с третьим выходом i-ro блока синхронизации, j-й (,2,,..,т) выход i-ro дешифратора группы соединен 3 с i-M входом j-го элемента ИЛИ груп пы, выход которого соединен с j-м управляющим входом выходного коммут тора и со входом чтения j-ro блока памяти. На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока управления; на фиг. 3 и 4 временные диаграммы paбotы устройст ва. Устройство содержит блок 1 управ ления, регистр 2 адреса обращения, группу регистров 3, блоки 4 синхронизации, коммутатор 5 управляквдих сигналов, блоки 6 памяти, выходной коммутатор 7, вход 8 обращения, выходы 9 регистров группы, выход 10 блока синхронизации, выходы 11 регистра адреса обращения, выход 12 индикации приема обращения и входы 13 запуска блоков синхронизации. Блок управления содержит блоки 1 сравнения, элемент ИЛИ-НЕ 15, элемент ИЛИ 16, элементы И 17, дешифра fop 18, счетчик 19 и элемент задерж ки 20. Коммутатор управляющих сигна лов содержит дешифраторы 21 и элементы ИЛИ 22. Устройство работает следующим образом. Цепи записи устройства для упрощения изложения не рассматриваются. При поступлении обращения к устройству код адреса заносится в регистр 2 адреса обращения, а на вход поступает сигнал Обращение единичного значения (фиг. 3 и фиг. 4 - ди граммы а ). На фиг. 3 и фиг. 4 приве дены соответственно временные диаграммы работы блока управления 1 при поступлении двух последовательн обращений к одному блоку памяти и к pa3tHbiM блокам памяти при наличии блоков 4 синхронизации, не занятых обработкой ранее поступивщих обраще ний. Передний фронт сигнала записи в регистр 2 адреса обращения и сигнал Обращение совпадают, поэтому данный сигнал на временных диаграммах не показан. Блок управления 1 осуществляет анализ занятости блока памяти 6, к которому производится обращение. Для этого код адреса блока памяти с выходов старших разрядов регистра 2 адреса через выходы 11 посту3пает на первые входы его блоков сравнения ,, на вторые входы которых с выходов соответствующих регистров 3/1-3f через выходы поступают коды адресов блоков памяти, к которым производились предыдущие обращения. В случае занятости блока синхронизации, например блока , обработкой предыдущего обращения с его выходов 10 j на стробирукяций вход блока сравнения 14 поступает нулевой сигнал занятости блока синхронизации 4 , разрешающий сравнение кодов адресов блоком 14, а также блокирующий по одному из входов блок 17 и тем самым запрещающий повторньй запуск блока синхронизации 4 . Если блок синхронизации, например блок 4, занят обслуживанием блока памяти, к которому производится и данное обращение (т.е. возникает конфликтная ситуация, связанная с невозможностью обработки одним блоком памяти более одного обращения), то на выходе блока сравнения 14 возникает единичный сигнал. Этот сигнал, проходя через схему ИЛИ-НЕ 15 на входы схем И 17. ,-17,, блокирует формирование на их выходах сигналов запуска блоков синхронизации 4. При этом устройство ожидает окончания обращения к данному блоку памяти. Этим исключается возможность повторного запуска блоков памяти, занятых обслуживанием предыдущих обращений. Если блок памяти не занят, о чем I свидетельствуют нулевые сигналы на выходах всех блоков сравнения 14j14f, и есть свободные блоки синхронизации 4, находящиеся в ждущем режиме, то при поступлении сигнала обращения со входа 8 на входы его схем И , на выходе одной из них, например схемы , формируется сигнал запуска блока синхронизации 4 (диаграммы 5). Данный сигнал поступает на управляющий вход блока синхронизации 4 и осуществляет его запуск. При этом блок синхронизации 4, формирует необходимые сигналы временной диаграммы для управления блоком памяти, сигнал записи в регистр и ненулевой сигнал занятости блока 4 (диаграммы 0), которьм поступает на вход схемы И и блокирует формирование сигнала запуска. Для формирования необходимой длительности сигнала запуска сигнал занятости блока 4| должен формироваться с некоторой задержкой по от.ношению к переднему фронту сигнала запуска. Передний фронт сигнала запи си в регистр 3 может совпадать с пе редним фронтом сигнала запуска (диаграммы 5), поэтому данный сигнал на временных диаграммах не показан. По переднему фронту сигнала занятости блока синхронизации 4j (диагра мы В ) на выходе схемы сравнения 14j формируется единичный сигнал сравнения (диаграммы 2)« осуществляющий блокировку запусков блоков синхронизации 4 до поступления следующего обращения. Сигнал запуска с выхода схемы И 17 через схему ИЛИ 16, элемент задержки 20, служащий для форми рования нужной длительности сигнала, и выход 12 вьщается в систему, сигна лизируя о приеме обращения на обработку (диаграммы ). Связь устройства и системы осуществляется по асинхронному принципу. В данном случае этот принцип заключается в том, что сигнал обращения к устройству поступает на его вход 8 до получения системой подтверждения о принятии на обработку предыдущего обращения, поеле чего система при необходимости формирует следующий сигнал обращения Для устранения возможности запуск нескольких блоков синхронизации блок 1 содержит специальную схему приоритета, состоящую из дешифратора 13 и счетчика 19. В исходном состоянии счетчик 19 обнулен, при этом выбран первый выход дешифратора 18. Единичный сигнал с первого выхода дешифратора 18 разрешает формирование сигнала запуска блока синхронизации 4 на выходе схемы И 17 , остальные схемы И блокированы нулевыми сигналами, поступакщими на их входы с невыбранных выходов де шифратора. Единичный сигнал запуска, проходя с выхода схемы И 17 через схему ИЛИ 16, элемент задержки 20 на суммирующий вход счетчика 19, увеличивает его содержимое на единицу. В этом случае становится выбранным второй выход дешифратора 18, еди ничньй сигнал с выхода которого разрешает формирование сигнала запуска на выходе схемы И 172 Такая дисциплина организации запуска блоков синхронизации является оптимальной, так как обеспечивает выбор блока синхронизации либо свободного, либо время освобождения которого минимально, если все блоки заняты. На диаграммах )К и J показаны сигналы с выходов i-ro и (i+1)-ro выходов дешифратора 18. Сигналом с выхода инициализирован ного блока синхронизации 4 производится запись кода адреса блока памяти в соответствующий ему регистр 3. Код адреса блока памяти с выхода регистра 3 поступает на управляющие, входы коммутатора 5 управляющих сигналов и через его дешифраторы 21 и схемы ИЛИ 22j подключает выходы инициализированного блока синхронизации 4{ к управляющим входам соответствующего блока памяти 6i и управляющему входу коммутатора 7, разрешая прохождение считанного числа с выхода данного блока памяти на выходы устройства. Пусть после выдачи в систему сигнала ответа (диаграмма Д) система сформировала следующее обращение к устройству. Если обращение производится к тому же блоку памяти, то на выходе блока сравнения сохраняется единичный сигнал (диаграмма 1 ) и устройство ожидает окончания обработки обращения данным блоком памяти. После этого задним фронтом сигнала занятости блока синхронизации 4 (диаграмма б) вьдача единичного сигйала с выхода блока сравнения 14 блокируется и на выходе схемы И 17. формируется сигнал запуска блока синхронизации 4. (диаграмма Ц ). Далее работа устройства происходит аналогично описанной. На диаграймах k показаны сигналы занятости блока синхронизации А ., на диаграммах Л - сигналы с вьпсода блока сравнения 14{,. Если обращение производится к блоку памяти, не занятому обработкой предыдущего обращения, то по фронту сигнала записи адреса в регистр 2 адреса обращения, совпадающему с фронтом сигнала обращения, производится окончание вьщачи единичного сигнала блокировки с выхода блока сравнения 14 и по заднему фронту этого сигнала формируется сигнал запуска блока синхронизации 4;(+ (диаграмма и). Далее работа устройства происходит аналогично описанному. Таким образом, предложенное уст- блока памйти и включение его в-раборойство обладает большей производи- 5 ту при возникшем внешнем обращении.

11112038

тельностью по сравнению с устройством-прототипом за счет сокращения потерь времени на поиск свободного

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Запоминающее устройство | 1982 |

|

SU1069000A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1282121A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ БЛОКАМИ ПАМЯТИ, содержащее п блоков синхронизации (п 1,2,...), П блоков, памяти (), регистр адреса обращения, выходной коммутатор, блок управления, содержащий И блоков сравнения, элемент ИЛИ-НЕ, элемент ИПИ,п элементов И, дешифратор, счетчик и элемент эадержки, причем выходы блоков памяти соединены с информационными входами выходного коммутатора, выход которого является выходом устройства, адресные входы блоков памяти соединены с выходами первой группы регистра адреса обращения, вход которого является адресным входом устройства, i -и

в }2

Т

0ue.t

Фиг. 2

а ff в g

д

ж

3

а

к

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ШИРИН А.Г., Дерюгин А.А | |||

| Цифровые вычислительные машины | |||

| М., Энергия, 1975, с | |||

| Катодный усилитель | 1923 |

|

SU492A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Структура электронных вычислительных машин | |||

| Л., Машиностроение, 1979, с | |||

| Судно | 1918 |

|

SU352A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-08-30—Публикация

1982-10-12—Подача