1

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых интег рирующих машин и специалиэированных процессоров, предназначенных для решения систем линейных дифференциальных уравнений вида

у - А„ + в; у(о; у, где А цирнтов соответственно

Ajj + в; у(0) . и В - матрица и вектор коэффиЦель изобретения - повышение быстродействия.

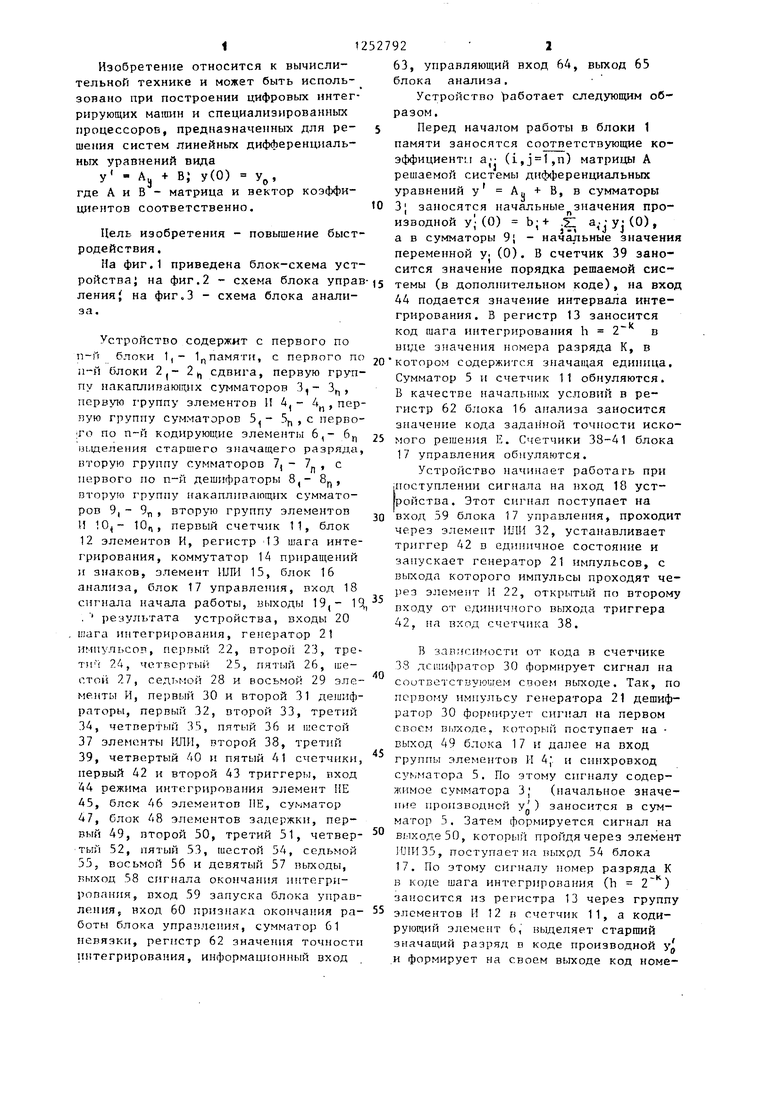

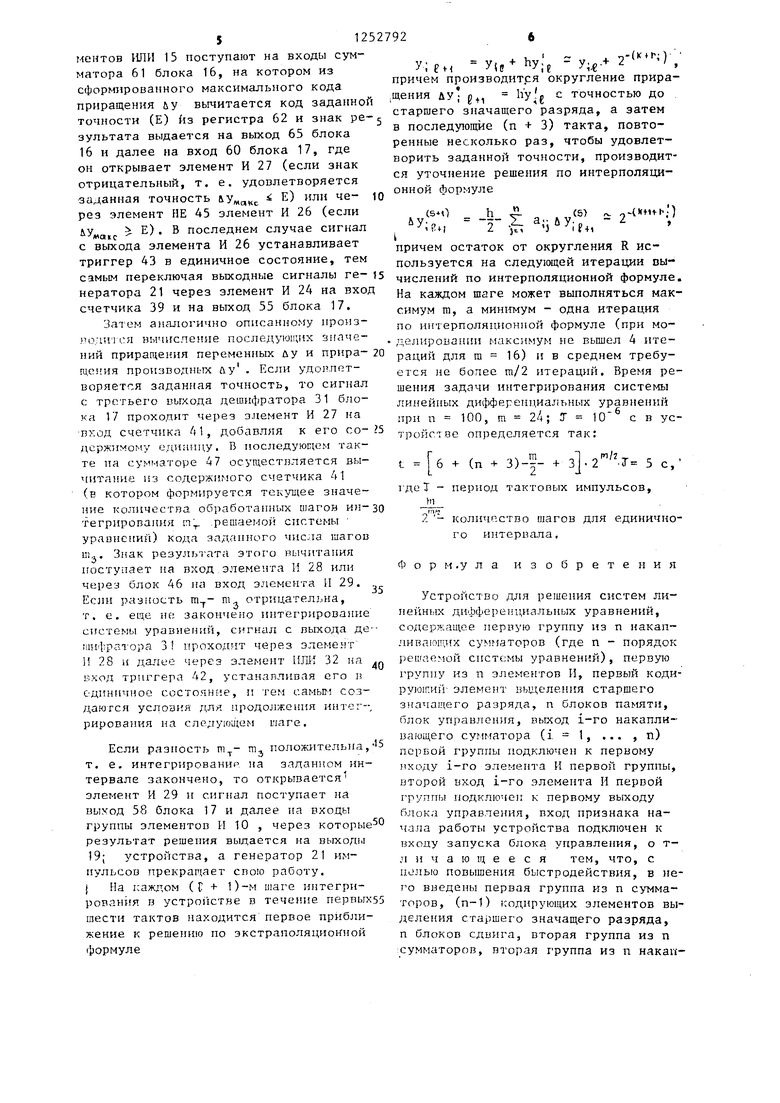

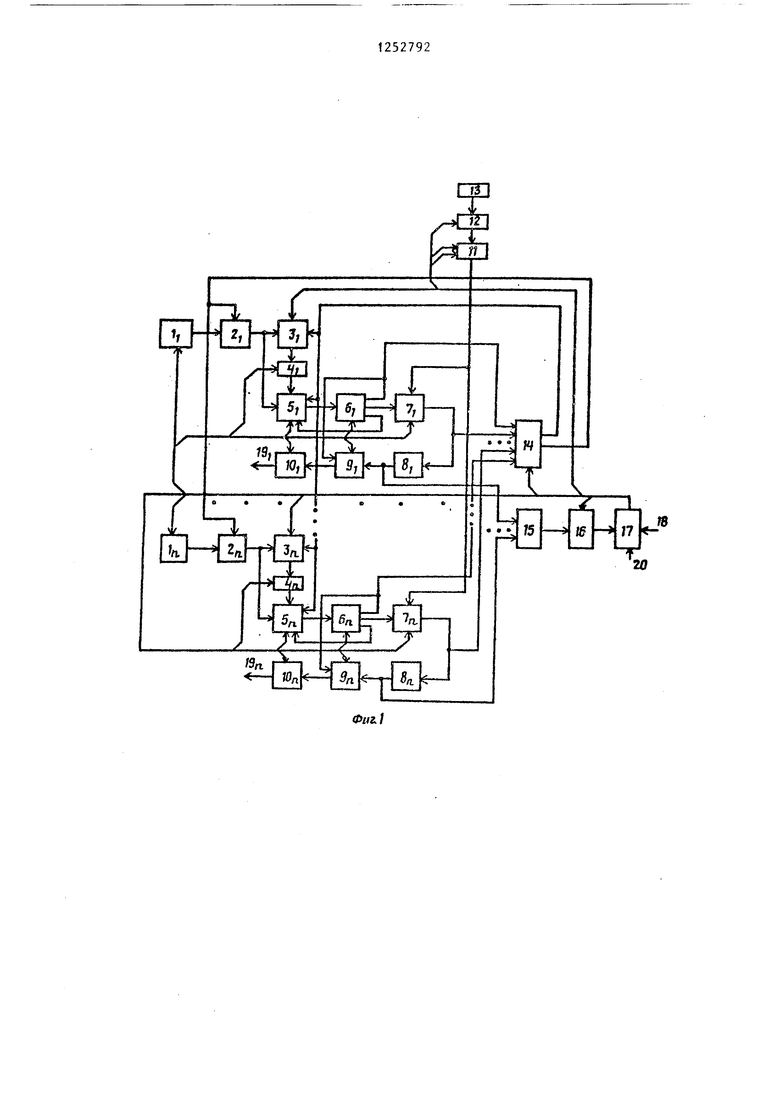

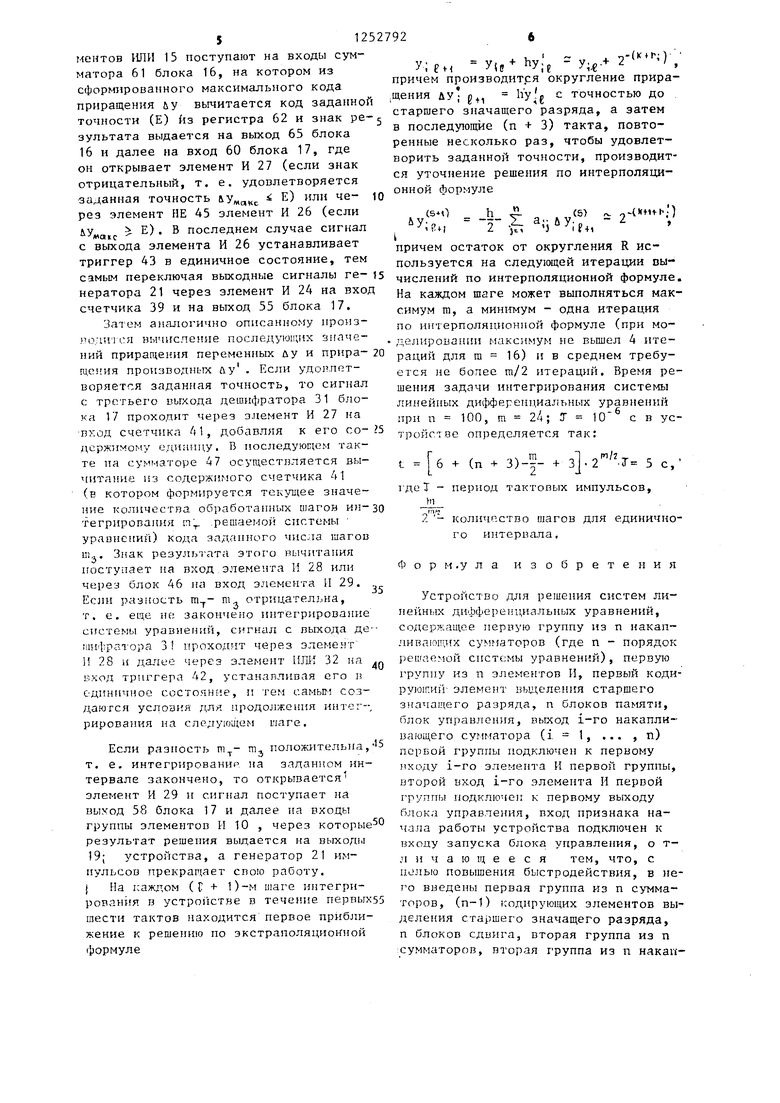

На фиг.1 приведена блок-схема уста в сумматоры 9; - начальные значения переменной у. (0). В счетчик 39 заносится значение порядка решаемой сисройства; на фиг.2 - схема блока управ-,5 темы (в дополнительном коде), на вход

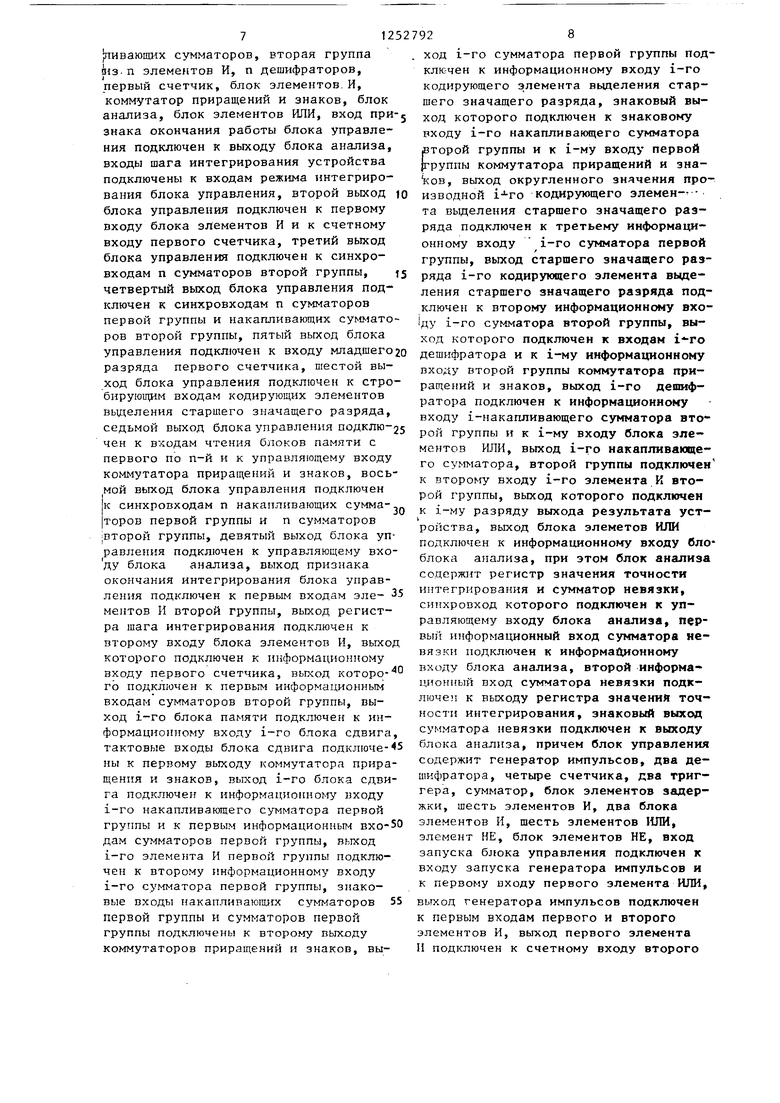

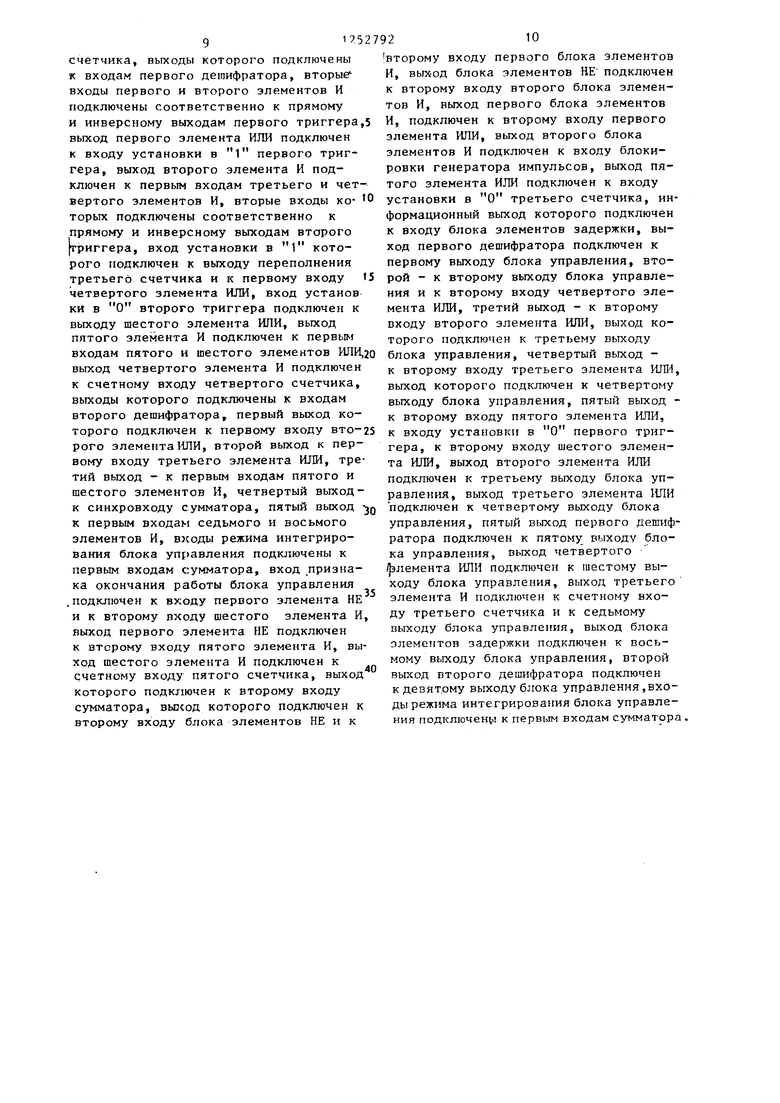

ления на фиг.З - схема блока анализа.

Устройство содержит с первого по Ti-ft блоки 1,- 1 памяти, с первого по ii-й блоки 2|- 2 сдвига, первую группу накапливающих сумматоров 3,- 3, первую группу элементов И 4, - 4 , первую группу сумматоров 5f, , с перво- ;го по п-й кодирующие элементы 6,- 6, выделения старшего значащего разряда, вторую группу сумматоров 7, - 7 , с первого по п-й дешифраторы 8,- 8, вторую группу накапливающих сумматозаноситсяh 2 в

44 подается значение интервала интегрирования. В регистр 13 код шага интегрирования h 2 виде значения номера разряда К, в

20 котором содержится значащая единица. Сумматор 5 и счетчик 11 обнуляются. В качестве начальных условий в регистр 62 блока 16 анализа заносится значение кода заданной точности иско25 мого решения Е. Счетчики 38-41 блока 17 управле шя обнуляются.

Устройство начинает работать при (Поступлении сигнала на вход 18 устройства. Этот сигнал поступает на

ров 9, 9п, вторую группу элементов И 10(- 10, первый счетчик 11, блок 12 элементов И, регистр 13 шага интегрирования, коммутатор 14 приращений и знаков, элемент ИЛИ 15, блок 16 анализа, блок 17 управления, БХОД 18 сигнала начала работы, выходы 19,- 1 . результата устройства, входы 20 шага интегрирования, генератор 21 импульсов, перпый 22, nTopoii 23, тре ти ( 24, четвсрть й 25, пятый 26, шестой 27, седтг,мой 28 и восьмой 29 элементы И, первый 30 и второй 31 дешифраторы, первый 32, второй 33, третий 34, четвертый 35, пятый 36 и шестой 37 элементы ЯПИ, второй 38, третий 39, четвертый 40 и пятый 41 счетчики, первый 42 и второй 43 триггеры, вход 44 режима интегрирования элемент НЕ 45, блок 46 элеме 1тов ПЕ, сумматор 47, блок 48 элементов задержки, пер- 49, второй 50, третий 51, четвер

вый

тый 52, пятый 53, шестой 54, седьмой 55, восьмой 56 и девятый 57 выходы, выход 58 сигнала окончания пите.гри- , вход 59 запуска блока управления, вход 60 признака оконча1П5Я ра- боты блока управления, сумматор 61 невязки, регистр 62 значения точности интегрирования, информационный вход

1252792 2

63, управляющий вход 64, выход 65 блока анализа,

Устройство аботает следующим образом.

Перед началом работы в блоки 1 памяти заносятся соотпетствующие коэффициент: i а;; (i,j 1,n) матрицы А

решаемой системы дифференциальных

уравнений у 3; заносятся

3

В, в сумматоры начальные значения про#. -,-jyj(o).

а в сумматоры 9; - начальные значения переменной у. (0). В счетчик 39 заносится значение порядка решаемой сисизводной У;(0) Ь;+

темы (в дополнительном коде), на вход

заносится h 2 в

44 подается значение интервала интегрирования. В регистр 13 код шага интегрирования h 2 виде значения номера разряда К, в

котором содержится значащая единица. Сумматор 5 и счетчик 11 обнуляются. В качестве начальных условий в регистр 62 блока 16 анализа заносится значение кода заданной точности искомого решения Е. Счетчики 38-41 блока 17 управле шя обнуляются.

Устройство начинает работать при (Поступлении сигнала на вход 18 устройства. Этот сигнал поступает на

вход 59 блока 17 управле1П1я, проходит через элемепт ИЛИ 32, устанавливает триггер 42 в единичное состояние и запускает генератор 21 импульсов, с выхода которого импульсы проходят через элемент И 22, открытый по второму входу от единичлого выхода триггера 42, на вход счетчика 38.

В зависимости от кода в счетчике 38 дсиифратор 30 формирует сигнал на соответствуюигем своем выходе. Так, по первому импульсу генератора 21 дешифратор 30 формируе 1- сигнал на первом своем выходе, который поступает на выход 49 блока 17 и далее на вход группы элементов И 4,. и спнхровход сл Ь)Матора 5, По этому сигналу содержимое сумматора 3; (начальное значение производной у ) заносится в сумматор 5. Затем формируется сигнал на выходе 50, который пройдя через элемент ИЛИ 35, поступает на. выхрд 54 блока 17. По этому сигналу помер разряда К в коде шага интегрирования (h 2) заносится из регистра 13 через группу элементов И 12 в счетчик 11, а кодирующий элемепт 6, выделяет старший значащий разряд в коде производной у и формирует на своем выходе код номе3,1252

pa этого разряда г в соответствии с вьфажением 2 у , где г - минимальное целое число, для которого вьтол- няется это неравенство. В качестве декодирующего элемента 6, можетисполь-5 зоваться микросхема К500ИВ165 (кодирующий элемент с приоритетом). Зняк значения производной у проходит транзитом через кодирующий элемент 6; на его знаковый выход и далее на знако- 10 вый вход ком гутатора 1А и управляющий вход сумматора 9. С третьего выхода дешифратора 30, пройдя через элемент ИЛИ 33, формируется сигнал на третьем выходе 51 блока 17, который поступает15 на синхровход сумматора 7, где происходит сложение кода (К) и кода г. Этот результат (К - г) эквивалентен произведению округленного значения производной у е Z на шаг интегриро-20

о-с i о-Г™-К

вания 2 , так как у п i 2 2 . Код лу 2- с выхода дешифратора 8 поступает на вход сумматора 9 и по сигналу на выходе 52 блока 17 добавляется, с учетом знака 25 на управляющем входе сумматора 9, к начальному значению переменной (0) :

у., У;„(0) .ду; у;„. .

Так вычисляется первое приближение значения искомой переменной на первом шаге интегрирования. Одновременно с этим из содержимого сумматора 5 вычитается округленное значение 2, которое формируется на выходе кодирую- 35 щего элемента, т. е. в сумматоре получается остаток R Уд - 2 . г Сигнал на выходе 53 блока 17 доба- ляет единицу в счетчик 11, в котором получается код К 1, что соответст- 40 вует в значении фор ированию

- 1 кода величины h/2 2 --, Этот .

нал устанавливает триггер 42 в нулевое состояние, по выходным сигналам которого закрывается элемент И 22 и открывается элемент И 23, устанавливается в единичное состояние триггер A3, по выходному сигналу которого открывается элемент И 24 и импульсы с выхода генератора 21 поступают на вход счетчика 39, на выход 55 блока 17 и далее на управляющие входы блоков Ь памяти и коммутатора 14, а через элемент 48 задержки - на выход 56 блока 17 и далее на синхровходы сумматоров 3 и 5. По этим сигналам в течение п тактов производится после-.

7924

допательипе считывание коэффициентов а- из блоков 1; и выдача их на входы блоков 2;, на управляюпше входы которых поступают последовательно с коммутатора 14 коды приращений ft у, , знаки которых коммутатором 14 по зна ковому пходу и иыходу коммутируются на управляющие входы сумматоров 3 и 5. Сдвиг коэффициентов а; на блоках 2 сдвига на (К + 2) разрядов вправо эквивалентен их умножению на приращение йу , а накопление этих результатов в сумматорах 3 и 5 эквивалентло вычислению новых значений произвоидных у- У; + Т а- ьу- и значеFj с 1 J

НИИ приращений производных лу, R;

п + 1-а;|Лу соответственно.

После сложения счетчик 39 вырабатывает сигнал переполнения, который сбрасывает триггер 43 в нулевое состояние, закрывая тем самым прохождение импульсов через элемент И 24 и открывая элемент И 25, с выхода которого сигналы поступают на счетчик 40. Кроме того, сигнал переполнения, про- й,ця через элемент ИЛИ 35 на выход 54 блока 17, разрешает кодирующему элементу 6; выделить и зашифровать старший значащий разряд из кода прираЩчЗ- ния производной ЛУ-, Выделенный номер старшего разряда г складывается с кодом К 1 с выхода счетчика 11 по сигналу на выходе 51, сформированному дешифратором 31 блока 17 управления. Эта операция эквивалентна умножению округленного значения, лу на половину шага h/2, т. е.

h „-( йУ;- -2- - 2

Этот код с выхода дешифратора 8- поступает на вход сумматора 9; и по сигналу на выходе 52, cфopмиpoвaннo ry {дешифратором 31, добавляется с учетом |знака на управляющем входе сумматора 9, к предыдущему значению переменной у. Одновременно с этим из содержимого сумматора 5 вычитается значение вьще- ленного разряда 2 и формируется новый остаток от округления приращения производной.

в этом же такте по сигналу на выходе 57 блока 17 с помощью блока 16 проверяется достижение заданной точности решения на каждом шаге интегрирования Для этого коды приращений &у- с выходов дешифраторов 8( через группу элеJ12

ментов ИЛИ 15 поступают на входы сумматора 61 блока 16, на котором из сформированного максимального кода приращения лу вычитается код заданно точности (Е) из регистра 62 и знак ре зультата выдается на выход 65 блока 16 и далее на вход 60 блока 17, где он открывает элемент И 27 (если знак отрицательный, т. е. удовлетворяется заданная точность лу„д,45. Е) или че- рез элемент НЕ 45 элемент И 26 (если

- Е). В последнем случае сигнал с выхода элемента И 26 устанавливает триггер 43 в единичное состояние, тем

самым переключая выходные сигналы ге- t5 числений по интерполяционной формуле.

35

нератора 21 через элемент И 24 на вход счетчика 39 и на выход 55 блока 17.

Затем аналогично описанному произ- ло;имел вычисление последующих значений приращения переменных йу и прира- 20 щеиия производньтх ау . Если удовлетворяется заданная точность, то сигнал с третьего выхода деши Фатора 31 блока 17 проходит через элемент И 27 на вход счетчика А1, добавляя к его со- 5 дсржимому единицу, В 1 оследуюЕ;ем такте на сумматоре 47 осуществляется вычитание из содержиг ого счетчика А1 (в котором формируется текущее значение количсстиа обработанных шагов ни-зо тегрировапия п; .решаемой системы уравнений) кода заданного числа шагов nij. Знак результата этого вычитания поступает на вход.элемента И 28 или через блок 46 ita вход элемента 11 29. Если разность т,, отрицательна, т. е. еще не закончено интегрирование системы уравнений, сигнал с выхода де-- 111И 1:ратора 3 проходит через элемент И 28 и далее через злемсчгг ИЛ1Т 32 нп. вход триггера 42, устанавливая его и единичное состояние, и тем самым создаются условия для продолжения интег-, рирова1п-1Я на следующем шаге.

Если разность пц- nij положительна,- 5 т. е, интегрированир. на заданном интервале закончено, то открывается элемент И 29 и сигнал поступает на выход 58 блока 17 и далее на входы группы элементов И 10 , через которые О результат решения выдается на выходы 19; устройства, а генератор 21 импульсов прекращает свою работу. j На 1;ажд ом (С + 1)-м таге интегри- рован1 я в ycTpoiicTBe в течение первых55 шести тактов находится первое приближение к решению по экстраполяциокной формуле

40

На каждом шаге может выполняться максимум го, а - одна итерация по интерполяционной формуле (при мо- делшровании максимум не вышел 4 итераций для ш 16) ив среднем требуется не бопее т/2 итераций. Время решения задачи интегрирования системы линейных дифференциальных уравнений при ti 100, m 24; J 10 с в устройстве определяется так:

.

где Т m

/-

6 + (п + 3)-|- + з..Т 5 с, период тактовых импульсов.

количество шагов для единичного интервала.

Ф

о р м.у л а

изобретения

Устройство для решения систем линейных дифференциальных уравнений, содержащее первую группу из п накап- ливл1оп,нх сумматоров (где п - порядок решаемой системы уравнений), первую группу из п элемерггов II, первый коди- руюши1г элемент выделения старшего значащего разряда, п блоков памяти, блок управления, выход i-ro накапливающего сумматора (, ... , п) первой группы подключеп к первому лходу i-ro элемепта И первой группы, второй вход i-ro элемепта И первой группы подключеп к первому выходу блока управления, вход признака начала работы устройства подключен к входу запуска блока управления, о т- л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в )ie- го введены первая группа из п сумматоров, (п-1) кодирующих элементов выделения старшего значащего разряда, п блоков сдвига, вторая группа из п :сумматоров, вторая группа из п накап, , I J П-(К « Л

у;ен У;в У;Е

причем производится округление приращения ду л Ьу я с точностью до старшего значащего разряда, а затем в последующие (п 3) такта, повторенные несколько раз, чтобы удовлетворить заданной точности, производится уточнение решения по интерполяционной формуле

-h-i 2 а,.у-,2--Ч

причем остаток от округления R используется на следующей итерации пыНа каждом шаге может выполняться максимум го, а - одна итерация по интерполяционной формуле (при мо- делшровании максимум не вышел 4 итераций для ш 16) ив среднем требуется не бопее т/2 итераций. Время решения задачи интегрирования системы линейных дифференциальных уравнений при ti 100, m 24; J 10 с в устройстве определяется так:

.

где Т m

/-

6 + (п + 3)-|- + з..Т 5 с, период тактовых импульсов.

количество шагов для единичного интервала.

Ф

о р м.у л а

изобретения

Устройство для решения систем линейных дифференциальных уравнений, содержащее первую группу из п накап- ливл1оп,нх сумматоров (где п - порядок решаемой системы уравнений), первую группу из п элемерггов II, первый коди- руюши1г элемент выделения старшего значащего разряда, п блоков памяти, блок управления, выход i-ro накапливающего сумматора (, ... , п) первой группы подключеп к первому лходу i-ro элемепта И первой группы, второй вход i-ro элемепта И первой группы подключеп к первому выходу блока управления, вход признака начала работы устройства подключен к входу запуска блока управления, о т- л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в )ie- го введены первая группа из п сумматоров, (п-1) кодирующих элементов выделения старшего значащего разряда, п блоков сдвига, вторая группа из п :сумматоров, вторая группа из п накапуливающих сумматоров, вторая группа П13. п элементов И, п дешифраторов, первый счетчик, блок элементов. И, коммутатор приращений и знаков, блок анализа, блок элементов ИЛИ, вход при-д знака окончания работы блока управления подключен к выходу блока анализа, входы шага интегрирования устройства подключены к входам режима интегрирования блока управления, второй выход ю блока управления подключен к первому входу блока элементов И и к счетному входу первого счетчика, третий выход блока управления подключен к синхро- входам п сумматоров второй группы, 55 четвертый выход блока управления подключен к синхровходам п сумматоров первой группы и накапливающих сумматоров второй группы, пятый выход блока управления подключен к входу младшего2о разряда первого счетчика, шестой выход блока управления подключен к стро- бирующим входам кодирующих элементов выделения старшего значащего разряда, седьмой выход блока управления подклю-25 чен к входам чтения блоков памяти с первого по п-й и к управляющему входу коммутатора приращений и знаков, восьмой выход блока управления подключен к синхровходам п накапливающих сумма-, торов первой группы и п сумматоров |второй группы, девятый выход блока управления подключен к управляющему входу блока анализа, выход признака окончания интегрирования блока управления подключен к первым входам эле- 35 ментов И второй группы, выход регистра шага интегрирования подключен к второму входу блока элементов И, выход которого подключен к И1 формационному входу первого счетчика, 1зыход которо- го подключен к первым информационным входам сумматоров второй группы, выход i-ro блока памяти подключен к информационному входу i-ro блока сдвига, тактовые входы блока сдвига подключе- 5 ны к первому выходу коммутатора приращения и знаков, выход i-ro блока сдвига подключен к инфopмaциoннo гy входу 1-го накапливающего сумматора первой группы и к первым информационным вхо-50 дам сумматоров первой группы, выход i-ro элемента И первой группы подключен к второму информационному входу i-ro сумматора первой группы, знаковые входы накапливающих сумматоров 55 первой группы и сумматоров первой группы подключены к второму выходу

коммутаторов приращений и знаков, вы- И подключен к счетному входу второго

ход 1-го сумматора первой группы подключен к информационному входу i-ro кодирующего элемента выделения старшего значащего разряда, знаковый выход которого подключен к знаковому входу i-ro накапливающего сумматора .второй группы и к i-му входу первой {группы коммутатора приращений и зна- koB, выход округленного значения производной кодирующего элемен--- та вьщеления старшего значащего разряда подключен к третьему информационному входу i-ro сумматора первой группы, выход старшего значащего разряда i-ro кодирующего элемента выделения старшего значащего разряда подключен к второму информационному вхо- 1ду i-ro сумматора второй группы, выход которого подключен к входам дешифратора и к 1-му информационному входу второй группы коммутатора приращений и знаков, выход i-ro дешифратора подключен к информационному входу i-накапливающего сумматора второй группы и к i-му входу блока элементов ИЛИ, выход i-ro накапливающего сумматора, второй группы подключен к втopo iy входу i-ro элемента К второй группы, выход которого подключен к i-му разряду выхода результата устройства, выход блока элеметов ИЛИ полтключен к информационному входу бло блока анализа, при этом блок анализа содержит регистр значения точности интегрирования и сумматор невязки, сипхровход которого подключен к управляющему входу блока анализа, первый информационный вход сумматора невязки подключен к информа Хионному входу блока анализа, второй информационный вход сумматора невязки подключен к выходу регистра значения точности интегрирования, знаковый выход сумматора невязки подключен к выходу блока анализа, причем блок управления содержит генератор импульсов, два дешифратора, четыре счетчика, два триггера, сумматор, блок элементов задержки, шесть элементов И, два блока элементов И, шесть элементов 11ПИ, элемент НЕ, блок элементов НЕ, вход запуска блока управления подключен к входу запуска генератора импульсов и к первому входу первого элемента ИЛИ,

выход генератора импульсов подключен к первым входам первого и второго элементов И, выход первого элемента

li

k

счетчика, выходы которого подключены к входам первого дешифратора, вторые входы первого и второго элементов И подключены соответственно к прямому и инверсному выходам первого триггера,5 выход первого элемента ИЛИ подключен к входу установки в 1 первого триггера, выход второго элемента И подключен к первым входам третьего и четвертого элементов И, вторые входы ко- О торьгх подключены соответственно к прямому и инверсному выходам второго риггера, вход установки в 1 которого подключен к вьгходу переполнения третьего счетчика и к первому входу 5 четвертого элемента ИЛИ, вход установ ки в О второго триггера подключен к выходу шестого элемента ИЛИ, выход пятого элемента И подключен к первым входам пятого и шестого элементов 1 ШИ,2о выход четвертого элемента И подключен к счетному входу четвертого счетчика, выходы которого подключены к входам второго дешифратора, первый выход которого подключен к первому входу вто-25 рого элемента ИЛИ, второй выход к первому входу третьего элемента ИЛИ, третий выход - к первым входам пятого и шестого элементов И, четвертый выход второму входу первого блока элементо И, выход блока элементов НЕ подключе к второму входу второго блока элемен тов И, выход первого блока элементов И, подключен к второму входу первого элемента ИЛИ, выход второго блока элементов И подключен к входу блокировки генератора импульсов, выход пя того элемента ИЛИ подключен к входу установки в О третьего счетчика, и формационный выход которого подключе к входу блока элементов задержки, вы ход первого дешифратора подключен к первому вьгходу блока управления, вто рой - к второму вьгходу блока управле ния и к второму входу четвертого эле мента ИЛИ, третий выход - к второму входу второго элемента ИЖ, выход ко торого подключен к третьему выходу блока управления, четвертый выход - к второму входу третьего элемента ИЛ выход которого подключен к четвертом выходу блока управления, пятый выход к второму входу пятого элемента ИЛИ, к входу установки в О первого триг гера, к второму входу шестого элемен та ИЛИ, выход второго элемента ИЛИ подключен к третьему вьгходу блока уп равления, выход третьего элемента ИЛ

к синхровходу сумматора, пятый выход --JQ подключен к четвертому выходу блока

к первым входам седьмого и восьмого элементов И, входы режима интегрирования блока управления подключены к первым входам сумматора, вход .приэна- ка окончания работы блока управления .подключен к входу первого элемента НЕ и к второму входу шестого элемента И, выход первого элемента НЕ подключен к второму входу пятого элемента И, выход шестого элемента И подключен к счетному входу пятого счетчика, выход Которого подключен к второму входу сумматора, вызсод которого подключен к второму входу блока элементов НЕ и к

второму входу первого блока элементов И, выход блока элементов НЕ подключен к второму входу второго блока элементов И, выход первого блока элементов И, подключен к второму входу первого элемента ИЛИ, выход второго блока элементов И подключен к входу блокировки генератора импульсов, выход пятого элемента ИЛИ подключен к входу установки в О третьего счетчика, информационный выход которого подключен к входу блока элементов задержки, выход первого дешифратора подключен к первому вьгходу блока управления, второй - к второму вьгходу блока управле-- ния и к второму входу четвертого элемента ИЛИ, третий выход - к второму входу второго элемента ИЖ, выход которого подключен к третьему выходу блока управления, четвертый выход - к второму входу третьего элемента ИЛИ выход которого подключен к четвертому выходу блока управления, пятый выход к второму входу пятого элемента ИЛИ, к входу установки в О первого триггера, к второму входу шестого элемента ИЛИ, выход второго элемента ИЛИ подключен к третьему вьгходу блока управления, выход третьего элемента ИЛИ

подключен к четвертому выходу блока

управления, пятый первого дешифратора подключен к пятому выходу блока управления, выход четвертого лемента ИЛИ подключен к шестому выходу блока управления, выход третьего элемента И подключен к счетному входу третьего счетчика и к седьмому вьгходу блока управления, выход блока элементов задержки подключен к восьмому выходу блока управления, второй выход второго дешифратора подключен к девятому выходу блока управления,входы режима интегрирования блока управления подключен. к первым входам сут-1матора.

:

к

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем линейных дифференциальных уравнений | 1988 |

|

SU1525714A2 |

| Устройство для решения интегральных уравнений Фредгольма второго порядка | 1985 |

|

SU1295413A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

| Вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1605253A1 |

| Генератор функций | 1990 |

|

SU1758641A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для извлечения квадратного корня | 1979 |

|

SU857982A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1981 |

|

SU1005087A1 |

Изобретение относится к области вычислительной техники и может быть исполь-зовано при построении цифровых интегрирующих машин и специализирован- нь(х процессоров, предназначенных для решения систем линейных дифференциальных уравнений вида у Ац В, где А и В - матрица и вектор коэффициентов соответственно. Цель изобретения - увеличение быстродействия устройства. Устройство содержит п блоков памяти, п блоков сдвига, п сумматоров, п накапливающих сумматоров, блок управления, счетчик, группы элементов И, регистр, коммутатор, блок анализа, элемент ИЛИ, п кодирующих элементов. Увеличение быстродействия устройства обеспечивается за счет совмещения процессов нахождения очередного разряда и инерционного процесса поиска решения. При п ТОО, m 24, У 10 с время интегрирования системы уравнений устройством составит порядка 5 с, где 7 - период тактовых импульсов, п - порядок системы урав- нений, m - число шагов интегрироваиня. 3 ил. 3 сл

65 Кбл.П

Редактор В.Петраш

Составитель В.Смирнов

Техред И.Верес Корректор С.Черни

Заказ 4622/50Тираж 671Подписное

ВНИИ1ТИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для решения систем дифференциальных уравнений | 1975 |

|

SU596952A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Воронов А.А | |||

| и др | |||

| Цифровые аналоги для систем автоматического управле - ПИЯ.- М.: Изд-во АН СССР, 1960 | |||

| Майоров Ф.М | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-08-23—Публикация

1985-02-22—Подача