Изобретение относится к вычислительной технике и может быть использовано в качестве устройства буферной памяти.

Целью изобретения является повышение достоверности за счет аппаратного разделения во времени совпадающих команд записи и чтения.

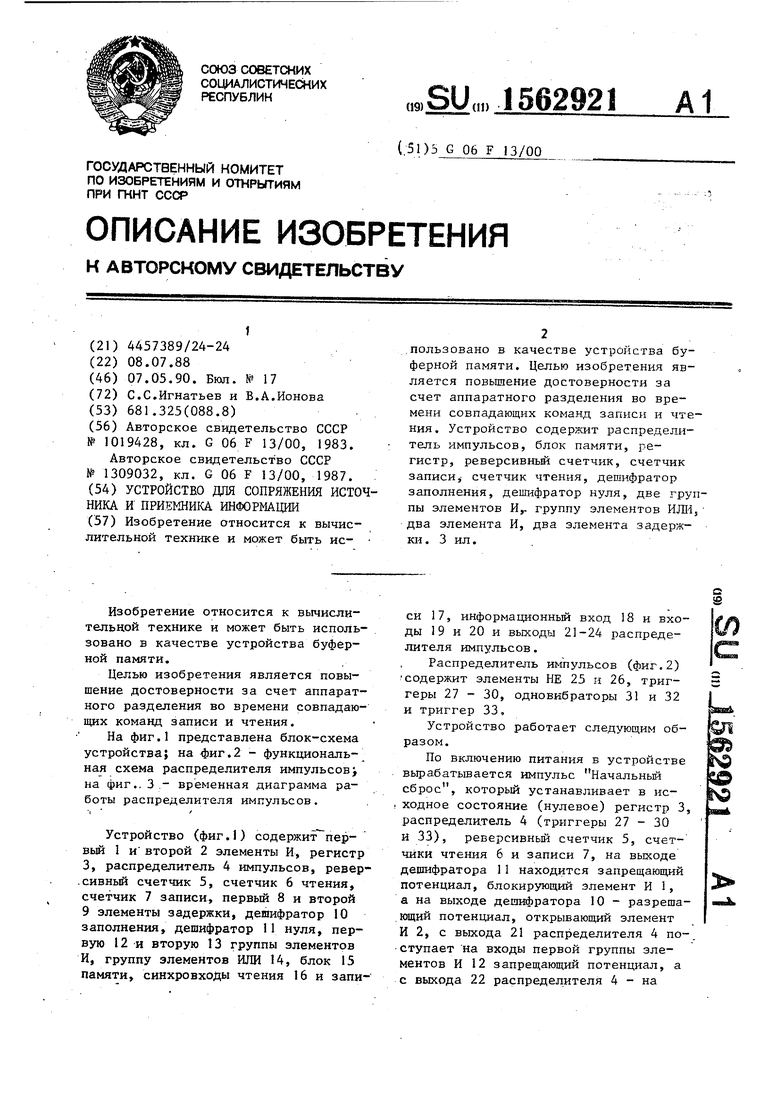

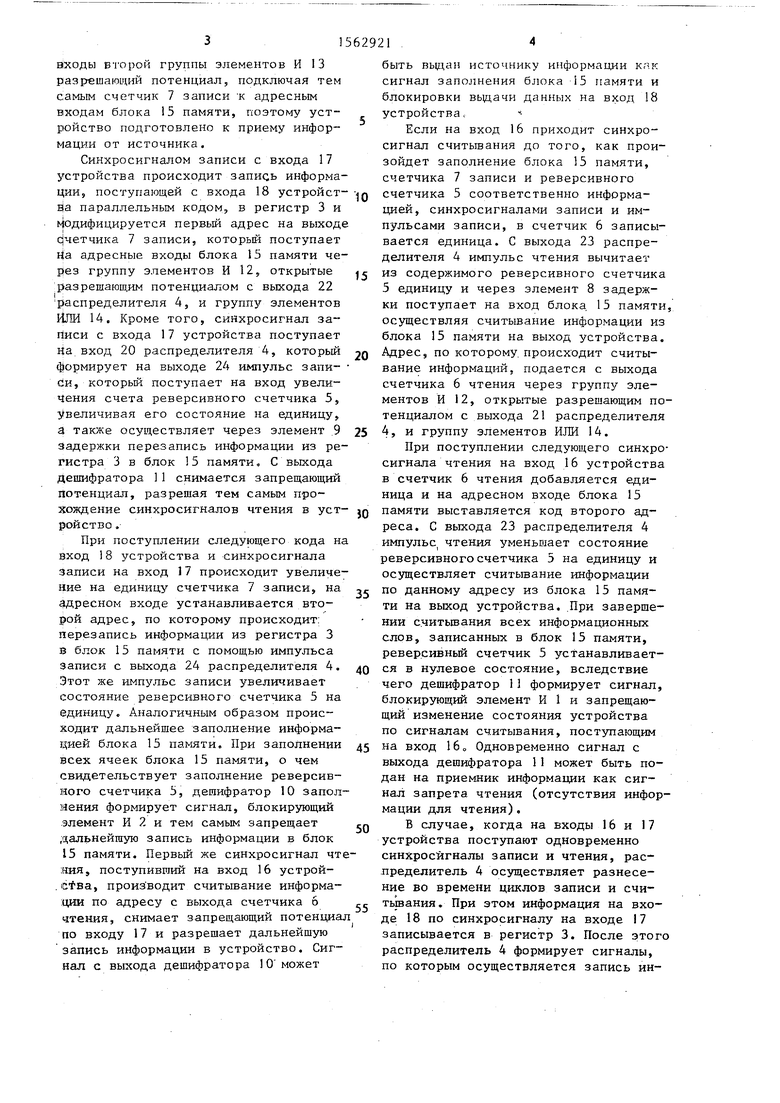

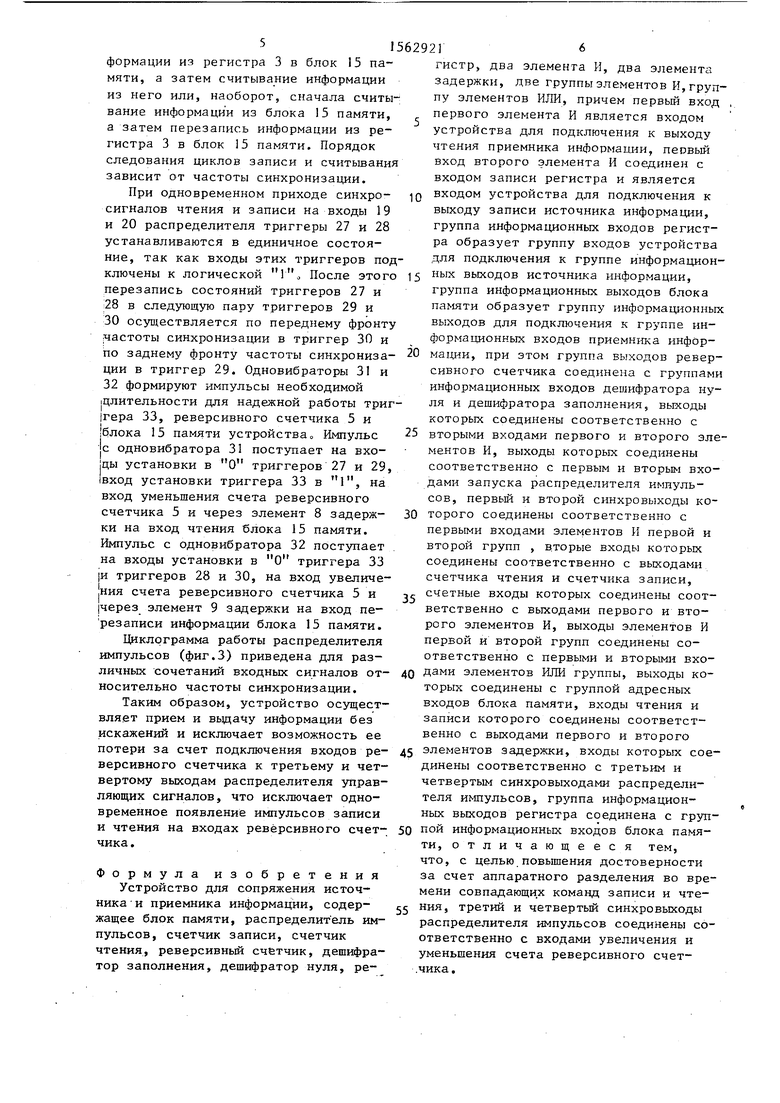

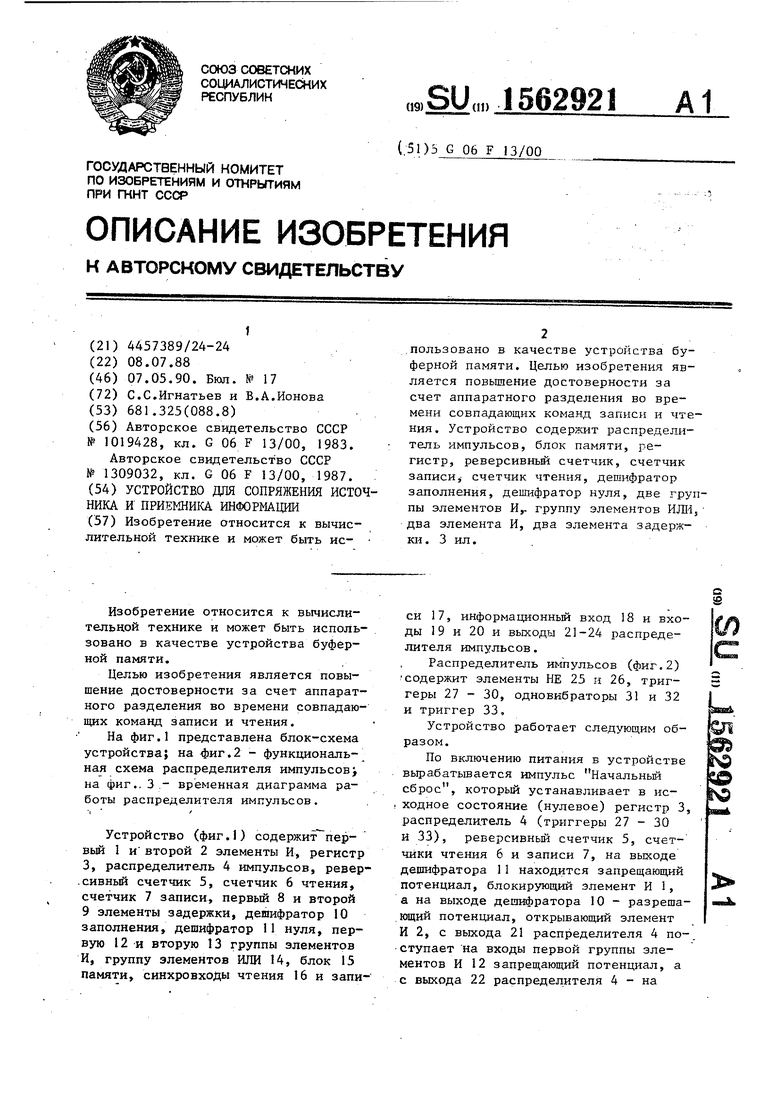

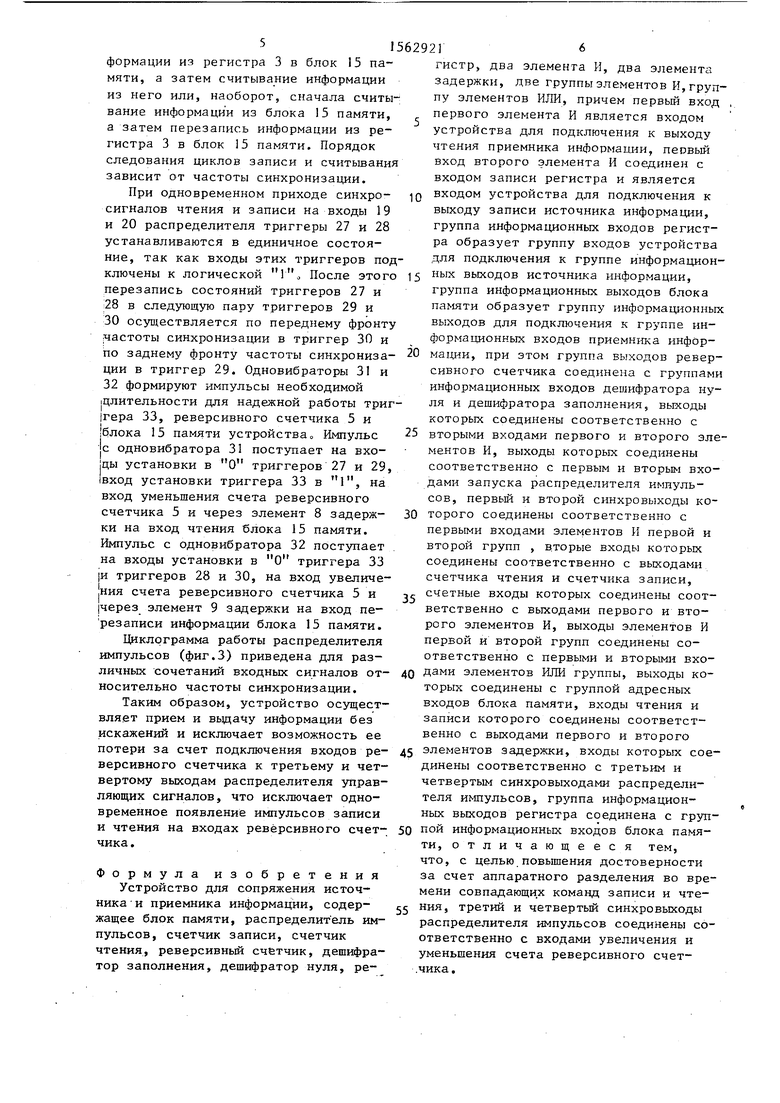

На фиг.1 представлена блок-схема устройства; на фиг.2 - функциональная схема распределителя импульсов на фиг. 3 - временная диаграмма работы распределителя импульсов.

Устройство (фиг.1) содержит пер- вый 1 и второй 2 элементы И, регистр 3, распределитель 4 импульсов, реверсивный счетчик 5, счетчик 6 чтения, счетчик 7 записи, первый 8 и второй 9 элементы задержки, дешифратор 10 заполнения, дешифратор 11 нуля, первую 12 и вторую 13 группы элементов И, группу элементов ИЛИ 14, блок 15 памяти, синхровходы чтения 16 и записи 17, информационный вход 18 и входы 19 и 20 и выходи 21-24 распределителя импульсов.

Распределитель импульсов (фиг.2) содержит элементы НЕ 25 ч 26, триггеры 27 - 30, одновкбраторы 31 и 32 и триггер 33.

Устройство работает следующим образом.

По включению питания в устройстве вырабатывается импульс Начальный сброс, который устанавливает в исходное состояние (нулевое) регистр 3, распределитель 4 (триггеры 27 - 30 и 33), реверсивньй счетчик 5, счетчики чтения 6 и записи 7, на выходе дешифратора 11 находится запрещающий потенциал, блокирующий элемент И 1, а на выходе дешифратора 10 - разрешающий потенциал, открывающий элемент И 2, с выхода 21 распределителя 4 поступает на входы первой группы элементов И 12 запрещающий потенциал, а с выхода 22 распределителя 4 - на

Г

ю

10

15

20

25

входы второй группы элементов И 13 разрешающий потенциал, подключая тем самым счетчик 7 записи к адресным входам блока 15 памяти, поэтому устройство подготовлено к приему информации от источника.

Синхросигналом записи с входа 17 устройства происходит запись информации, поступающей с входа 18 устройст- йа параллельным кодом, в регистр 3 и модифицируется первый адрес на выходе фчетчика 7 записи, который поступает rta адресные входы блока 15 памяти через группу элементов И 12, открытые

разрешающим потенциалом с выхода 22 i,

распределителя 4, и группу элементов

ИЛИ 14. Кроме того, синхросигнал записи с входа 17 устройства поступает На вход 20 распределителя 4, который формирует на выходе 24 импульс запи- си, который поступает на вход увеличения счета реверсивного счетчика 5, Увеличивая его состояние на единицу, а также осуществляет через элемент 9 задержки перезапись информации из регистра 3 в блок 15 памяти. С выхода дешифратора 11 снимается запрещающий Потенциал, разрешая тем самым прохождение синхросигналов чтения в устройство .

При поступлении следующего кода на вход 18 устройства и синхросигнала Записи на вход 17 происходит увеличение на единицу счетчика 7 записи, на адресном входе устанавливается второй адрес, по которому происходит перезапись информации из регистра 3 в блок 15 памяти с помощью импульса Записи с выхода 24 распределителя 4. Этот же импульс записи увеличивает состояние реверсивного счетчика 5 на единицу. Аналогичным образом происходит дальнейшее заполнение информацией блока 15 памяти. При заполнении всех ячеек блока 15 памяти, о чем свидетельствует заполнение реверсивного счетчика 5, дешифратор 10 заполнения формирует сигнал, блокирующий элемент И 2 и тем самым запрещает дальнейшую запись информации в блок 15 памяти. Первый же синхросигнал чтения, поступивший на вход 16 устройства, производит считывание информации по адресу с выхода счетчика 6 ,-с чтения, снимает запрещающий потенциал по входу 17 и разрешает дальнейшую запись информации в устройство. Сигнал с выхода дешифратора 10 может

5629214

быть выдан источнику информации кяк сигнал заполнения блока 15 памяти и блокировки выдачи данных на вход 18 устройства.

Если на вход 16 приходит синхросигнал считывания до того, как произойдет заполнение блока 15 памяти, счетчика 7 записи и реверсивного счетчика 5 соответственно информацией, синхросигналами записи и импульсами записи, в счетчик 6 записывается единица. С выхода 23 распределителя 4 импульс чтения вычитает из содержимого реверсивного счетчика 5 единицу и через элемент 8 задержки поступает на вход блока 15 памяти, осуществляя считывание информации из блока 15 памяти на выход устройства. Адрес, по которому происходит считывание информации, подается с выхода счетчика 6 чтения через группу элементов И 12, открытые разрешающим потенциалом с выхода 21 распределителя 4, и группу элементов ИЛИ 14.

При поступлении следующего синхросигнала чтения на вход 16 устройства в счетчик 6 чтения добавляется единица и на адресном входе блока 15 памяти выставляется код второго яд- реса. С выхода 23 распределителя 4 импульс чтения уменьшает состояние реверсивного счетчика 5 на единицу и осуществляет считывание информации по данному адресу из блока 15 памяти на выход устройства. При завершении считывания всех информационных

Ю

35

40

45

50

слов, записанных в блок 15 памяти, реверсивный счетчик 5 устанавливается в нулевое состояние, вследствие чего дешифратор 13 формирует сигнал, блокирующий элемент И 1 и запрещающий изменение состояния устройства по сигналам считывания, поступающим на вход 160 Одновременно сигнал с выхода дешифратора 11 может быть подан на приемник информации как сигнал запрета чтения (отсутствия информации для чтения).

В случае, когда на входы 16 и 17 устройства поступают одновременно синхросигналы записи и чтения, распределитель 4 осуществляет разнесение во времени циклов записи и счи- ть шания. При этом информация на входе 18 по синхросигналу на входе I7 записывается в регистр 3. После этого распределитель 4 формирует сигналы, по которым осуществляется запись инс

0

5

0

слов, записанных в блок 15 памяти, реверсивный счетчик 5 устанавливается в нулевое состояние, вследствие чего дешифратор 13 формирует сигнал, блокирующий элемент И 1 и запрещающий изменение состояния устройства по сигналам считывания, поступающим на вход 160 Одновременно сигнал с выхода дешифратора 11 может быть подан на приемник информации как сигнал запрета чтения (отсутствия информации для чтения).

В случае, когда на входы 16 и 17 устройства поступают одновременно синхросигналы записи и чтения, распределитель 4 осуществляет разнесение во времени циклов записи и счи- ть шания. При этом информация на входе 18 по синхросигналу на входе I7 записывается в регистр 3. После этого распределитель 4 формирует сигналы, по которым осуществляется запись информации из регистра 3 в блок 15 памяти, а затем считывание информации из него или, наоборот, сначала считывание информации из блока 15 памяти, а затем перезапись информации из регистра 3 в блок 15 памяти. Порядок следования циклов записи и считывания зависит от частоты синхронизации.

При одновременном приходе синхросигналов чтения и записи на входы 19 и 20 распределителя триггеры 27 и 28 устанавливаются в единичное состояние, так как входы этих триггеров подключены к логической После этого перезапись состояний триггеров 27 и 28 в следующую пару триггеров 29 и 30 осуществляется по переднему фронту частоты синхронизации в триггер 30 и по заднему фронту частоты синхронизации в триггер 29. Одновибраторы 31 и 32 формируют импульсы необходимой длительности для надежной работы триг irepa 33, реверсивного счетчика 5 и , блока 15 памяти устройства Импульс с одновибратора 31 поступает на входы установки в О триггеров 27 и 29, вход установки триггера 33 в 1, на вход уменьшения счета реверсивного счетчика 5 и через элемент 8 задержки на вход чтения блока 15 памяти. Импульс с одновибратора 32 поступает на входы установки в О триггера 33 |и триггеров 28 и 30, на вход увеличе

ния счета реверсивного счетчика 5 и |через элемент 9 задержки на вход перезаписи информации блока 15 памяти.

Циклограмма работы распределителя импульсов (фиг.З) приведена для различных сочетаний входных сигналов относительно частоты синхронизации.

Таким образом, устройство осуществляет прием и выдачу информации без искажений и исключает возможность ее потери за счет подключения входов реверсивного счетчика к третьему и четвертому выходам распределителя управляющих сигналов, что исключает одновременное появление импульсов записи и чтения на входах реверсивного счетчика.

Формула изобретения

Устройство для сопряжения источника и приемника информации, содержащее блок памяти, распределитель импульсов, счетчик записи, счетчик чтения, реверсивный СЧЁТЧИК, дешифратор заполнения, дешифратор нуля, ре

0

5

5

гистр, два элемента И, два элемента задержки, две группы элементов И, группу элементов ИЛИ, причем первый вход , первого элемента И является входом устройства для подключения к выходу чтения приемника информации, первый вход второго элемента И соединен с входом записи регистра и является Q входом устройства для подключения к выходу записи источника информации, группа информационных входов регистра образует группу входов устройства для подключения к группе информацион- 5 ных выходов источника информации, группа информационных выходов блока памяти образует группу информационных выходов для подключения к группе информационных входов приемника инфор- 0 мации, при этом группа выходов реверсивного счетчика соединена с группами информационных входов дешифратора нуля и дешифратора заполнения5 выходы которых соединены соответственно с 5 вторыми входами первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами запуска распределителя импульсов, первьй и второй синхровыходы ко- 0 торого соединены соответственно с первыми входами элементов И первой и второй групп , вторые входы которых соединены соответственно с выходами счетчика чтения и счетчика записи, счетные входы которых соединены соответственно с выходами первого и второго элементов И, выходы элементов И первой и второй групп соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, выходы которых соединены с группой адресных входов блока памяти, входы чтения и записи которого соединены соответственно с выходами первого и второго элементов задержки, входы которых соединены соответственно с третьим и четвертым синхровыходами распределителя импульсов, группа информационных выходов регистра соединена с груп- 0 пой информационных входов блока памяти, отличающееся тем, что, с целью повышения достоверности за счет аппаратного разделения во времени совпадающих команд записи и чте- 5 ния, третий и четвертый синхровыходы распределителя импульсов соединены соответственно с входами увеличения и уменьшения счета реверсивного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1278869A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1401471A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1309032A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1986 |

|

SU1396147A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1982 |

|

SU1072036A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для сопряжения двух вычислительных машин | 1979 |

|

SU885988A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства буферной памяти. Целью изобретения является повышение достоверности за счет аппаратного разделения во времени совпадающих команд записи и чтения. Устройство содержит распределитель импульсов, блок памяти, регистр, реверсивный счетчик, счетчик записи, счетчик чтения, дешифратор заполнения, дешифратор нуля, две группы элементов И, группу элементов ИЛИ, два элемента И, два элемента задержки. 3 ил.

| Устройство сопряжения | 1982 |

|

SU1019428A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1309032A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-07—Публикация

1988-07-08—Подача