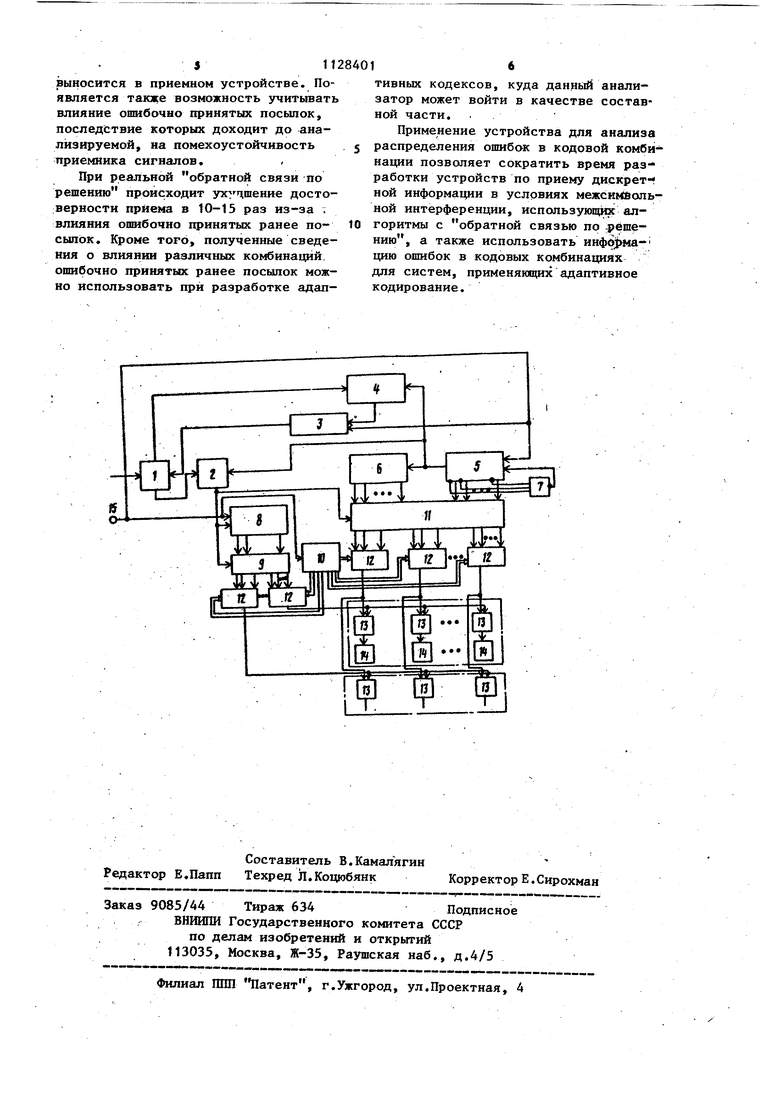

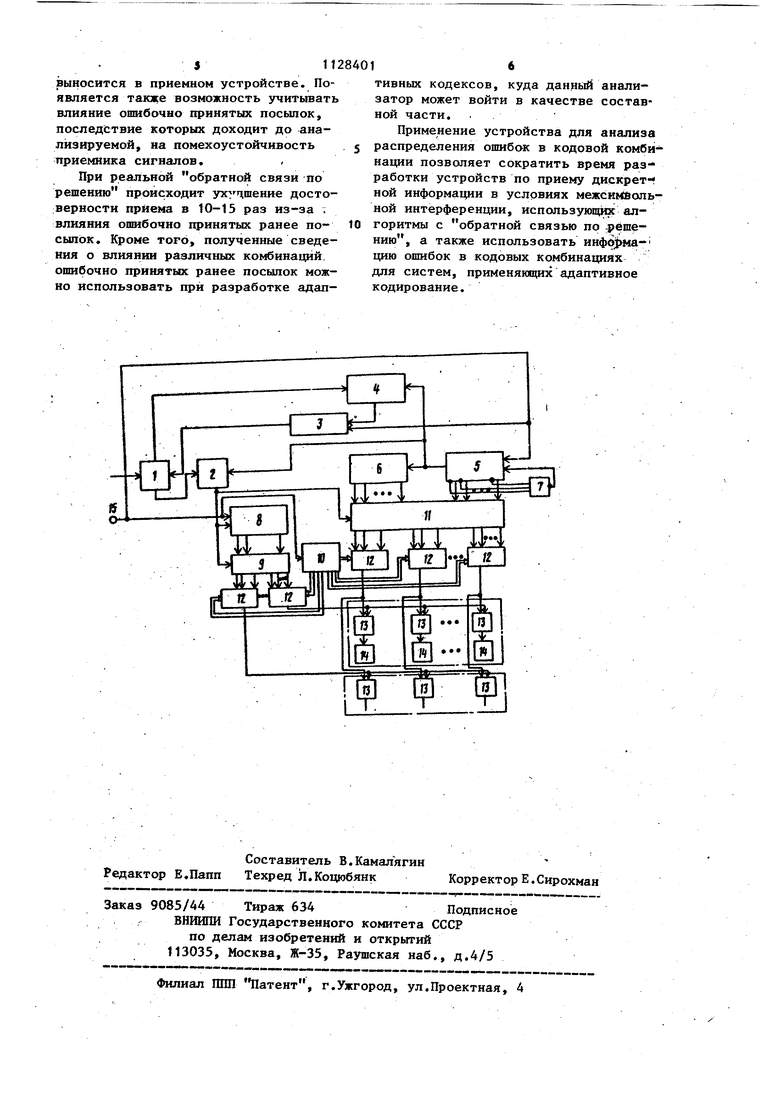

Устройство относится к технике измерений и контроля каналов связи при передаче бинарной информации,, при разработке, наладке и испытаниях устройств обработки дискретной информации с (Использованием обратной связипо решению. Известно устройство выявления ошибок, содержащее соединенные соответствующим образом .между собой гене ратор псевдослучайной последовательности, блок сравнения, блок синхрони зации и блок индикации ошибочной ком бинации Cl Недостатком известного устройства является малое быстродействие, поскольку оно блокируется при каждой ошибке. Это устройство, кроме того, не позволяет обнаружить ошибки, возникакицие из-за межсимвольной интерференции принятых ранее посыпок и оказывающих влияние на анализируемую посыпку. Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство дл анализа распределения ошибок в кодовой комбинации, содержащее блок согласования , выход которого подключен к первому входу блока сравнения, второй вход которого соединен с выходом датчика испытательного текста, прямые выходы разрядов которого подключены к первым информационным входам дешифратора кодовых комбинаций, управляющий вход которого сое-, динен с выходом блока сравнения, и счетчики С 2}. Однако известное устройство анализирует межсимвольную интерференцию только от предьщущей посыпки и не учитывает межсимвольную интерференци от более ранних посылок, знергия которых присутствует в интервале анализируемой посылки. Цель изобретения - повьш1ение точности анализа распределения ошибок, появляющихся при работе по каналам с межсимвольной интерференцией приемников, использующих обратную связь по решению.. Поставленная цепь достигается тем что в устройство для анализа распределения ошибок в кодовой комбинации, содержащее блок согласования, выход которого подключен к первому входу блока сравнения, второй вход которого соединен с выходом датчика испыта тельного текста, прямые выходы разрядов которого подключены к первым информационным входам дешифратора кодовых комбинаций, управляющий вход которого соединен с выходом блока сравнения, и счетчики, введены линия задержки, регистр сдвига, две группы многовходовьгх коммутаторов, буферный регистр, формирователь управляющих сигналов, дешифратор ошибочных комбинаций, двухвходовые элементы совпадения И, многовходовый элемент И-НЕ, при этом выход датчика испытательного текста подключен к первому входу блока синхронизации и к входу буферного, регистра, выходы разрядов которого подключены к вторым информационным входам дешифратора кодовых комбинаций, выходы которого подключены к соответствующим входам первой группы многовходовых коммутаторов, управляющие входы которых соединены с соответствующими выходами формирователя управляющих сигналов, вход которого соединен с управляющим входом регистра сдвига, с тактовым входом устрой- СТВ& для анализа распределения ошибок в кодовой комбинации, с первым входом линии задержки и с тактовым входрм датчика испытательного, текста, установочный вход которого, соединен с выходом многовходового элемента И-НЕ, входы которого соединены с инверсными выходами разрядов, датчика испытательного текста, при этом выход блока сравнения подключен к информационному входу регистра сдвига и к управляющему входу дешифратора ошибоч- ных комбинаций, выходы которого подключены к соответствующим входам второй группы многовходовых коммутаторов, управляющие входы которых соединены с соответствующими выходами формирователя управляющих сигналов, а выходы всех многовходовых коммута- , торов соединены с первыми входами соответствующих двухвходовых элементов совпадения И, вторые входы которьк соединены с соответствующими вьгхо. дами первой группы многовходовых коммутаторов, а выходы подключены к счетчикам, при этом выход линии задержки подключен к управляющему входу блока согласования, второй выход которого подключен к второму входу блока синхронизации, выход которого соединен с вторым входом линии задержки. . На чертеже представлена структурная электрическая схема устройства для анализа распределения ошибок в кодовой комбинации. Устройство для анализа распределения ошибок в кодовой комбинации содержит блок 1 согласования, блок 2 сравнения, линию 3 задержки, блок 4 синхронизации, датчик 5 испытатель ного текста, буферный регистр 6, мно говходовый элемент И-НЕ 7, регистр 8 сдвига, дешифратор 9 ошибочнмх комби наций, формирователь 10 управляющих сигналов, дешифратор 11 кодовых комбинаций, многовходовые коммутаторы 12, двухвходовые элементы совпаде- ния И 13, счетчики 14, тактовый вход 15. Устройство работает следующим образом. Двоичная информация на первый .вход блока1 согласования, затем с второго выхода блoka 1 она поступает на второй вход блока 4 синхронизации, на первый вход которо го поступает сигнал с выхода датчика 5 испытательного текста. После установления синхронизма сигнал с выхода блока 4 синхронизации через линию задержки 3, длина которой равна длине буферного регистра 6 и выбирается, равной числу перекрываемых посылок п , поступает на управляющий вход блока 1, которьй переключает поступающую двоичную информацию на первый вход блока 2 сравнения.На второй вход блока 2 сравнения.поступает двоичный сигнал с выхода датчика. испытательного текста 5, и этот же сигнал поступает на вход буферного регистра 6. . Выходы буферного регистра 6 и дат чика 5 испытательного текста заведены на информационные входы дешифрато ра 11 кодовых комбинаций. Количество выходов разрядов датчика 5 испытательного текста равно числу посыпок m , попадаемых в интервал анализа. Сигнал с выхода блока 2 сравнения по ступает на информационный вход регис тра 8 сдвига, в котором продвигается с помощью тактовых импульсов, поступающих на тактовый вход15 и.следующих со скоростью информационных поcbutoK. Кроме того, тактовые импульсы заводятся на тактовый вход датчика 5 испытательного текста и на вход ормирователя 10 управляющих сигналов. Выходы разрядов регистра 8 сдвига, длина которого равна длине буферного регистра 6, заводятся на вход дешифратора 9 ошибочных комбинаций. С помощью дешифратора 9 ошибочных .комбинаций определяется влияние на принятие неправильного решения в приемном устройстве с использованием обратной связи по решению вследствие взаимодействия анализируемой посьтки с хвостами предшествующих посыпок, о которых уже принято. Выхорешениеды дешифратора 9 ошибочных комбина- ций, формирователя 10 управляющих сигналов заведены навходы многовходовых коммутаторов 12, которые используются с целью уменьшения числа двухвходовых элементов совпадения И 13 и числа счетчиков 14. Управление многовходовых коммутаторов 12 осуществляет формирователь 10 управляющих сигналов. Выходы многовходовых коммутаторов 12 через двухвходовые элементы совпадения И 13 заведены на счетчики 14. Двухвходовые элементы совпадения И 13 и счетчики 14 объединены в субблоки, число которых равно числу выходов многовходовых коммутаторов 12, включенных на выход дешифратора 9 ошибочных комбинаций, а число двухвходовых элементов совпадения И 13 и счетчиков 14 в каждом субблоке равно числу многовходовых коммутаторов 12, включенных на выход дешифратора кодовых комбинаций 11. При одновременном поступлении сигнала на оба входа какого-либо двухвходового элемента совпадения И 13 на его выходе цоявляется сигнал, который увеличивает :содержимое счетчика 14 на единицу. Линия 3 задержки введена для того, чтобы нулевая комбинация, которая может возникнуть в датчике 5 испытательного текста при включении, успела выйти из буферного регистра 6. , Инверсные выходы датчика испытательного текста 5 заведены через многовходовой элемент И-НЕ 7 на его установочный вход для того, чтобы исключить возможность возникновения и циркуляции нулевой комбинации после включения датчика 5 испытательного текста. Технико-экономическое преимущество предлагаемого устройства по сравнению с известным заключается в том, что появляется возможность .учесть влияние на анализируемую посыпку последу щих посыпок, которые попадают на интервал анализа посыпки, решение о которой

выносится в приемном устройстве. Появляется также возможность учитывать влияние ошибочно принятых посыпок, последствие которых доходит до анализируемой, на помехоустойчивость приемника сигналов.

При реальной обратной связи по решению происходит ух цшение достоверности приема в 10-15 раз из-за . влияния ошибочно 1ФИНЯТЫХ ранее посыпок. Кроме того, полученные сведения о влиянии различных комбинаций, ошибочно принятых ранее посыпок можно использовать при разработке адаптивных кодексов, куда даннЬ1Й анализатор может войти в качестве составной части, .

Применение устройства для анализа распределения ошибок в кодовой комбинации позволяет сократить время раз- работки устройств по приему дискрет- ной информации в условиях межскКйольной интерференции, использующих алгоритмы с обратной связью по .решению, а также использовать инфй5 мацию ошибок в кодовых комбинациях для систем, применяющих адаптивное кодирование.

| название | год | авторы | номер документа |

|---|---|---|---|

| Тренажер радиотелеграфиста | 1983 |

|

SU1119057A1 |

| Устройство коррекции двойных ошибок с использованием кода Рида-Соломона | 1988 |

|

SU1662010A1 |

| Устройство для формирования испытательного сигнала | 1975 |

|

SU558414A1 |

| Устройство синхронизации двоичных сигналов в приемной аппаратуре многоканальной системы связи | 1981 |

|

SU1083389A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ КОМБИНИРОВАННОГО ПРИМЕНЕНИЯ ДВОЙСТВЕННОГО БАЗИСА ПОЛЯ GF(2) И ВЫДЕЛЕНИЯ "СКОЛЬЗЯЩЕГО ОКНА" С ОШИБКАМИ | 2014 |

|

RU2580806C2 |

| УСТРОЙСТВО ДИВЕРГЕНТНОГО ДЕКОДИРОВАНИЯ СЕГМЕНТОВ ЛИНЕЙНОЙ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2820053C1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Устройство для определения достоверности передачи бинарной информации | 1984 |

|

SU1229970A1 |

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

УСТРОЙСТВО ДЛЯ АНАЛИЗА РАСПРВДЕЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ, содержащее блок согласования, выход которого подключен к первому входу блока сравнения,.второй вход которого соединен с выходом датчика испытательного текста, прямые выходы разрядов которого подключены к первым информационным входам дешифратора кодойых комбинаций, управляющий вход которого соединен с выходом блока сравнения, и счетчики, отличающееся тем, что, с целью повышения точности анализа, в него введены линия задержки, регистр сдвига, две группы многовходовых коммутаторов, буферньй регистр; формирователь управляющих сигналов, дешифратор ошибочньк,комбинаций, Двухвходовые элементы совпадения И, многовходовый элемент И-НЕ, при этом выход датчика испытательного текста подключен к первому входу блока синхронизации и к входу буферного регистра, выходы разрядов которого подключены к вторым информационным входам дешифратора сесом 77 я.т..,,, №кГ кодовых комбинаций, выходы которого подключены к соответствующим входам первой группы многовходовых коммутаторов, управляющие входы которых соединены с соответствующими выходами формирователя управлякицих сигналов, вход которого соединен с управляющим входом регистра сдвига, с тактовым входом устройства для анализа распределения ошибок в кодовой комбинации, с первым входом линии задержки и с тактовым входом датчика испытательного текста,установочньй вход которо- го соединен с выходом многовходового элемента И-НЕ, входы которого соединены с инверсными выхода1 и разрядов датчика испытательного т-екста, при этом выход блока сравнения подключен к информационному входу регистра сдвига и к управляющему входу дещифратора ошибочных комбинаций, выхиды которогоподключены к соответствующим входам второй группы многовходо ых коммутаторов, управляющие входы которых соединены с ссответствукицими выходами формирователя управляющих i сигналов, а выходы всех многовходовых коммутаторов соединены с первыми входами соответствукицих двухвходовых элементов совпадения И, вторые входы которых соединены с соответствуюп ими выходами первой группы ьшоговхо- ; довых коммутаторов, а выходы подклю- « чены к счетчикам, при этом выход линии задержки подключен к управляю- щему входу блока,согласования, второй выход которого подключен к второму входу блока синхронизации, выход которого сЬединен с вторьш входом линии задержки.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Валтер и др | |||

| Измерительные приборы для телеграфии и передачи данных | |||

| М., Связь, 1980, с.34-39 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| 1972 |

|

SU422111A1 | |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-12-07—Публикация

1983-10-11—Подача