Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ БЛОКОВ ИНФОРМАЦИИ | 2003 |

|

RU2249920C2 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для исправления искажений в системах передачи дискретной информации | 1987 |

|

SU1603532A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

| Устройство для записи-воспроизведения многоканальной информации | 1984 |

|

SU1190410A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| Генератор сочетаний | 1984 |

|

SU1166090A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2008 |

|

RU2390943C1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в системах передачи дискретной информации, оперирующих кодами с двухкратной избыточностью (квадратично-вы- четными), позволяет повысить точность декодирования за счет исправления пачек ошибок и расширить функциональные возможности за счет обеспечения параллельного вывода декодированного кодового слова целиком или по частям. Это достигается благодаря введению дополнительного регистра сдвига, буферного регистра, двух дешифраторов, триггера, блока .управления и логических элементов. 1 з.п. ф-лы. 3 ил.

Изобретение относится к вычислительной технике и технике связи и может применяться для исправления ошибок в системах передачи дискретной информации с кодами, обладающими двухкратной избыточностью, например квадратичновычетными.

Известны декодирующие устройства циклического кода, содержащие буферный регистр, коммутаторы, элементы И. ИЛИ. сумматоры по модулю два и кодовый фильтр, выходы которого подключены к входам трех пороговых блоков.

Недостатком этих устройств является низкая производительность (на бит кодового слова затрачивается два-три такта).

Известны также декодеры, содержащие регистр данных, регистр синдрома,.элёмент ИЛИ-НЕ и вентили (коммутаторы). .

Недостатками декодеров являются низкая производительность (три такта на бит кодового слова) и повышенная сложность схемы коррекции ошибок (для одновременного изменения большого числа бит в соответствии с максимальной длиной исправляемой пачки ошибок).

Наиболее близким к предлагаемому является устройство для декодирования линейного циклического кода, содержащее два регистра, два кодовых фильтра, два пороговых блока, дешифратор, четыре коммутатора, два блока сумматоров по модулю два, IK-триггер, элемент И. два элемента ИЛИ и блок регистрации веса ошибок, где каждый пороговый блок содержит сумматор и дешифратор.

Недостатком известного устройства является невозможность исправления группи00 GJ 00

о

рующихся в пачку ошибок при их числе, превышающем половину кодового расстояния. Необходимость очистки выводящего информацию регистра в конце цикла обработки не позволяет осуществить последовательный вывод декодированной информации без снижения производительности или усложнения устройства.

Целью изобретения является повышение точности декодирования за счет исправления пачек ошибок и расширение функциональных возможностей путем обеспечения параллельного вывода декодированного кодового слова целиком или по частям.

8 декодирующее устройство линейного циклического кода, содержащее два кодовых фильтра, регистры, два пороговых блока, дешифратор, элемент И, элементы ИЛИ, триггер, коммутаторы, сумматоры по модулю два и блок регистрации веса ошибок, где первый установочный вход первого регистра сдвига объединен с информационным входом первого кодового фильтра и является информационным входом устройства, тактовый вход первого регистра сдвига объединен с тактовыми входами второго регистра и второго кодового фильтра и является первым тактовым входом устройства, выходы первого кодового фильтра подключены к первым информационным входам первого коммутатора, выходы которого соединены с информационными входами второго кодового фильтра, выходы которого подключены к вторым информационным входам первого коммутатора, первым входам первого дешифратора и входам первого и второго пороговых блоков, первые и вторые выходы которых соединены соответственно с одноименными управляющими и имформэцион- ными входами второго коммутатора, выходы которого подключены к первым входам блока регистрации веса ошибок, выход первого дешифратора соединен с вторым входом блока регистрации веса ошибок и первым входом второго элемента ИЛИ, первые выходы второго регистра сдвига подключены к входам первого сумматора по модулю два, выход которого соединен с первым информационным входом третьего, коммутатора, выход которого подключен к информационному входу второго регистра сдвига, выход первого триггера соединен с первым входом первого элемента И введены блок управления,третий регистр сдвига, буферный регистр, третий сумматор по модулю два, второй и третий дешифраторы, второй - четвертый элементы И, элемент ИЛИ-НЕ, источник логической единицы и второй триггер, информационный вход которого подключен к информационному входу устройства, тактовый вход второго триггера объединен с тактовыми входами третьего регистра сдвига и первого триггера

и первым тактовым входом- блока управления и подключен к первому тактовому входу устройства, выход второго триггера соединен с вторым информационным входом третьего коммутатора и вторым установоч0 ным входом первого регистра сдвига, выход второго сумматора по модулю два подключен к первому установочному входу второго и информационному входу первого регистров сдвига, первые выходы первого и треть5 его регистров сдвига соединены с вторыми и третьими установочными входами второго регистра сдвига и первыми и вторыми входами второго сумматора по модулю два, вторые выходы первого и третьего регистров

0 сдвига подключены к четвертым и пятым установочным входам второго регистра сдвига, первые и вторые выходы которого соединены с третьими установочными входами первого и с установочными входами

5 третьего регистров сдвига и являются первыми информационными выходами устройства, третий выход первого регистра сдвига подключен к третьему входу второго и пер- .вому входу третьего сумматоров по модулю два, третий выход третьего регистра сдвига

0 соединен с четвертым входом второго сумматора по модулю два, выход первого сумматора по модулю два является вторым информационным выходом, выход третьего сумматора по модулю два подключен к ше5 стому установочному входу второго и информационному входу третьего регистров сдвига, входы второго дешифратора, первые входы третьего дешифратора и первый вход второго элемента И подключены к со0 ответствующим выходам второго кодового фильтра, вторые входы третьего дешифратора и первого элемента И подключены к первому выходу первого порогового блока, второй вход первого элемента ИЛИ подклю5 чен к первому выходу второго порогового блока, первый вход третьего элемента И подключен к выходу первого триггера, выход первого элемента ИЛИ соединен со вторым входом третьего элемента И, выход

0 которого подключен к первому входу второго элемента ИЛИ и пятому вхрду второго сумматора по модулю два, выход второго дешифратора соединен с вторым входом второго элемента ИЛИ, выход третьего де5 шифратора подключен к третьему информационному входу блока регистрации веса ошибок и второму входу первого дешифратора, выход первого элемента И соединен с шестым входом второго и вторым входом

третьего сумматоров по модулю два и третьим входом второго элемента ИЛИ. выход которого подключен к первому входу четвертого элемента И, выход которого соединен с тактовым входом блока регистрации веса ошибок, выходы которого подключены к информационным входам буферного ре|ги- стра и входам элемента ИЛИ-НЕ, выход Которого соединен с информационным входом первого триггера, вторым входом второго элемента И и является первым управляющим выходом устройства, выход второго элемента И соединен с седьмым входом второго сумматора по модулю два, выходы буферного регистра являются его- рыми управляющими выходами устройства, второй тактовый вход блока управления объединен с тактовым входом первого кодового фильтра и вторым входом четвертого элемента И и является вторым тактовым входом устройства, установочные входы блока управления являются одноименными входами устройства, первый выход блока управления подключен к входам разрешения записи первого - третьего регистров сдвига и первому управляющему входу первого коммутатора, третий - пятый выходы блока управления соединены соответственно с вторым управляющим входом первого и управляющим входом третьего коммутато- ров и входом обнуления второго регистра сдвига, шестой выход блока управления подключен к входам обнуления первого триггера, блока регистрации веса ошибок и тактовому входу буферного регистра, и яв- ляется третьим управляющим выходом устройства, седьмой выход блока управления является четвертым управляющим выходом устройства, выход источника логической единицы соединен с третьим информацией- ным входом второго коммутатора.

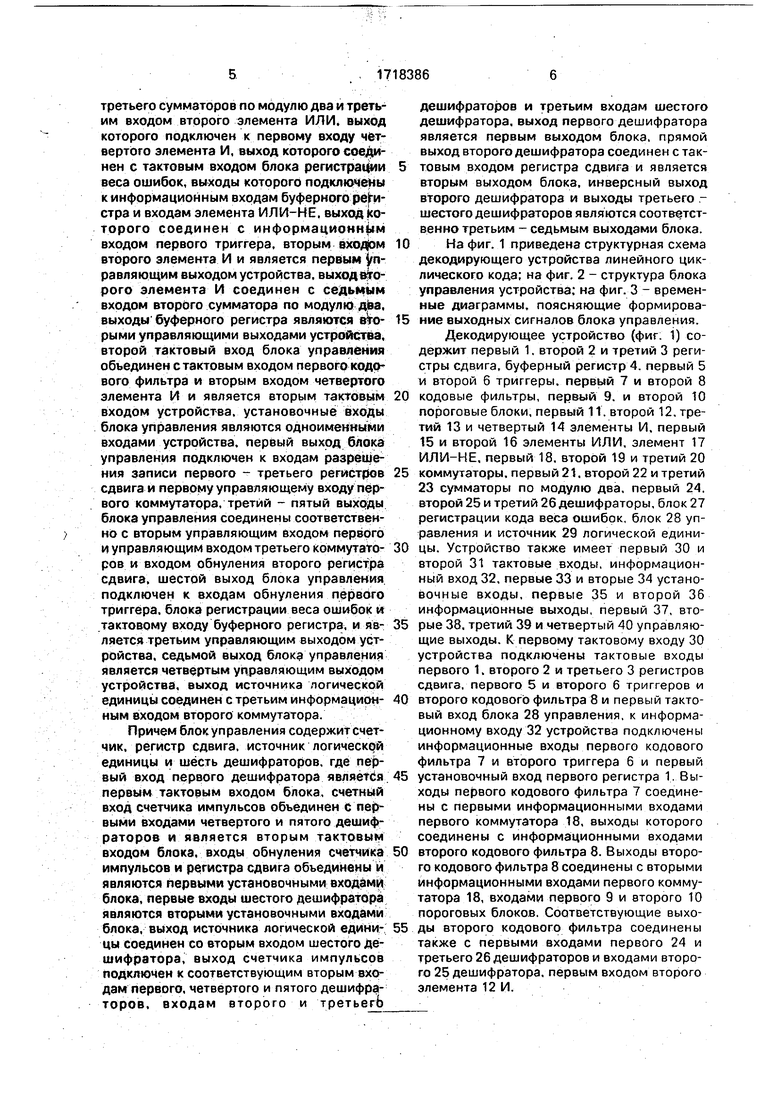

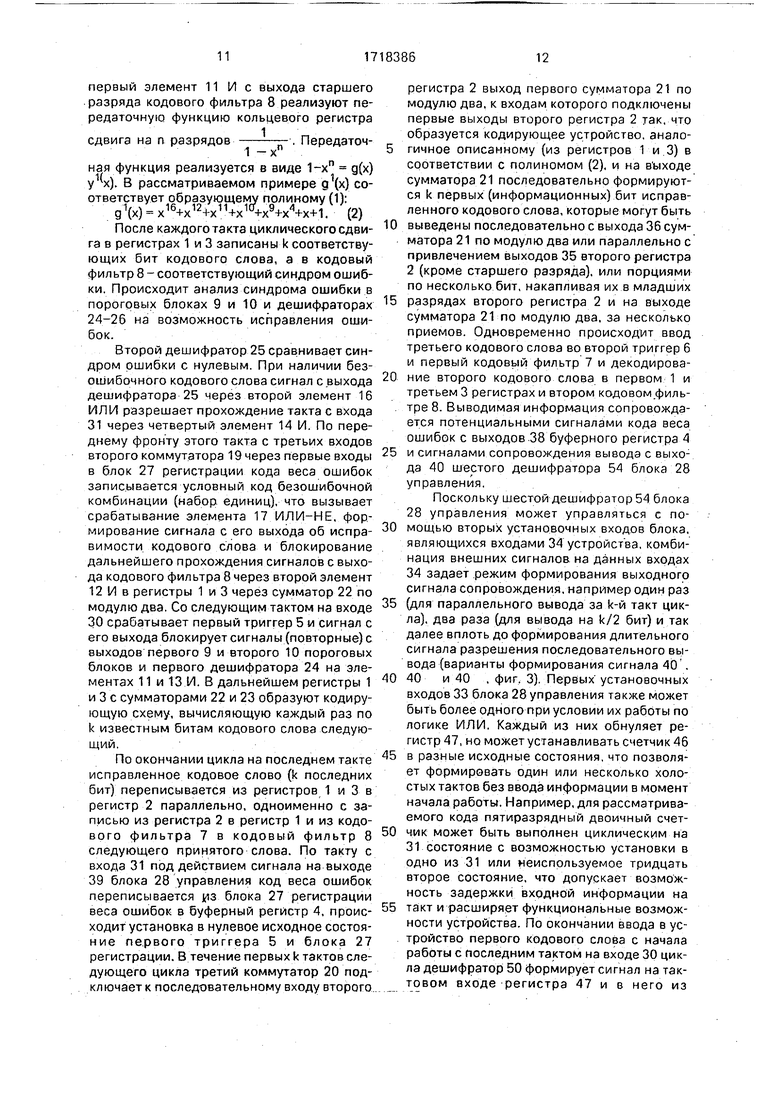

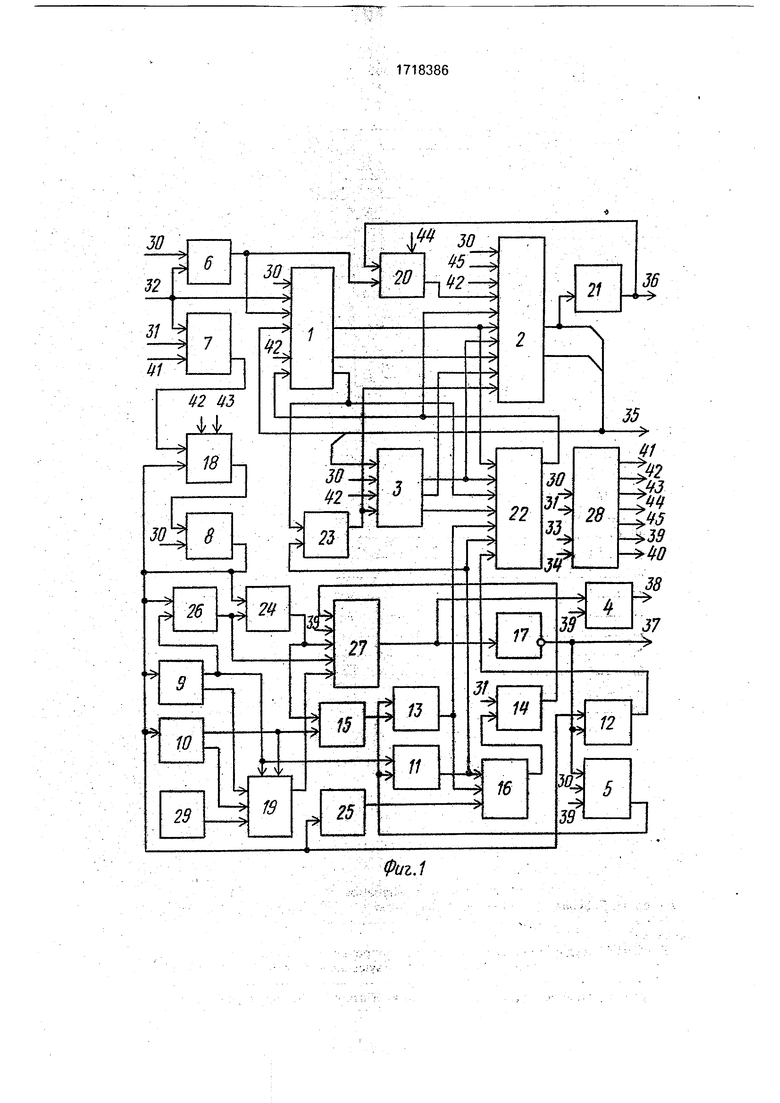

Причем блок управления содержит счетчик, регистр сдвига, источник логической единицы и шесть дешифраторов, где первый вход первого дешифратора является первым тактовым входом блока, счетный вход счетчика импульсов объединен с первыми входами четвертого и пятого дешифраторов и является вторым тактовым входом блока, входы обнуления счетчика импульсов и регистра сдвига объединены и являются первыми установочными входами блока, первые входы шестого дешифратора являются вторыми установочными входами блока, выход источника логической едини-; цы соединен со вторым входом шестого дешифратора, выход счетчика импульсов подключен к соответствующим вторым входам первого, четвертого и пятого дешифраторов, входам второго и третьего

дешифраторов и третьим входам шестого дешифратора, выход первого дешифратора является первым выходом блока, прямой выход второго дешифратора соединен с тактовым входом регистра сдвига и является вторым выходом блока, инверсный выход второго дешифратора и выходы третьего .- шестого дешифраторов являются соответственно третьим - седьмым выходами блока.

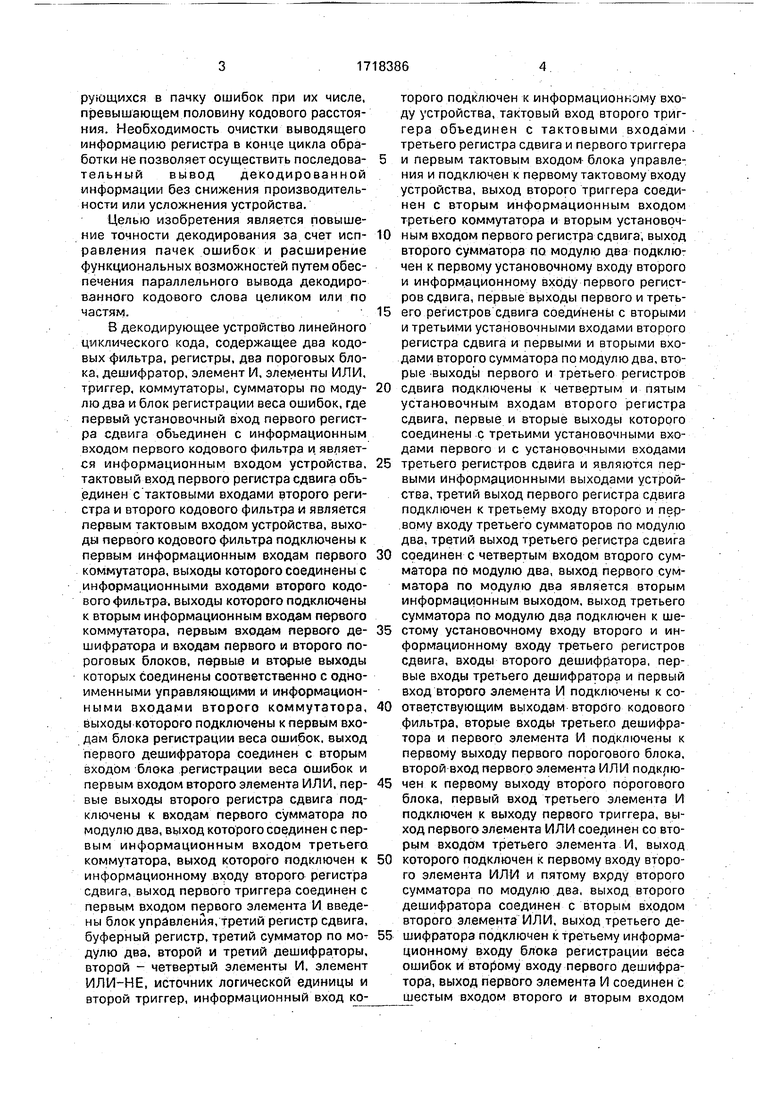

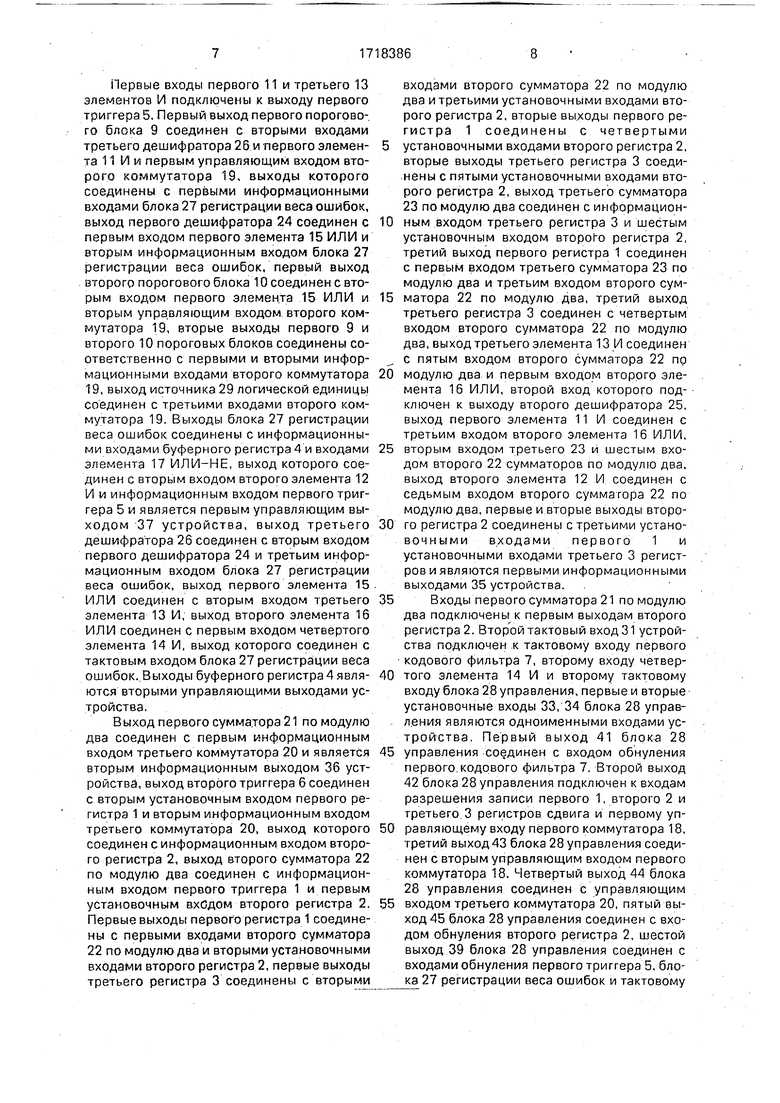

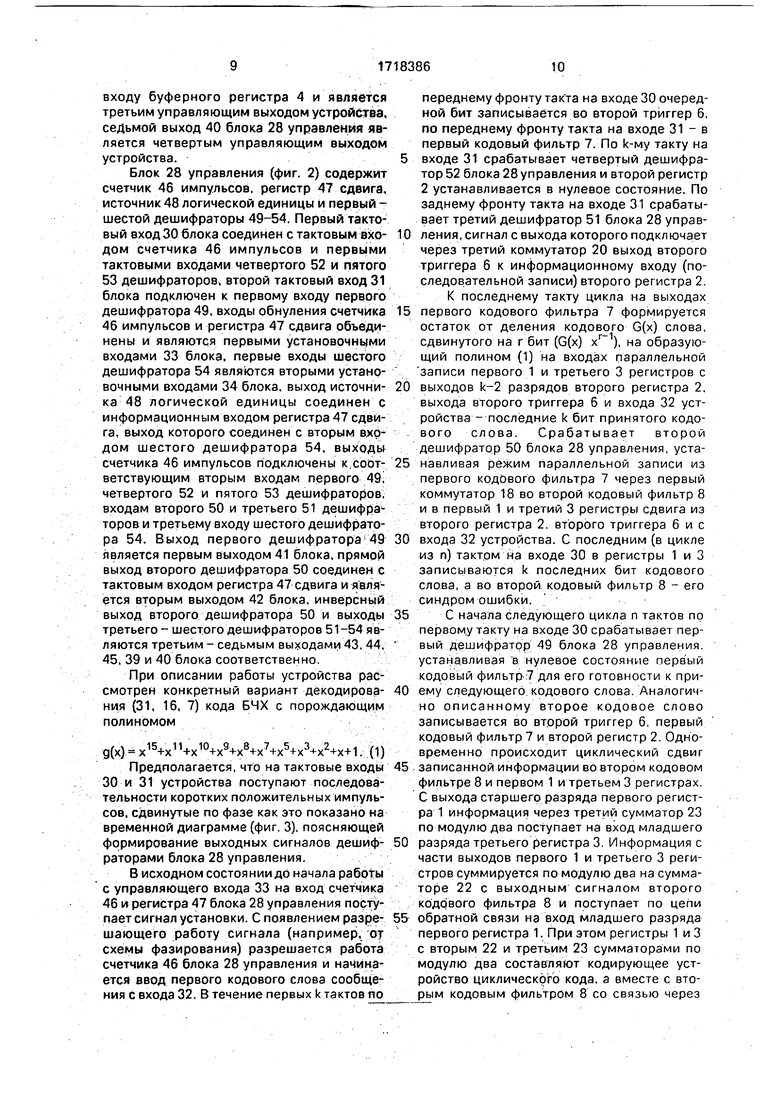

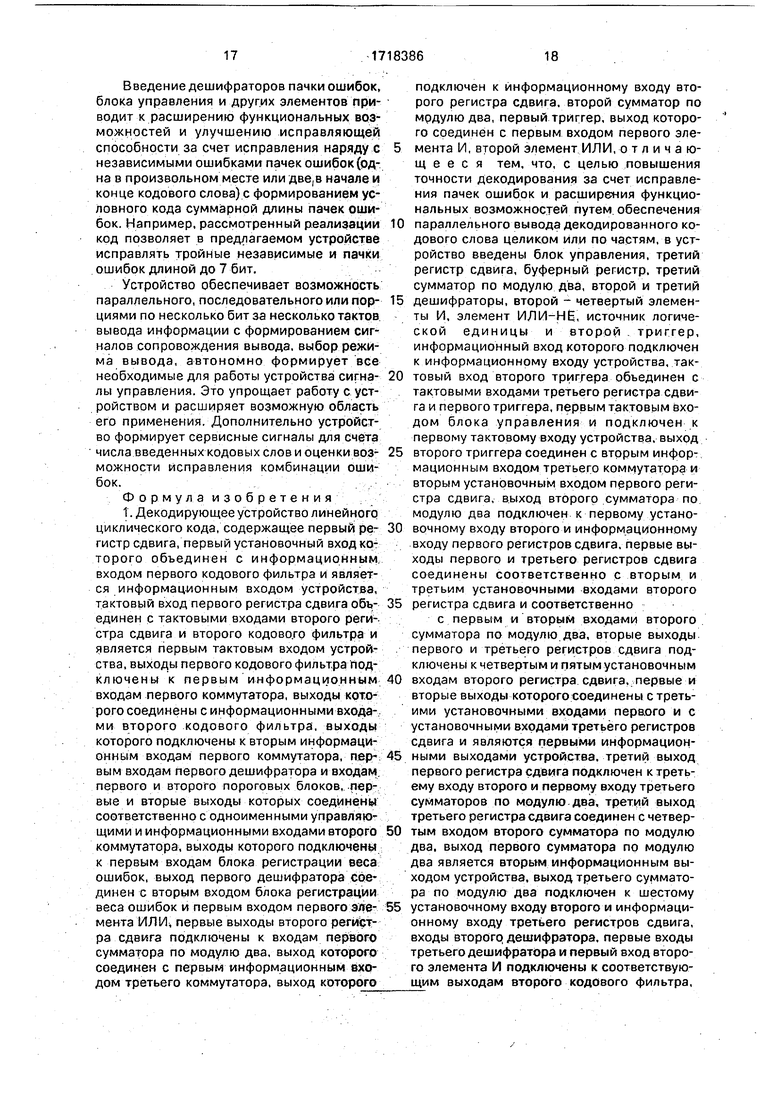

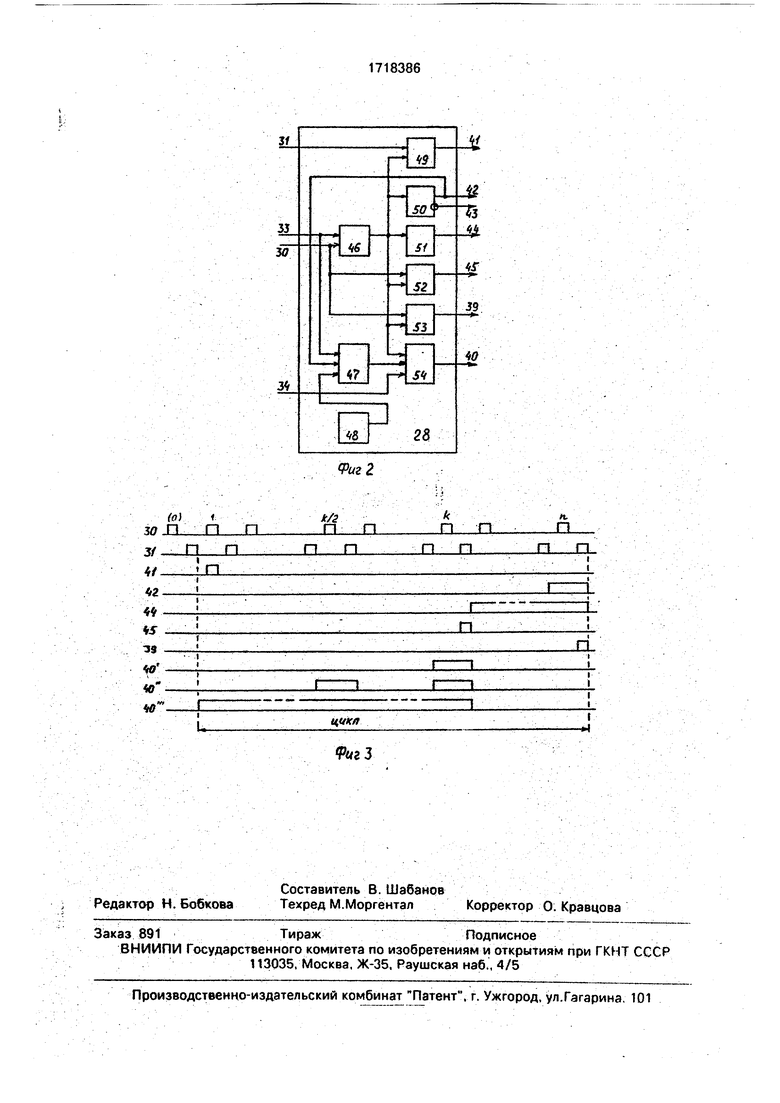

На фиг. 1 приведена структурная схема декодирующего устройства линейного циклического кода; на фиг. 2 - структура блока управления устройства: на фиг. 3 - временные диаграммы, поясняющие формирование выходных сигналов блока управления.

Декодирующее устройство (фиг. 1) содержит первый 1. второй 2 и третий 3 регистры сдвига, буферный регистр 4. первый 5 и второй 6 триггеры, первый 7 и второй 8 кодовые фильтры, первый 9, и второй 10 пороговые блоки, первый 11. второй 12, третий 13 и четвертый 14 элементы И, первый 15 и второй 16 элементы ИЛИ, элемент 17 ИЛИ-НЕ, первый 18, второй 19 и третий 20 коммутаторы, первый 21. второй 22 и третий 23 сумматоры по модулю два, первый 24. второй 25 и третий 26 дешифраторы, блок 27 регистрации кода веса ошибок, блок 28 управления и источник 29 логической единицы. Устройство также имеет первый 30 и второй 31 тактовые входы, информационный вход 32, первые 33 и вторые 34 устано- вочные входы, первые 35 и второй 36 информационные выходы, первый 37, вторые 38. третий 39 и четвертый 40 управляющие выходы. К первому тактовому входу 30 устройства подключены тактовые входы первого 1. второго 2 и третьего 3 регистров сдвига, первого 5 и второго 6 триггеров и второго кодового фильтра 8 и первый тактовый вход блока 28 управления, к информационному входу 32 устройства подключены информационные входы первого кодового фильтра 7 и второго триггера 6 и первый установочный вход первого регистра 1. Выходы первого кодового фильтра 7 соединены с первыми информационными входами первого коммутатора 18, выходы которого соединены с информационными входами второго кодового фильтра 8. Выходы второго кодового фильтра 8 соединены с вторыми информационными входами первого коммутатора 18, входами первого 9 и второго 10 пороговых блоков. Соответствующие выходы второго кодового фильтра соединены также с первыми входами первого 24 и третьего 26 дешифраторов и входами второго 25 дешифратора, первым входом второго элемента 12 И.

Первые входы первого 11 и третьего 13 элементов И подключены к выходу первого триггера 5. Первый выход первого порогового блока 9 соединен с вторыми входами третьего дешифратора 26 и первого элемента 11 И м первым управляющим входом второго коммутатора 19, выходы которого соединены с первыми информационными входами блока 27 регистрации веса ошибок, выход первого дешифратора 24 соединен с первым входом первого элемента 15 ИЛИ и вторым информационным входом блока 27 регистрации веса ошибок, первый выход второго порогового блока 10 соединен с вторым входом первого элемента 15 ИЛИ и вторым управляющим входом второго коммутатора 19, вторые выходы первого 9 и второго 10 пороговых блоков соединены соответственно с первыми и вторыми информационными входами второго коммутатора 19, выход источника 29 логической единицы соединен с третьими входами второго коммутатора 19. Выходы блока 27 регистрации веса ошибок соединены с информационными входами буферного регистра 4 и входами элемента 17 ИЛИ-НЕ, выход которого соединен с вторым входом второго элемента 12 Л и информационным входом первого триггера 5 и является первым управляющим выходом 37 устройства, выход третьего дешифратора 26 соединен с вторым входом первого дешифратора 24 и третьим информационным входом блока 27 регистрации веса ошибок, выход первого элемента 15 ИЛИ соединен с вторым входом третьего элемента 13 И, выход второго элемента 16 ИЛИ соединен с первым входом четвертого элемента 14 И, выход которого соединен с тактовым входом блока 27 регистрации веса ошибок..Выходы буферного регистра 4 являются вторыми управляющими выходами устройства.

Выход первого сумматора 21 по модулю два соединен с первым информационным входом третьего коммутатора 20 и является вторым информационным выходом 36 уст- ройствй, выход второго триггера 6 соединен с вторым установочным входом первого регистра 1 и вторым информационным входом третьего коммутатора 20, выход которого соединен с информационным входом второго регистра 2, выход второго сумматора 22 по модулю два соединен с информационным входом первого триггера 1 и первым установочным входом второго регистра 2. Первые выходы первого регистра 1 соединены с первыми входами второго сумматора 22 по модулю два и вторыми установочными входами второго регистра 2, первые выходы третьего регистра 3 соединены с вторыми

входами второго сумматора 22 по модулю два и третьими установочными входами второго регистра 2, вторые выходы первого регистра 1 соединены с четвертыми

установочными входами второго регистра 2, вторые выходы третьего регистра 3 соединены с пятыми установочными входами второго регистра 2, выход третьего сумматора 23 по модулю два соединен с информацион0 ным входом третьего регистра 3 и шестым установочным входом второго регистра 2, третий выход первого регистра 1 соединен с первым входом третьего сумматора 23 по модулю два и третьим входом второго сум5 матора 22 по модулю два, третий выход третьего регистра 3 соединен с четвертым входом второго сумматора 22 по модулю два, выход третьего элемента 1.3 И соединен с пятым входом второго сумматора 22 по

0 модулю два и первым входом второго элемента 16 ИЛИ, второй вход которого подключен к выходу второго дешифратора 25, выход первого элемента 11 И соединен с третьим входом второго элемента 16 ИЛИ,

5 вторым входом третьего 23 И шестым входом второго 22 сумматоров по модулю два, выход второго элемента 12 И соединен с седьмым входом второго сумматора 22 по модулю два, первые и вторые выходы второ0 го регистра 2 соединены с третьими устано- вочными входами первого 1 и установочными входами третьего 3 регистров и являются первыми информационными выходами 35 устройства.

5Входы первого сумматора 21 по модулю

два подключены к первым выходам второго регистра 2. Второй тактовый вход 31 устройства подключен .к тактовому входу первого кодового фильтра 7, второму входу четвер0 того элемента 14 И и второму тактовому входу блока 28 управления, первые и вторые установочные входы 33, 34 блока 28 управ- ления являются одноименными входами устройства, Первый выход 41 блока 28

5 управления соединен с входом обнуления первого,кодового фильтра 7. Второй выход 42 блока 28 управления подключен к входам разрешения записи первого 1, второго 2 и третьего. 3 регистров сдвига и первому уп0 равляющему входу первого коммутатора 18, третий выход 43 блока 28 управления соединен с вторым управляющим входом первого коммутатора 18. Четвертый выход 44 блока 28 управления соединен с управляющим

5 входом третьего коммутатора 20, пятый выход 45 блока 28 управления соединен с входом обнуления второго регистра 2, шестой выход 39 блока 28 управления соединен с входами обнуления первого триггера 5, блока 27 регистрации веса ошибок и тактовому

входу буферного регистра 4 и является третьим управляющим выходом устройства, седьмой выход 40 блока 28 управления является четвертым управляющим выходом устройства.

Блок 28 управления (фиг. 2) содержит счетчик 46 импульсов, регистр 47 сдвига, источник 48 логической единицы и первый - шестой дешифраторы 49-54. Первый тактовый вход 30 блока соединен с тактовым вхо- дом счетчика 46 импульсов и первыми тактовыми входами четвертого 52 и пятого 53 дешифраторов, второй тактовый вход 31 блока подключен к первому входу первого дешифратора 49, входы обнуления счетчика 46 импульсов и регистра 47 сдвига объединены и являются первыми установочными входами 33 блока, первые входы шестого дешифратора 54 являются вторыми установочными входами 34 блока, выход источни- ка 48 логической единицы соединен с информационным входом регистра 47 сдвига, выход которого соединен с вторым вхр дом шестого дешифратора 54, выходы счетчика 46 импульсов подключены к;соот- ветствующим вторым входам первого 49 четвертого 52 и пятого 53 дешифраторов, входам второго 50 и третьего 51 дешифра1- торов и третьему входу шестого дешифратора 54. Выход первого дешифратораГ49 является первым выходом 4.1 блока, прямой выход второго дешифратора 50 соединен с тактовым входом регистра 47 сдвига и является вторым выходом 42 блока, инверсный выход второго дешифратора 50 и выходы третьего- шестого дешифраторов 51-54 являются третьим - седьмым выходами 43. 44. 45, 39 и 40 блока соответственно.

При описании работы устройства рассмотрен конкретный вариант декодирова- ния (31, 16, 7) кода БЧХ с порождающим полиномом

g(x) X15+x11+x10+x9+x8+x7+x5+x3+x2+x+1. .(1)

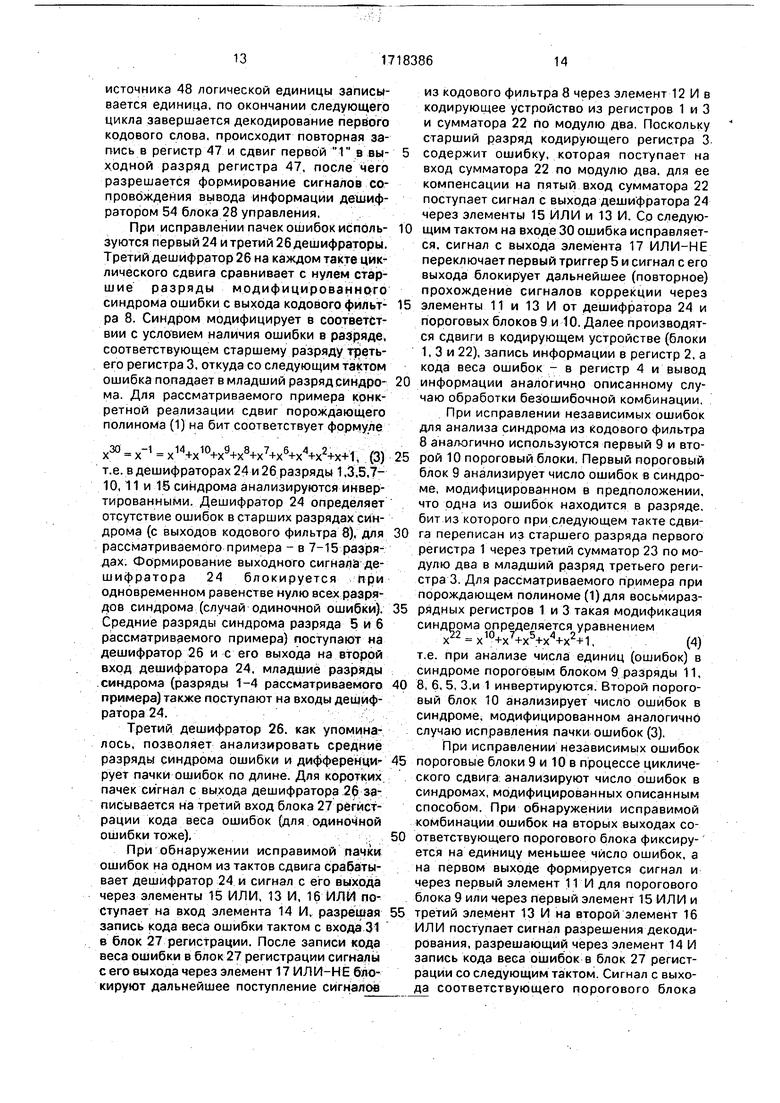

Предполагается, что на тактовые входы 30 и 31 устройства поступают последовательности коротких положительных импульсов, сдвинутые по фазе как это показано на временной диаграмме (фиг. 3), поясняющей формирование выходных сигналов дешиф- раторами блока 28 управления.

В исходном состоянии до начала работы с управляющего входа 33 на вход счетчика 46 и регистра 47 блока 28 управления поступает сигнал установки. С появлением разре- шающего работу сигнала (например от схемы фазирования) разрешается работа счетчика 46 блока 28 управления и начинается ввод первого кодового слова сообщения с входа 32. В течение первых k тактов по

переднему фронту такта на входе 30 очередной бит записывается во второй триггер 6, по переднему фронту такта на входе 31 - в первый кодовый фильтр 7. По k-му такту на входе 31 срабатывает четвертый дешифратор 52 блока 28управления и второй регистр 2 устанавливается в нулевое состояние. По заднему фронту такта на входе 31 срабатывает третий дешифратор 51 блока 28 управления, сигнал с выхода которого подключает через третий коммутатор 20 выход второго триггера 6 к информационному входу (последовательной записи) второго регистра 2.

К последнему такту цикла на выходах первого кодового фильтра 7 формируется остаток от деления кодового G(x) слова, сдвинутого на г бит (G(x) хг ), на образующий полином (1) на входах параллельной записи первого 1 и третьего 3 регистров с выходов k-2 разрядов второго регистра 2, выхода второго триггера 6 и входа 32 устройства - последние k бит принятого кодового слова. Срабатывает второй дешифратор 50 блока 28 управления, устанавливая режим параллельной записи из первого кодового фильтра 7 через первый коммутатор 18 во второй кодовый фильтр 8 и в первый 1 и третий 3 регистры сдвига из второго регистра 2, второго триггера бис входа 32 устройства. С последним (в цикле из п) тактом на входе 30.в регистры 1 и 3 записываются k последних бит кодового слова, а во второй кодовый фильтр 8 - его синдром ошибки.

С начала следующего цикла п тактов по первому такту на входе 30 срабатывает первый дешифратор 49 блока 28 управления, устанавливая в нулевое состояние первый кодовый фильтр; для его готовности к приему следующего кодового слова. Аналогично описанному второе кодовое слово записывается во второй триггер 6, первый кодовый фильтр 7 и второй регистр 2. Одновременно происходит циклический сдвиг записанной информации во втором кодовом фильтре 8 и первом 1 и третьем 3 регистрах. С выхода старшего разряда первого регистра 1 информация через третий сумматор 23 по модулю два поступает на вход младшего разряда третьего регистра 3. Информация с части выходов первого 1 и третьего 3 регистров суммируется по модулю два на сумматоре 22 с выходным сигналом второго кодрвого фильтра 8 и поступает по цепи обратной связи на вход младшего разряда первого регистра 1. При этом регистры 1 и 3 с вторым 22 и третьим 23 сумматорами по модулю два составляют кодирующее устройство циклического кода, а вместе с вторым кодовым фильтром 8 со связью через

первый элемент 11 И с выхода старшего разряда кодового фильтра 8 реализуют передаточную функцию кольцевого регистра

сдвига на п разрядов -. Передаточная функция реализуется в виде 1-х д(х) ). В рассматриваемом примере д1(х) соответствует образующему полиному (1):

д1(х) x16+x12+x11+x10+x9V+x+1 (2)

После каждого такта циклического сдвига в регистрах 1 и 3 записаны к соответствующих бит кодового слова, а в кодовый фильтр 8 - соответствующий синдром ошибки. Происходит анализ синдрома ошибки в пороговых блоках 9 и 10 и дешифраторах 24-26 на возможность исправления ошибок.

Второй дешифратор 25 сравнивает синдром ошибки с нулевым. При наличии безошибочного кодового слова сигнал с выхода дешифратора 25 через второй элемент 16 ИЛИ разрешает прохождение такта с входа 31 через четвертый элемент 14 И. По переднему фронту этого такта с третьих входов второго коммутатора 19 через первые входы в блок 27 регистрации кода веса ошибок записывается условный код безошибочной комбинации (набор, единиц), что вызывает срабатывание элемента 17 ИЛИ-НЕ, формирование сигнала с его выхода об испра- вимости кодового слова и блокирование дальнейшего прохождения сигналов с выхода кодового фильтра 8 через второй элемент 12 И в регистры 1 и 3 через сумматор 22 по модулю два. Со следующим тактом на входе 30 срабатывает первый триггер 5 и сигнал с его выхода блокирует сигналы (повторные) с выходов первого 9 и второго 10 пороговых блоков и первого дешифратора 24 на элементах 11 и 13 И. В дальнейшем регистры 1 и 3 с сумматорами 22 и 23 образуют кодирующую схему, вычисляющую каждый раз по к известным битам кодового слова следующий.

По окончании цикла на последнем такте исправленное кодовое слово (k последних бит) переписывается из регистров 1 и 3 в регистр 2 параллельно, одноименно с записью из регистра 2 в регистр 1 и из кодового фильтра 7 в кодовый фильтр 8 следующего принятого слова. По такту с входа 31 под действием сигнала на выходе 39 блока 28 управления код веса ошибок переписывается из блока 27 регистрации веса ошибок в буферный регистр 4, происходит установка в нулевое исходное состояние первого триггера 5 и блока 27 регистрации. В течение первых k тактов следующего цикла третий коммутатор 20 подключает к последовательному входу второго.

регистра 2 выход первого сумматора 21 по модулю два, к входам которого подключены первые выходы второго регистра 2 так, что образуется кодирующее устройство, аналогичное описанному (из регистров 1 и.З) в соответствии с полиномом (2), и на в ыходе сумматора 21 последовательно формируются k первых (информационных) бит исправленного кодового слова, которые могут быть

0 выведены последовательно с выхода 36 сумматора 21 по модулю два или параллельно с привлечением выходов 35 второго регистра 2 (кроме старшего разряда), или порциями по несколько бит, накапливая их.в младших

5 разрядах второго регистра 2 и на выходе сумматора 21 по модулю два, за несколько приемов. Одновременно происходит ввод третьего кодового слова во второй триггер 6 и первый кодовый фильтр 7 и декодирова0 ние второго кодового слова в первом 1 и третьем 3 регистрах и втором кодовом филь- . тре 8. Выводимая информация сопровождается потенциальными сигналами кода веса ошибок с выходов .38 буферного регистра 4

5 и сигналами сопровождения вывода с выхода 40 шестого дешифратора 54 блока 28 управления.

Поскольку шестой дешифратор 54 блока 28 управления может управляться с по0 мощью вторых установочных входов блока, являющихся входами 34 устройства, комбинация внешних сигналов, на данных входах 34 задает режим формирования выходного сигнала сопровождения, например один раз

5 (для параллельного вывода за k-й такт цикла), два раза (для вывода на k/2 бит) и так далее вплоть до формирования длительного сигнала разрешения последовательного вывода (варианты формирования сигнала 40 .

0 40 и 40 , фиг, 3). Первых установочных входов 33 блока 28 управления также может быть более одного при условии их работы по логике ИЛИ. Каждый из них обнуляет регистр 47, но может устанавливать счетчик 46

5 в разные исходные состояния, что позволяет формировать один или несколько холостых тактов без ввода информации в момент начала работы. Например, для рассматриваемого кода пятиразрядный двоичный счет0 чик может быть выполнен циклическим на 31 состояние с возможностью установки в одно из 31 или неиспользуемое тридцать второе состояние, что допускает возможность задержки входной информации на

5 такт и расширяет функциональные возможности устройства. По окончании ввода в устройство первого кодового слова с начала работы с последним тактом на входе 30 цикла дешифратор 50 формирует сигнал на тактовом входе регистра 47 и в него из

источника 48 логической единицы записывается единица, по окончании следующего цикла завершается декодирование первого кодового слова, происходит повторная запись в регистр 47 и сдвиг первой 1 в выходной разряд регистра 47, после чего разрешается формирование сигналов сопровождения вывода информации дешифратором 54 блока 28 управления,

При исправлении пачек ошибок используются первый 24 и третий 26 дешифраторы. Третий дешифратор 26 на каждом такте циклического сдвига сравнивает с нулем старшие разряды модифицированного синдрома ошибки с выхода кодового фильтра 8. Синдром модифицирует в соответствии с условием наличия ошибки в разряде, соответствующем старшему разряду третьего регистра 3. откуда со следующим тактом ошибка попадает в младший разряд синдрома. Для рассматриваемого примера конкретной реализации сдвиг порождающего полинома (1) на бит соответствует формуле

Х30 х-1 X14+x10+x9+x8+x7+x6+x4+x2+x+li gj;

т.е. в дешифраторах 24 и 26 разряды 1,3.5,t- 10, 11 и 15 синдрома анализируются инвертированными. Дешифратор 24 определяет отсутствие ошибок в старших разрядах синдрома (с выходов кодового фильтра 8), для рассматриваемого примера - в 7-15 разрядах. Формирование выходного сигнала дешифратора 24 блокируется при одновременном равенстве нулю всех разрядов синдрома (случай одиночной ошибки). Средние разряды синдрома разряда 5 и 6 рассматриваемого примера) поступают на дешифратор 26 и с его выхода на второй вход дешифратора 24, младшие разряды .синдрома (разряды 1-4 рассматриваемого примера) также поступают на входы дешифратора 24.

Третий дешифратор 26. как упоминалось, позволяет анализировать средние разряды синдрома ошибки и дифферемци - рует пачки ошибок по длине. Для коротких, пачек сигнал с выхода дешифратора 26 записывается на третий вход блока 27 регистрации кода веса ошибок (для одиночной ошибки тоже).:

При обнаружении исправимой пачки ошибок на одном из тактов сдвига срабатывает дешифратор 24 и сигнал с его выхода через элементы 15 ИЛИ, 13 И, 16 ИЛИ поступает на вход элемента 14 И, разрешая запись кода веса ошибки тактом с входа 31 в блок 27 регистрации. После записи кода веса ошибки в блок 27 регистрации сигналы с его выхода через элемент 17 ИЛИ-НЁ блокируют дальнейшее поступление сигналов

из кодового фильтра 8 через элемент 12 И в кодирующее устройство из регистров 1 и 3 и сумматора 22 по модулю два. Поскольку старший разряд кодирующего регистра 3 5 содержит ошибку, которая поступает на вход сумматора 22 по модулю два. для ее компенсации на пятый вход сумматора 22 поступает сигнал с выхода дешифратора 24 через элементы 15 ИЛИ и 13 И. Со следую0 щим тактом на входе 30 ошибка исправляется, сигнал с выхода элемента 17 ИЛИ-НЕ переключает первый триггер 5 и сигнал с его выхода блокирует дальнейшее (повторное) прохождение сигналов коррекции через

5 элементы 11 и 13 И от дешифратора 24 и пороговых блоков 9 и 10. Далее производятся сдвиги в кодирующем устройстве (блоки 1, 3 и 22), запись информации в регистр 2, а кода веса ошибок - в регистр 4 и вывод

0 информации аналогично описанному случаю обработки безошибочной комбинации. При исправлении независимых ошибок для анализа синдрома из кодового фильтра 8 аналогично используются первый 9 и вто5 рой 10 пороговый блоки. Первый пороговый блок 9 анализирует число ошибок в синдроме, модифицированном в предположении, что одна из ошибок находится в разряде. бит из которого при следующем такте сдви0 га переписан из старшего разряда первого регистра 1 через третий сумматор 23 по модулю два в младший разряд третьего регистра 3. Для рассматриваемого примера при порождающем полиноме (1) для восьмираз5 рядных регистров 1 и 3 такая модификация синдрома определяется уравнением

xk x 45VV+1,(4)

т.е. при анализе числа единиц (ошибок) в синдроме пороговым блоком 9 разряды 11,

0 8, 6, 5, 3,и 1 инвертируются. Второй пороговый блок 10 анализирует число ошибок в синдроме, модифицированном аналогично случаю исправления пачки ошибок (3).

При исправлении независимых ошибок

5 пороговые блоки 9 и 10 в процессе циклического сдвига: анализируют число ошибок в синдромах, модифицированных описанным способом. При обнаружении исправимой комбинации ошибок на вторых выходах со0 ответствующего порогового блока фиксируется на единицу меньшее число ошибок, а на первом выходе формируется сигнал и через первый элемент 11 И для порогового блока 9 или через первый элемент 15 ИЛИ и

5 третий элемент 13 И на второй элемент 16 ИЛИ поступает сигнал разрешения декодирования, разрешающий через элемент 14 И запись кода веса ошибок в блок 27 регистрации со следующим тактом. Сигнал с выхода соответствующего порогового блока

также поступает на управляющий вход второго коммутатора 19 и подключает вторые выходы данного порогового блока через коммутатор 19 к первым входам блока 27 регистрации веса ошибок.

При срабатывании второго порогового блока 10 аналогично описанному случаю исправления пачки ошибок корректируется ошибочный бит из старшего разряда третьего регистра 3 путем подачи корректирующего сигнала через элементы 15 ИЛИ и 13 И на пятый вход сумматора 22 по модулю два. Одновременно может сработать дешифратор 24 (и 26) при группировании исправляемых ошибок. При исправлении одиночной ошибки дешифратор 26 формирует выходной сигнал, но срабатывание дешифратора 24 блокируется сигналами младших разрядов синдрома. Это сделано для дифференцирования одиночной ошибки от случая исправления пачки ошибок, имеющей (в рассматриваемом примере) тот же код числа независимых ошибок.

При срабатывании первого порогового блока 9 сигнал с его выхода через элемент 11 И поступает также на вход третьего сумматора 23 по модулю два для коррекции бита, переписываемого следующим тактом в младший разряд регистра 3, код веса ошибок с выходов блока 27 регистрации через элемент 15 ИЛИ блокирует поступление сигналов с. выхода кодового фильтра 8 через элемент 12 И в кодирующее устройство (блоки 1, 3 и 22) аналогично описанным случаям. Для рассматриваемого варианта реализации устройства с порождающим полиномом (1) выход старшего разряда регистра 1 не участвует в формировании суммы по модулю два сумматором 22 в младший разряд регистра 1. Поэтому сигналы на третьем и шестом входах второго сумматора 22 по модулю два являются излишними. Однако в общем случае существуют циклические коды, например квадратично-вычетный код (31. 16 и 7). с полиномами

д(х) Х15+х14+х13+х9+х8+х3-И и

д 1 (х) - X16+x15+x13+x12+x8+x6+x3+x+1,

для которых выход старшего разряда регистра 1 участвует в формировании суммы по модулю два сумматором 22. Для этих случаев выход элемента 11 И и выход старшего разряда регистра 1 подключены соответственно к четвертому и пятому входам второго сумматора 22 по модулю два, и при срабатывании первого порогового блока 9 дополнительно сигнал с выхода элемента. 11 И KOppeKTnpyef ошибку в сумматоре 22. Для

различения одиночной исправляемой ошибки и неисправимой комбинации ошибок при срабатывании первого порогового блока 9 сигнал с его выхода поступает на вход дешифратора 24 и независимо от состояния других входов формирует выходной сигнал на четвертый вход блока 27 регистрации веса ошибок. В дальнейшем работа устройства аналогична описанному.

Второй пороговый блок Юобнаружива- ет комбинации ошибок, сгруппированных в (г+1)-м разряде , т.е. позволяет исправлять ошибки любой кратности в пределах, достижимых для данного кодового расстояния в

случаях, когда максимальный безошибочный интервал в кодовом слове имеет длину не менее k-1 бит. Для кодовых слов с числом информационных элементов

20

k

п +1

(5)

при числе ошибок не более трех сумма безошибочных интервалов равна п -3. Если комбинация ошибок не обнаруживается

вторым пороговым блоком .10, то длина наибольшего безошибочного интервала не превышает - 2 бит, тогда сумма двух остальных интервалов не менее (п -3) - (k -2) бит или, используя соотношение n -2k-1

из (5), не менее k -2, т.е. два безошибочных

k интервала содержат по бит, либобольkший из них не менее - бит. Таким образом

из трех безошибочных интервалов либо один имеет длину k -2 бит и два остальных

по к-1 бит, либо найдутся два интервала

k длиной не менее j бит каждый. Поэтому

первый пороговый блок 9, обнаруживающий наборы ошибок, когда одна из ошибок отделена от других безошибочными интерk k валами длиной и - -Л бит, обеспечивает

обнаружение всех комбинаций ошибок с кратностью не более трех, не обнаруживаемых вторым пороговым блоком 10. и части ошибок большей кратности в пределах,

обеспечиваемых кодовым расстоянием. Аналогично могут исправляться тройные ошибки при нечетном k.

Третий управляющий выход 39 устройства может быть использован для счета числа введенных в устройство кодовых слов, например для установки устройства по входу 33 после окончания приема, обработки и вывода сообщения, содержащего заданное число кодовых слов.

Введение дешифраторов пачки ошибок, блока управления и других элементов приводит к расширению функциональных возможностей и улучшению исправляющей способности за счет исправления наряду с независимыми ошибками пачек ошибок (одна в произвольном месте или две,в начале и конце кодового слова) с формированием условного кода суммарной длины пачек ошибок. Например, рассмотренный реализации код позволяет в предлагаемом устройстве исправлять тройные независимые и пачки ошибок длиной до 7 бит.

Устройство обеспечивает возможность параллельного, последовательного или порциями по несколько бит за несколько тактов. вывода информации с формированием сигналов сопровождения вывода, выбор режима вывода, автономно формирует все необходимые для работы устройства сигналы управления. Это упрощает работу с устройством и расширяет возможную область его применения. Дополнительно устройство формирует сервисные сигналы для счета числа введенных кодовых слов и оценки возможности Исправления комбинации ошибок.

Ф о р м у л а и з о б р е т е н и я

подключен к информационному входу второго регистра сдвига, второй сумматор по мрдулю два, первый триггер, выход которого соединен с первым входом первого эле- 5 мента И, второй элемент ИЛИ, отличающееся тем, что, с целью повышения точности декодирования за счет исправления пачек ошибок и расширения функциональных возможностей путем обеспечения

0 параллельного вывода декодированного кодового слова целиком или по частям, в устройство введены блок управления, третий регистр сдвига, буферный регистр, третий сумматор по модулю два, второй и третий

5 дешифраторы, второй - четвертый элементы И, элемент ИЛИ-НЁ, источник логической единицы и второй . триггер, информационный вход которого подключен к информационному входу устройства, так0 товый вход второго триггера объединен с тактовыми входами третьего регистра сдвига и первого триггера, первым тактовым входом блока управления и подключен к первому тактовому входу устройства, выход

5 второго триггера соединен с вторым информационным входом третьего коммутатора и вторым установочным входом первого регистра сдвига, выход второго .сумматора по. модулю два подключен к первому устано0 вочному входу второго и информационному входу первого регистров сдвига, первые выходы первого и третьего регистров сдвига соединены соответственно с вторым и третьим установочными входами второго

5 регистра сдвига и соответственно

с первым и вторым входами второго сумматора по модулю два, вторые выходы .первого и третьего регистров сдвига подключены к четвертым и пятым установочным

0 входам второго регистра сдвига, первые и вторые выходы которого соединены с третьими установочными входами первого и с установочными входами третьего регистров сдвига и являются первыми информацион5 ными выходами устройства, третий выход первого регистра сдвига подключен к третьему входу второго и первому входу третьего сумматоров по модулю два, третий выход третьего регистра сдвига соединен с четвер0 тым входом второго сумматора по модулю два, выход первого сумматора по модулю два является вторым информационным выходом устройства, выход третьего сумматора по модулю два подключен к шестому

5 установочному входу второго и информационному входу третьего регистров сдвига, входы второго дешифратора, первые входы третьего дешифратора и первый вход второго элемента И подключены к соответствующим выходам второго кодового фильтра,

вторые входы третьего дешифратора и первого элемента И подключены к первому выходу первого порогового блока, второй вход первого элемента ИЛИ подключен к первому выходу второго порогового блока, первый вход третьего элемента И подключен к выходу первого триггера, выход первого элемента ИЛИ соединен с вторым входом третьего элемента И, выход которого подключен к первому входу второго элемента ИЛИ и пятому входу второго сумматора по модулю два, выход второго дешифратора соединен с вторым входом второго элемента ИЛИ, выход третьего дешифратора подключен к третьему информационному входу блока регистрации веса ошибок и второму входу первого дешифратора, выход первого элемента И соединен с шестым входом второго и вторым входом третьего сумматоров по модулю два и третьим входом второго элемента ИЛИ, выход которого подключен к первому входу четвертого элемента И, выход которого соединен с тактовым входом блока регистрации веса ошибок, выходы которого подключены к информационным входам буферного регистра и входам элемента ИЛИ-НЕ, выход которого соединен с информационным входом первого триггера, вторым входом второго элемента И и является первым управляющим выходом устройства, выход второго элемента И соединен с седьмым входом второго сумматора по модулю два, выходы буферного регистра являются вторыми управляющими выходами устройства, второй тактовый вход блока управления объединен с тактовым входом первого кодового фильтра, вторым входом четвертого элемента И и является вторым тактовым входом устройства, установочные входы блока управления являются одноименными входами устройства, первый выход блока управления соединен с входом обнуления первого кодового фильтра, второй выход блока управления подключен к входам разрешения записи первого - третьего регистров сдвига и первому управляющему входу первого коммутатора, третий пятый выходы блока управления соединены соответственно с вторым управляющим входом первого коммутатора, управляющим входом третьего коммутатора и входом обнулений второго регистра сдвига, шестой выход блока управления подключен к входам обнуления первого триггера, блока регистрации веса ошибок и тактовому входу буферного регистра и является третьим управняющим выходом устройства, седьмой выход блока управления является четвертым управляющим выходом устройства, выход источника логической единицы соединен с третьим информационным входом второго коммутатора

вход первого дешифратора является вторым тактовым входом блока, входы обнуления счетчика импульсов и регистра сдвига объединены и являются первыми установочными входами блока, первые входы шестого

дешифратора являются вторыми установочными входами блока, выход источника логи- ческой единицы соединен с информационным входом регистра сдвига, выход которого соединен с вторым входом

шестого дешифратора, выходы счетчика импульсов подключены к соответствующим вторым входам первого, четвертого и пятого дешифраторов, входам второго и третьего дешифраторов и третьим входам шестого

дешифратора, выход первого дешифратора является первым выходом блока, прямой выход второго дешифратора соединен с тактовым входом регистра сдвига и является вторым выходом блока, инверсный выход

второго и выходы третьего - шестого дешифраторов являются соответственно третьим - седьмым выходами блока.

30

36

1 JIL

XL

к/г П

П

П

П

П

П

k

П П

rt.

JO

П П

П П

| Колесник В.Д., Мирончиков Е.Т | |||

| Декодирование циклических кодов | |||

| - М.: Связь | |||

| Приспособление для контроля движения | 1921 |

|

SU1968A1 |

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

| Касами Т | |||

| и др | |||

| Теория кодирования | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Нефтяная топка для комнатных печей | 1922 |

|

SU401A1 |

| Авторское свидетельство СССР № 1487198 | |||

| кл | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

Авторы

Даты

1992-03-07—Публикация

1990-01-08—Подача