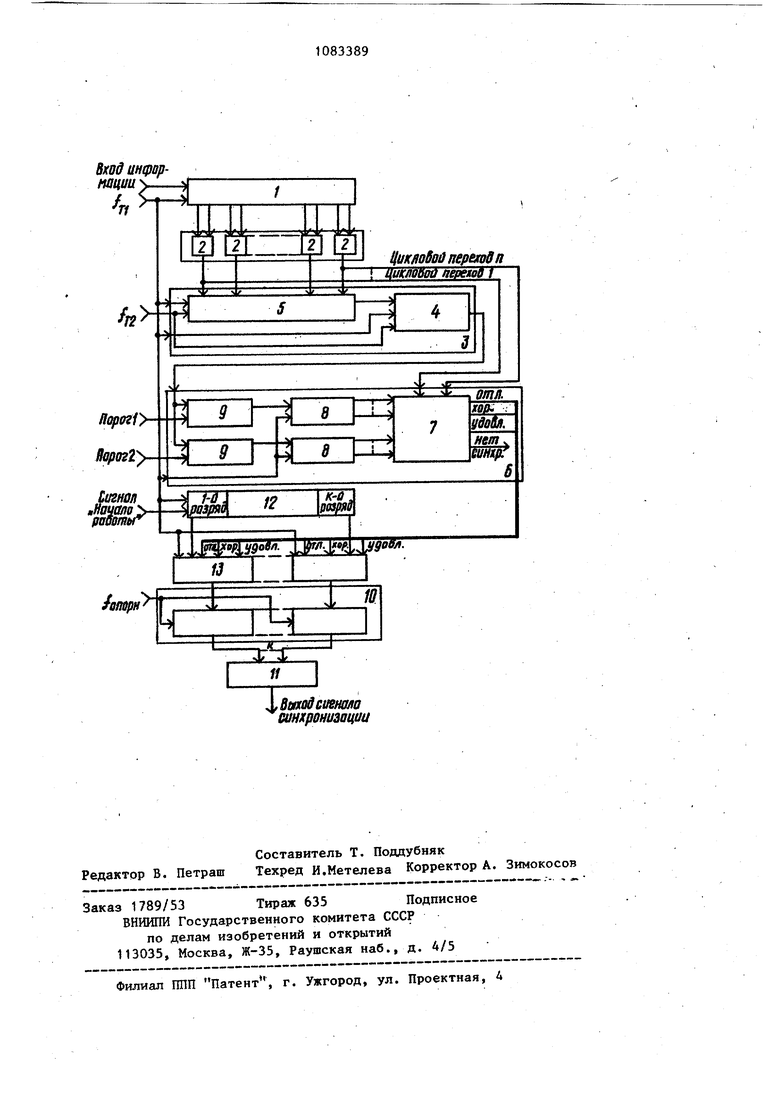

I1 Изобретение относится к технике телеграфной связи и может использоваться для синхронного приема дискретной инфо-рмации при работе совокупности демодуляторов в многоканаль ной системе связи. Известно устройство для цикловой синхронизации, содержащее объединенные по входу регистр задержки и блок обнаружения ошибок, выход которого подключен к дешифратору, счетчик, коммутатор, k-1 счетчиков, пороговьш- блок, генератор импульсов и сумматор, причем блок обнаружения ошибок выполнен в виде двух последовательно соединенных фильтров Хаффсиен и регистра, другой вых-од блока обнаружения ошибок через коммутатор . подключен к входам k счетчиков, выходы которых через последовательно соединенные пороговый блок и генератор импульсов подключены к входу сумматора, другой вход которого соединен с выходом регистра задержки, а выход дешифратора подключен к другому входу коммутатора tl 3 Однако для функционирования данного устройства для цикловой синхронизации необходима специальная синхропоследовательность. Наиболее близким к предлагаемо 1у является устройство синхронизации двоичных сигналов в приемной аппарат ре многоканальной системы связи, содержащее на входе последовательно соединенные линию задержки с отводами, блок определения фронтов и блок подсчета фронтов, при этом выход блока подсчета фронтов подсоединен к пороговому блоку С 2 . «„ В известном устройстве для осуществления приема необходимо включать специальную синхропоследовательность Кроме того, при возможных скачках фа зы радиолинии, переходе с луча на луч или перерывах связи этот принцип не обеспечивает достаточно высокую помехоустойчивость. Цель изобретения - повышение поме хоустойчивости без применения специальных сигналов и в режиме частого изменения условий связи. Поставленная цель достигается тем что в устройство синхронизации двоич ных сигналов в приемной аппаратуре многоканальной системы связи, содержащее на входе последовательно соединенные линию задержки с отводам блок определения фронтов и блок 89 подсчета фронтов, введены последовательно соединенные блок выработки оценок качества синхронизации, формирователь сброса, блок запоминания фазы и формирователь синхросигнала, а также кольцевой коммутатор, выходы fc-разрядов которого подсоединены к соответствующим входам формирователя сброса, а вход первого разряда кольцевого коммутатора подсоединен к шине Начало работы, при этом первый и последний выходы блока определения фронтов подсоединены к соответствующим входам блока выработки оценок качества синхронизации, к другому входу которого подключен выход блока подсчета фронтов, причем, тактовые входы линии задержки с отводами,блока подсчета фронтов, блока выработки оценок, кольцевого коммутатора и формирователя сброса объединены и подключены к шине тактовой частоты, опорный вход блока запоминания фазы подключен к шине опорной частоты, а установочный вход блока подсчета фронтов подключен к шине установки.. На чертеже представлена структурная электрическая схема предлагаемого устройства. . Устройство синхронизации двоичных сигналов в приемной аппаратуре многоканальной системы связи содержит линию 1 задержки с отводами, блок 2 определения фронтов, состоящий из полусумматоров, блок 3 подсчета фронтов, содержащий счетчик и параллельно-последовательный регистр 5, блок 6 вьфаботки оценок качества синхронизации, содержащий дешифратор 7, последовательный регистр 8 и пороговые элементы 9, блок 10 запоминания фазы, состоящий из 1с делителей частоты, формирователь 11 синхросигнала, кольцевой комг утатор 12 и формирователь 13 сброса. Устройство работает следующим образом. При поступлении на вход линии 1 задержки уплотненного во времени сигнала, несущего информацию о всех К принимаемых параллельно сообщениях, в определенной части блока 2 в соответствии с видом кодовых комбинаций фиксируются фронты принятых посылок. При этом на выходах блока 2 появляются импульсы, совпадающие во времени, только для каждого корреспондента в отдельности. На каждом такте f работы линии 1 задержки осуществляется параллельная запись этих импульсов в параллел но-последовательный регистр 5 и зат их последовательное продвижение на вход счетчика 4. Тактовая частота „ последовательно-параллельного регистра 5 опр деляется из условия €у2. Т1 где m - максимальное количество фрон тов посылок в кодовой комбинации. Ynic , ; где V - скорость телеграфировани Бод, П число отсчетов на длител ности элементарной посьш в соответствии с выбранн точностью синхронизации-, li; - число обслуживаемых каналов . Подсчитанное счетчиком А количес во фронтов посылок в кодовой комбинации является одним из компонентов используемых для оценки достоверности вырабатываемого в дальнейшем Сигнала сброса. Цифровой код количе ва переходов в анализируемой кодовой комбинации с выхода счетчика 4 подается на входы пороговых элементов 9, где происходит его сравнение с двумя наперед заданными числовыми порогами. При этом величина порога 1 выбирается исходя из среднего значения числа фронтов на длине кодовой комбинации, что дает возможность характеризовать ее по количеству переходов. Величина порога 2 равна нулю, что позволяет обнаружить даже одиночный переход в любом месте кодовой комбинации и за счет этого оценить ее на отсутствие просечек в наиболее помехоустойчивой средней части посыпок. Сигналы с выходов пороговых элементов записьшаются в последовательные регистры 8, имеющие инфор-. мационкую емкость .nk .С выходов последовательных регистров 8, взя7 тых через 1 разрядов, сигналы поступают на входы дешифратора 7. Сюдй же подаются сигналы с выходов тех полусумматоров блока 2, которые фиксируют наличие в кодовой комби-нации цикловых переходов. В результате анализа всех поступивших Иа его вход сигналов дешифратор 7 на одной Из выходных шин формирует импульсы оценок качества синхронизации (Отлично, Хорошо, Удовлетворительно), которые подаются на формирователь 13 сброса. По каждому из выходов формируется сигнал начальной установки фазы того делителя частоты блока 10, номер которого соответствует разряду тсольцевого коммутатора 12. Тактовая частота продвижения сигналов в кольцевом коммутаторе -f. В основу работы формирователя 13 сброса заложен принцип приоритета лучшей оценки качества синхронизации. Реализация схемы приоритета такова, что в момент выработки сигналов цикловой и тактовой синхронизации осуществляется запоминание оценок их качества в элементах памяти (триггерах). При этом выходы запоминающих триггеров скоммутированы через схемы совпадения таким образом, что при поступлении сигналов синхронизации с оценкой качества ниже, чем ранее запомненные, последние не пропускаются на выход формирователя 13 сброса, вследствие чего при ухудшении условий связи или даже частичных перерывах в работе,когда оценки качества сигналов синхронизации имеют тенденцию к снщсению, выработанные в этих условиях сигналы сброса не имеют возможности переустановить ранее запомненные (в хо- роших условиях) фазы делителей частоты блока 10. Выходы k делителей частоты блока 10 подключены к соответствующим входым формирователя 11, который формирует сигналы цикловой и тактовой синхронизации для работы оконечной аппаратуры. Технико-экономическая эффективность изобретения заключается в возможности повьш1ения помехоустойчивости приема дискретных сообщений при тых изменениях условий связи я кратковременных перерывах в работе, а также без применения специальных синхросигналов.

,Воа1 С1№мш10 синхроиизвцоа

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации двоичных сигналов в приемной аппаратуре системы связи | 1984 |

|

SU1256225A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА РАДИОСТАНЦИЙ | 1994 |

|

RU2099868C1 |

| Устройство для устранения "обратной работы | 1979 |

|

SU836805A1 |

| Устройство для передачи сигналов точного времени | 1984 |

|

SU1205165A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Устройство поэлементной синхронизации и регенерации | 1978 |

|

SU741479A1 |

| Устройство цикловой синхронизации последовательного модема | 1986 |

|

SU1450123A1 |

| Генератор псевдослучайных чисел | 1984 |

|

SU1239844A1 |

| Способ передачи сигналов точного времени по линиям связи с переменным временем распространения и устройство для его реализации | 1979 |

|

SU858058A1 |

УСТРОЙСТВО СИНХРОНИЗАЦИИ ДВОИЧНЫХ СИГНАЛОВ В ПРИЕМНОЙ АППАРАТУРЕ МНОГОКАНАЛЬНОЙ СИСТЕМЫ СВЯЗИ, содержащее на входе последовательно соединенные линию задержки с отводами, блок определения фронтов и блок подсчета фронтов, о т л ичающееся тем, что, с целью повышения помехоустойчивости без применения специальных сигналов и в режиме частого изменения условий связи, в него введены последовательно соединенные блок вьфаботки оценок качества.синхронизации, форми:рователь сброса, блок запоминания ф&зы и формирователь синхросигнала, а также кольцевой коммутатор, выходы 1i разрядов которого подсоединены к соответствующим входам формирователя сброса, а вход первого разряда кольцевого коммутатора подсоединен к шине Начало работы, при этом первый и последний выходы блока определения фронтов подсоединены к соответствующим входам блока вьфаботки оценок качества синхронизации, к другому входу которого подключен выход блока подсчета фронтов, причем тактовые входы линии задержки @ с отводами, блока подсчета фронтов, блока выработки оценок, кольцевого коммутатора и формирователя сброса объединены- и подключены к шине тактовой частоты, опорный вход блока запоминания фазы подключен к шине опорной частоты, а установочный вход блока подсчета фронтов подклюэо чен к шине установки. : : X) ;о

| ,1 | |||

| Устройство для цикловой синхронизации | 1978 |

|

SU849521A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Мешковский К.А | |||

| Теория и техника помехоустойчивого кодирования | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1984-03-30—Публикация

1981-11-26—Подача