2. Устройство по п. 1, отличающееся тем, что, блок управления содержит генератор импульсо распределитель импульсов, элемент НЕ, элемент ИЛИ-НЕ, элемент И, ключ, генератор одиночных импульсов, коммутатор, триггер и элемент ИЛИ, причем выход генератора импульсов соединен с входом распределителя импульсов и через элемент НЕ - с. первыми входами элементов ИЛИ-НЕ и И, вторые входы которых соединены соответственно с первым и вторым выходами распределителя импульсов, выходы которого соединены с первым выходом блока управления, первый выход распределителя импульсов подключен к первому входу элемента ИЛИ, выход элемента И соединен с первыми входами триггера и генератора одиночных

импульсов, второй вход и выход которого соединены соответственно с выходом ключа и информационным входом коммутатора, управляющий вход которого является входом задания режима блока управления, управляющий и информационный входы ключа соединены соответственно с входом начального запуска и входом нулевого потенциала блока управления, первый выход коммутатора соединен с вторым входом триггера, выход которого соединен с вторым входом элемента ИЖ, выходы с второго по восьмой блока управления соединены соответств енно с выходом элемента ИЛИ-НЕ, вторым выходом коммутатора,выходом генератора импульсов ,выходом элемента И,первым выходом распределителя импульсов,выходом элемента ИЛИ и выходом триггера,

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Вычислительное устройство | 1982 |

|

SU1070545A1 |

| Вычислительное устройство | 1983 |

|

SU1144105A2 |

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Квадратор | 1983 |

|

SU1180885A1 |

| Квадратор | 1986 |

|

SU1322273A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

I. УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭКСПОНЕНЦИАЛЬНОЙ ФУНКЦИИ по авт.св. №896619, от л ич а rout е е с я тем, что, с целью расширения класса решаемых задач путем дополнительного вычисле.ния логарифмической функции, в него введены блок управления, третий регистр сдвиг га, регистр аргумента, второй и третий элементы ИЛИ, четвертый, пятый и шестой элементы И, второй элемент задержки, третий триггер, коммутатор и схема сравнения, причем первый выход Склока управления соединен с входом регистра аргумента, выход которого соединен с первым информационным входом схемы сравнения, вХод синхронизации которой соединен с вторым выходом блока управления, третий выход которого подключен к первому входу первого триггера, второй вход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом схемы сравнения, второй игформационный вход которок соединен с выходом коммутатора, первый информационный вход которого соединен с информационным входом третьего регистра сдвига и выхо- / дом третьего элемента ИЛИ, первый вход которого соединен с прямым выходом третьего триггера, первый .вход которого соединен с выходом пятого элемента И, первый вход которого соединен с прямым выходом первого триггера, входы синхронизации первого, второго и третьего регистров сдвига соединены с четвертым выходом блока управления, пятый выход которого соединен с вторым входом четвертого элемента И,-шестой выход блока управления соединен с вторыми входами .Q второго и пятого элементов И и вхо$ дом сброса схемы сравнения, седьмой сл выход блока управления соединен с с входами записи первого и второго регистров сдвига, восьмой выход блока управления сое1динен с входами ввода данных второго и записи третьего регистров сдвига и вторым входом вто. рого элемента ИЛИ, входы ввода данных первого и третьего регистров ел vj сдвига соединены с входом нулевого : потенциала устройства, вход задания г 4; 1 режима которого соединен с управляющим входом коммутатора, второй информационный вход которого соединен с выходом первого элемента ИЛИ, выход третьего регистра сдвига соединен с первым входом шестого элемента И и вторым входом третьего тригг.ера, инверсный выход которого соединен через второй элемент задержки с вторым входом шестого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ.

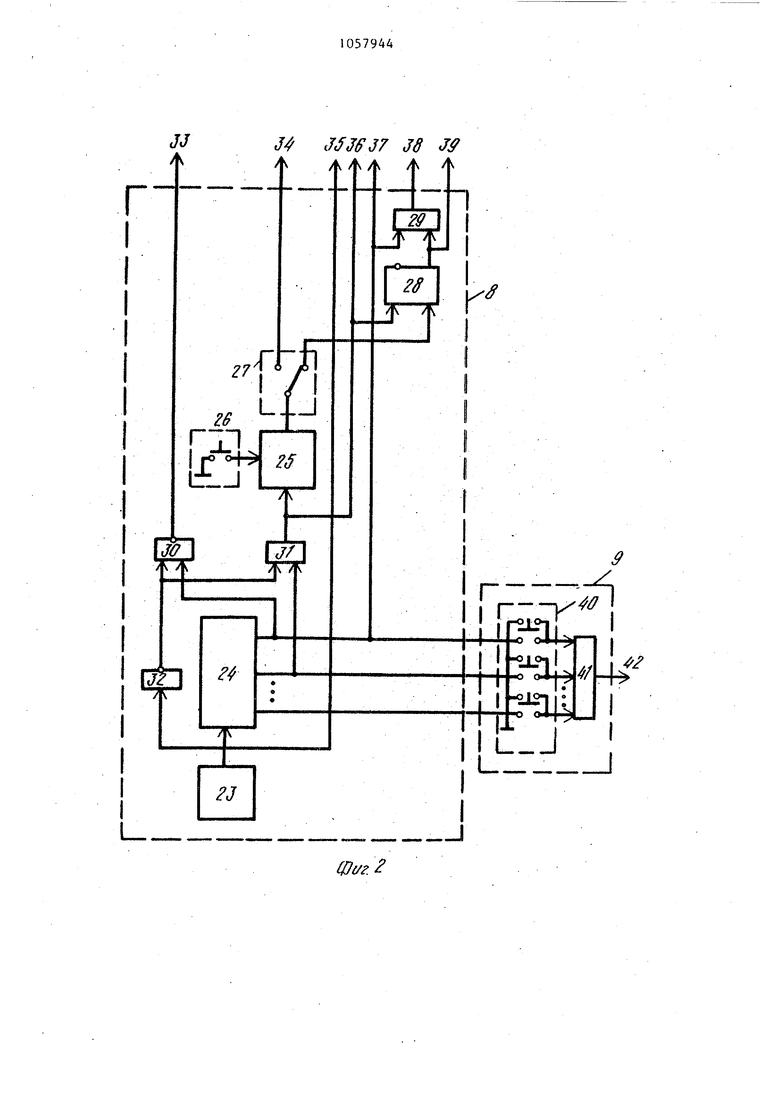

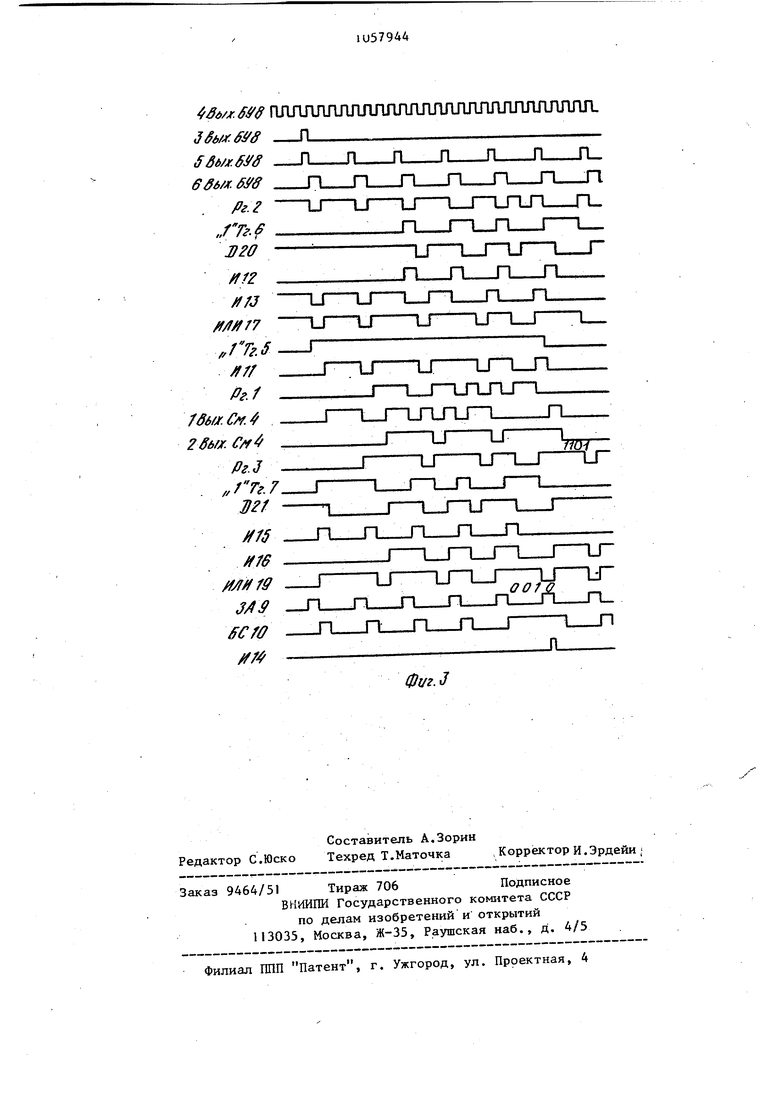

Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительнь1х устройствах и устройствах дискретной автоматики для вычисления экспоненциальной или логарифмической функции. По основному авт.св. № 896619 известно устройство, содержащее два регистра сдвига, сумматор, два триггера, три элемента И, элемент ИЛИ и элемент задержки, причем первый выход сумматора соединен через первый регистр сдвига с его первым входом, первый вход и прямой выход первого триггера соединены соответственно с входной шиной устройства и с перBbiM входом первого элемента И, выход которого соединен с вторым входом сумматора, второй выход которого сое динен с первым входом второго элемен та И, выход которого соединен с первым входом второго триггера, второй вход которого подключен к выходу вто рого регистра сдвига и к первому вхо ду третьего элемента И, второй вход которого через первый элемент задержки соединен с инверсным выходом второго триггера, прямой выход которого подключен к первому входу первого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом третьего элемента И и с вторым входом первого элемента И, подключенного вторым входом к входу BTopqro регистра сдвига ij . Недостаток устройства заключается в ограниченных функциональных возможностях. Цель изобретения - расширение класса решаемых задач Путем дополнительного вычисления логарифмической функции. Поставленная цель достигается тем, что в устройство для вычисления экспоненциальной функции дополнительно введены блок управления, третий регистр сдвига, регистр аргумента, второй и третий элементы ИЛИ, четвертый, пятый и шестой элементы И, второй элемент задержки, третий триггер коммутатор и схема сравнения, причем первый выход блока управления соединен с входом регистра аргумента, выход которого соединен с первым информационным входом схема сравнения, вход синхронизации которой соединен с вторым выходом блока управления, третий выход которого подключен к первому входу первого триггера, второй вход кото-, роге соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом схемы сравнения, второй информационный вход которой соединен с выходом коммутатора, первый информационный вход которого соединен с информационным входом третьего регистра сдвига и выходом третьего элемента ИЛИ, первый вход которого соединен с прямым выходом третьего триг гера, первый вход которого соединен с выходом пятого элемента И, первый вход которого соединен с прямым выхо дом первого триггера, входы синхронизации первого, второго и третьего регистров сдвига соединены с четвертым выходом блока управления, пятый выход которого соединен с вторым вхо дом четвертого-элемента И, шестой выход блока управления соединен с вторыми входами второго и пятого эле ментов И и входом сброса схемы сравнения, седьмой выход блока управления соединен с входами записи первого и второго регистров сдвига, восьмой выход блока управления соединен с входами ввода данных второго и записи третьего регистров сдвига и вторым входом второго элемента ИЛИ, входы ввода данных первого и третьего регистров сдвига соединены с входом нулевого потенциала устройства, вход задания режима которого соединен с управляющим входом коммутатора, второй информационный вход которого соединен с выходом первого элемента ИЛИ, выход третьего регистра сдвига соединен с первым входом шестого элемента И и вторым входом третьего триггера, инверсный выход которого соединен через второй элемент задержки с вторым входом шестого эле мента И, выход которого соединен-с вторым входом третьего элемента ИЛИ, Причем блок управления содержит генератор импульсов, распределитель импульсов, элемент НЕ, элемент ИЛИНЕ, элемент И, ключ, генератор одиночных импульсов, коммутатор, триггер и элемент ИЛИ, причем выход генератора импульсов соединен с входом распределителя импульсов и через элемент НЕ - с первыми входа.ми элементов ИЛИ-НЕ и И, вторые йходы которых соединены соответственно с пер 444 вым и вторым выходами распределителя импульсов, выходы которого соединены с первым выходом блока управления, первый выход распределителя импульсов подключен к первому входу элемента ИЛИ, выход элемента И соединен с первыми входами триггера и генератора одиночных импульсов, второй вход и выход которого соединелы соответственно с выходом ключа и информационным входом коммутатора, управляющий вход которого является входом задания режима блока управления, управляющий и информационный входы ключа соединены соответственно с входом начального запуска и входом нулевого потенцигша блока управления, первый выход коммутатора соединен с вторым входом триггера, выход которого соединен с вторым входом элемента ИЛИ, выходы с второго по восьмой блока управления соединены соответственно с выходом элемента ИЛИНЕ, вторым выходом коммутатора, выходом генератора импульсов, выходом элемента И, первым выходом распределителя импульсов, выходом элемента ИЛИ и выходом триггера. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок-схема блока управления и регистра аргумента; на фиг. 3 - поясняющие работу, устройства диаграммы. Устройство для вычисления экспоненциальной функции содержит регистры 1-3 сдвига, сумматор 4, триггеры 5-7, блок 8 управления, регистр 9 аргумента, схему 10 сравнения, элементы И 11-16 элементы ИЛИ 17-19, элементы 20 и 21 задержкии коммутатор 22. Блок управления содержит генератор 23 импульсов, распределитель 24 импульсов, генератор 25 одиночных импульсов, ключ 26, коммутатор 27, триггер 28, элемент HJM 29, элемент ИЛИ-НЕ 30, элемент И 31, элемент НЕ 32, выходы 33-39 блока управления. Регистр аргумента содержит коммутатор 40 элемент ИЛИ 41 и выход регистра 42, Устройство для вычисления экспоненциальной функции работает следующим образом. Генератор 23 тактовых импульсов блока 8 управления вырабатывает последовательность импульсоЕ), из которых распределитель 24 импульсов на п каналов (где п - количество разрядов регистров 1-3 сдвига) формирует п последовательностей импульсов длительностью (/г-г (где f - тактовая частота генератора 23) с периодом и сдвинутых друг относительно друга на время .

С помощью коммутатора 40, который может быть выполнен в виде л-разрядного клавишного переключателя, набирают дополнительный двоичньй код отрицательного значения аргумента дпя вычисления экспоненциальной функции либо прямой двоичный код положительного значения аргумента для вычисления логарифмической функции. Коммутатор 40 подключает в единичных разрядах соответствующие выходы распределителя 24 импульсов к входам элемента ИЛИ 41, на выходе которого формируется последовательный п-разрядный двоичный код набранного значения аргумента.

В исходном состоянии коммутатором 27 блока 8 управления подключают выход генератора 25 одиночных импульсов к второму входу триггера 28. Затем с помощью ключа 26 запускают генератор 25 одиночных импульсов, на вход которого поступает последовательность импульсов с выхода элемента И 31, которая формируется из инвертированных элементом НЕ 32 тактовых импульсов и сигналов п-1-го выхода распределителя 24 импульсов.

Выходной сигнал генератора 25 одиночных импульсов устанавливает триггер 28 в единичное .состояние, в котором он находится до следующего импульса, действующего на выходе элемента И 31. Единичный сигнал прямого выхода триггера 28 поступает по шине 39 на восьмой выход блока 8 управления и далее на вход ввода данных регистра 2 сдвига, вход .записи регистра 3 сдвига и через элемент ИЛИ 18 на второй вход триггера 5, сбрасывая его в нулевое состояние. Одновременно единичный сигнал триггера 28 через элемент ИЛИ 29 поступает по щине 38 на.седьмой выход блока 8 управления и далее на входы записи регистров 1 и 2 сдвига. Так как входы ввода данных регистров 1 и 3 сдвига соединены с шиной логического нуля, то под действием тактовых импульсов четвертого выхода блока 8 управления в разряды регистров 1 и 3 сдвига записываются нулевые коды. Поскольку на вход ввода данных регистра 2 сдвига поступает единичный сигнал в течение п тактов с седьмого выхода блока 8 управления, то под действием тактовых импульсов четвертого выхода блока 8 управления во все разряды регистра 2 сдвига записываются единичные коды. В процессе сдвига с выходов регистров 2 и 3 информации, сформированного в результате предшествующей работы устройства, триггеры 6 и 7 устанавливаются в нулевое состояние, элементы И 12 и 15 блокированы нулевыми сигналами выхода переноса сумматора 4 и прямого выхода триггера 5 соответственно.

Таким образом, в исходном состоя- НИИ в регистрах 1 и 3 сдвига-во всех разрядах содержится нулевой код, а в регистре 2 сдвигаво всех разрядах единичны) код, кроме старшего п-го,

так как после сброса триггера 28 на входе ввода данных регистра 2 сдвига действует нулевой сигнал, а на вход записи регистра 2 сдвига в каждом п-ом такте через элемент ИЛИ 29

поступает единичный сигнал п-го выхода распределителя 24 импульсов. По этой же причине в п-ом разряде кода, формируемого в процессе вычислений в регистре И сдвига, всегда записан

ноль.

После установки устройства в исходное состояние коммутатором 27 подключают выход генератора 25 одиночных импульсов к щине 34, которая

соединена с первым входом триггера 5. Затем коммутатором 22 устанавливают режим работы устройства. Коммутатор 22 подключает второй информационный вход блока 10 сравнения

к выходу элемента ИЛИ 19 в режиме вычислеш-1Я экспоненциальной функции либо к выходу элемента ИЛИ 17 в режиме вычисления логарифмической функции.

В режиме вычисления функции от начальных условий Уо 1, в регистрах 2 и 3 сдвига формируются двоичные коды функции и аргумента соответственно. В режиме вычисления функции от начальных условий у.0, Хо 1 двоичные коды функции -и аргумента формируются в регистрах 3 и 2 сдвига соответственно. Работа устройства в режимах вычисле ния экспоненциальной н логарифмической функций аналогична. Запуск процесса вычислений осуществляется кнопочным переключателем, который запускает генератор 25 одиночных импульсов блока 8 упра ления. Выходной импульс генератора 25 одиночных импульсов поступает с третьего выхода блока 8 управления на первый вход-триггера 5, устанавливая его в единичное состояние, в котором сигнал прямого выхода триггера 5 снимает блокировку элементов И 11 и 15. После установки триггера 5 в еди ничное состояние первый импульс последовательности, синхронизирующей а-е такты работы устройства, поступает с шестого -выхода блока 8 управления через элемент И 15 на первьшг вход триггера 7 и устанавливает его в единичное состояние,в котором он находится п тактов, так ка с выхода регистра 3 сдвигаются нуле вые сигналы. Единичный сигнал прямого выхода триггера 7 через элемен ИЛИ 19 поступает на информационный вход регистра 3 сдвига, во все разряды которого под действием тактовы импульсов записываются единичные коды, что соответствует дополнитель ному коду единицы младшего разряда. Второй импульс последовательност шестого выхода блока 8 управления , поддерживает триггер 7 в единичном состоянии в течение .очередного п-го такта, что обеспечивает запись в п-й разряд кода регистра 3 сдвига единичного сигнала отрицательного знака. В следующем такте единичный сигнал первого разряда кода, сдвигаемого, с выхода регистра 3, сбрасы вает триггер 7 в нулевое состояние. Элемент 21 задержки на такт поддерживает на выходе в течение этого та та нулевой сигнал инверсного выхода триггера 1 его предыдущего состояния j что обеспечивает блокировку элемента И 16 и стирание единицы в первом разряде кода, сдвигаемого с выхода регистра 3 сдвига, так как на первом и втором входах элемента ИЛИ 19 действуют нулевые сигналы выхода элемента И 16 и прямого выхо да-триггера 7. К моменту сдвига с вьп:ода регистра 3 второго разряда к да на выходе элемента 21 задержки устанавливается единичный сигнал, который снимает блокировку элемента И 16, что обеспечивает подключение выхода регистра 3 сдвига к его информационному входу через элементы И 16 и ИЛИ 19. Таким образом, после второго шага вычислений в ре-, гистре 3 сдвига формируется дополнительный двоичный код 111... 10..На последующих шагах в регистре 3 сдвига формируется аналогичным образом дополнительный двоичный код отрицательного значения аргумента э кспоненциальной функции или отрицательного значения логарифмической функции. Рассмотрим процесс формирования кодов в регистрах 1 и 2 сдвига с момента установки триггера 5 в единичное состояние. В это время единичный сигнал инверсного выхода триггера 6 через элемент 20 задержки на такт действует на втором входе элемента И 13, а на первом входе элемента ИЛИ I7 действует нулевой сигнал прямбго выхода триггера 6. Начальный двоичный код 011I ... 1 сдвигается с выхода регистра 2 через элемент И 13, ИЛИ 17 и И II на второй вход сумматора 4 и с его первого выхода суммы поступает на информационный вход регистра 1 сдвига и записывается в него на время п тактов под действием тактовых импульсов четвертого выхода блока 8 управления, В следующие п тактов (на втором шаге вычислений) на первый вход сумматора 4 с выхода регистра 1 сдвигается двоичный код 0111 ... 1, а на второй вход сумматора ч поступает с выхода регистра 3 сдвига через элементы И 13, krffl 17 и И 11 такой же двоичный код 0111...1. В результате суммирования последовательнь1м двоичнь1м сумматором 4 на его втором выходе формируется сигнал переноса в п-й разряд, который приводит к срабатыванию элемента И 12 в момент п-го такта. Триггер 6 устанавливается в единичное состояние и поддерживается в нем в течение п-го такта. В это время на входе записи регистров 1 и 2 сдвига действует импульс п-го такта с седьмого выхода блока 8 управления, который блокирует запись .единичного сигнала в п-е разряды кодов регистров I и 2 сдвига. Триггер 6 сбрасывается в нулевое состояние единичным сигналом парного разряда кода, сдвигаемого с выхо да регистра 2. Элемент 20 задержки на такт поддерживает на выходе в те чение такта нулевой сигнал инверсно го выхода триггера 6 его предыдущего состояния, что обеспечивает блокировку элемента И 13 во время сдви га первого разряда кода с выхода регистра 2 сдвига. На первом и втором входах элемента ИЛИ 17 действуют нулевые сигналы прямого выхода триггера 6 и выхода элемента И 13 соответственно. Нулевой сигнал выхо да элемента ИЛИ 17 обеспечивает запись нули в первом разряде кода, сдвигаемого в регистре 2. К моменту сдвига с выхода регистра 2 второго разряда-кода на выходе элемента 20 задержки устанавливается единичный сигнал, который открывает элемент И 13. Таким образом, остальные разряды кода, начиная с второго разряда, поступают с выхода регистра 2 сдвига на его информационный вход через элементы И 3 и И.ПИ 17 без изменения. В регистр 2 сдвига записывается двоичный код 0111.10, который также с выхода элемента ИЛИ 1 через элемент И I1 поступает на вто рой вход сумматора 4, на первый вхо которого сдвигается содержимое регистра 1 сдвига. Дальнейшие вычисления выполняются аналогичным образом, причем за время п тактов про изводится каждый последуюишй таг вы числений. В режиме вычисления экспоненциальной функции вычисление выполняет ся до тех пор пока па вглходе элемен та ИЛИ 19 не сформируется дополнительный последовательный двоичный к аргумента, который равен заданному на коммутаторе 40 задатчика 9 значению аргумента. В этом случае срабатывает блок 10 сравнения, на выходе которого формируется единичный сигнал, открывающий элемент И 14. Импульсьгый сигнал пятого выхода блока 8 управления проходит через элементы И 14 и ИЛИ 18 на второй вход триггера 5 и сбрасывает его в нулевое состояние, в котором сигнал его прямого входа блокирует элементы И 11 и 15. В регистрах 2 и 3 сдвига фиксируются динамическим способом двоичный код экспоненциальной функции и дополнительный код отрицательного значения аргумента. В режиме вычисления логарифмиЧеской функции вычисления выполняются до тех пор, пока на выходе элемента ИЛИ 17 не с.,формируется двоичный код аргумента, который .равен заданному на задатчике 9 значению аргумента. В этом случае аналогичным образом срабатывает блок 10 сравнения, триггер 5 сбрасывается в нуле- вое состояние, элементы И 11 и 15 блокируются сигналом прямого выхода триггера 5, а в регистрах 3 и 2 сдвига фиксируются динамическим способом дополнительный код отрицательного значения логарифмической функции и прямой код положительного значения аргумента соответственно. На фиг, 3 приведена временная диаграмма для случая вычисления логарифмической функции при . Положительный уровень соответствует единичному значению сигнала. Заданное значение аргумента равно 0.100, где точкой отделен знаковьй разряд.

JJ

J J JffJ7 Jd Jff

L

ф1/г.2

aL

10,1

/

t

.I

lЛJlГlЛJшnгlЛJlГlnлJlruшJmrlлллJг L

Авторы

Даты

1983-11-30—Публикация

1982-03-24—Подача