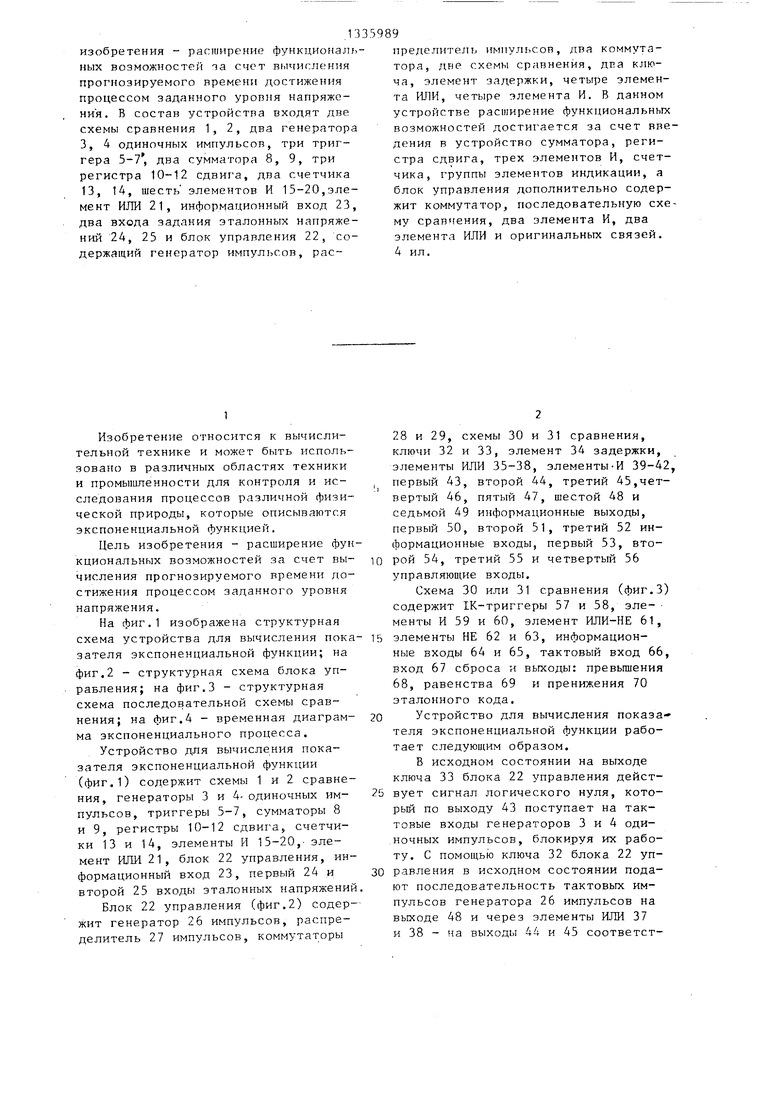

изобретения - расширение функциональных возможностей ia счет причисления прогнозируемого времени достижения процессом заданного уровня напряжения. В состав устройства входят две схемы сравнения 1, 2, два генератора 3, 4 одиночных импульсов, три триггера 5-7, два сумматора 8, 9, три регистра 10-12 сдвига, два счетчика 13, 14, шесть элементов И 15-20,элемент ИЛИ 21, информационный вход 23, два входа задания эталонных напряжений 24, 25 и блок управления 22, содержащий генератор импульсов, рас1

Изобретение относится к вычислительной технике и может быть исполь- в различных областях техники и промышленности для контроля и исследования процессов различной физической природы, которые описываются экспоненциальной функцией.

Цель изобретения - расширение функциональных возможностей за счет вычисления прогнозируемого времени достижения процессом заданного уровня напряжения.

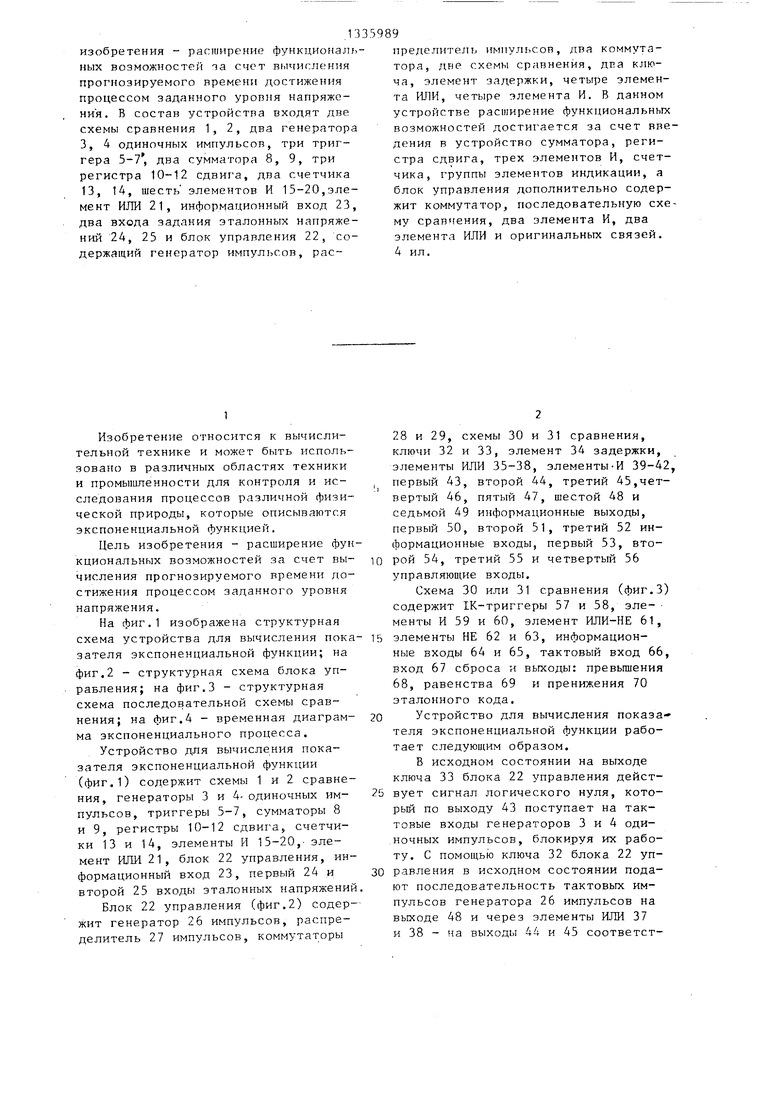

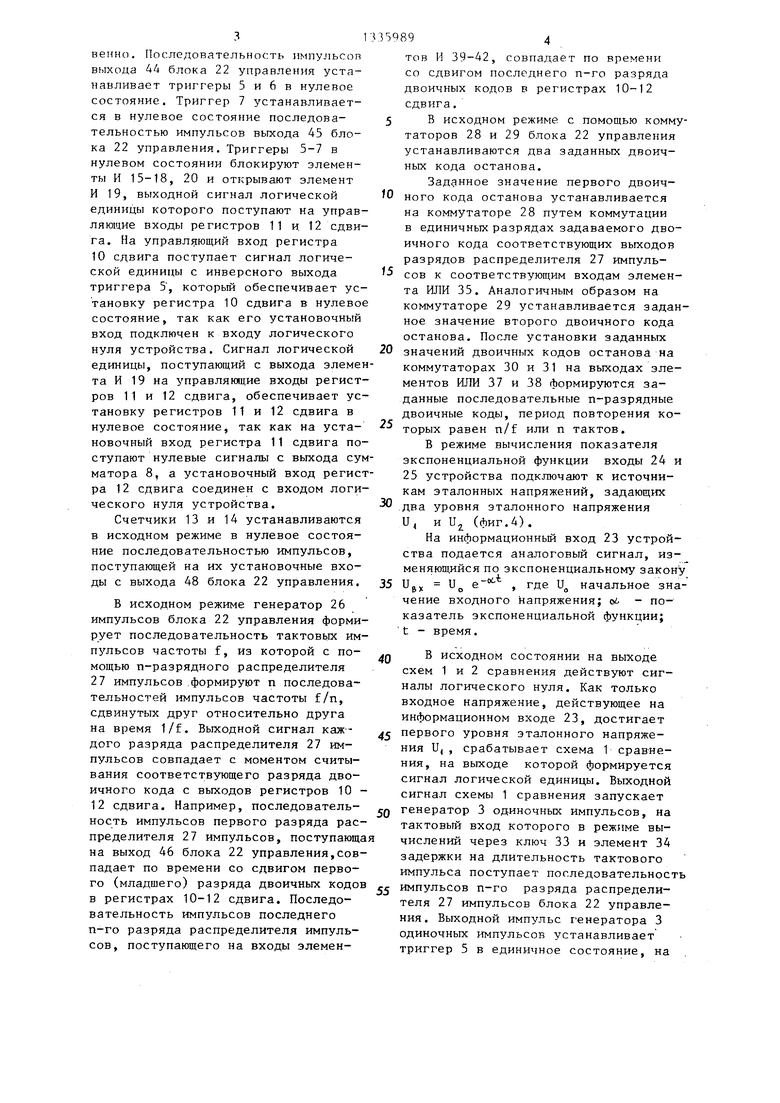

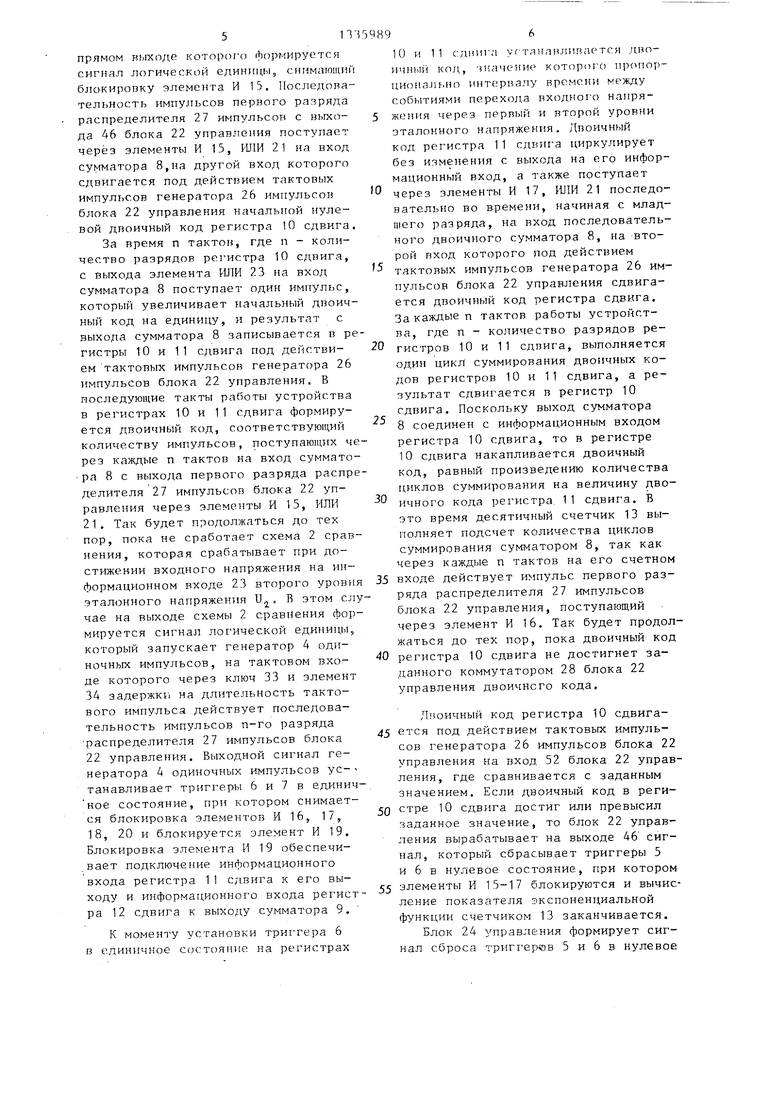

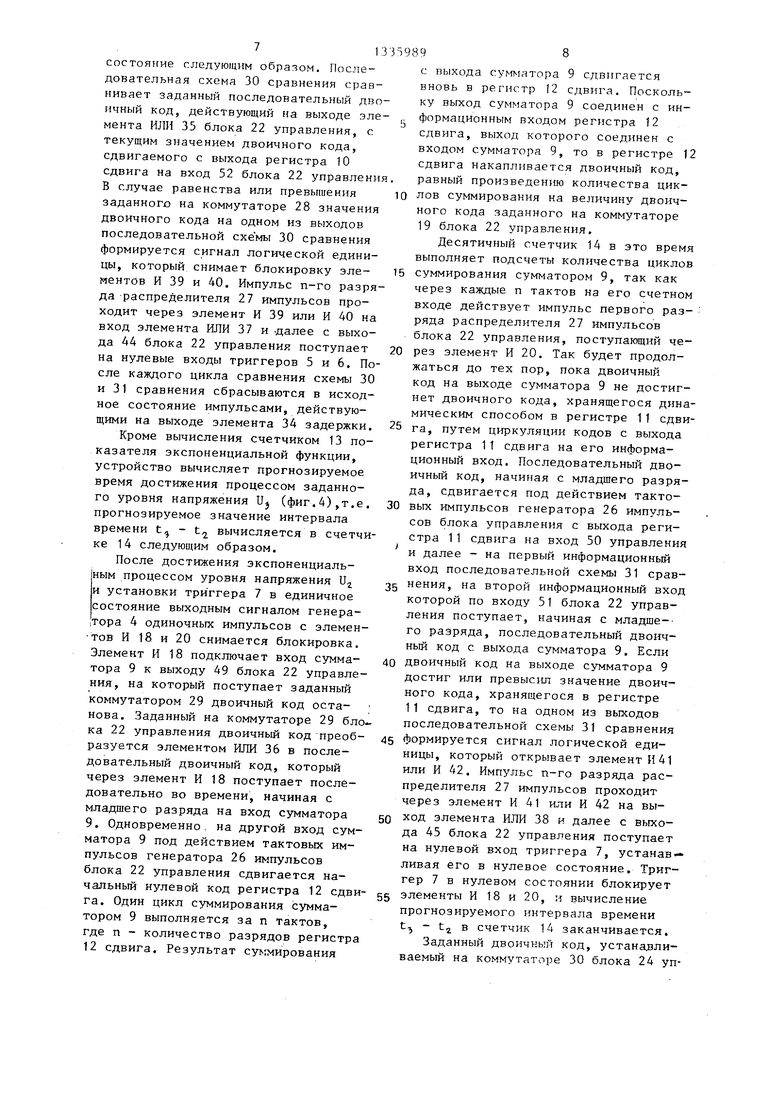

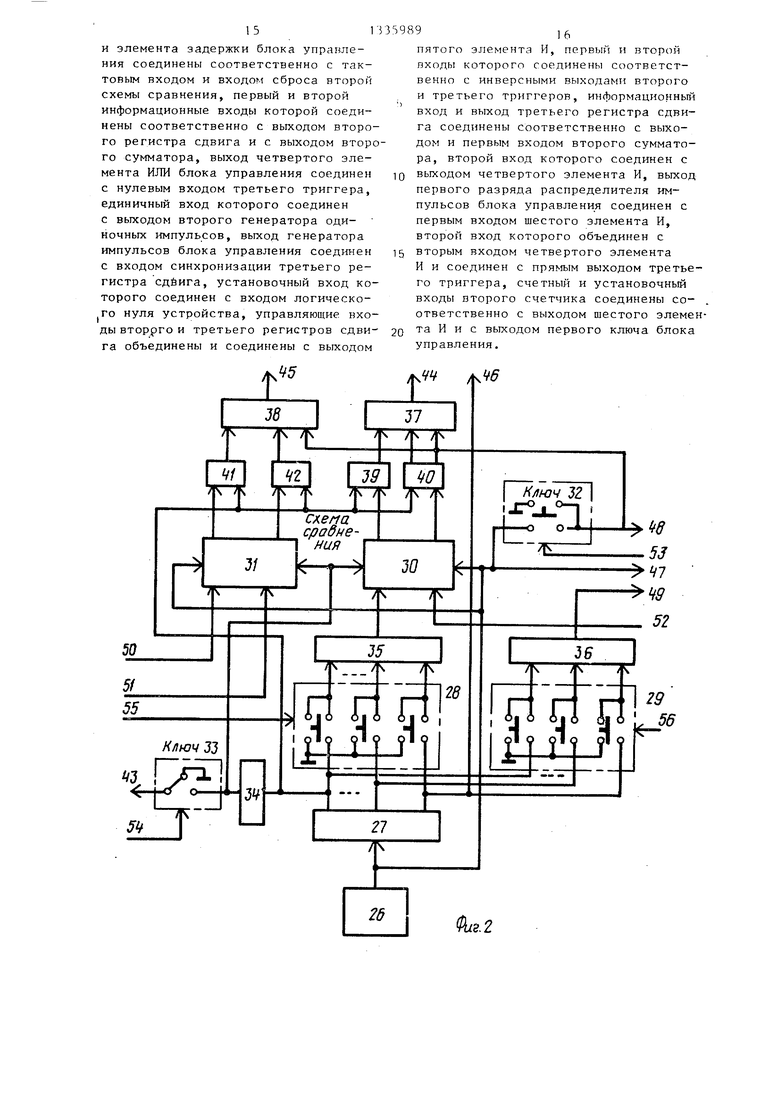

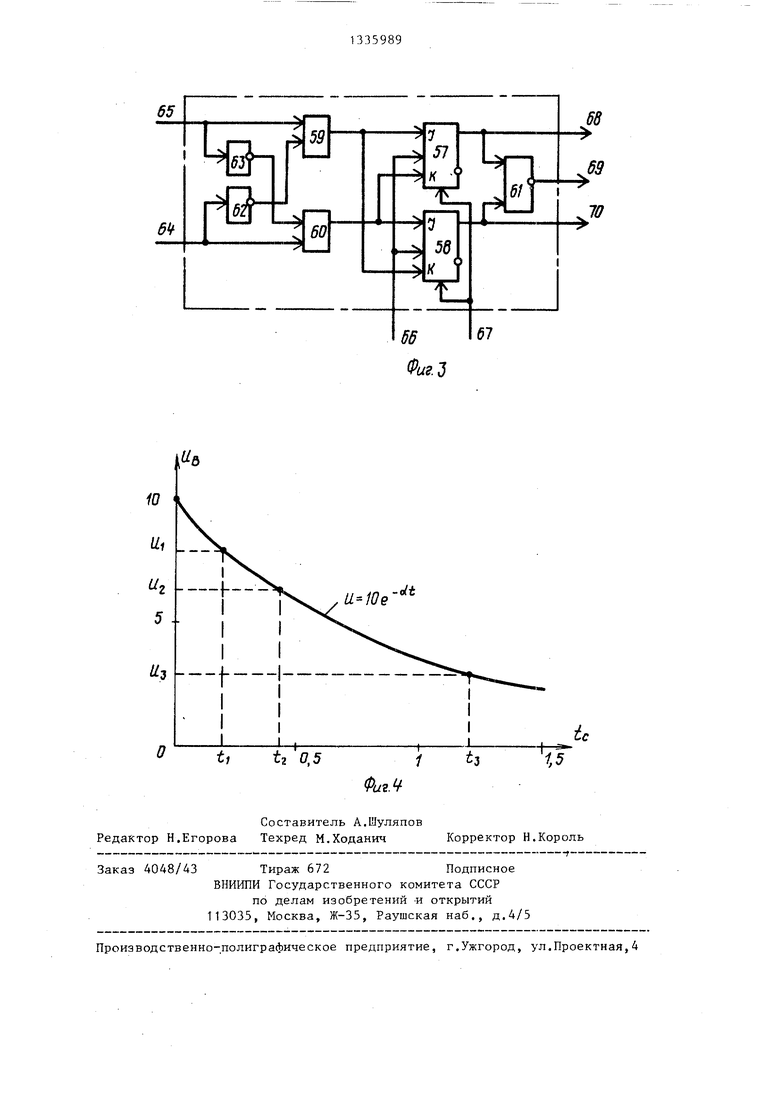

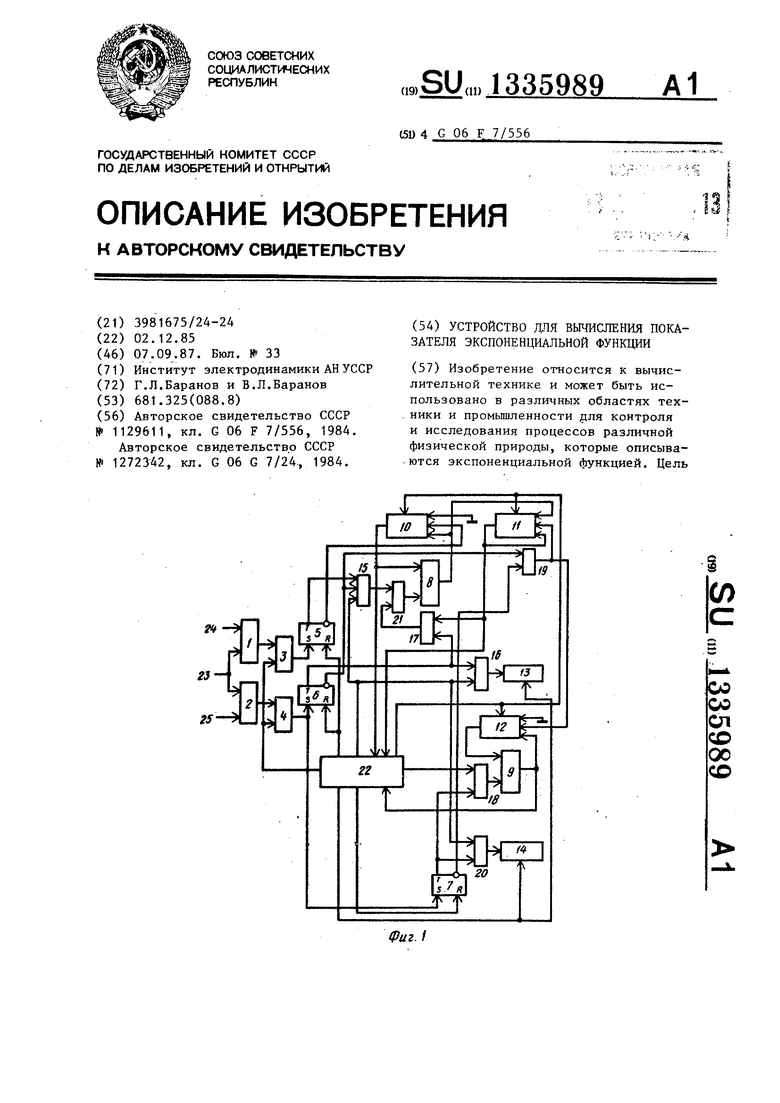

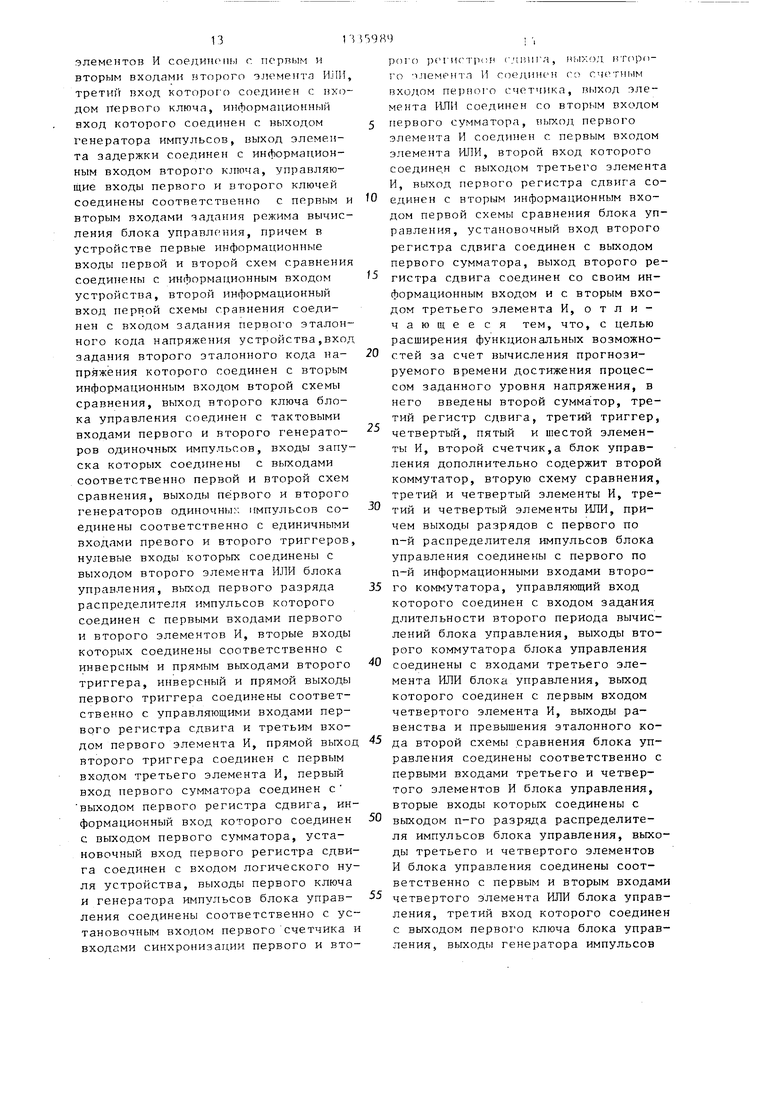

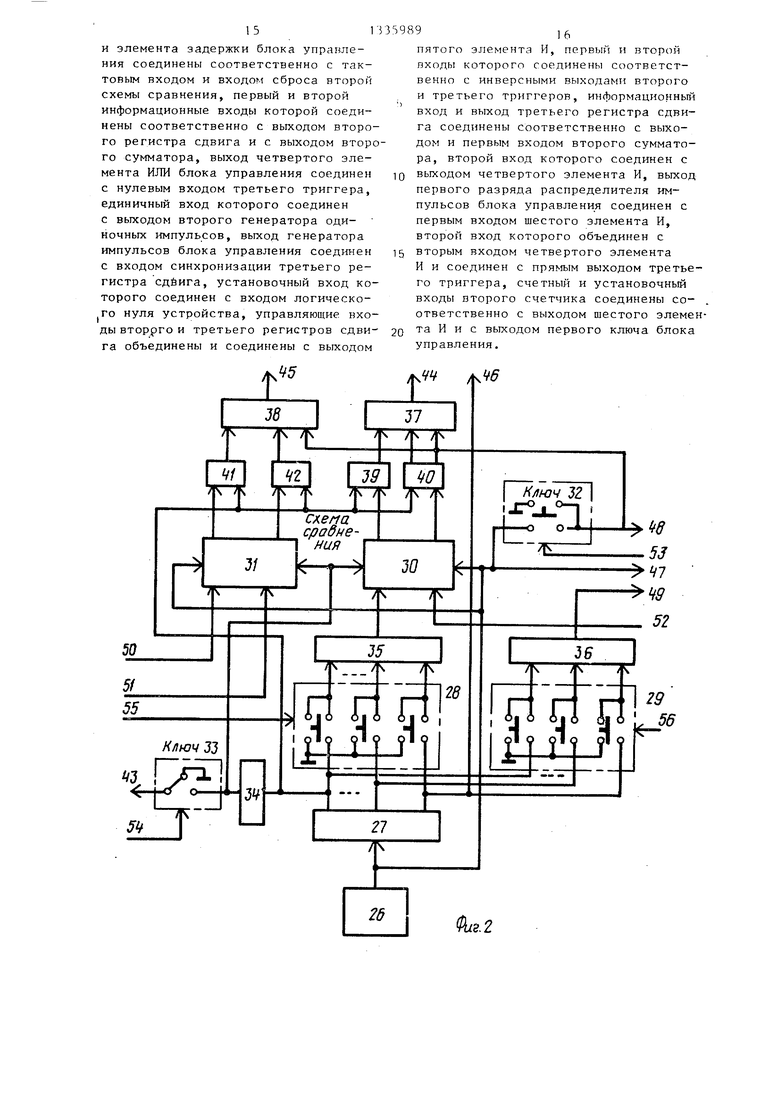

На фиг.1 изображена структурная схема устройства для вычисления показателя экспоненциальной функции; на фиг,2 - структурная схема блока управления; на фиг.З - структурная схема последовательной схемы сравнения; на фиг.4 - временная диаграмма экспоненциального процесса.

Устройство для вычисления показателя экспоненциальной функции (фиг.1) содержит схемы 1 и 2 сравнения, генераторы 3 и 4- одиночных импульсов, триггеры 5-7, сумматоры 8 и 9, регистры 10-12 сдвига, счетчики 13 и 14, элементы И 15-20,- элемент ИЛИ 21, блок 22 управления, информационный вход 23, первый 24 и второй 25 входы эталонных напряжений

Блок 22 управления Сфиг,2) содержит генератор 26 импульсов, распределитель 27 импульсов, коммутаторы

пределитель импульсов, два коммутатора, две схемы сравнения, два ключа, элемент задержки, четыре элемента ИЛИ, четыре элемента И. В данном устройстве расширение функциональных возможностей дости1 ается за счет введения в устройство сумматора, регистра сдвига, трех элементов И, счетчика, группы элементов индикации, а блок управления дополнительно содержит коммутатор, последовательную схему сравнения, два элемента И, два элемента ИЛИ и оригинальных связей. 4 ил.

28 и 29, схемы 30 и 31 сравнения, ключи 32 и 33, элемент 34 задержки, элементы ИЛИ 35-38, элементы-И 39-42, первый 43, второй 44, третий 45,четвертый 46, пятый 47, шестой 48 и седьмой 49 информационные выходы, первый 50, второй 51, третий 52 информационные входы, цервый 53, второй 54, третий 55 и четвертый 56 управляюп(ие входы.

Схема 30 или 31 сравнения (фиг.З) Содержит 1К-триггеры 57 и 58, эле- - менты И 59 и 60, элемент ИЛИ-НЕ 61,

элементы НЕ 62 и 63, информационные входы 64 и 65, тактовый вход 66, вход 67 сброса и выходы: превышения 68, равенства 69 и пренижения 70 эталонного кода.

Устройство для вычисления показателя экспоненциальной функции работает следующим образом.

В исходном состоянии на выходе ключа 33 блока 22 управления действует сигнал логического нуля, который по выходу 43 поступает на тактовые входы генераторов 3 и 4 одиночных импульсов, блокируя их работу. С помощью ключа 32 блока 22 управления в исходном состоянии подают последовательность тактовых импульсов генератора 26 импульсов на выходе 4В и через элементы ИЛИ 37 и 38 - на выходы 44 и 45 соответственно. Последовательность импульсоп выхода 44 блока 22 управления устанавливает триггеры 5 и 6 в нулевое состояние. Триггер 7 устанавливается в нулевое состояние последовательностью импульсов выхода 45 блока 22 управления. Триггеры 5-7 в нулевом состоянии блокируют элементы И 15-18, 20 и отгфывают элемент И 19, выходной сигнал логической единицы которого поступают на управляющие входы регистров 11 и. 12 сдвига. На управляющий вход регистра 10 сдвига поступает сигнал логической единицы с инверсного выхода триггера 5, который обеспечивает установку регистра 10 сдвига в нулевое состояние, так как его установочный вход подключен к входу логического нуля устройства. Сигнал логической единицы, поступающий с выхода элемента И 19 на управляющие входы регистров 11 и 12 сдвига, обеспечивает установку регистров 11 и 12 сдвига в нулевое состояние, так как на установочный вход регистра 11 сдвига поступают нулевые сигналы с выхода сумматора 8, а установочный вход регистра 12 сдвига соединен с входом логического нуля устройства.

Счетчики 13 и 14 устанавливаются в исходном режиме в нулевое состояние последовательностью импульсов, поступающей на их установочные входы с выхода 48 блока 22 управления.

В исходном режиме генератор 26 импульсов блока 22 управления формирует последовательность тактовых импульсов частоты f, из которой с помощью п-разрядного распределителя 27 импульсов формируют п последовательностей импульсов частоты f/n, сдвинутых друг относительно друга на время 1/f. Выходной сигнал каждого разряда распределителя 27 импульсов совпадает с моментом считывания соответствующего разряда двоичного кода с выходов регистров 10 - 12 сдвига. Например, последовательность импульсов первого разряда распределителя 27 импульсов, поступающа на выход 46 блока 22 управления,совпадает по времени со сдвигом первого (младшего) разряда двоичных кодов в регистрах 10-12 сдвига. Последовательность импульсов последнего п-го разряда распределителя импульсов, поступающего на входы элемен0

5

0

5

0

5

0

5

0

5

тон и 39-42, совпадает по времени со сдвигом последнего п-го разряда двоичных кодов в регистрах 10-12 сдвига.

В исходном режиме с помощью коммутаторов 28 и 29 блока 22 управления устанавливаются два заданных двоичных кода останова.

Заданное значение первого двоичного кода останова устанавливается на коммутаторе 28 путем коммутации в единичных разрядах задаваемого двоичного кода соответствующих выходов разрядов распределителя 27 импульсов к соответствующим входам элемента ИЛИ 35. Аналогичным образом на коммутаторе 29 устанавливается заданное значение второго двоичного кода останова. После установки заданных значений двоичных кодов останова на коммутаторах 30 и 31 на выходах элементов ИЛИ 37 и 38 формируются заданные последовательные п-разрядные двоичные коды, период повторения которых равен n/f или п тактов.

В режиме вычисления показателя экспоненциальной функции входы 24 и 25 устройства подключают к источникам эталонных напряжений, задающих два уровня эталонного напряжения и и и (фиг.4).

На информационный вход 23 устройства подается аналоговый сигнал, изменяющийся по экспоненциальному закону Ug и е , где U начальное значение входного напряжения; oi- - показатель экспоненциальной функции; t - время.

В исходном состоянии на выходе схем 1 и 2 сравнения действуют сигналы логического нуля. Как только входное напряжение, действующее на информационном входе 23, достигает первого уровня эталонного напряжения и,, срабатывает схема 1 сравнения, на выходе которой формируется сигнал логической единицы. Выходной сигнал схемы 1 сравнения запускает генератор 3 одиночных импульсов, на тактовый вход которого в режиме вычислений через ключ 33 и элемент 34 задержки на длительность тактового импульса поступает пог.ледовательность импульсов п-го разряда распределителя 27 импульсов блока 22 управления. Выходной импульс генератора 3 одиночных импульсов устанавливает триггер 5 в единичное состояние, на

5n

прямом выходе которого формируется сигнал логической единицы, ctniMaioiHur блокировку элемента И 15. Последовательность импульсов первого разряда распределителя 27 импульсов с выхода 46 блока 22 управления поступает через элементы И 15, Ш1И 21 на вход сумматора 8,на другой вход которого сдвигается под действием тактовых импульсов генератора 26 импульсов блока 22 управления начальной нулевой двоичный код регистра 10 сдвига За время п тактов, где п - количество разрядов регистра 10 сдвига, с выхода элемента Ш 1И 23 на вход сумматора 8 поступает один импульс, который увеличивает начальный двоичный код на единицу, и результат с выхода сумматора 8 записывается в регистры 10 и 11 сдвига под действием тактовых импульсов генератора 26 импульсов блока 22 управления. В последующие такты работы устройства в регистрах 10 и 11 сдвига формируется двоичный код, соответствующий количеству импульсов, поступающих через каждые п тактов на вход суммато- ра 8 с выхода первого разряда распределителя 27 импульсов блока 22 управления через элементы И 15, ИЛИ 21, Так будет продолжаться до тех пор, пока не сработает схема 2 сравнения, которая срабатьшает при достижении входного напряжения на информационном входе 23 второго уровня эталонного напряжения U. В этом случае на выходе схемы 2 сравнения формируется сигнал логической единицы, который запускает генератор А одиночных импульсов, на тактовом входе которого через ключ 33 и элемент 34 задержки на длительность тактового импульса действует последовательность импульсов п-го разряда распределителя 27 импульсов блока 22 управления. Выходной сигнал генератора 4 одиночных импульсов ус- танавливает триггеры 6 и 7 в единич- ное состояние, при котором снимается блокировка элементов И 16, 17, 18, 20 и блокируется элемент И 19. Блокировка элемента И 19 обеспечивает подключение информационного входа регистра 11 сдвига к его выходу и информационного входа регистра 12 сдвига к выходу сумматора 9.

К моменту установки триггера 6 в единичное состоянт е на регистрах

5

9896

10 и 11 сдиига уС тяипшпшается дво- ичны1 код, значение которог о пропорционально интервалу времени между событиями перехода входного напря- 5 жения через первый и второй уровни эталонного напряжения. Двоичный код регистра 11 сдвига циркулирует без с выхода на его информационный вход, а также поступает 0 через элементы И 17, Ш1И 21 последовательно во времени, начиная с младшего разряда, на вход последователь- тюго двоичного сумматора 8, на второй вход которого под действием тактовых импульсов генератора 26 импульсов блока 22 управления сдвигается двоичный код регистра сдвига. За каждые п тактов работы устройства, где п - количество разрядов ре- 0 гистров 10 и 11 сдвига, выполняется один цикл суммирования двоичных кодов регистров 10 и 11 сдвига, а результат сдвигается в регистр 10 сдвига. Поскольку выход сумматора 8 соединен с информационным входом регистра 10 сдвига, то в регистре 10 сдвига накапливается двоичный код, равный произведению количества циклов суммирования на величину дво- - ичного кода регистра. 11 сдвига. В это время десятичный счетчик 13 выполняет подсчет количества циклов суммирования сумматором 8, так как через каждые п тактов на его счетном 5 входе действует импульс первого разряда распределителя 27 импульсов блока 22 управления, поступающий через элемент И 16. Так будет продолжаться до тех пор, пока двоичный код 0 регистра 10 сдвига не достигнет заданного коммутатором 28 блока 22 управления двоичного кода.

Дтюичный код регистра 10 сдвига- 5 ется под действием тактовых импульсов генератора 26 импульсов блока 22 управления на вход 52 блока 22 управления, где сравнивается с заданным значением. Если двоичный код в реги- 0 стре 10 сдвига достиг или превысил заданное значение, то блок 22 управления вырабатывает на выходе 46 сигнал, который сбрасывает триггеры 5 и 6 в нулевое состояние, при котором 5 элементы И 15-17 блокируются и вычисление показателя экспоненциальной функции счетчиком 13 заканчивается.

Блок 24 управления формирует сигнал сброса триггеров 5 и 6 в нулевое

713

состояние следующим образом. Последовательная схема 30 сравнения сравнивает заданный последовательный двоичный код, действующий на выходе элемента ИЛИ 35 блока 22 управления, с текущим значением двоичного кода, сдвигаемого с выхода регистра 10 сдвига на вход 52 блока 22 управлени В случае равенства или превышения заданного на коммутаторе 28 значения двоичного кода на одном из выходов последовательной схе мы 30 сравнения формируется сигнал логической единицы, который снимает блокировку элементов И 39 и 40. Импульс п-го разряда -распределителя 27 импульсов проходит через элемент И 39 или И 40 на вход элемента ИЛИ 37 и -далее с выхода 44 блока 22 управления поступает на нулевые входы триггеров 5 и 6. После каждого цикла сравнения схемы 30 и 31 сравнения сбрасываются в исходное состояние импульсами, действующими на выходе элемента 34 задержки.

Кроме вычисления счетчиком 13 показателя экспоненциальной функции, устройство вычисляет прогнозируемое время достижения процессом заданного уровня напряжения Uj (фиг.4),т.е. прогнозируемое значение интервала времени t, - t вычисляется в счетчике 14 следующим образом.

После достижения экспоненциальным процессом уровня напряжения U и установки триггера 7 в единичное состояние выходным сигналом генератора 4 одиночных импульсов с элементов И 18 и 20 снимается блокировка. Элемент И 18 подключает вход сумматора 9 к выходу 49 блока 22 управления, на который поступает заданный коммутатором 29 двоичный код останова. Заданный на коммутаторе 29 блока 22 управления двоичный код преобразуется элементом ИЛИ 36 в последовательный двоичный код, который через элемент И 18 поступает последовательно во времени, начиная с младшего разряда на вход сумматора 9. Одновременно, на другой вход сумматора 9 под действием тактовых импульсов генератора 26 ш гаульсов блока 22 управления сдвигается начальный нулевой код регистра 12 сдвига. Один цикл суммирования сумматором 9 выполняется за п тактов, где п - количество разрядов регистра 12 сдвига. Результат суммирования

9

с выхода сумматора 9 С7(вигается вновь в регистр 12 сдвига. Поскольку выход сумматора 9 соединен с информационным входом регистра 12

сдвига, выход которого соединен с

входом сумматора 9, то в регистре 12 сдвига накапливается двоичный код, равный произведению количества циклов суммирования на величину двоичного кода заданного на коммутаторе 19 блока 22 управления.

Десятичный счетчик 14 в это время выполняет подсчеты количества циклов

суммирования сумматором 9, так как через каждые п тактов на его счетном входе действует импульс первого разряда распределителя 27 импульсов блока 22 управления, поступающий через элемент И 20. Так будет продолжаться до тех пор, пока двоичный код на выходе сумматора 9 не достигнет двоичного кода, хранящегося динамическим способом в регистре 11 сдвига, путем циркуляции кодов с выхода регистра 11 сдвига на его информационный вход. Последовательный двоичный код, начиная с младшего разряда, сдвигается под действием тактовых импульсов генератора 26 импульсов блока управления с выхода регистра 11 сдвига на вход 50 управления и далее - на первый информационный вход последовательной схемы 31 сравнения, на второй информационный вход которой по входу 51 блока 22 управления поступает, начиная с младше-- го разряда, последовательный двоичный код с выхода сумматора 9. Если

двоичный код на выходе сумматора 9 достиг или превысил значение двоичного кода, хранящегося в регистре 11 сдвига, то на одном из выходов последовательной схемы 31 сравнения

формируется сигнал логической единицы, который открывает элемент И 41 или И 42. Импульс п-го разряда распределителя 27 импульсов проходит через элемент И 41 или И 42 на выход элемента ИЛИ 38 и далее с выхода 45 блока 22 управления поступает на нулевой вход триггера 7, устанавливая его в нулевое состояние. Триггер 7 в нулевом состоянии блокирует

элементы И 18 и 20, и вычисление прогнозируемого интервала времени t - tj, в счетчик 14 заканчивается.

Заданный двоичный код, устанавливаемый на коммутаторе 30 блока 24 уп91335989,

равления, определяется заранее дляU у „-ч - г .(f.

установленных уровней напряжений И,i о

и 1 следующим образом.у у - j,.-,4

Показатель экспоненциальной функ- ° ции определяется из соотношений Разделив соотношения (5) на (6),

(6) на (7), логарифмуем их, после . 111-У1 - 1п у, . ,,gj,

.«о

т t, - t, , (2)

где t, и tj - моменты срабатыванияРазделив соотношение (9) на (8),

пороговых элементов. получим 1 и 2, соответственно;

k, - величина двоичного ко--i u

tt- f- - / I- f лп

да, накопленного -г с, uu;

регистрах 10 и 11 сдви-

га к моменту време- (t - t, ) определяется из соот -а ношения (2). Соотношение (10) с учеп - количество разрядов „ (2) представить в следуюРеГИСТРОВ 10 и д„д.

сдвига;

f - частота генератора 2625

импульсов.( j. ) f. 1пУ1 1 12У1 1 ( Из соотношений (1) и (2) получаем L п InlJj - InUjJ t выражения для расчета величины заданного двоичного кода, устанавливаемо- де (t - t) - прогнозируемое время го на коммутаторе 28: момента t до мо- f мента достижения про- ( п 2 o(. k,(3)цессом уровня напряжения Uj;

Величина С, в двоичном коде уста- - величина двоичного

навливается на коммутаторе 28 блока35 кода, накопленного

22 управления.в регистре 11 сдвига

При достижении соотношенияк моменту времени .

ч;

п - количество разрядов

oc-k, , (4)40 регистров 1 1 и 12

сдвига;

f - частота генератора

схема 30 сравнения блока 22 управле-26 импульсов,

ния останавливает процесс вычисле-Если на коммутаторе 29 блока

ния показателя ао экспоненциальной45 22 управления установить в двоичном

функции, величина которого фиксируеткоде величину ся в счетчике 13. Заданный двоичный

код, который устанавливается на ком- . мутаторе 29 блока 22 управления, оп- i ТпО

ределяется заранее для установлен-50

1 f-Ui ч

ных уровней напряжений U, , U, и U

(фиг.4) следующим образом.

Входное напряжение, действуюш:ее

1 f-Ui ч

1 иГ

- сг.

- сг.

то при достижении соотношения

на информационном входе 23, достигает соответственно уровней U, 55

з :,.г

и, и„е- -;(5) . (13)

In и, - In U bL(t - t,); (8) In Uj - In U, 66(t, - t,,), (9)

1 f-Ui ч

1 иГ

(12)

- сг.

то при достижении соотношения

II 1

схема 31 сратзнения блока 22 управления останавливает процосс счета п счетчике 14, в котором фиксируется величина прогнозируемого времени (t , - tj) .

Если на коммутаторе 29 блока 22 управления установить в двоичном коде величину

С,

--- (InU, - InU)

f n

- с:

то при достижении соотношения

с, k,

схема 31 сравнения блока 22 управления остановит процесс счета в счетчике 14, когда значение в нем достигнет величины постоянной времени с экспоненциального процесса.

Соотношение (15) следует из выражений (1), (2) и (14) с учетом связи между показателем йЬ экспоненциальной функции и постоянной временини о .

об

Таким образом, устройство в счетчике 13 вычисляет значение показател экспоненциальной функции, а в счег- чике 14 - значение постоянной времени или прогнозируемое время прохождения экспоненциальным процессом двух заданных уровней напряжения U и Uj.

Схема 30 или 31 сравнения (фиг.З) работает следующим образом.

На информационные входы 64 и 65 поступают, начиная с младшего разряда, последовательные двоичные коды чисел А и В соответственно. В исходном состоянии триггеры 57 и 58 находятся в нулевом состоянии, в которое они устанавливаются каждые n тактов последовательностью импульсов на входе 67 сброса. На выходе элементов И 59 и 60 формируются поразрядно логические функции АВ и АВ соответственно. Если В А, то триггер 58 устанавливается в единичное состояние выходн ым сигналом элемента И 60.

,

3398912

Kor/i.a Л В, элементы М 39 и 60 закрыты и триггеры 37 и 38 сохраняют нулевое состояние. После тгоразряд( ного сравнения гзсех разрядов последовательных двоичных кодов чисел А и В триггер 37 находится в единичном состоянии и на выходе 68 превышения формируется единичный сигнал,

10 если В А. В случае В А триггер 58 находится в единичном состоянии и на выходе 70 пренижения формируется единичный сигнал. Когда А В, триггеры 37 и 38 сохраняют

15 нулевое состояние и на выходе элемента ШШ-НЕ 63 формируется единичный сигнал. ,

Формула изобретения

20

Устройство для вычисления показателя экспоненциальной функции, содержащее первый и второй схемы сравнения, первый и второй генераторы

25 одиночных импульсов,первый и второй триггеры, первый суьтматор, первый и второй регистры сдвигов, первый элемент ИЛИ, первый, второй и третий элементы И, -первый счетчик, блок

30 управления, содержащий генератор

импульсов, распределитель импульсов, элемент задержки, первый и второй ключи, первый коммутатор, первый и второй элементы ИЛИ, первую схему

35 сравнения, первый и второй элементы И, выход генератора импульсов соединен с входом распределителя импульсов, выходы с первого по п-й которого, где n - разрядность регистров

40 сдвига, соединены с первого по п-й информационными входами первого коммутатора, управляющий вход которого соединен с входом задания длительности первого периода вычислений

45 блока управления, выходы коммутатора через первьй элемент ИЛИ соединены с первым информационным входом первой схемы сравнения, тактовый вход и вход сброса которой соединеgg ны соответственно с выходом генератора импульсов и с выходом элемента задержки, п-й выход распределителя импульсов соединен с входом элемента задержки и с первыми входами первоgg го и второго элементов И, вторые входы которых соединены с входами соответственно, двенства и превышения эталонного кода первой схемы . сравнения, выходы первого к второго

ГЗ) ГГ)9Й9

лементов И соединопы с перв1 1м и

м л ч п п к л с м к ч в п т в в л ды И в че ле с ле

вторым входами второго элемента ИЛИ третий вход которогч) соединен с входом П€;рвого ключа, информационный вход которого соединен с выходом генератора импульсов, выход элемента задержки соединен с информационным входом второго ключа, управляющие входы первого и второго ключей соединены соответственно с первым и вторым входами задания режима вычисления блока управл(П)ия, причем в устройстве первые информационные входы первой и второй схем сравнения соединены с информационным входом устройства, второй информационный вход первой схемы сравнения соединен с входом задания первого эталонного кода напряжения устройства,вход задания второго эталонного кода напряжения которого соединен с вторым информационным входом второй схемы сравнения, выход второго ключа блока управления соединен с тактовыми входами первого и второго генераторов одиночных импульсов, входы запуска которых соединены с выходами соответственно первой и второй схем сравнения, выходы первого и второго генераторов одиночны:-; импульсов соединены соответственно с единичными входами превого и второго триггеров нулевые входы которых соединены с выходом второго элемента ИЛИ блока управления, выход первого разряда распределителя импульсов которого соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с инверсным и прямым выходами второго триггера, инверсный и прямой выходы первого триггера соединены соответственно с управляющими входами первого регистра сдвига и третьим входом первого элемента И, прямой выход второго триггера соединен с первым входом третьего элемента И, первый вход первого сумматора соединен с выходом первого регистра сдвига, информационный вход которого соединен с выходом первого сумматора, установочный вход первого регистра сдвига соединен с входом логического нуля устройства, выходы первого ключа и генератора импульсов блока управления соединены соответственно с установочным входом первого счетчика и входами синхронизации первого и вто0

5

0

5

0

5

0

5

0

5

рого р(Ч И(троя г/(|,1П а, ньг/.од nTfip - го итемрнтл И соединен C j C4 THiiiM входом первого счетчика, выход элемента ИЛИ соединен со вторым входом первого сумматора, выход первого элемента И соединен с первым входом элемента ИЛИ, второй вход которого соедине.н с выходом третьего элемента И, выход первого регистра сдвиг а соединен с вторым информационным входом первой схемы сравнения блока управления, установочный вход второго регистра сдвига соединен с выходом первого сумматора, выход второго регистра сдвига соединен со своим ин- формационньгм входом и с вторым входом третьего элемента И, отличающее ся тем, что, с целью расширения функциональных возможностей за счет вычисления прогнозируемого времени достижения процессом заданного уровня напряжения, в него введены второй cyMMaiTop, третий регистр сдвига, третий триггер, четвертый, пятый и шестой элементы И, второй счетчик,а блок управления дополнительно содержит второй коммутатор, вторую схему сравнения, третий и четвертый элементы И, третий и четвертый элементы ИЛИ, причем выходы разрядов с первого по п-й распределителя импульсов блока управления соединены с первого по п-й информационными входами второго коммутатора, управляющий вход которого соединен с входом задания длительности второго периода вычислений блока управления, выходы второго коммутатора блока управления соединены с входами третьего элемента ИЛИ блока управления, выход которого соединен с первым входом четвертого элемента И, выходы равенства и превышения эталонного кода второй схемы сравнения блока управления соединены соответственно с первыми входами третьего и четвертого элементов И блока управления, вторые входы которых соединены с выходом п-го разряда распределителя импульсов блока управления, выходы третьего и четвертого элементов И блока управления соединены соответственно с первым и вторым входами четвертого элемента ИЛИ блока управления, третий вход которого соединен с выходом первог о ключа блока управления, выходы генератора импульсов

151

и элемента задержки блока управления соединены соответственно с тактовым входом и входом сброса второй схемы сравнения, первый и второй информационные входы которой соединены соответственно с выходом второго регистра сдвига и с выходом второго сумматора, выход четвертого элемента ИЛИ блока управления соединен с нулевым входом третьего триггера, единичный вход которого соединен с выходом второго генератора оди- ночных импульсов, выход генератора импульсов блока управления соединен с входом синхронизации третьего регистра сдйига, установочный вход которого соединен с входом логического нуля устройства, управляющие входы вторрго и третьего регистров сдвига объединены и соединены с выходом

t

5

38

9,6

пятого элемента И, первый и второй входы которого соединены соответственно с инверсными выходами второго и третьего триггеров, информационный вход и выход третьего регистра сдвига соединены соответственно с выходом и первым входом второго сумматора, второй вход которого соединен с

выходом четвертого элемента И, выход первого разряда распределителя импульсов блока управления соединен с первым входом шестого элемента И, второй вход которого объединен с

вторым входом четвертого элемента

И и соединен с пряклтм выходом третьего триггера, счетный и установочный входы второго счетчика соединены со- , ответственно с выходом шестого элемента И и с выходом первого ключа блока управления.

t

W

/

46

J7

/ ч

И д Ш Ш

7 7К 7 7F лч / /гч /

сравнения

6 53

Ключ J2

.

65

Щи

ПЙЗ

70

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1984 |

|

SU1272342A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Устройство для вычисления экспоненциальной функции | 1982 |

|

SU1057944A2 |

| Вычислительное устройство | 1982 |

|

SU1070545A1 |

Изобретение относится к вычислительной технике и может быть использовано в различных областях техники и промьшленности для контроля и исследования процессов различной физической природы, которые описываются экспоненциальной функцией. Цель (Л со со ел СО 00 со

-0/4

Фиг

Составитель А.Шуляпов Редактор Н.Егорова Техред М.Ходанич Корректор Н.Король

Заказ 4048/43 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений -и открытий t13035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1984 |

|

SU1272342A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1985-12-02—Подача