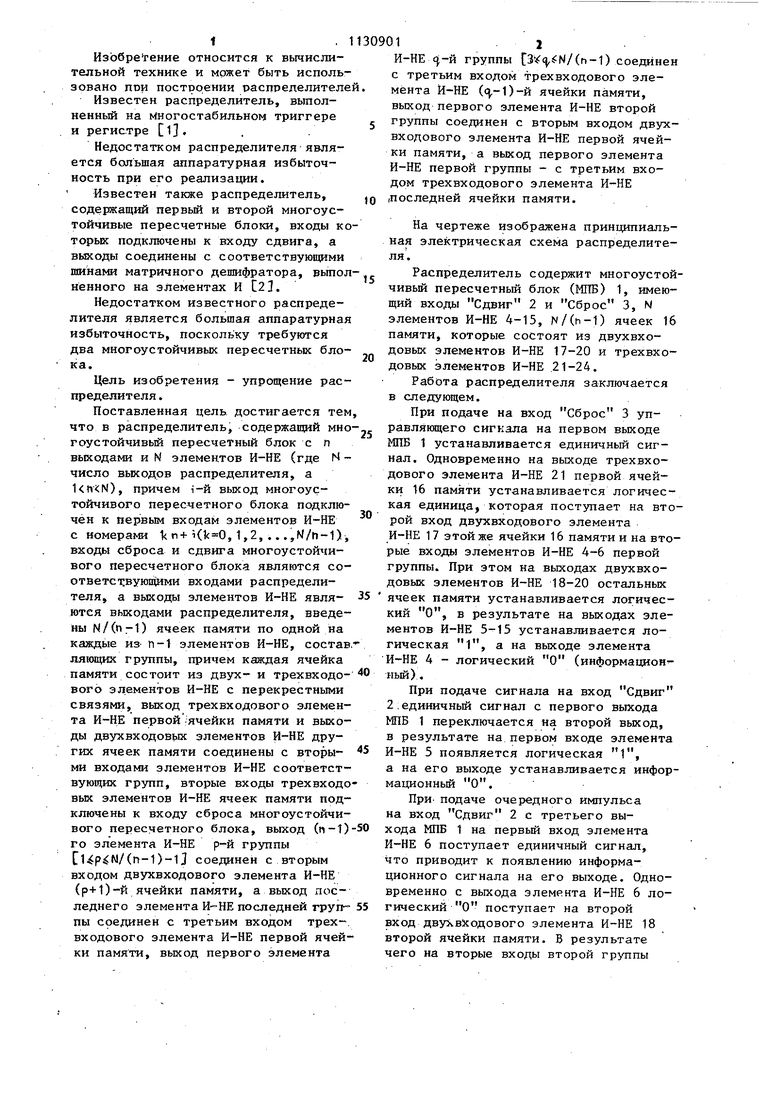

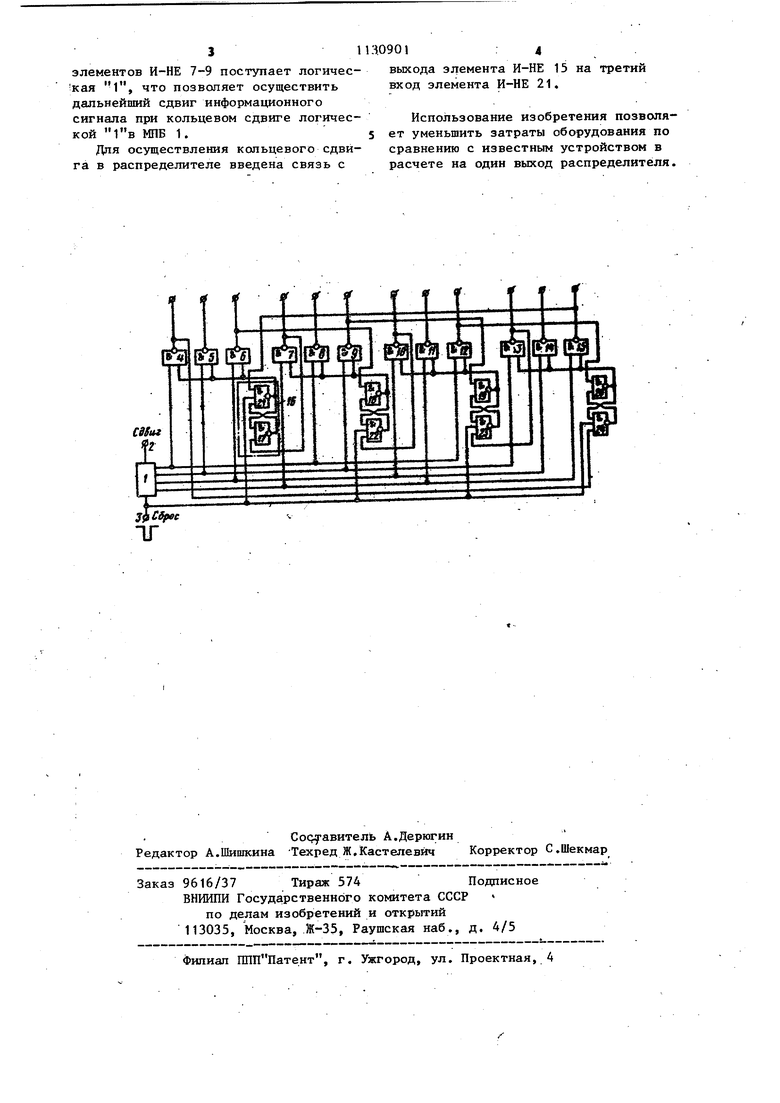

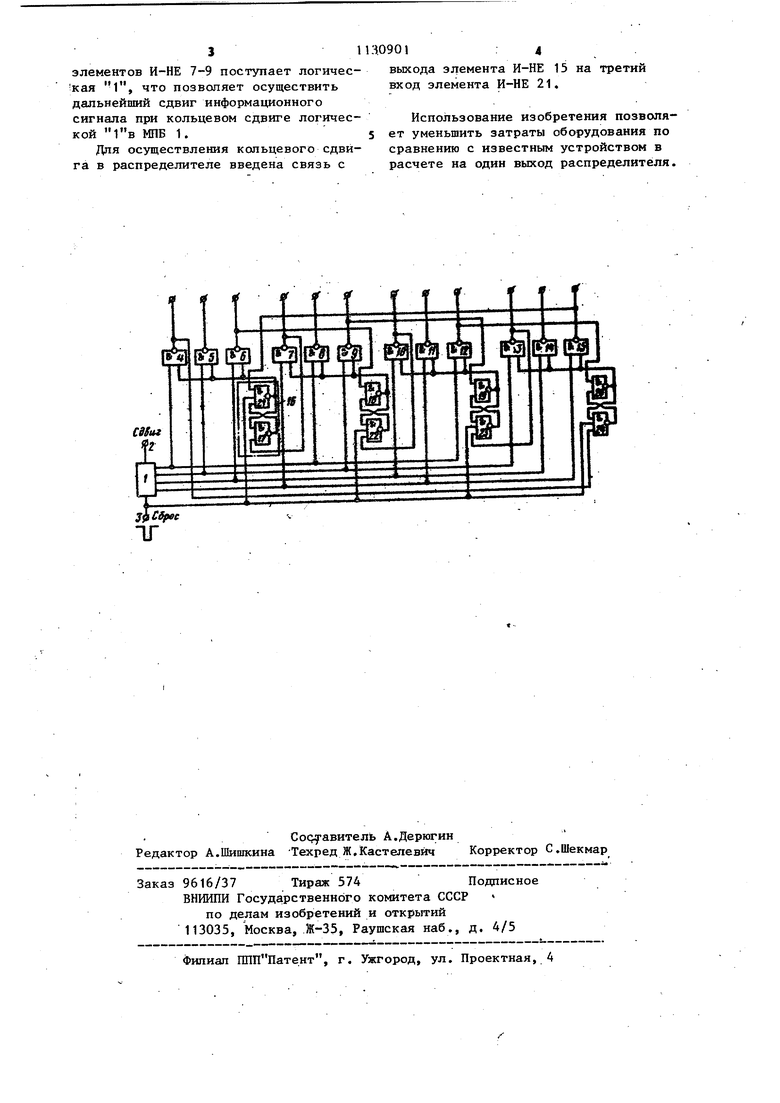

Изобрегение относится к вычислительной технике и может быть использовано пои построении распределителе Известен распределитель, выполненный на многостабильном триггере и регистре 1. Недостатком распределителя является большая аппаратурная избыточность при его реализации. известен также распределитель, содержащий первьй и второй многоустойчивые пересчетные блоки, входы ко торьк подключены к входу сдвига, а выходы соединены с соответствующими шинами матричного дешифратора, вьтол ненного на элементах И С2 3. Недостатком известного распределителя является большая аппаратурная избыточность, поскольку требуются два многоустойчивых пересчетных блока. Цель изобретения - упрощение распределителя . Поставленная цель достигается тем что в распределитель, содержаний мно гоустойчивый пересчетный блок с п выходами и М элементов И-НЕ (где N число выходов распределителя, а ), причем 1-й выход многоустойчивого пересчетного блока подключён к первым входам элементов И-НЕ с номерами 1 п+i(, 1,2, .. .,М/п-1), входы сброса и сдвига многоустойчивого пересчетного блока являются соответстсвушщими входами распределителя, а выходы элементов И-НЕ являются выходами распределителя, введены N/(n.-1) ячеек памяти по одной на каждые из n-t элементов И-НЕ, состав ляющих группы, причем каждая ячейка памяти состоит из двух- и трехвходового элементов И-НЕ с перекрестными связями, выход трехвходового элемента И-НЕ первой ;ячейки памяти и выходы двухвходовьк элементов И-НЕ других ячеек памяти соединены с вторыми входами элементов И-НЕ соответствующих групп, вторые входы трехвходо вых элементов И-НЕ ячеек памяти подключены к входу сброса многоустойчивого пересчетного блока, выход (n-t) го элемента И-НЕ группы (n-1)-1J соединен с вторым входом двухвходового элемента И-НЕ (р+1)-и ячейки памяти, а выход последнего элемента И-НЕ последней гругг пы соединен с третьим входом трехвходового элемента И-НЕ первой ячейки памяти, выход первого элемента И-НЕ группы ,:N/(h-1) соединен с третьим входом трехвходового элемента Й-НЕ (с{,-1)-й ячейки памяти, выход первого элемента И-НЕ второй группы соединен с вторым входом двухвходового элемента И-НЕ первой ячейки памяти, а выход первого элемента И-НЕ первой группы - с третьим входом трехвходового элемента И-НЕ .последней ячейки памяти. На чертеже изображена принципиальная электрическая схема распределителя. Распределитель содержит многоустойчивый пересчетный блок (МПБ) 1, имеющий входы Сдвиг 2 и Сброс 3, N элементов И-НЕ 4-15, N/(h-1) ячеек 16 памяти, которые состоят из двухвходовых элементов И-НЕ 17-20 и трехвходовых элементов И-НЕ .21-24. Работа распределителя заключается в следующем. При подаче на вход Сброс 3 управлянлдего сигнала на первом выходе МПБ 1 устанавливается единичный сигнал. Одновременно на выходе трехвходового элемента И-НЕ 21 первой ячейки 16 памяти устанавливается логическая единица, которая поступает на второй вход двзгхвходового элемента И-НЕ 17 этой же ячейки 16 памяти и на вторые входы элементов И-НЕ 4-6 первой группы. При этом на выходах двухвходовых элементов И-НЕ 18-20 остальных ячеек памяти устанавливается логический О, в результате на выходах элементов И-НЕ 5-15 устанавливается логическая 1, а на выходе элемента И-НЕ 4 - логический О (информационньй) . При подаче сигнала на вход Сдвиг 2 единичный сигнал с первого выхода МПБ 1 переключается на второй выход, в результате на первом входе элемента И-НЕ 5 появляется логическая 1, а на его выходе устанавливается информационньй О. При- подаче очередного импульса на вход Сдвиг 2 с третьего выхода МПБ 1 на первый вход элемента И-НЕ 6 поступает единичный сигнал, что приводит к появлению информационного сигнала на его выходе. Одновременно с выхода элемента И-НЕ 6 логический О поступает на второй вход двухвходового элемента И-НЕ 18 второй ячейки памяти. В результате чего на вторые входы второй группы

51

элементов И-НЕ 7-9 поступает логическая 1, что позволяет осуществить дальнейший сдвиг информационного сигнала при кольцевом сдвиге логической МПБ 1.

Для осуществления кольцевого сдвига в распределителе введена связь с

13.0901д

выхода элемента И-НЕ 15 на третий вход элемента И-НЕ 21.

Использование изобретения позволя5 ет уменьшить затраты оборудования по сравнению с известным устройством в расчете на один выход распределителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для одноканального синхронного фазового управления вентильным преобразователем | 1982 |

|

SU1046894A1 |

| ГЕНЕРАТОР СЛУЧАЙНЫХ ЧИСЕЛ | 2001 |

|

RU2211481C2 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Устройство для умножения с накоплением комплексных чисел | 1988 |

|

SU1587230A1 |

| Устройство для одноканального синхронного фазового управления вентильным трехфазным преобразователем | 1982 |

|

SU1086543A1 |

| Генератор псевдослучайных кодов | 1983 |

|

SU1167710A1 |

| АССОЦИАТИВНЫЙ ВЫЧИСЛИТЕЛЬ СМЕЩЕНИЯ ЦЕНТРА ТЕКУЩЕГО ИЗОБРАЖЕНИЯ ОТ ЦЕНТРА ЭТАЛОННОГО | 1991 |

|

RU2029358C1 |

| Счетчик импульсов | 1978 |

|

SU746949A1 |

| СПОСОБ И МНОГОФУНКЦИОНАЛЬНОЕ АССОЦИАТИВНОЕ МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СТРОКОВЫХ ДАННЫХ И РЕШЕНИЯ ЗАДАЧ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2014 |

|

RU2582053C2 |

| "Устройство реализации операции "/х/-произведение @ -мерных кубов" | 1989 |

|

SU1656522A1 |

РАСПРЕДЕЛИТЕЛЬ, содержащий многоустойчивый пересчетный блок с п выходами и N элементов И-НЕ (где N - число выходов распределителя, а 1 1 п i N ), причем i -и выход многоустойчивого пересчетного блока подключен к первым входам элементов И-НЕ с номерами к ri+t(, 1,2, ..., (Vh-l), входы сброса и сдвига многоустойчивогсг пересчетного блока являются соответствующими входами распределителя, а выходы элементов И-НЕ являются выходами распределителя, отличающийся тем, что, с целью упрощения распределителя, в него введены N/(n-1) ячеек памяти по одной на каждые из h-1 элементов И-НЕ, составляющих группы, причем каждая ячейка памяти состоит из двухи трехвходового элементов И-НЕ с перекрестными связями, причем выход трехвходового элемента И-НЕ первой ячейки памяти и выходы двухвходовых элементов И-НЕ других ячеек памяти соединены с вторыми входами элементов И-НЕ соответствукйщх групп, вторые входы трехвходовых элементов И-НЕ ячеек памяти подключены к входу сброса многоустойчивого пере- счетного блока, выход (n-l)-ro элемента И-НЕ р-й группы (n-1)-1 соединен t вторым входом двухвходового элемента И-НЕ (р+1)-й ячейки памяти, а выход последнего элемента И-НЕ последней группы соединен с третьим входом трехвходового элемента И-НЕ первой ячейки памяти, выход первого элемента И-НЕ -й группы З t{,N/(п -1)3 соединен с третьим входом грехвходового элемента И-НЕ ()-й ячейки памяти, выход первого элемента И-НЕ второй группы соеСО динен свтор1 в входом двухвходового элемента И-НЕ первой ячейки памяти, со а выход первого элемента И-НЕ первой группы - с третьим входом трехвходового элемента И-НЕ последней ячейки |Памяти.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Букреев И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| М., Советское радио, 1975, с | |||

| ПЕРЕДВИЖНАЯ ДИАГРАММА ДЛЯ СРАВНЕНИЯ ЦЕННОСТИ РАЗЛИЧНЫХ ПРОДУКТОВ ПО ИХ КАЛОРИЙНОСТИ | 1919 |

|

SU285A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, с | |||

| ПЕРЕДВИЖНАЯ ДИАГРАММА ДЛЯ СРАВНЕНИЯ ЦЕННОСТИ РАЗЛИЧНЫХ ПРОДУКТОВ ПО ИХ КАЛОРИЙНОСТИ | 1919 |

|

SU285A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-23—Публикация

1983-07-13—Подача