элементы ИЛИ, первые входы которых соединеныСоответственно с первым, вторым, TpejTbHM и четвертым входами элемента И, являющимися соответственно первым, вторым, третьим и четвертым сигнальными входами блока выбора направления передачи, управляющим входом и перэым, вторым, третьим, четвертым и пятым выходами которого являются соответственно объединенные вторые входы первого, второго третьего и четвертого элементов ИЛИ и выходы первого, второго, третьего и четвертого элементов ИЛИ и элемента И.

4. Устройство по п. 1, отличающееся тем, что анализатор временных интервалов содержит х умматор по mod 2 и последовательно соединенные счетчик импульсов, формирователь импульсов, блок памятиi второй вход которого через переключатель соединен с первым вькодом сумматора по mod 2, второй выход которого соединен с вторым входом пере5012

ключателя, и блок сравнения контролируемых временных интервалов с заданным временным интервалом

2(t. .

где tf, момент приема сигнала исполнительным приемопередатчиком;

i - момент прохождения комъгутаторов сигналом от задающего приемопередатчика; i -.точка проводного канала связи, в которую включены коммутаторы;

consi Р обработки сигнала исполнительным приемопередатчиком,

причем выход блока памяти, выход блока сравнения, вход счетчика импульсов и входы сумматора по mod 2 являются соответственно первым и вторым выходами, управляющим и сигнальными входами анализатора временных интервалов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля проводных каналов связи | 1984 |

|

SU1223377A2 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Устройство для контроля чередования фаз @ -фазной сети | 1981 |

|

SU1029301A1 |

| СИСТЕМА АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ | 1991 |

|

RU2006896C1 |

| Волоконно-оптическая система связи | 1990 |

|

SU1823141A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА СВЯЗИ | 1995 |

|

RU2138910C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| СИСТЕМА СПУТНИКОВОЙ СВЯЗИ | 2004 |

|

RU2279762C2 |

| Устройство доступа к общей памяти | 1990 |

|

SU1836686A3 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПРОВОДНЫХ КАНАЛОВ СВЯЗИ, содержащее первый и второй задающие приемопередатчики команд, исполнительный приемопередатчик команд, г коммутаторов (f - число символов в слове ), блок выбора направления передачи и анализатор временных интервалов, причем первый информационный выход каждого коммутатора через соответствующий проводной канал связи соединен с соответствующим входом исполнительного приемопередатчика команд, а первые и вторые управляющие выходы первого и второго задающих приемопередатчиков команд через линии связи соединены соответственно с первым и четвертым, вторым и третьим сигнальными входами блока выбора направления передачи, отлич ающее с я тем, что, с целью гокращения времени контроля,, первый и второй информационные входы каждого коммутатора через проводные каналы связи соединены соответственно с соответствукядим информационным выходом задающего приемопередатчика команд и с соответствующим информационным выходом второго задающего приемопередатчика команд, управляющий вход которого соединен с управляющим входом первого задающего приемопередатчика команд и через линию связи с первым выходом анализатора временных интервалов, второй вькод которого соединен с управляющим входом блока выбора направления передачи, первый, второй, третий и четвер тый выходы которого соединены соответственно с объединенными первыми, объединенными вторыми, объединен-ными третьими и объединенными четвертыми управляющими входами коммутаторов, второй информационный выход каждого из которых соединен с соответствующим сигнальным входом анализатора временных интервалов, управляющий вход которого соединен с пятым выходом блока выбора направления пе редачи . 2.Устройство по п. 1, отличающееся тем, что каждый коммутатор содержит последовательно соединенные первый,второй, третий и четвертый логические элементы, при этом выход четвертого и первый вход оо первого, выход первого и первый СП вход четвертого логических элементов соответственно объединены, а первые входы первого и третьего, вторые входы первого, второго, третьего и 1С четвертого, а также выходы первого и третьего логических элементов являются соответственно первым и вторым информационными входами, первым, вторым, третьим и четвертым управ- ляющими входами и первым и вторым информационными выходами коммутатора. 3.Устройство по п. 1, о т л ичающееся тем, что блок выбора направления передачи содержит первый, второй, третий и четвертый

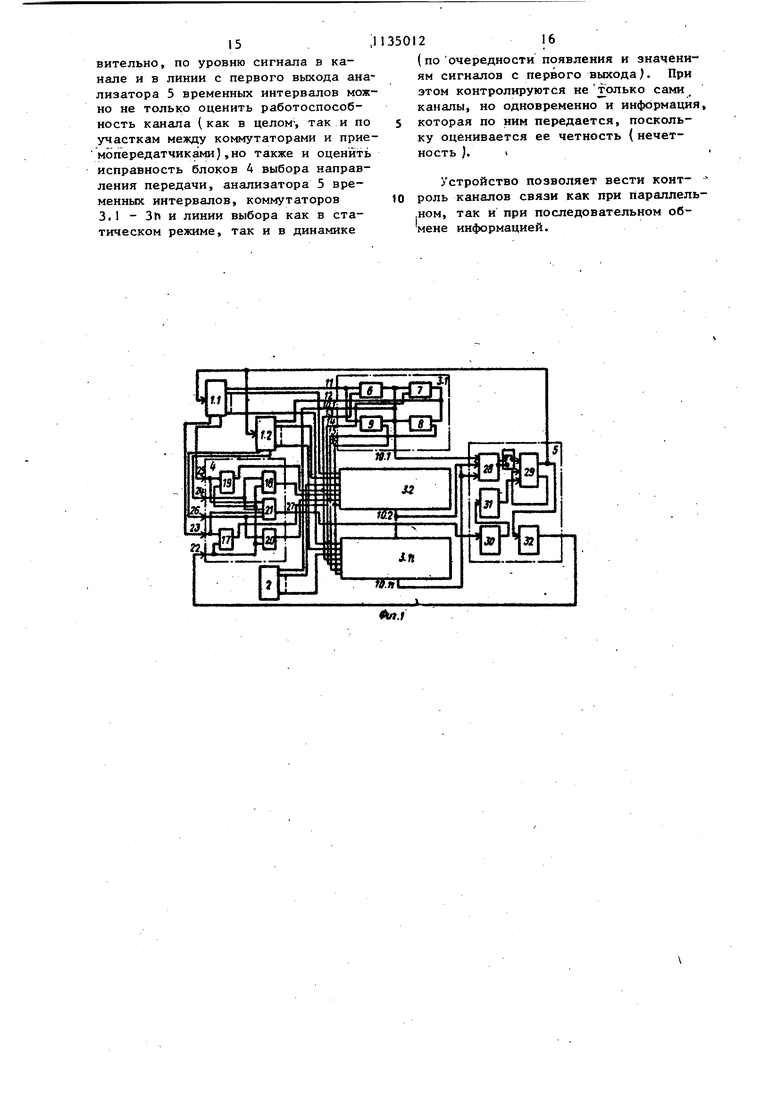

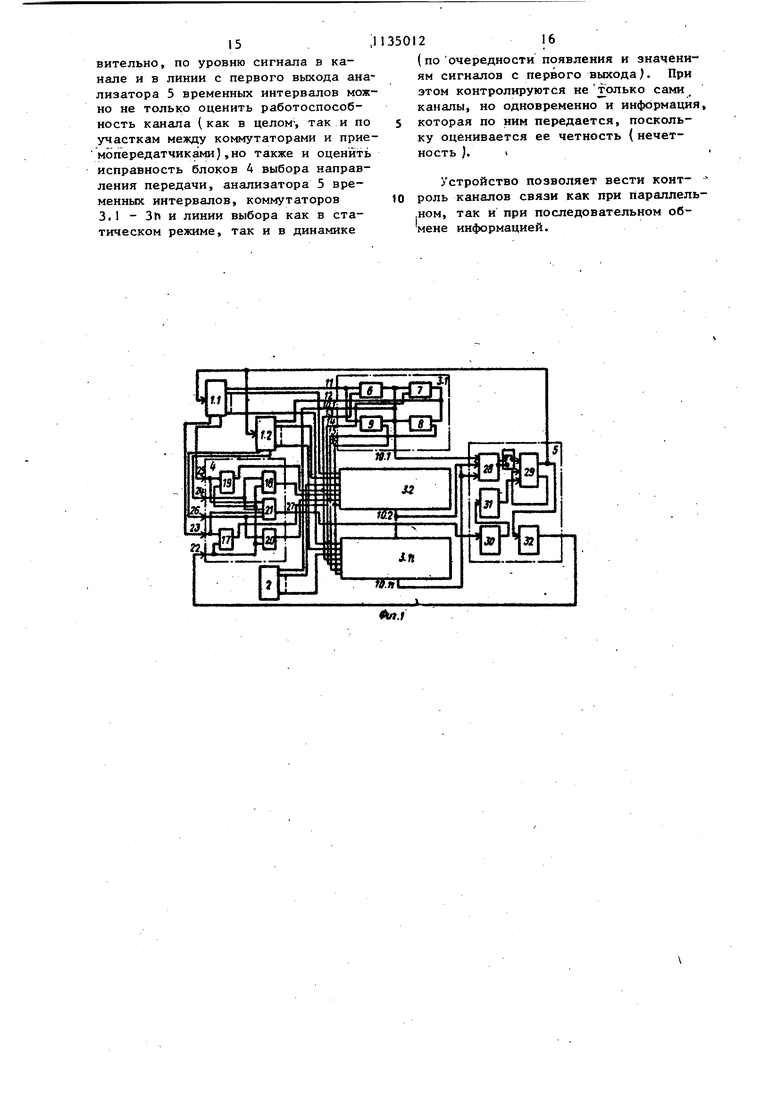

Изобретение относится к электросвязи и может быть использовано для контроля и испытаний переключаемых каналов связи. Известно устройство для контроля проводных каналов связи, содержащее первый и второй задающие приемопередатчики команд, исполнительный приемопередатчик команд, коммутаторы, блок выбора направления передач и анализатор временные интервалов, причем, первый информационный выход каждого коммутатора через соответствующий проводной канал связи соед ней с соответствующим входом испопнительногб приемопередатчика команд, а первые и вторые управляющие выходы первого и второго задающих приемопередатчиков .команд через линии связи соеди-г йены соответственно с первым, вторым, третьим и четвертым йиг нальными входами блока выбора направления передачи 1 . Однако известное устройство требует значительных временных затрат на проведение контроля. Цель изобретения - сокращение времени контроля. Цель достигается тем, что .в устройстве для контроля проводных каналов связи, содерясащем первый и второй задающие приемопередатчики команд, исполнительный приемопередатчик команд, я коммутаторов (п - число символов в слове), блок выбора направления передачи и анализатор временных интервалов, причем первый информационный выход каждого коммутатора через соответствующий проводной канал связи соединен с соответствующим входом исполнительного приемопередатчика команд, а первые и вторые управляющие выходы первого и второго задающих приемопередатчиков команд через линии связи соединены соответственно с первым и четвертым, вторым и третьим сигнальными входами блока выбора направления 3 передачи, первый и второй информационные входы каждого коммутатора через проводные каналы связи соединены соответственно с соответствующим информационным выходом первого задающего приемопередатчика команд и с соответствующим информационным выходом второго задающего приемопередатчика команд, управляющий вход которого соединен с управляющим входом первого задающего приемопередатчика команд и через линию связи с первым выходом анализатора временных интервалов, второй выход которого соединен с управляющим входом блока выбора направления передачи, первый второй, третий и четвертый выходы которого соединены соответственно с объединенными первыми, объединенными вторыми, объединенными, третьими и объединенными четвертыьм управляю щими входами коммутаторов, второй информационный выход каждого из которых соединен с соответствующим си нальным входом анализатора временны интервалов, управляющий вход которо го соединен с пятым выходом блока в бора направления передачи. Кроме того, каждый коммутатор содержит последовательно соединенные первые, второй, третий и четвер тый логические элементы, при этом выход четвертого и первый вход первого, вькод первого и первый вход четвертого логических элементов соответственно объединены, а первые входы первого и третьего, вторые вх ды первого, второго, третьего и четвертого, а также выходы первого и третьего логических элементов являются соответственно первым и вторым информационными входами, первым, вторым, третьим и четвертым управляющими входами и первым и вто рым информационными входами коммута тора. Блок выбора направления передачи содержит первый, второй, третий и четвертый элементы ИЛИ, первые входы которых соединены соответственно с первым, вторым, третьим и четвертым входами элемента И, являющимися соответственнопервым, вторым, трет им и четвертым сигнальными входами блока выбора направления передачи, управляющим входом и первым, вторым третьим, четвертым и пятым выходами которого являются соответственно объединенные вторые входы первого,. 124 второго, третьего и четвертого элементов ИЛИ и выходы первого, второго, третьего и четвертого элементов ИЛИ и эл« мента И. Анализатор временных интервалов содержит сумматор по mod 2 и последовательно соединенные счетчик импульсов, формирователь импульсов, блок памяти, второй вход которого Через переключатель соединен с первым выходом сумматора по mod 2, второй выход которого соединен с вторым входом переключателя, и блок сравнения контролируемых временных интервалов с заданным временным интервалом)oonsl. где i - момент приема сигнала исполнительным приемопередатчиком;i - момент прохождения коммутаторов сигналом от задающего приемопередатчика; i - точка проводного канала связи, в которую включены коммутаторы; const РР обработки сигнала исполнительным приемопередатчиком. причем выход блока памяти, выход блока сравнения, вход счетчика импульсов и входы сумматора по mod 2 явля ются соответственно первым и вторым выходами, управляювщм и сигнальными входами анализатора временных интервалов. На фиг,1 приведена гнкциональная схема устройства; на фиг.2 - временные диаграммы, поясняющие его работу. Устройство для контроля проводных каналов связи содержит первый 1.1 и второй 1.2 задающие приемопередатчики команд, исполнительный приемопередатчик 2, и коммутаторов 3.1, 3.2,.. . ,3,ti (л - число символов в слове), блок 4 выбора направления передачи и анализатор 5 временных интервалов. Каждый коммутатор 3.1 - З.г содержит последовательно соединенные первый, второй, третий и четвертый логические элементы 6, 7, 8и9. При этом выход четвертого и первый вход первого логических элементов 9 и 6, а также выход первого и первый вход четвертогоЛогических элементов 6 и 9 соответственно объединены; выsход первого и выход третьего логических элементов 6 и 8 также объеди нены и являются первым и вторым информационными выходами 10.1 - 10п коммутаторов 3.1 - Зп , а первые вх ды первого и третьего логических элемен-тов 6 и 8, вторые входы первого, второго, третьего и четвертого логических элементов 6, 7, 8 и 9 являются соответственно первым информационным входом 11, вторым информационны входом 12, первым, вто рым, третьиА и четвертым управляющими входами 13, 14, 15 и 16. Логические элементы 6, 7, 8 и 9 коммутаторов 3.1 Зп имеют три состояния выхода: О, 1 и Разомкнуто (высокое выходное сопротивление). Если на второй (.управляющий) вход логического элемента подан О, то на его выходе появится О или 1 в зависимости от состояния первого (информационного ) входа. Если на управляющем входе логического элеме та - I, то состояние выхода Разомкнуто. В качестве логических элементов 6, 7, 8 и 9 с тремя состояниями выхода могут быть испол зованы, например, элементы микропро цессорной серии 589АП16 (589АП26). Одноименные управляю1Цие входы 1 3 14, 15 и 16 коммутаторов 3.1 - 3. n объединены. Первый и второй информационные входы II и 12 каждого ком мутатора 3,1 - 3.n через проводные . каналы связи соединены соответствен но с соответствующими информационным выходом первого задающего приемопередатчика 1.1 команд и с соответствующим Информационным выходом второго задающего приемопередатчика 1.2 команд, а первый информацион ный выход 10.1 - 10.л каждого комму татора через соответствующий провод ной канал связи соединен с соответсттзукнцим входом исполнительного приемопередатчика 2 команд. Второй информационный выход 10.1-10.1л каж дого Коммутатора соединен с соответ ствующим сигнальным входом анализатора 5 временных интервалов. Блок 4 выбора направления переда чи содержит элементы ИЛИ 17 - 20 и элемент И 21, первый, второй, третий и четвертый входы которого соединены соответственно с первыми дами первого, второго, третьего и четвертого элементов ИЛИ 17, 18, 19 и 20. Вторые входы последних объеди 126 нены и являются управляющим входом 22 блока 4 выбора направления передачи, а первый, второй, третий и четвертый входы элемента И 21 являются соответственно его первым, вторым, третьим и четвертым сигнальными входами 23, 24, 25 и 26. Выходы первого, второго, третьего и четвертого элементов И 17, 18, 19 и 20 являются соответственно первым, вторым, третьим и четвертым выходами, а выход элемента И 21 является пятым выходом 27 блока 4 выбора направления передачи. Первый, второй, третий и четвертый выходы блока 4 выбора направления передачи подключены соответственно к объединенным одноименным управляющим входам 13, 14, 15 и 16 коммутаторов 3.1 - З.п. Первый и второй сигнальные входы 23 и 24 блока 4 выбора направления передачи через линии связи соединены соответственно с первыми управляющими выходами задающих приемопередатчиков 1.1 и 1.2, а четвертый и третий сигнальные входы 26 и 25 через линии связи соединены соответственно с BiOpNMH управляющими входами задающих приемопередатчиков 1.1 и 1.2. Анализатор 5 временных интервалов содержит сумматор 28 по mod 2, блок 29 памяти, счетчик 30 импульсов, формирователь 31 импульсов и блок 32 сравнения контролируемых временных интервалов с заданным временным интервалом Т 2()+ tcoh9+ Счетчик 30 импульсов, формирователь 31, блок 29 памяти и блок 32 сравнения соединены последовательно. Второй вход блока 29 памяти через переключатель соединен с первым выходом сумматора 28 по mod 2, второй выход которого соединен с вторым входом переключателя. При этом прямой выход блока 29 памяти, выход блока 32 сравнения, вход счетчика 30 импульсов и входы сумматора 28 по mod 2 являются соответственно первым и вторым выходами, управляющим и сигнальными входами анализатора 5 временных интервалов. Сигнальные входы анализатора 5 временных интервалов подключены соответственно к вторым информационным выходам IO.I - lO.rt коммутаторов 3.1 - З..Г1, управляющий вход соединен с пятым выходом 27 блока 4 выбора

направления передачи, первый выход через линию связи - с управляющими i входами первого и второго задающих приемопередатчиков 1.1 и 1.2, а второй выход - с управляющим входом 22 блока 4 выбора направления передачи .

Задающий приемопередатчик 1.1 (1.2) предназначен для выдачи сигналов выбора направления, выдачи сигналов к исполнительному приемопередатчику 2 и приема от порледнего сигналов подтверждения с целью обработки информации. В общем случае задающим приемопередатчиком может быть процессор.

Исполнительньй приемопередатчик 2 предназначен для приема сигналов от задающего приемопередатчика 1.1 (1.2), их обработки и выдачи сигналов подтверждения к задающему приемопередатчику 1.1 (1 .2 J.

В качестве исполнительного приемопередатчика 2 может быть использовано внешнее или периферийное-устройство или устройство удаленных терминалов (например, АЦПУ, внешнее запоминсшицее устройство и т.д.) .

Сумматор 28 по mod 2 предназначен для выработки положительного импульса только при наличии информации (посланных сигналов или сигналов подтверждения )на выходах 10.1 - 0. коммутаторов 3.1 - З.п. Сумматор 28 по mod 2 может быть реализован, например, на ИС 155 ИП2.

Первый и второй выходы сумматора 28 по mod 2 соединены соответственно с первым и вторым входами переключателя, выход которого соединен с вторым (счетным ) входом блока 29 памяти. В зависимости от того, четное или нечетное число единичных бит содержит передаваемое по каналу слово, второй вход блока 29 памяти перемычкой подключается к первому или второму ВЫХОДУ сумматуэра 28 по mod 2.

Блок 29 памяти может быть реализован, например, на триггере ИС 133 ТМ2, работающем в счетном режиме (третий вход -D -вход триггера связан с его инверсным выходом). Сигнал на второй вход (С-вход) поступает с соответствуюп(его выхода сумма тора 28 по mod 2 и триггер срабатывает по фронту этого сигнала (переход из низкого уровня в высокий).

Четвертый вход (R-вход) триггера соединен с выходом формирователя 31 и является входом установки в исходное состояние.

Счетчик 30 предназначен для выработки импульса по каждому нечетному импульсу (1,3,5,), поступающему с пятого выхода 27 блока А вы бора направления передачи (перепад

О с высокого уровня в низкий). Счетчик может быть, например, реализован на счетном триггере ИС 133 ТМ2, включенном в счетном режиме с инвертором на счетном входе.

5 Формирователь 31 импульсов предназначен для формирования короткого импульса по переднему фронту сигнале ( перепад с низкого уровня в высокий), поступающего со счетчика 30. По импульсу на выходе формирователя 31 (перепад с высокого уровня в низкий) происходит установка по R-входу в исходное состояние блока 29 памяти. Блок 32 сравнения осуществляет

5 контроль временных интервалов с

заданным временным интервалом и вы рабатывает импульс в случае превышения контролируемым интервалом заданного.Импульс вырабатывается

0 только в том случае, если на входе

блока 32 сравнения сигнал с высоким уровнем с выхода блока 29 памяти присутствует в течение времени, больщего, чем заданное время Т

5 2(). В качестве блока 32 сравнения может быть использован серийный таймер.

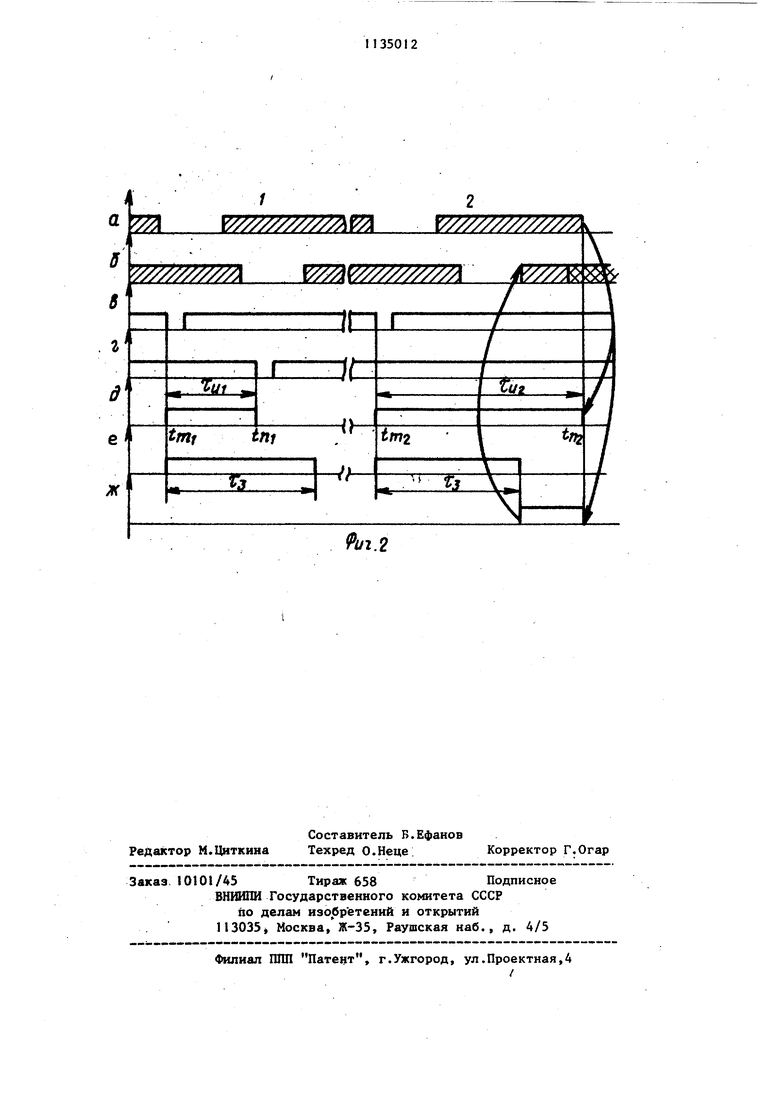

На фиг.2 приведены соотношения для нормальной работы (случай Ы и

р работы с отказом (случай 2 К На фнг.2 обозначены: q - состояние переключаемого канала от задающего приемопец: { Хатчика, например 1.1, к исполнительному приемопередатчику 2 (задающий приемопередатчик 1.1 входы 11 - логические элементы 6 коммутаторов 3.1 - 3,пвыходы 10.1 - 10.h - исполнительный приемопередатчик 2); нулевое значе-

Q ние соответствует сигналам выбора направления, заштрихованные односторонне значения соответствуют разомкнутому состоянию канала;

S- состояние переключаемого

канала от испсшнительного приемопередатчика 2 к задакщему приемопередатчику, например 1.1 (исполнительный приемоп&редатчик 2 - выходы 9; 10.I - 10.n - логические элементы 9 ком таторов 3.1 - 3n - входы 11 задающий приемопередатчик 1.1); двой ным штрихом отмечено разомкнутое состояние переключаемого канала, реали зованное в результате контроля ; в - сигналы от задакяцего приемопередатчика, например 1.1, к испол нительному приемопередатчику 2 (сигнал передается нулевым значением); г - сигналы подтверждения от исполнительного приёмопередатчика 2 к задающему приемопередатчику, причем в случае 1 подтверждение есть, а в случае 2 подтверждение нет; д - результат запоминания моментов прохождения коммутаторов послан HbJM сигналом i (от задающего приемопередатчика) и сигналом подтверждения in (от исполнительного приемопередатчика ) в вцде импульса длительностью Tj. (импульсы показаны единичным значением, индекс 1 - для случая Г, индекс 2 - для случая 2); с - импульсы длительностью Т. . соответствукщие заданному интервалу времени; - результат сравнения полученны .интервалов tj, с заданньм Т, в виде импульса единичного значения, при этом для случая 1 импульс отсутствует, а для случая 2 - имеется. ; Принцип работы устройства заключается в следующем. Обмен информацией между задающим и исполнительным приемопередатчиками производится по каналу связи, в заданную точку v которого включен переключатель, без дополнительных контрольных линий. По каждой линии канала может быть реализовано два направления (от задающего приемо передатчика к исполнительному и наоборот ). Инициатива в выборе направления принадлежит задакяцему приемопередатчику, который реализует выбор направления обмена (фиг.2а, 6). Контроль производится одновременно с обменом информацией. Поскольку обмен ;должен производиться четными (нечет ными)) кодами, предварительного конт роля не требуется. Обмен может производиться как в параллельном, так ив последователь .ном коде. Пример реализации прер,ставлен на фиг.1 для параллельного h-разрядного . В случае примеиения последовательного кода для 12 связи задающего приемопередатчика с исполнительным нужна только одна переключаемая линия канала и, соответственно, один коммутатор. Сущность контроля состоит в том, что в переключателе, включенном в заданную точку i канала связи, запонимают моменты прохождения посланного от задающего приемопередатчика сигнала (AHr.2d, ) и сигнала (подтверждения), посланного от исполнительного приемопередатчика (., i) . По указанным моментам в переключателе формируют временной интервал (фиг.23, TI), который сравнивают с заданным интервалом {4мг.2е, Tj) . Заданный интервал выбирается из соотношения Ч 21 и- Попв1 . где: t - момент приема исполнительным приемопередатчиком сигнала;t- - момент прохождения переключателя ( заданной точки i канала, в которьй включен переключатель ) посланным .. сигналом; сопз-1 время обработки сигнала исполнительным приемопередатчиком;i - точка проводного канала связи, в которую включен . коммутатор. Если сформированньй в переключателе временной интервал меньше заданного - канал исправен (фиг.2ж,1), если больше - канал неисправен (4миг.2,2) и автоматически отключается (4ИГ.25, двойные штрихи). Повторное включение канала осуществляется задающим приемопередатчиком путем снятия, а затем повторной подачи сигнала выбора направления (фиг.2о(,2) . Стрелками на фиг.2,2 указаны воздействия на отключение канала (левая стрелка) и повторное включение направления (две правые стрелки). В случае отказа (фиг.2,2Г задающий приемопередатчик (процессор может по желанию или повторить контроль, вторично установив то же направление, или установить новое направление, или по программе начать диагностику переключаемых каналов, выдавая, например, последовательно в каждую линию канала, начиная с первой, контрольную информацию (при n отсутствии ее в других разрядах) и локализуя таким образом отказавШую переключаемую линию канала. Устройство (Аиг.1) работает следующим образом. В исходном состоянии задающие приемопередатчики 1.1 и 1.2 не выбрали направления. Это значит, что линии выбора (сигнальные входы 23 26) находятся в единичном состоянии сигнал на управляющем входе 22 блока 4 выбора направления передачи ра вен О и на управляющие входы 1316 коммутаторов 3.1-Зп подана 1. Все линии разомкнуты (фиг.2и,5, заштрихованный начальный участок). Та продолжается до тех пор, пока задаю щий приемопередатчик, например 1.1, не выберет направление, для чего, например, по линии (сигнальный вход 23) выбора передаст нулевой сигнал в блок 4 выбора направления передач В этом случае на выходе блока 4 выбора направления передачи, соединен ном с управляющим входом 13 и управ ляющим (вторым) входом логического элемента 6, появится сигнал выбора направления. Линия (информационный вход П) перейдет в замкнутое состо ние (фиг.2а, незаштрихованные перепады). Одновременно с появлением сигнала выбора направления на выходе 27 блока 4 выбора направления пе редачи появляется сигнал с выхода элемента И 21. Этот сигнал поступает на управляющ1- й вход анализатора 5 временных интервалов и- далее на вход счетчика 30, а с его выхода на формирователь 31. С выхода после него сигнал поступает на вход сброса блока 29 памяти, устанавливая ег в нулевое (исходное) состояние. Далее задающий приемопередатчик 1.I посылает сигнал к исполнительному приемопередатчику 2 по замкнутой линий (фиг.2 6) по цепи: задающий приемопередатчик 1.1, канал связи, входы П коммутаторов 3.1-Зп, логические элементы 6, первые информационные выходы 10.I - 10п коммутаторов 3.1 - 3h, канал связи, исполнительный приемопередатчик 2. Одновременно с вторых информационных выходов IO.I - 10п коммутаторов 3. Зп этот сигнал поступает на сигнал ные входы анализатора 5 временных интервалов и далее на входы суммато ра 28 по mod 2. С одного из выходов 1212 последнего (выход выбирается в зависимости о.т того, четное или нечетное число бит содержит сигнал задатчика) снимается сигнал, поступающий на вход синхронизации блока 29 памяти и устанавливающий его в единичное состояние. Сигнал с выхода блока 29 памяти поступает на вход блока 32 сравнения, включая его в работу (фиг.26, . Передав сигнал исполнительному приемопередатчику 2, задающий приемопередатчик I.1 изменяет направление передачи в линии, для чего снимает нулевой си1- нал с линии (сигнального входа 23, фиг.2о1) и выставляет его на линии (сигнальный вход 26, фиг.. В соответствии с этим на выходе блока 4 направления передачи, соединенном л с управляницим входом 13, снимается сигнал выбора направления, а на управляющем входе 16 - появляется. Это означает, что сигнал выбора направления появится теперь на управляющем входе логического элемента 9 и пропадет на управляющем входе логического элемента 6. Одновременно с появлением сигнала выбора указанного направления на выходе 27 блока 4 выбора направления передачи появляется сигнал с выхода элемента И 21. Этот сигнал поступает на управляющий вход анализатора 5 временных интервалов и далее на вход счетчика 30. Поскольку на выходе счетчика 30 сигнал появляется на каждый нечетный сигнал на входе,то в этом случае на входе формирователя 31 сигнала нет и состояние выхода блока 29 памяти не изменяется. Далее исполнительный приемопередатчик 2 посылает сигнал подтверждения к задающему приемопередатчику 1.1 (фиг.2а) по цепи: исполнительный приемопередатчик 2, канал связи, первые информационные выходы 10.1 - Юм коммутаторов 3.1 - Зп, логические элементы 9, входы 11 коммутаторов 3.1 - Зп, канал связи, задакиций. приемопередатчик 1.1 Одновременно с вторых информационных выходов 10.1 - 10.П коммутаторов 3.1 - Зп этот сигнал поступает на сигнальные входы анализатора 5 времеиных интервалов и далее на выходы сумматора 28 по mod 2, с выхода которого снимается сигнал на вход синхронизации блока 29 памяти, устанавливающий его в нулевое состояние . При этом сигнал с выхода блока 2 памяти подается на вход блока 32 сравнения нулем и выключает его из работы (фиг.21Э, . Если же перекл чаемый канал неисправен, что соотве ствует отсутствию сигнала на входе синхронизации блока 29 памяти, то состояние, последнего не изменяется, блок 32 сравнения работает и по истечении заданного времени .Tj. (фиг.2 tna) формирует сигнал (фиг.2ж), поступающий с второго выхода анализатора 5 временных интервалов на управляюпщй вход 22 блока 4 выбора направления передачи. Этот сигнал поступает на первые входы элементов ИЛИ 17 - 20, вследствие чего-на вылодах блока 4 выбора направления передачи появляется единичный сигнал, который поступает на управляющие входь 13 - 6 коммутаторов 3.1 Зй( и отключает линии, в том числе и выбранное направление (фиг.25, участок двойной штриховки). Однако пока не снят сигнал выбора, установ ленный ранее задающим приемопередат чиком 1 . на линии (сигнальный вход 26, фиг,25), состояние сигнала на выходе 27 блока 4 выбора направления передачи, состояние счетчика 30 формирователя 31 и блока 29 не изменяется. Для выбора нового направл ния задающий приемопередатчик 1.1 должен сначала снять сигнал выбора. При этом сигнал на выходе 27 возрастает с низкого уровня до высокого, что не изменяет состояния счетчика 30 (счетчик управляется перепадом из высокого уровня в низкий), а следовательно, формирователя 31, блоков 29 и 32. Затем приемопередатчик 1.1 реализует повторное включение направления. Для этого вновь выставляется сигнал выбора (фиг.2сг). Появляется сигнал на выходе 27 блока 4 выбора направления передачи (перепад с высокого уровня в низкий), по которому изменяется состояние счетчика 30 (на его выходе происходит изменение сигнала с высокого уровня д низкого, а формирователь 31 выраба тывает импульс, устанавливакнций блок 29 памяти (фиг.2б, tf, ) и блок-3 сравнения (фиг.2х, по правым стрелкам фиг.2)) в исходное состояние, f гатор 3. - Зп при этом реали 12J4 зует выбранное направление обмена по каналу. Если при выдаче сигнала выбора исходное -состояние не установилось (приемопередатчик 1.1 получает информацию об исходном состоянии по уровню в проводном канале связи и (или) по сигналу с выхода блока 29 памяти, поступающему на вход приемопередатчика 1.1) , достаточно выставить сигнал выбора вторично. Отсутствие исходного состояния и в этом случае означает отказ данного направления и необходимость выбора другого направления или диагностики. Работа исполнительного приемопередатчика 2 с задающим приемопередатчиком 1.2 происходит аналогично, только по информационным выходам io.l 10п и входам 12 и через логические элемеиты 7 и 8, управляемые по входам 14 и Г5 коммутаторов 3.1 - 3 п . Таким образом, контроль переключаемых каналов осуществляется одновременно с обменом информации между задающим приемопередатчиком 1.1 (1.2) и исполнительным приемопередатчиком 2 и не требует дополнительного времени. Выбор точки i линии, в которой производится переключение (т.е. располагаются коммутаторы 3.1 и 3fi, блок 4 выбора направления передачи и анализатор 5 временных интервалов), задается конкретными условиями работы системы. С целью сокращения длины линии выбора направления рациональнее размещать коммутаторы 3.1 - Зп, блок 4 выбора направления передачи и анализатор 5 ближе к задающему приемопередатчику 1.1 (1.2). Линии выбора и линия с первого выхода анализатора 5 временных интервалов входит конструктивно в канал связи и длина их равна расстоянию от задающего приемопередатчика 1.1 - 1.2 до коммутатора 3.1 - Зп. Технико-экономическая эффективность устройства для контроля проводных каналов связи заключается в сокращении времени контроля, обусловленном тем, что контроль осуществляется одновременно с обменом по каналу. Кроме того, не требуется контроля временных интервалов на стороне как задающего, так и исполнитель- , кого приемопередатчика. Дополнительный эффект состоит в еличении глубины контроля. Дейст15

вительно, по уровню сигнала в канале и в линии с первого выхода анализатора 5 временных интервалов можно не только оценить работоспособность канала (как в целом-, так и по участкам между коммутаторами и приемопередатчиками),но также и оценить исправность блоков 4 выбора направления передачи, анализатора 5 временных интервалов, коммутаторов 3.1 - Зг и линии выбора как в статическом режиме, так и в динамике

3501216

(поочередности появления и значени-ям сигналов с первого выхода). При этом контролируются нетолько сами каналы, но одновременно и инфЬрмация, 5 которая по ним передается, поскольку оценивается ее четность ( нечетность ). I

Устройство позволяет вести конт- 10 роль каналов связи как при параллельном, так и при последовательном обмене информацией.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1985-01-15—Публикация

1981-10-08—Подача