вый, второй и третий формирователи сигналов переднего фронта, входы которых подключены к информационным входам блока, элементы И установки, выходы которых соединены с выходами установки в начальное состояние, последовательно соединенные первый элемент ИЛИ, входы которого связаны соответственно с первыми входами элементов И установки и подключены к выходам упомянутых формирователей, элемент И управления, элемент памяти и элемент задержки- и последовательно соединенные второй элемент ИЛИ, входы которого подключены ко входам обратной связи блока, четвертый формирователь сигнала переднего фронта, выход которого соединен со входом установки в «О элемента памяти, другой выход которого связан с объединенными вторыми входами элементов И установки и первым управляющим выходом блока, и пятый формирователь сигнала переднего фронта, выход которого подключен к выходу установки в исходное состояние блока, при этом другой вход элемента И управления соединен со входом пятого формирователя и управляющим входом блока, выход элемента задержки со вторым управляющим выходом блока, а выход второго элемента ИЛИ - с третьим управляющим выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля чередования фаз @ -фазной сети | 1983 |

|

SU1108547A2 |

| Устройство для контроля чередования фаз @ -фазной сети | 1981 |

|

SU1020908A1 |

| Устройство для контроля чередования фаз @ -фазной сети | 1982 |

|

SU1096724A2 |

| Устройство для контроля за ходом вычислительного процесса | 1987 |

|

SU1539780A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для обнаружения ошибок при передаче данных по телефонному каналу | 1989 |

|

SU1755377A1 |

| Многоканальный генератор последовательностей импульсов | 1983 |

|

SU1228232A1 |

| Устройство перемежения данных | 1990 |

|

SU1815670A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЧЕРЕДОВАНИЯ ФАЗ М-ФАЗНОЙ СЕТИ, содержащее формирователи полумеандров, входы которых подключены к контролируемым фазам, и блок логического контроля, функционально связанный с формирователями полумеандров и состоящий из субблоков, каждый из которых выполнен в виде последовательно соединенных элемента И и элемента памяти, отличающееся тем, что, с целью повышения информативности путем контроля угла сдвига между напряжением и током и определения наименования фаз в случае обратного порядка чередования, оно дополнительно снабжено дешифратором, тактовым блоком и блоком управления, а блок логического контроля содержит п субблоков, (где п - число, кратное шести), в каждый из которых дополнительно включен элемент неравнозначности, на первый вход которого подан логический «О, второй вход подключен к выходу логического «О элемента памяти и связан с информационным выходом субблока, выход - к управляющему выходу субблока, комбинационные, входы которого соединены со входами элемента И, тактовый вход связан со входом синхронизации элемента памяти, а вход установки в исходное состояние - со входом установки в «1 элемента памяти, при этом входы дешифратора и информационные входы блока управления подключены к выходам формирователей полумеандров, выходы дешифратора, сгруппированные по три, подключены соответственно к комбинационным входам субблоков логического контроля, управляющие выходы которых подсоеди нены ко входам обратной связи блока управления, а информационные выходы связаны с информационными выходами устройства, входы установки в исходное состояние объединены со входом сброса тактового блока и подключены к выходу установки в исходное состояние блока управления, . выходы установки в начальное состояние которого соответственно соединены со входами начала отсчета тактового блока, кроме того, выходы последнего подключены к тактовым входам субблоков, первый управляющий выход блока управления подключен к первому управляющему выходу устройства, второй управляющий вы(0 ход - ко входу запуска тактового блока, (Л третий управляющий выход - ко второму управляющему выходу устройства, а управляющий вход к управляющему входу устройства. 2.Устройство по. п. 1, отличающееся тем, что дешифратор содержит три по количеству фаз элемента НЕ, входы которых являются входами дешифратора, а выходы последнего собраны в шесть групп, по три выхода в каждой, при этом первый ю вход дешифратора подключен к первым высо ходам первой, второй и третьей групп несо о посредственно, а к первым выходам четвертой, пятой и шестой групп - через первый элемент НЕ, второй вход дешифратора подсоединен ко вторым выходам первой, второй и шестой групп через второй элемент НЕ, а ко вторым выходам третьей, четвертой и пятой групп - непосредственно, а третий вход дешифратора подключен к третьим выходам первой, пятой и шестой групп непосредственно, а к третьим выходам второй, третьей и четвертой групп через третий элемент НЕ. 3.Устройство по. п. 2, отличающееся тем, что блок управления содержит пер

1

Изобретение относится к электротехнике и может быть применено для контроля ассиметрии фаз с целью последующего использования контрольной информации в цепях регулирования реактивной мощности нагрузок, а также для защиты потребителей от неправильного чередования и обрыва фаз.

Известно устройство для контроля чередования фаз трехфазной сети, содержащее формирователи полумеандров каждой фазы, связанные своими выходами с блоком логического контроля чередования фаз и исполнительным органом 1.

Недостатками известного устройства являются низкая информативность контроля, заключающаяся в невозможности определения адреса исчезнувщей фазы, и значительный неконтролируемый диапазон ассиметрии фаз.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является устройство для контроля чередования фаз т-фазной сети, сйдержащее последовательно соединенные с блоком логического контроля, блоком задержки и исполнительным органом формирователи полумеандров, присоединяемые к контролируемым фазам, при этом блок логического контроля выполнен в виде т-1 субблоков контроля, у каждого из которых вход сброса и один комбинационный вход соединены с формирователем полумеандра опорной фазы, второй комбинайионный вход соединен с выходом предыдущего узла контроля, остальные комбинационные входы связаны с формирователем полумеандров, а выход подан на комбинационный вход следующего узла контроля 2.

Недостатком устройства является низкая информативность контроля.

Целью изобретения является повыщение информативности путем контроля сдвига между напряжением и током и определения наименования фаз в случае обратного порядка чередования.

Цель достигается тем, что устройство

для контроля чередования фаз т-фазной сети, содержащее формирователи полумеандров,входы которых подключены к контролируемым фазам, и блок логического контроля, функционально связанный с формирователем полумеандров и состоящий из субблоков, каждый из которых выполнен в виде последовательно соединенных элемента И и элемента памяти, дополнительно снабжено дещифратором, тактовым блоком и блоком управления, а блок логического контроля содержит п субблоков (где п - число, кратное щести), в каждый из которых дополнительно включен элемент неравнозначности, на первый вход которого подан логический «О, второй вход подключен к нулевому выходу элемента па мяти и связан с информационным выходом субблока, а выход - к управляющему выходу субблока, комбинационные входы которого соединены со входами элемента И, тактовый вход связан со входом синхроQ низации элемента памяти, а вход установки в исходное состояние - со входом установки в «1 элемента памяти, при этом входы дещифратора и информационные входы блока управления подключены к выходам формирователей полумеандров, выходы

5 дещифратора, сгруппированные по три, подключены соответственно к комбинационным входам субблоков логического контроля, управляющие выходы которых подсоедийены ко входам обратной связи блока управления, а информационные выходы связаны с информационными выходами устройства, входы установки в исходное состояние объединены со входом сброса тактового блока и подключены к выходу установки в исходное состояние блока управления, выходы установки в начальное состояние которого соответственно соединены со входами начала отсчета тактового блока, кроме того, выходы последнего, подключены к тактовым входам субблоков, первый управляющий выход подключен к первому управляющему выходу устройства, второй управляющий выход - ко входу запуска тактового блока, третий управляющий выход - ко второму управляющему выходу устройства, а управляющий вход - к управляющему входу устройства. Дещифратор содержит три по количеству фаз элемента НЕ, входы котбрых являются входами дещифратора, а вьгходы последнего собраны в шесть групп, по три выхода в каждой, при этом первый вход дещифратора подключен к первым выходам первой, второй и третьей групп непосредственно, а к первым выходам четвертой, пятой и щестой групп - через первый элемент НЕ, второй вход дещифратора подсоединен ко вторым выходам первой, второй и щестой групп через второй элемент НЕ, а ко вторым выходам третьей четвертой и пятой групп - непосредственно, а третий вход дешифратора подключен к третьим выходам первой, пятой и щестой групп непосредственно, а к третьим выходам второй, третьей и четвертой- групп через третий элемент НЕ. Кроме того блок управления содержит первый, второй и третий формирователи сигналов переднего фронта, входы которых подключены к информационным входам блока. элементы И установки, выходы которых соедийены с выходами установки в начальное состояние, последовательно соединенные первый элемент ИЛИ, входы которого связаны соответственно с первыми входами элементов И установки и подключены к выходам упомянутых формирователей, элемент управления, элемент памяти и элемент задержки и последовательно соединенные второй элемент ИЛИ, входы которого подключены ко входам обратной связи блока, четвертый формирователь сигнала переднего фронта, выход которого соединен со входом установки в «О элемента памяти, другой выход которого связан с объединенными вторыми входами элементов И установки и первым управляющим вь1ходом блока, и пятый формирователь сигнала переднего фронта, выход которого подключен к выходу установки в исходное состояние блока, при этом другой вход элемента И управления соединен со входом пятого формирователя и управляющим входом блока, выход элемента задержки - со вторым управляющим выходом блока, а выход второго элемента ИЛИ - с третьим управляющим выходом блока. На фиг. 1 представлена функциональная схема устройства для контроля чередования фаз трехфазной сети; на фиг. 2 (а, б, в, г, д, е, ж, з, и) - временные диаграммы работы устройства для трехфазной сети; на фиг. 3 (а; б, в, г, д, е, ж, 3, и, к, л, м) - временные диаграммы работы устройства для щестифазной сети. Устройство содержит {фиг. 1 формирователь 1.1, 1.2 и 1.3 полу меандров, входы которых подключены к контролируемым фазам а, в, с, дещифратор 2, блок логического контроля, состоящий из субблоков 3.1-3,6, блок 4 управления и тактовый блок 5. Выходы А, В и С формирователей 1 .1, 1.2 и 1.3 подключены соответственно ко входам дещифратора 2 и информационным входам блока 4 управления. Дешифратор 2 содержит элементы НЕ 6, 7 и 8, входы которых подключены ко входам А, ,В и С. Выходы дещифратора 2 собраны в щесть групп (I, II, HI, IV, V, VI) по три выхода (согласно количеству фаз) в каждой, и образуют следующие комбинации сигналов полумеандров: I - А, В, С; П - А, В, С; И1 - А, В, С; IV - А, В, С; V - А, В, С, VI - А, В, С. При этом первый вход А подключем к первым выходам первой, второй и третьей групп непосредственно, а к первым выходам четвертой, пятой и щестой групп - через первый элемент НЕ б, второй вход В подсоединен ко вторым выходам первой, второй и шестой групп через второй элемент НЕ 7, а ко вторым выходам третьей, четвертой и пятой групп - непосредственно, а третий вход С подключен к третьим выходам первой, пятой и щестой групп непосредственно, а к третьим выходам второй, третьей и четвертой групп - через третий элемент НЕ 8. Каждый субблок 3N (где N 1,... 6) содержит элемент И-9, входы которого подключены к комбинационным входам субблока, элемент 10N памяти и элемент 11 неравнозначности, выход которого соединен с управляющим выходом 12 субблока. Выход элемента И 9N подключен к информационному входу элемента 10N памяти, вход синхронизаци которого соединен с тактовым входом 13 субблока. На первый вход элемента 11 неравнозначности подан логический «О а второй вход подключен к нулевому выходу элемента 10 памяти. Кроме того, нулевой выход последнего связан с информационным выходом 14 субблока а вход установки в «I - со входом 15 установки в исходное состояние.

Блок 4 управления содержит первый, второй и третий формирователь 16, 17 и 18 сигналов переднего фронта, входы которых подключены соответственно к информационным входам А, В, и С блока, элементы И 19, 20 и 21 установки, выходы которых соединены с выходами 22,23 и 24 установки в начальное состояние, последовательно соединенные первый элемент ИЛИ 25, входы которого связаны соответственно с первыми входами элементов И 19, 20 и 21 и подключены к выходам упомянутых формирователей 16, 17 и 18, элемент И 26 управления, элемент 27 памяти и элемент 28 задержки, последовательно соединенные второй элемент ИЛИ 29 и четвертый формирователь 30 сигнала переднего фронта и пятый формирователь 31. сигнала переднего фронта. Входы элемента ИЛИ 29 подключены ко входам 12.1- 12.6 обратной связи блока 4. Выход четвертого формирователя 30 соединен со входом установки в «О элемента 27 памяти, вход установки в «1 которого подключен к выходу элемента И 26 управления.

S

Первый вход последнего связан с выходом первого элемента ИЛИ 25, а второй вход - со входом пятого формирователя 31 и С управляющим входом 32 блока 4. Нулевой выход элемента 27 памяти подключен к объединеннБш вторым входам элементов И 19, 20 и 21 и первому управляющему выходу 33 блока 4, а единичный выход - через эле.мент 28 задержки ко второму управляющему выходу 34 блока 4. .Выход пятого формирователя 31 соединен с выходом установки в исходное состояние. Выход второго элемента 29 ИЛИ подключен к третьему управляющему выходу 35 блока 4. Тактовый блок 5 содержит генератор 36 тактов и кольцевой счетчик 37. Вход генератора 36. подключен ко входу запуска блока 5, а выход - ко входу сдвига счетчика 37.

Входы сброса последнего соединены со входом сброса блока 5, входы нечетных разрядов - со входами начала отсчета, а выходы - с выходами тактового блока 5.

Вход запуска блока 5 подключен ко второму управляющему выходу 34 блока 4 управления. Вход сброса, связан со входами ,15 установки в исходное состояние субблоков 3.1-3.6 и подсоединен к выходу установки в исходное состояние блока 4 управления. Выходы тактового блока 6. соединены соответственно с тактовыми входами 13.1 -13.6 субблоков 3.1-3.6 логического контроля. Комбинационные входы последних подключены к выходам дещифратора 2; субблока 3.1 - к выходам 1(А,В,С); субблока 3,2 - к выходам 11(А, В, С); субблока 3.3 - к выходам III(А, В,С); субблока 3.4 - к выходам IV( А, В, С);

субблока 3.5 - к выходам V(A, В, С); субблока 3.6 - к выходам VI(А, В, С); Управляющий вход 32 блока 4 подсоединен к управляющему входу устройства; первый управляющий выход 33 блока 4 -к первому управляющему выходу устройства; третий управляющий выход 35 блока 4 - ко второму управляющему выходу устройства.

Формирователи 1.1, 1.2 и 1.3 полумеандров предназначены для формирования полумеандров фаз а, в к с. Длительность полумеандра соответствует длительности полупериода фазы и равна Т/2.

Дещифратрр 2 предназначен для формирования комбинаций сигналов полумеандров, длительностью каждой из которых Т/6.

Субблоки 3.1-3.6 логического контроля предназначены для контроля комбинаций сигналов полумеандров в промежутки времени, определяемые длительностью каждой комбинации и выдачи контрольной информации в приемник, например, процессор (не показан).

Блок 4 управления предназначен для подачи тактовых сигналов в субблоки 3.1-- 3.6 логического контроля в промежутки времени, определяемые длительностью комбинаций сигналов полумеандров. Элемент 28 задержки в блоке 4 управления предназначен для сдвига тактовой серии на Т/2/г, где п - целое число, кратное щести.

Генератор 36 блока 5 предназначен для формирования тактовой серии, период следования тактов которой Т/П. Кольцевой счетчик 37 содержит п разрядов. Пример реализации устройства на фи-г. 1 показан для л 6.

Устройство для контроля чередования фаз щестифазной сети существенных отличий не имеет и реализуется наращиванием элементов в схеме. Соответственно количеству фаз возрастает количество формирователей полумеандров, количество входов дещифратора, количество элементов НЕ в нём, количество выходов в комбинационной группе, количество формировате.лей сигналов переднего фронта полумеандров в блоке управления, количество элементов И установки, количество входов установки в начальное состояние тактового блока и количество комбинационных входов в субблоках логического контроля. При этом число п, кратное щести, тем больще, чем выщё требуемая точность контроля угла сдвига между током и напряжением.

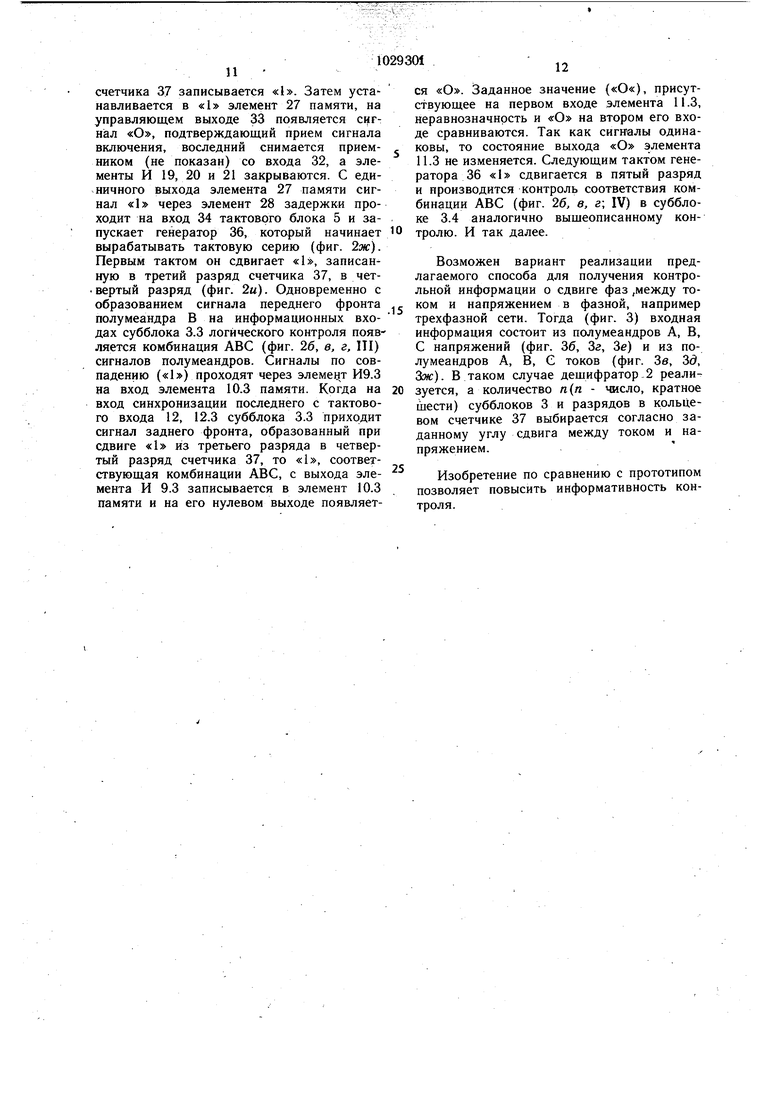

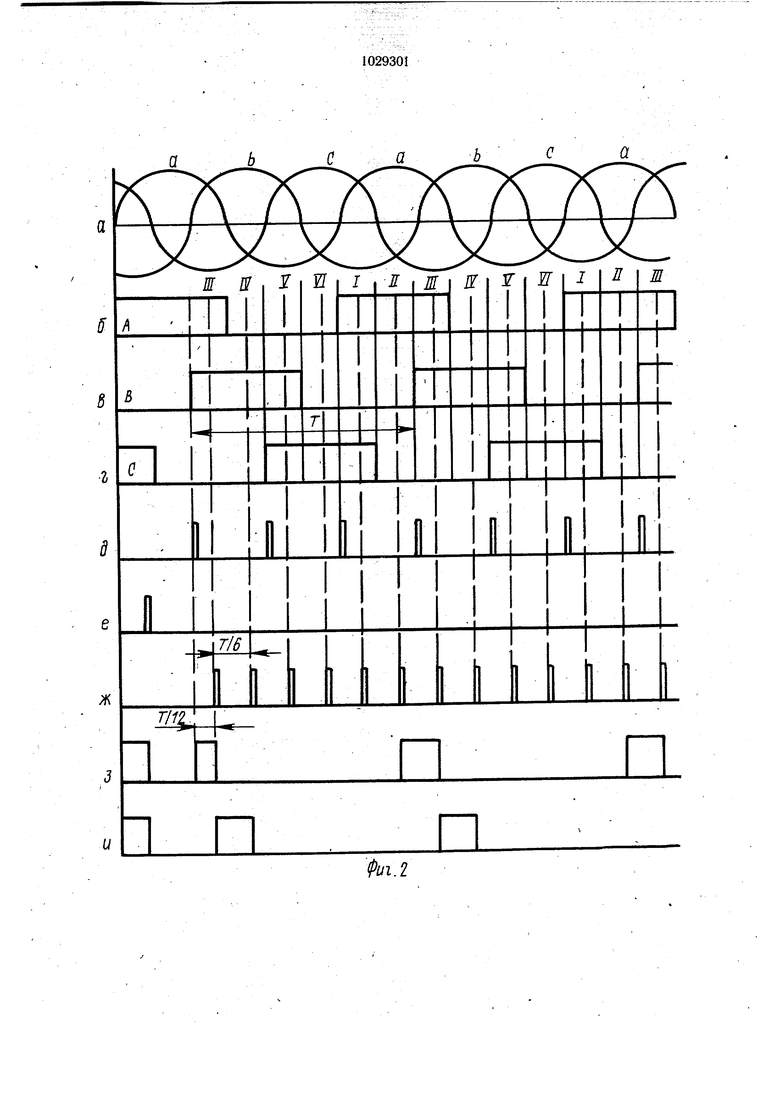

На фиг. 2 для трехфазной сети даны временные диаграммы: 2а - изменения текущих значений фаз а, в, с; 26, 2в, 2г изменения сигналов полумеандров А, В, С, соответствующих фаз а, в, с; 2д - сигналы передних фронтов полумеандров А, В, С; 2е - сигнал переднего фронта на выходе 15 формирователя 31 блока 4 (сигнал установки в .исходное состояние субблоков 3 и блока 5); 2ж - тактовая серия на выходе генератора 36 блока 5; 2з, 2ы - состояния 3-го и 4-го разрядов кольцевого счетчика 37 блока 5. На фиг. 3 для шестифазной сети даны временные диаграммы: За - изменения текущих значений фаз а, а, в, в, с, с; 36, Зв, Зг, 3d, 3 е, Зж - изменения сигналов полумеаидров А, А, В, В, С, С соответствующих фаз а, а, в, Ь, с, с, Зз - сигналы передних фронтов полумеандров А, А, В, В, С, С, Зи -- сигнал установки

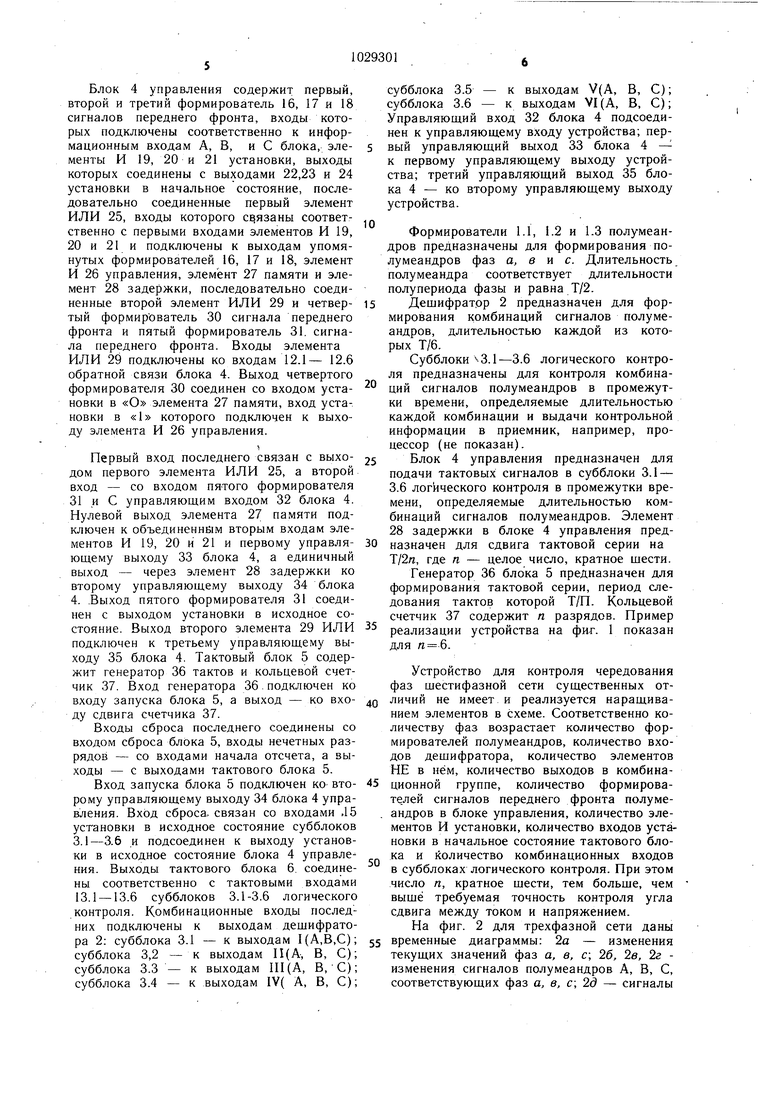

Состояния сигналов полумеандров для трехфазной сети представлены в табл. 1.

Попумеандры

В

001

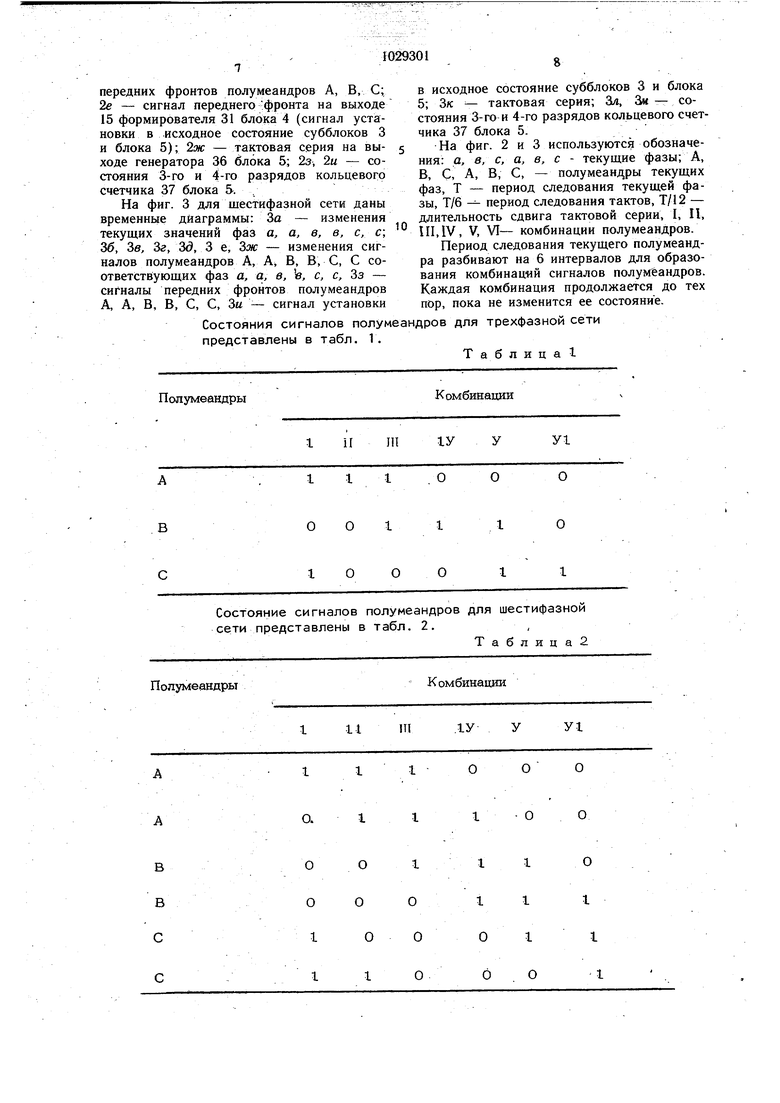

Состояние сигналов полумеандров для шестифазной сети представлены в табл. 2.,

Попумеакдры

о.

о

в в с

о

Таблица

Комбинации

О

ОО

О

Табпица2

Комбинации

III

У1

.1У

У

о

о

о

о

о

о I

1 1 I о

I

1 о о в исходное состояние субблоков 3 и блока 5; 3/с - тактовая серия; 3л, 3м - состояния 3-го и 4-го разрядов кольцевого счетчика 37 блока 5. На фиг. 2 и 3 используются обозначения: а, в, с, а, в, с - текущие фазы; А, В, С, А, В, С, - полумеандры текущих фаз, Т - период следования текущей фазы, Т/6 - период следования тактов. Т/12 - длительность сдвига тактовой серии, I, II, ni,lV, V, VI- комбинации полумеандров. Период следования текущего полумеандра разбивают на 6 интервалов для образования комбинаций сигналов полумёандров. Каждая комбинация продолжается до тех пор, пока не изменится ее состояние.

В табл. 1 и 2 «1 - наличие сигнала высокого уровня полумеандра, «О - наличие низкого уровня полумеандра.

Включение устройства в работу может произойти во время любой комбинации, поэтому за начало отсчета принимают сигнал переднего фронта (фиг. 2д или фиг. Зз) полумеандра (фиг. 2в или фиг. Зг), который формируется первым после включения. .

Указанный сигнал является сигналом для начала формирования тактовой серии (фиг. 2ж или фиг. Зк). С целью повышения стабильности работы устройства тактовую серию сдвигают (фиг. 2ж или фиг. Зк) относительно переднего фронта текущего полумеандра на Т/2л (фиг. 2 и 3 /г б).

Величина сдвига объясняется разбросом параметров реальных элементов и порогом их срабатывания. Поэтому при больших п для исключения этого влияния и повышения вероятности стробирования в интервале текущей комбинации выбирают усредненное значение сдвига Т/2/г (фиг. 2 и 3 Т/12).

Устройство работает следующим образом (фиг. 1 и 2)

Пусть на одном из управляющих выходов 12.1 -12.6 субблоков 3.1-3.6 логического контроля имеется сигнал «1 несоответствия. Тогда последний поступает на соответствующий вход обратной связи блока 4 управления и через элемент ИЛИ 29 и формирователь 30 устанавливает «О элемент 27 памяти. Кроме того, с выхода элемента ИЛИ 29 сигнал несоответствия поступает на второй управляющий выход 35 устройства. Сигнал «О с единичного выхода элемента 27 памяти через элемент 28 задержки поступает на второй управляющий выход 34 блока 4 управления. Сигнал «1 с нулевого выхода элемента 27 памяти поступает на вторые входы элементов И 19, 20 и 21 и открывает их. Сигнал «О с выхода 34 блока 4, поступает на вход запуска генератора 36 тактового блока 5 и отключает его.

Генератор 36 прекращает вырабатывать тактовую серию, в результате чего отсутствуют поразрядный сдвиг «1 в счетчике 37 и стробирование задним фронтом сигнала элементов 10.1...10.6 памяти субблоков 3.1-3.6 и на нулевых выходах элементов памяти появляется контрольная информация несоответствия.

Приемник информации (не показан), работающий по программе, приняв сигнал прерывания с выхода 35 устройства, снимает с выходов 14.1 -14.6 контрольную информацию и выдает сигналы воздействия для устранения ассиметрии или обрыва фазы. В случае невозможности принятия рещения из-за неопределенности в контрольной информации приемник согласно программе

может произвести запуск устройства и съем контрольной информации неоднократно. Например, произошел обрыв фазы а. Тогда устройство включается по сигналу переднего фронта полумеандра В или С. Допустим, что устройство включилось по сигналу переднего фронта полумеандра В. Благодаря несоответствию возникшей комбинации А, В, С с ее заданным значением (фиг. 26, в, г; VI), происходит останов устройства. Из этого следует, что при стробировании отсутствует фаза а, однако судить о том, что произошел обрыв фазы а или ее сдвиг, пока нельзя. Поэтому производится повторный запуск устройства, но уже

по следующему сигналу переднего фронта полумеандра С. Комбинация ABC (фиг. 26, в, г; 6) соответствует заданному значению (ABC 1). Следующая комбинация может быть ABC, соответствующая ассиметрии фазы а в сопоставлении с первой комбинацией останова, или ABC, соответствующая заданному значению (фиг. 26, в, г; VI). За Нею должна следовать комбинация ABC (фиг 26, в, г, I), но ее нет, появляется комбинация ABC, не соответствующая за, данному значению. Сопоставляя комбинацию ABC с первоначальной комбинацией останова, следует, что произошел обрыв фазы а. Таким образом, устройство позволяет приемнику различить обрыв фазы от ассиметрии фаз.

Запуск устройства производится следующим образом (фиг. 1)..

На управляющий вход 32 устройства приемник посылает сигнал включения. В дальнейшем сигнал снимается при получе5 НИИ приемником подтверждения на первом управляющем выходе 33. Сигнал включения поступает в блок 4 управления, в котором открывает элемент И 26 и формирует сигнал переднего фронта на выходе формирователя 31. С вь1хода последнего сигнал переднего фронта поступает на входы 15 субблоков 3.1-3.6 логического контроля и тактового блока 5, в которых он устанавливает в «1 элементы 10.1-10.6 памяти и производит сброс разрядов кольцевого счетчика 37 (фиг. 2з и 2и). На информационный вход блока 4 управления от одного из формирователей, например 1.2 (фиг. 2е), полумеандров поступает сигнал. Последний формирует сигнал переднего фронта на выходе формирователя 17 (фиг.

0 2() и проходит через открытый элемент И 20 на выход 23 блока 4 и через элемент ИЛИ 25 и открытый элемент И 26 на вход установки в «1 элемента 27 памяти. Но так как первая цепь содержит только один элемент И 20, то на вход 23 кольцевого счетчика 37 тактового блока 5 сигнал переднего фронта поступает с опережением. По этому сигналу в третий разряд (фиг. 2э) счетчика 37 записывается «1. Затем устанавливается в «1 элемент 27 памяти, на управляющем выходе 33 появляется щтнал «О, подтверждающий прием сигнала включения, воследний снимается приемником (не показан) со входа 32, а элементы И 19, 20 и 21 закрываются. С единичного выхода элемента 27 памяти сигнал «1 через элемент 28 задержки проходит на вход 34 тактового блока 5 и запускает генератор 36, который начинает вырабатывать тактовую серию (фиг. 2ж). Первым тактом он сдвигает «1, записанную в третий разряд счетчика 37, в чет. вертый разряд (фиг. 2ы). Одновременно с образованием сигнала переднего фронта полумеандра В на информационных входах субблока 3.3 логического контроля появляется комбинация ABC (фиг. 26, в, г, ITI) сигналов полумеандров. Сигналы по совпадению («1) проходят через элемент И9.3 на вход элемента 10.3 памяти. Когда на вход синхронизации последнего с тактового входа 12, 12.3 субблока 3.3 приходит сигнал заднего фронта, образованный при сдвиге «1 из третьего разряда в четвертый разряд счетчика 37, то «1, соответствующая комбинации ABC, с выхода элемента И 9.3 записывается в элемент 10.3 памяти и на его нулевом выходе появляется «О. Заданное значение {«О«), присутствующее на первом входе элемента 11.3, неравнозначность и «О на втором его входе сравниваются. Так как сигналы одинаковы, то состояние выхода «О элемента 11.3 не изменяется. Следующим тактом генератора 36 «1 сдвигается в пятый разряд и производится контроль соответствия комбинации ABC (фиг. 26, в, г; IV) в субблоке 3.4 аналогично вышеописанному контролю. И так далее. Возможен вариант реализации предлагаемого способа для получения контрольной информации о сдвиге фаз ,между током и напряжением в фазной, например трехфазной сети. Тогда (фиг. 3) входная информация состоит из полумеандров А, В, С напряжений (фиг. 36, За, Зе) и из полумеандров А, В, С токов (фиг. Зв, 3(3, Зэк). В таком случае дешифратор-2 реализуется, а количество п(п - число, кратное шести) субблоков 3 и разрядов в кольЦе вом счетчике 37 выбирается согласно заданному углу сдвига между током и напряжением. Изобретение по сравнению с прототипом позволяет повысить информативность контроля.

г/6

I

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля чередования фаз трехфазной сети | 1977 |

|

SU642817A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля чередования и обрыва фаз фазной сети | 1977 |

|

SU708456A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1983-07-15—Публикация

1981-07-10—Подача